A New Low-Power Circuit Design Optimization for Image Processing

Abstract

1. Introduction

2. Related Work

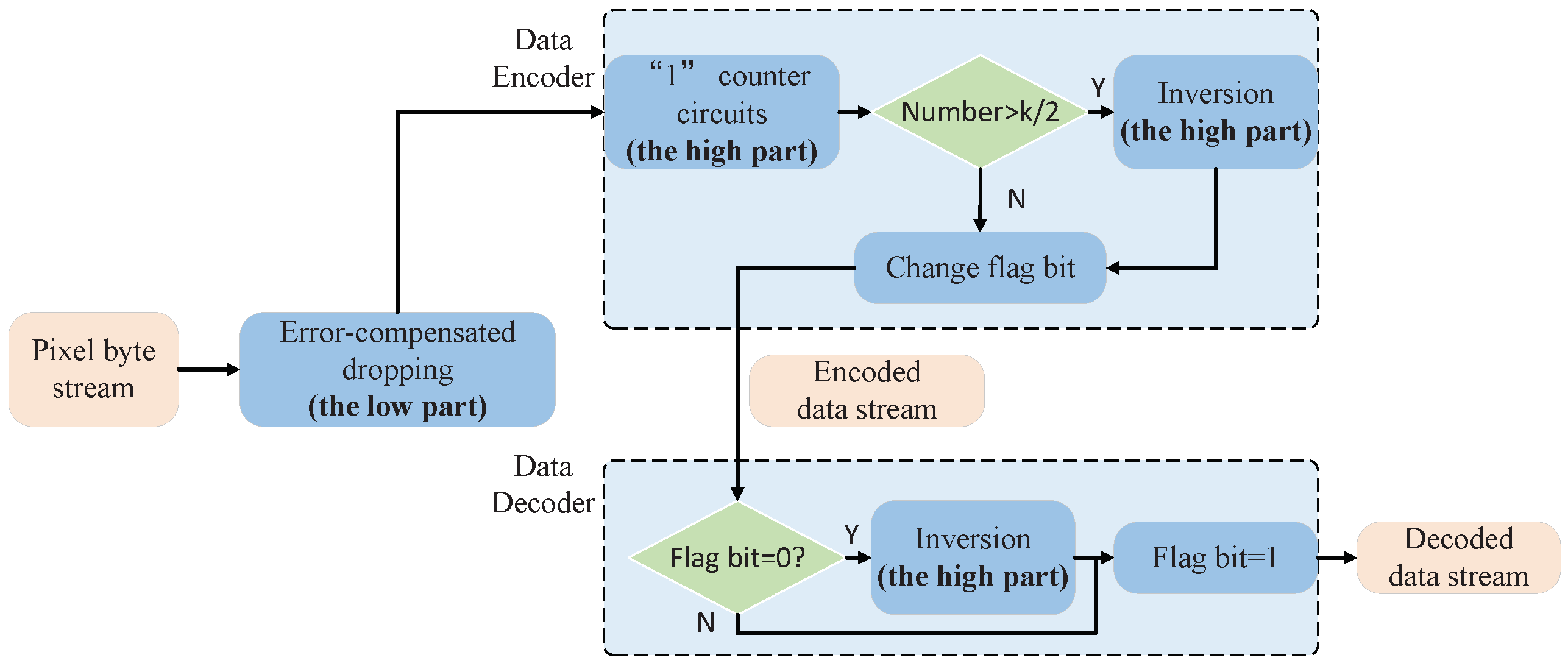

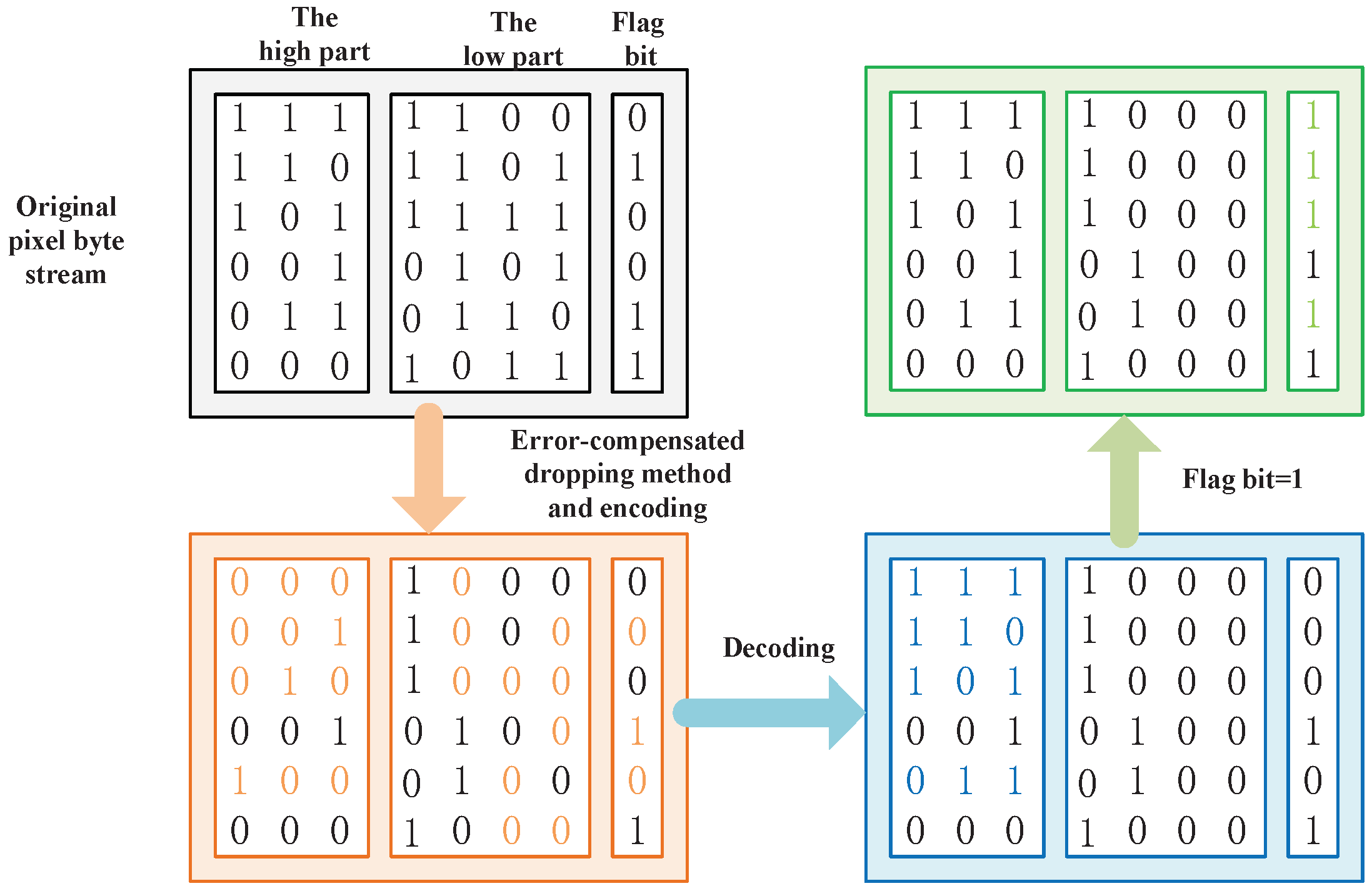

3. Proposed Method

| Algorithm 1 Data Encoder |

|

| Algorithm 2 Data Decoder |

|

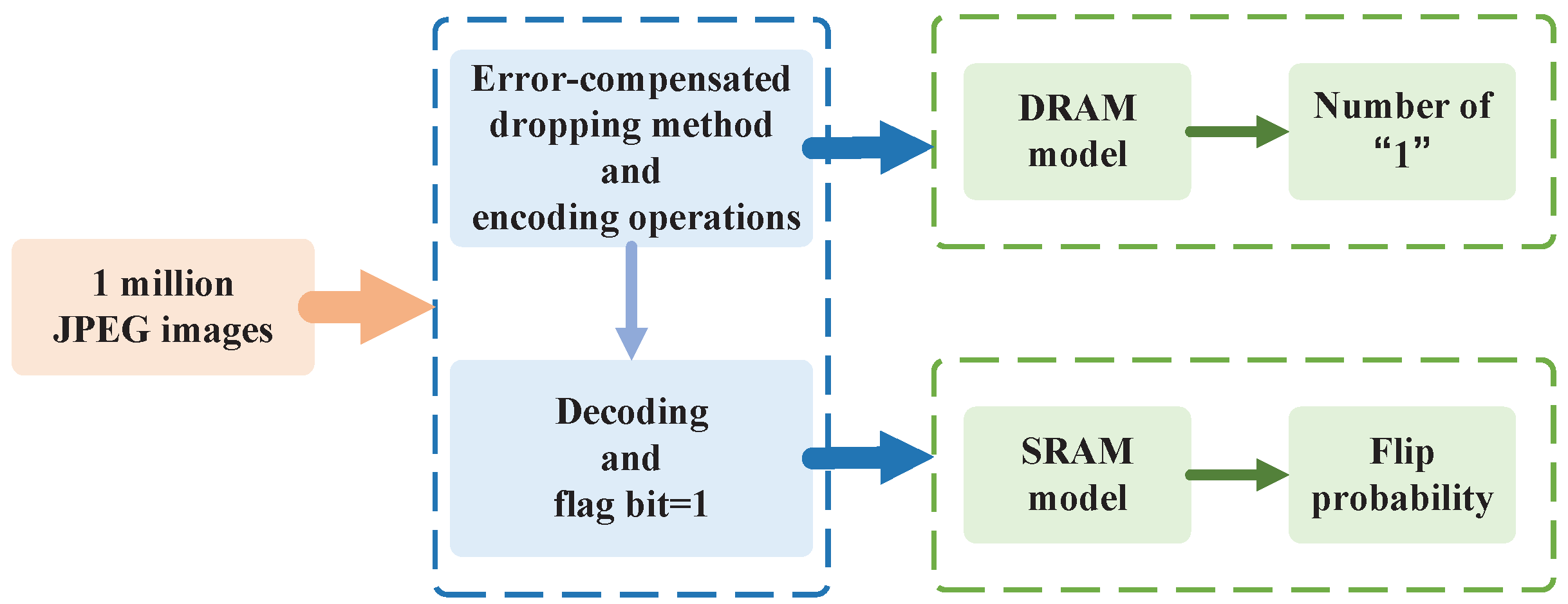

4. Simulation Experiment

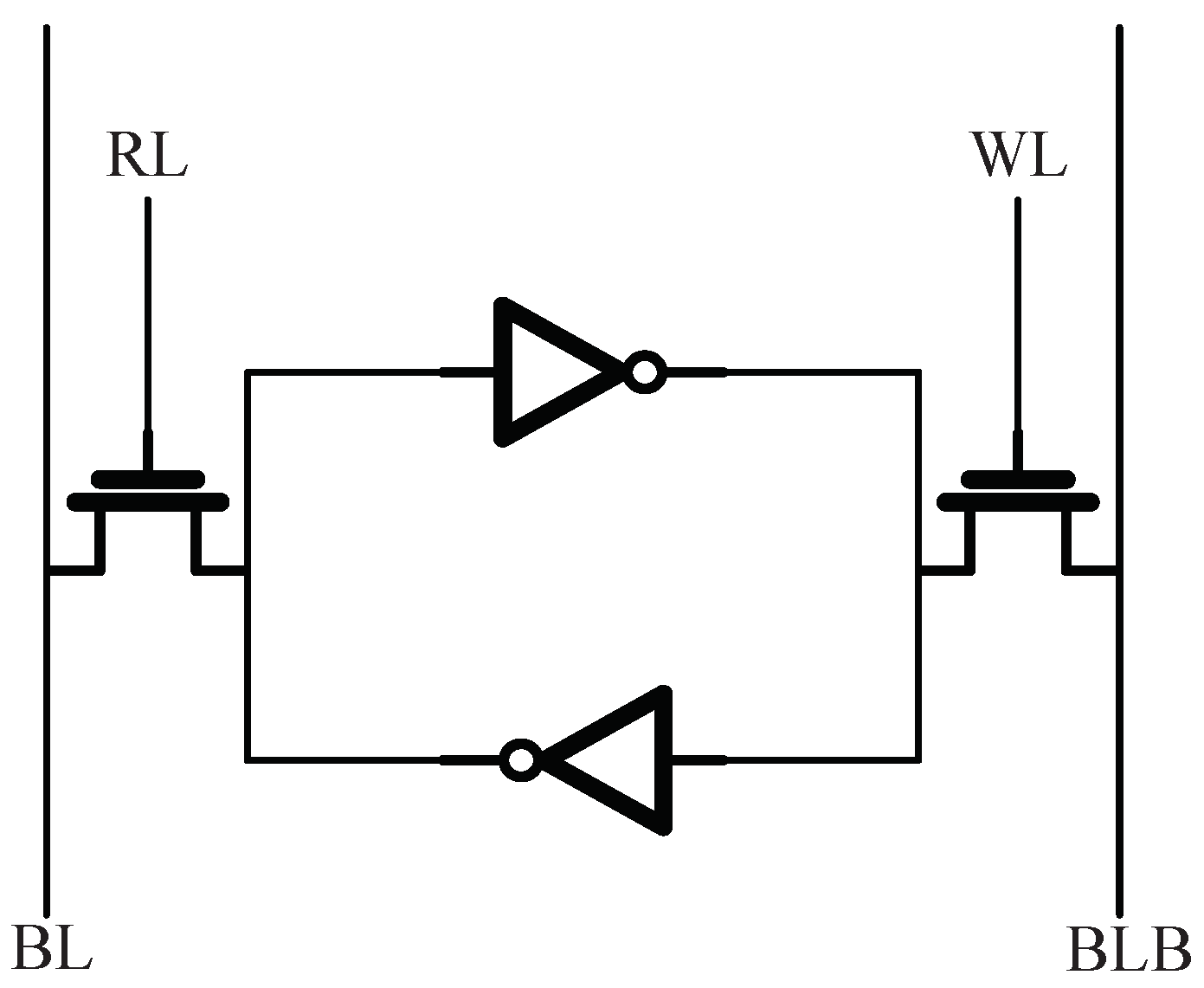

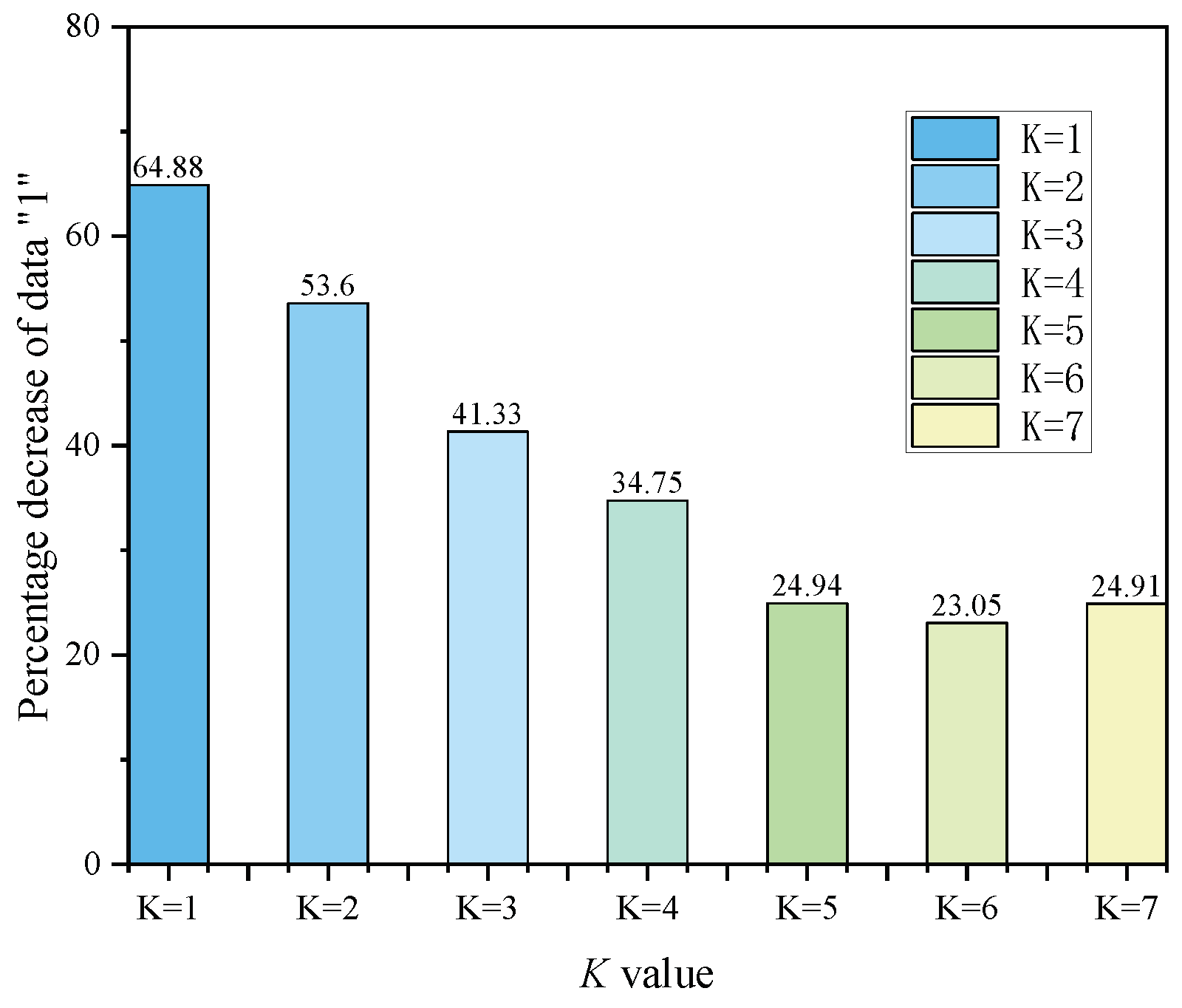

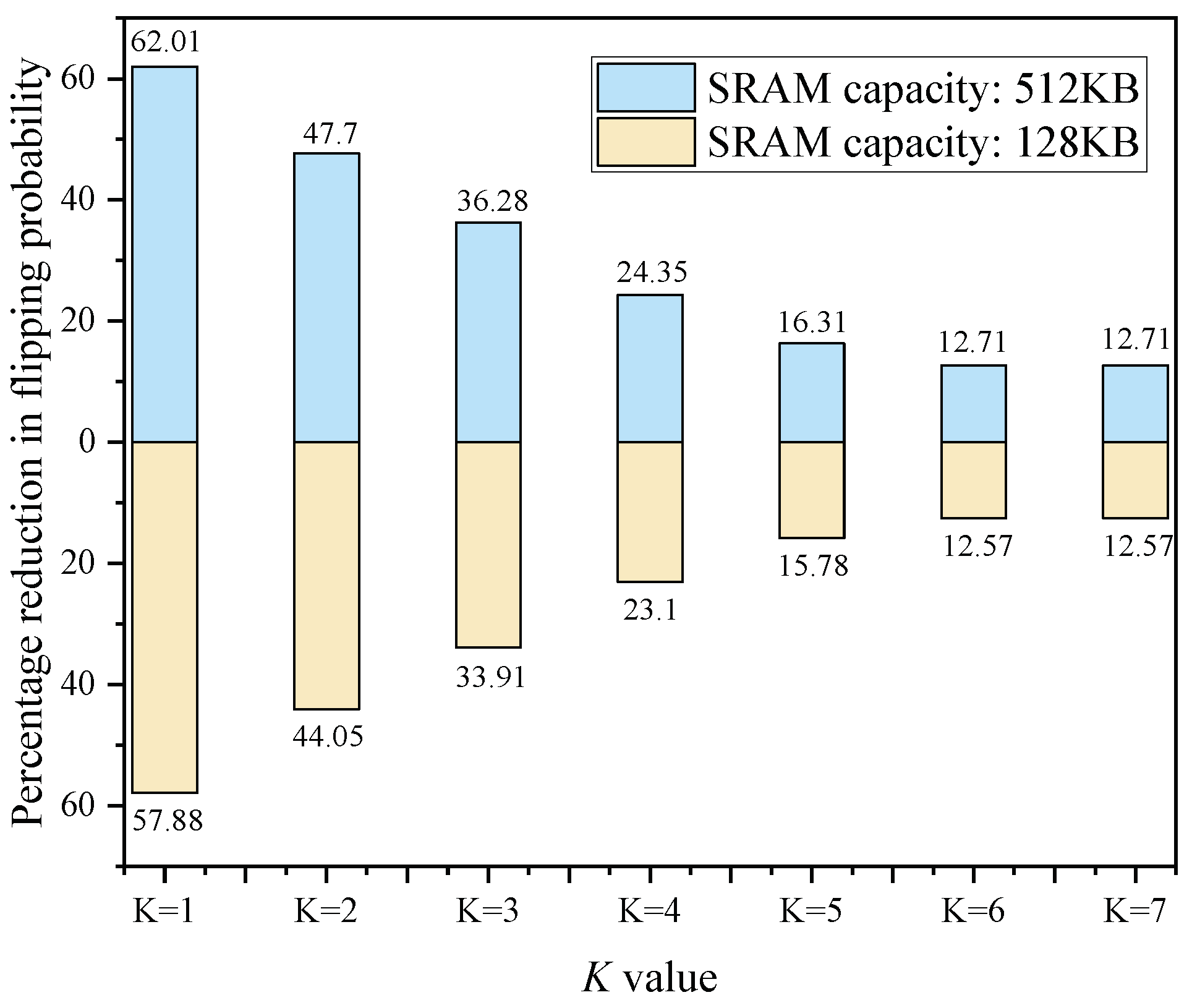

4.1. Storage Power Consumption Simulation

4.2. Circuit Overhead Simulation

| Algorithm 3 Circuit logic structure |

| INPUT: OUTPUT:

|

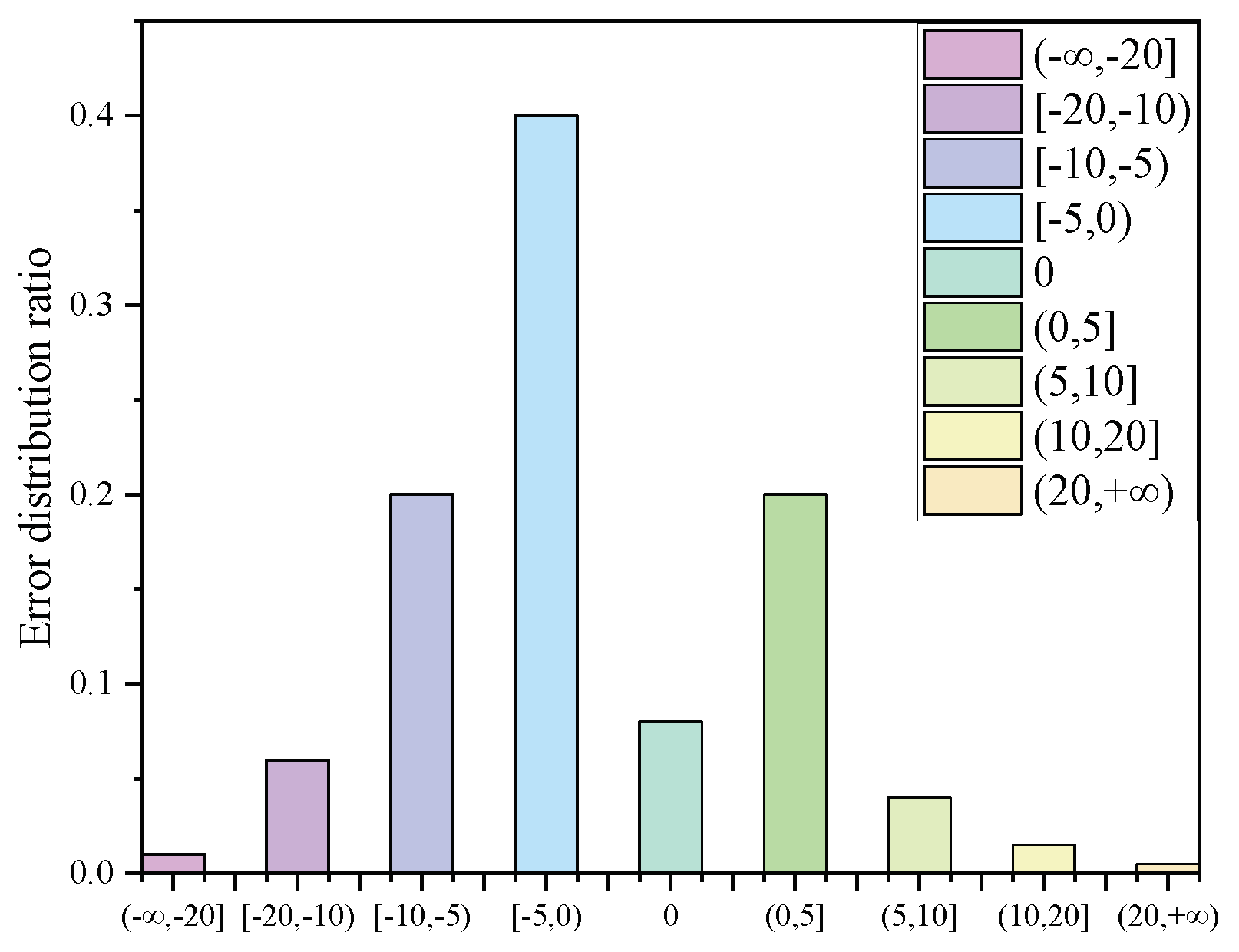

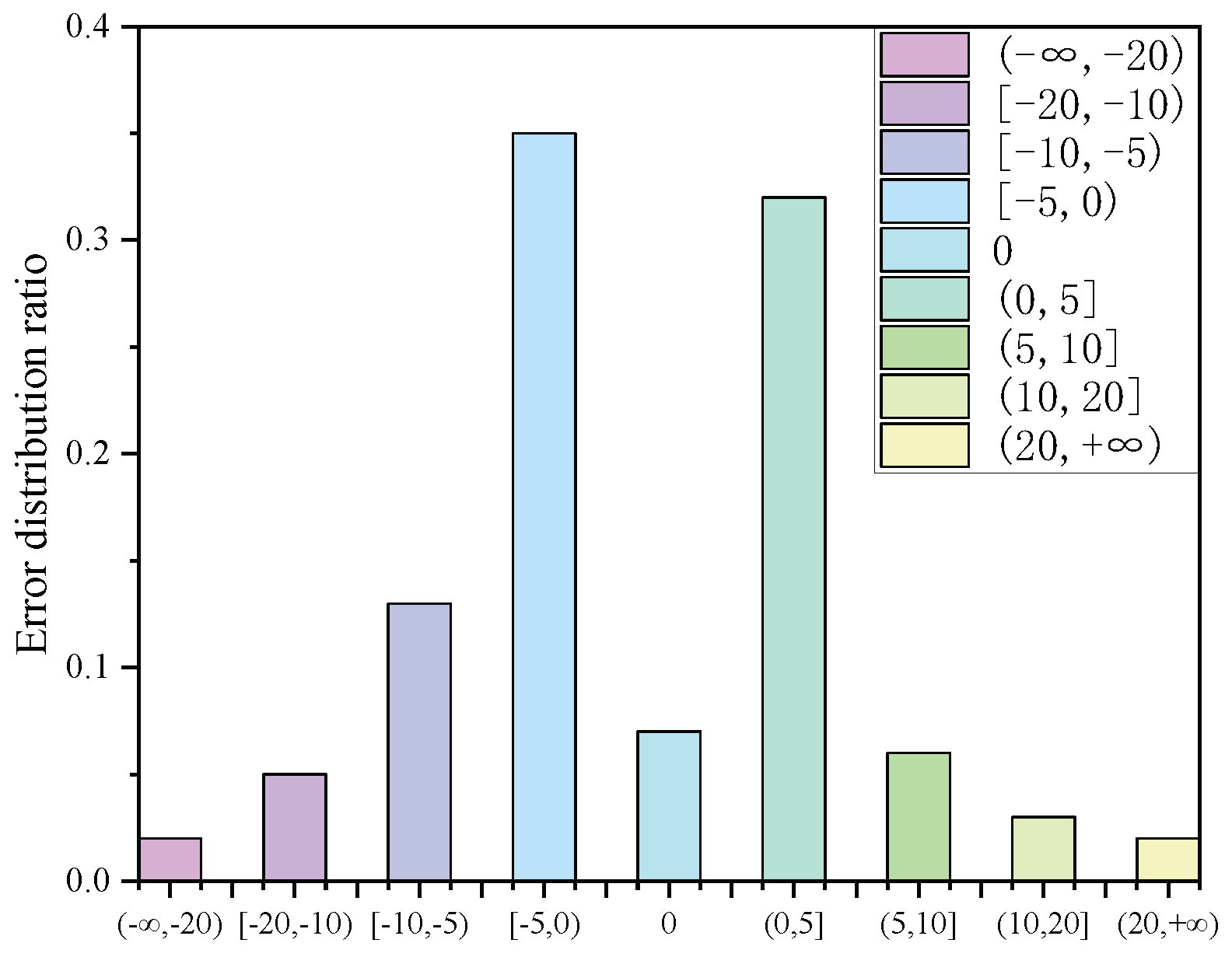

4.3. Output Quality Simulation for Image Application

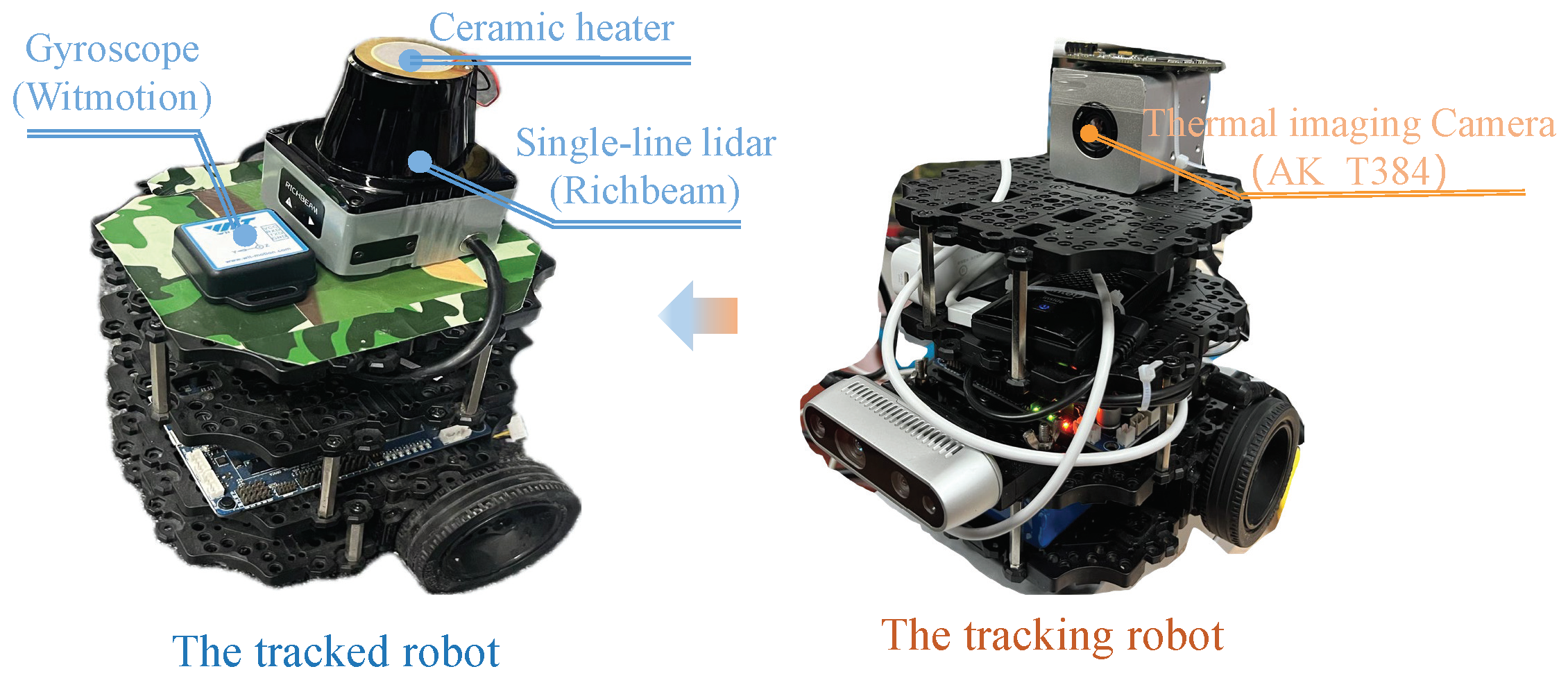

4.4. Experiment on a Robotic Platform

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Lin, C.P.; Tseng, P.C.; Chiu, Y.T.; Lin, S.S.; Cheng, C.C.; Fang, H.C.; Chao, W.M.; Chen, L.G. A 5 mW MPEG4 SP encoder with 2D bandwidth-sharing motion estimation for mobile applications. In Proceedings of the 2006 IEEE International Solid State Circuits Conference—Digest of Technical Papers, San Francisco, CA, USA, 6–9 February 2006; pp. 1626–1635. [Google Scholar] [CrossRef]

- Carroll, A.; Heiser, G. An analysis of power consumption in a smartphone. In Proceedings of the 2010 USENIX Conference on USENIX Annual Technical Conference, Boston, MA, USA, 23–25 June 2010; p. 21. [Google Scholar]

- Moore, G.E. Cramming more components onto integrated circuits. Proc. IEEE 1998, 86, 82–85. [Google Scholar] [CrossRef]

- Shafique, M.; Garg, S. Computing in the Dark Silicon Era: Current Trends and Research Challenges. IEEE Des. Test 2017, 34, 8–23. [Google Scholar] [CrossRef]

- Wey, I.C.; Lin, P.J.; Wu, B.C.; Peng, C.C.; Lin, P.H. Near-threshold-voltage circuit design: The design challenges and chances. In Proceedings of the 2014 International SoC Design Conference (ISOCC), Jeju, Republic of Korea, 3–6 November 2014; pp. 138–141. [Google Scholar] [CrossRef]

- Chang, I.J.; Mohapatra, D.; Roy, K. A voltage-scalable & process variation resilient hybrid SRAM architecture for MPEG-4 video processors. In Proceedings of the 2009 46th ACM/IEEE Design Automation Conference, San Francisco, CA, USA, 26–31 July 2009; pp. 670–675. [Google Scholar]

- Mukhopadhyay, S.; Mahmoodi, H.; Roy, K. Statistical design and optimization of SRAM cell for yield enhancement. In Proceedings of the IEEE/ACM International Conference on Computer Aided Design, San Jose, CA, USA, 7–11 November 2004; pp. 10–13. [Google Scholar] [CrossRef]

- Gaioni, L. Analytical Analysis of Power-Constrained Repeaters’ Insertion in Large-Scale CMOS Chips. Electronics 2024, 13, 4368. [Google Scholar] [CrossRef]

- Shiga, H.; Takashima, D.; Shiratake, S.i.; Hoya, K.; Miyakawa, T.; Ogiwara, R.; Fukuda, R.; Takizawa, R.; Hatsuda, K.; Matsuoka, F.; et al. A 1.6 GB/s DDR2 128 Mb Chain FeRAM with Scalable Octal Bitline and Sensing Schemes. IEEE J. Solid-State Circuits 2010, 45, 142–152. [Google Scholar] [CrossRef]

- Niyato, D.; Hossain, E.; Rashid, M.M.; Bhargava, V.K. Wireless sensor networks with energy harvesting technologies: A game-theoretic approach to optimal energy management. IEEE Wirel. Commun. 2007, 14, 90–96. [Google Scholar] [CrossRef]

- Li, B.; Xia, L.; Gu, P.; Wang, Y.; Yang, H. Merging the Interface: Power, area and accuracy co-optimization for RRAM crossbar-based mixed-signal computing system. In Proceedings of the 2015 52nd ACM/EDAC/IEEE Design Automation Conference (DAC), San Francisco, CA, USA, 8–12 June 2015; pp. 1–6. [Google Scholar] [CrossRef]

- Park, J.; Johnson, J. RGB No More: Minimally-Decoded JPEG Vision Transformers. In Proceedings of the IEEE/CVF Conference on Computer Vision and Pattern Recognition (CVPR), Vancouver, BC, Canada, 18–22 June 2023; pp. 22334–22346. [Google Scholar]

- Qiao, F.; Zhou, N.; Chen, Y.; Yang, H. Approximate Computing in Chrominance Cache for Image/Video Processing. In Proceedings of the 2015 IEEE International Conference on Multimedia Big Data, Beijing, China, 20–22 April 2015; pp. 180–183. [Google Scholar] [CrossRef]

- Zhou, N.; Qiao, F.; Yang, H.; Wang, H. Low-Power Off-Chip Memory Design for Video Decoder Using Embedded Bus-Invert Coding. In Proceedings of the 2011 Tenth International Symposium on Autonomous Decentralized Systems, Tokyo, Japan, 23–27 March 2011; pp. 251–255. [Google Scholar] [CrossRef]

- Liu, S.; Pattabiraman, K.; Moscibroda, T.; Zorn, B.G. Flikker: Saving DRAM refresh-power through critical data partitioning. In Proceedings of the Sixteenth International Conference on Architectural Support for Programming Languages and Operating Systems, New York, NY, USA, 5–11 March 2011; pp. 213–224. [Google Scholar] [CrossRef]

- Gupta, V.; Mohapatra, D.; Raghunathan, A.; Roy, K. Low-Power Digital Signal Processing Using Approximate Adders. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2013, 32, 124–137. [Google Scholar] [CrossRef]

- Chang, I.J.; Mohapatra, D.; Roy, K. A Priority-Based 6T/8T Hybrid SRAM Architecture for Aggressive Voltage Scaling in Video Applications. IEEE Trans. Circuits Syst. Video Technol. 2011, 21, 101–112. [Google Scholar] [CrossRef]

- Liu, M.; Que, H.; Yang, X.; Zhang, K.; Yu, Q.; Yan, L.; Wang, T.; Jin, Y.; Zhou, N. A Selective Bit Dropping and Encoding Co-Strategy in Image Processing for Low-Power Design in DRAM and SRAM. IEEE J. Emerg. Sel. Top. Circuits Syst. 2023, 13, 48–57. [Google Scholar] [CrossRef]

- Wang, Y. Video Processing and Communications; Signal Processing Series; Prentice Hall: Saddle River, NJ, USA, 2002. [Google Scholar]

- Krizhevsky, A.; Sutskever, I.; Hinton, G.E. Imagenet classification with deep convolutional neural networks. In Proceedings of the Advances in Neural Information Processing Systems 25 (NIPS 2012), Lake Tahoe, NV, USA, 3–6 December 2012. [Google Scholar]

- He, K.; Zhang, X.; Ren, S.; Sun, J. Deep residual learning for image recognition. In Proceedings of the IEEE Conference on Computer Vision and Pattern Recognition, Las Vegas, NV, USA, 27–30 June 2016; pp. 770–778. [Google Scholar]

- Montemerlo, M. FastSLAM: A Factored Solution to the Simultaneous Localization and Mapping Problem. In Proceedings of the AAAI02, Menlo Park, CA, USA, 28 July–1 August 2002. [Google Scholar]

- Dwijotomo, A.; Abdul Rahman, M.A.; Mohammed Ariff, M.H.; Zamzuri, H.; Wan Azree, W.M.H. Cartographer slam method for optimization with an adaptive multi-distance scan scheduler. Appl. Sci. 2020, 10, 347. [Google Scholar] [CrossRef]

- Noreen, I.; Khan, A.; Habib, Z. Optimal path planning using RRT* based approaches: A survey and future directions. Int. J. Adv. Comput. Sci. Appl. 2016, 7, 11. [Google Scholar] [CrossRef]

| K | With No Processing | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|---|---|---|---|---|---|---|---|---|

| Navg | 3.955 | 1.389 | 1.835 | 2.321 | 2.581 | 2.969 | 3.043 | 2.970 |

| K | With No Processing | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|---|---|---|---|---|---|---|---|---|

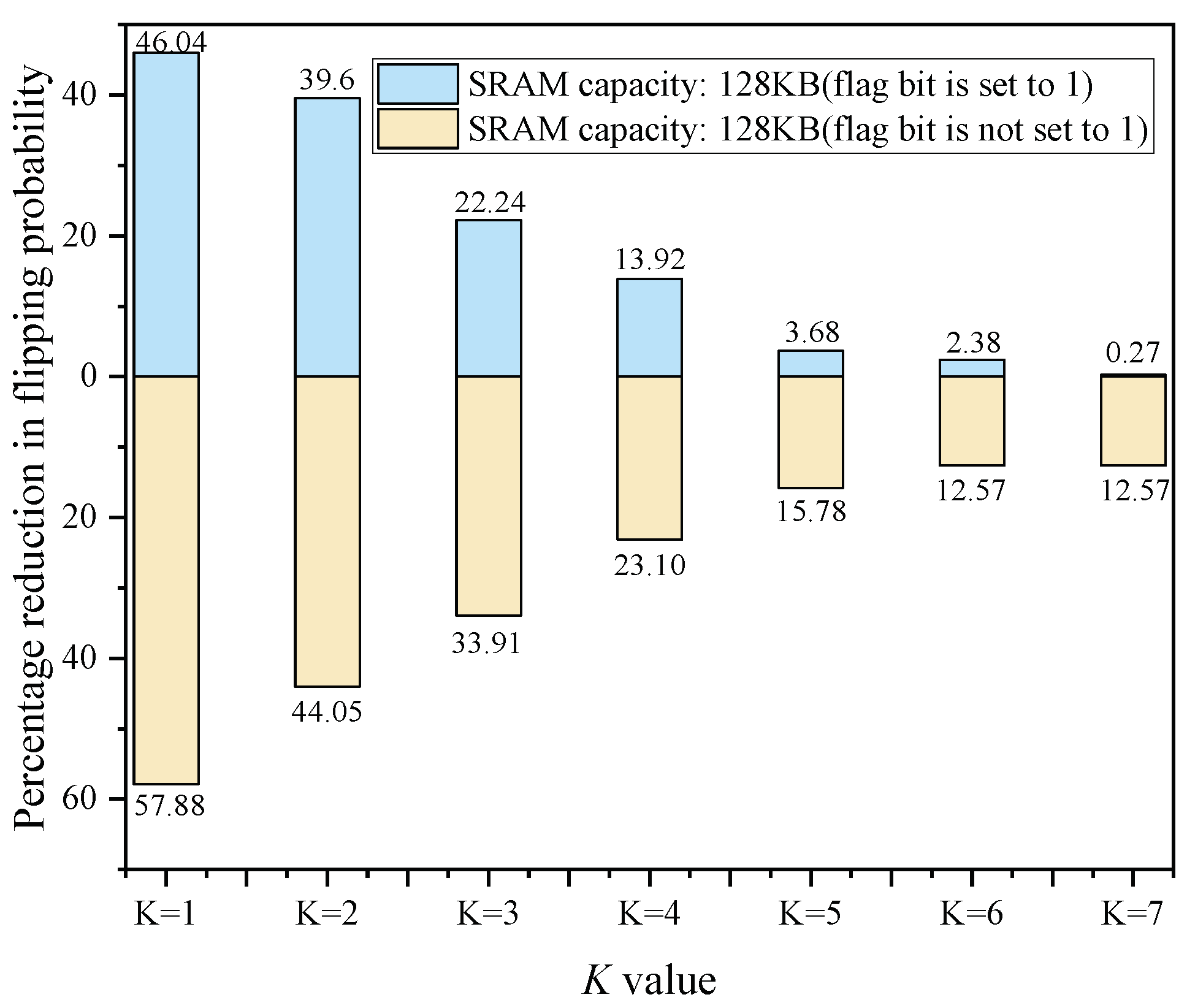

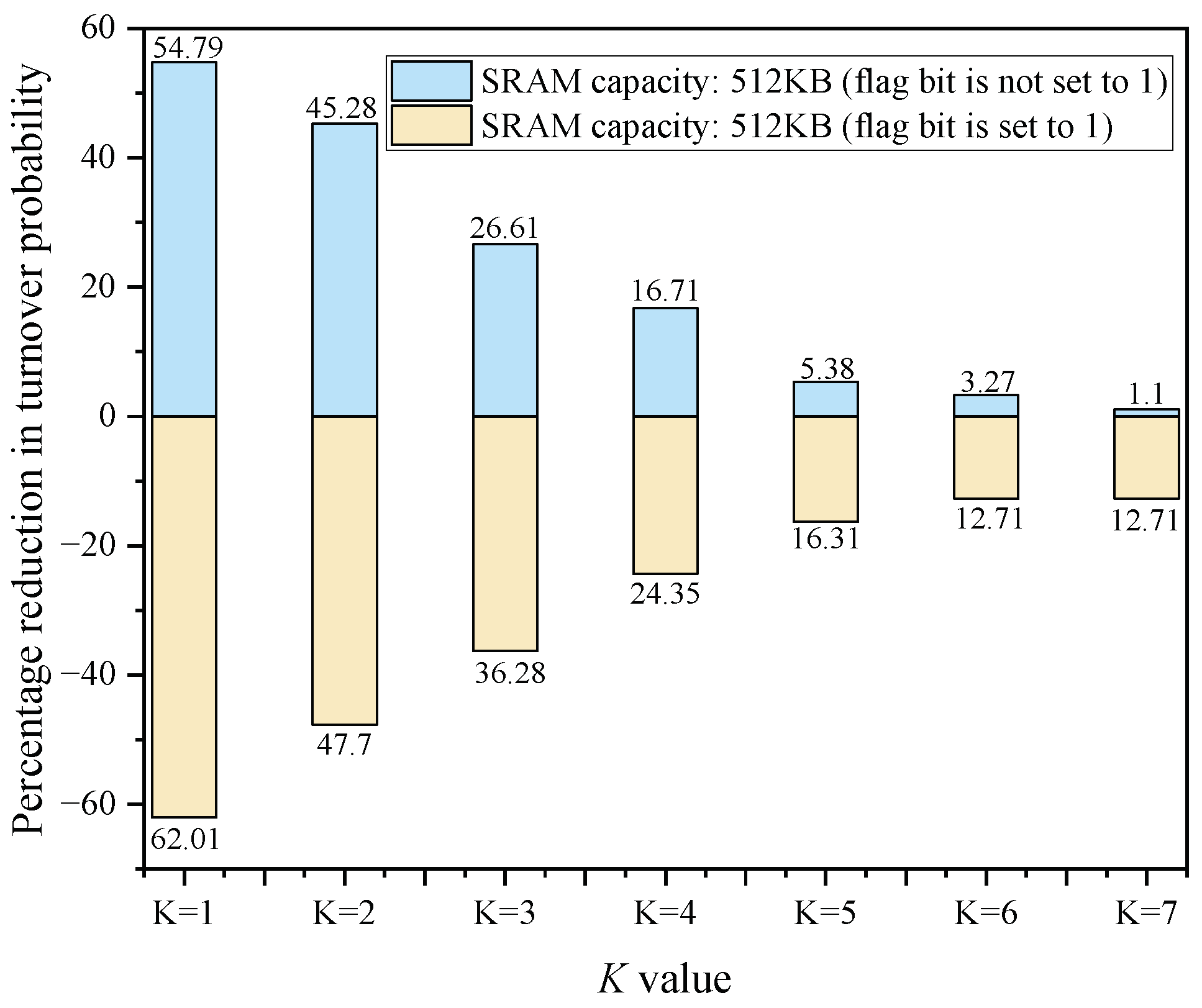

| Filp probability/cache areas of 128 KB | 0.49 | 0.20 | 0.27 | 0.32 | 0.37 | 0.41 | 0.43 | 0.43 |

| Filp probability/cache areas of 128 KB (Flag bit is not set to 1) | 0.49 | 0.26 | 0.29 | 0.38 | 0.42 | 0.47 | 0.47 | 0.48 |

| Filp probability/cache areas of 512 KB | 0.44 | 0.17 | 0.23 | 0.28 | 0.34 | 0.37 | 0.39 | 0.39 |

| Filp probability/cache areas of 128 KB (Flag bit is not set to 1) | 0.44 | 0.20 | 0.24 | 0.33 | 0.37 | 0.42 | 0.43 | 0.44 |

| K Value | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|---|---|---|---|---|---|---|---|

| Power (W) | 77.48 | 61.83 | 27.55 | 18.64 | 18.22 | 20.75 | 25.47 |

| Area (m2) | 241.84 | 171.92 | 120.44 | 84.61 | 91.64 | 71.40 | 89.32 |

| Dataset | Network Structure | Initial Learning Rate | Lr_Decay (0.9) | Batch_Size | Epochs |

|---|---|---|---|---|---|

| Fashion | MLP 128-MLP 4 | 0.001 | / | 32 | 20 |

| MNIST handwritten digits | MLP 128-MLP 4 | 0.001 | / | 32 | 20 |

| Iris flower | MLP 16-MLP 8-MLP 3 | 0.001 | / | 32 | 20 |

| CIFAR-10 | ResNet18 | 0.01 | 2500 | 128 | 40 |

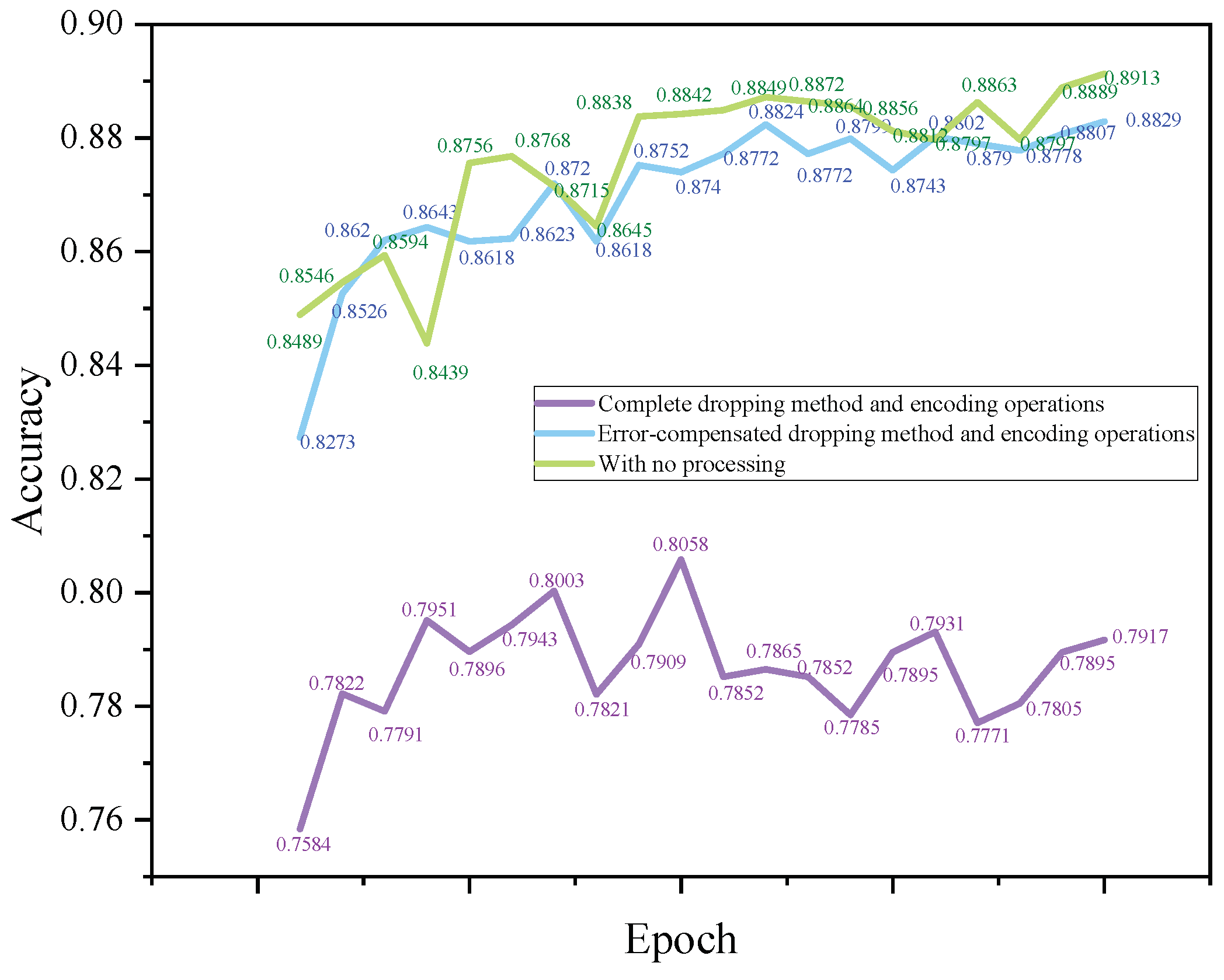

| Epoch | 1 | 2 | 3 | ... | 15 | 16 | 17 | 18 | 19 | 20 |

|---|---|---|---|---|---|---|---|---|---|---|

| Accuracy (Accurate storage) | 84.9% | 85.4% | 85.9% | … | 88.1% | 87.9% | 88.9% | 88.0% | 88.6% | 88.5% |

| Accuracy (K = 7) | 82.9% | 85.9% | 85.7% | … | 88.4% | 88.6% | 88.2% | 89.3% | 88.5% | 88.9% |

| Accuracy (K = 6) | 84.2% | 86.2% | 86.4% | … | 87.6% | 88.9% | 88.4% | 88.8% | 88.7% | 89.2% |

| … | … | … | … | … | … | … | … | … | … | … |

| Accuracy (K = 1) | 82.7% | 85.3% | 86.2% | … | 87.4% | 88.1% | 87.9% | 87.8% | 88.1% | 88.3% |

| Epoch | 1 | 2 | 3 | ... | 35 | 36 | 37 | 38 | 39 | 40 |

|---|---|---|---|---|---|---|---|---|---|---|

| Accuracy (Accurate storage) | 64.9% | 67.7% | 70.3% | … | 89.3% | 88.9% | 89.7% | 90.4% | 89.6% | 89.8% |

| Accuracy (K = 7) | 61.2% | 69.9% | 71.7% | … | 89.4% | 88.7% | 90.2% | 89.3% | 90.4% | 89.9% |

| Accuracy (K = 6) | 65.7% | 69.3% | 69.9% | … | 89.7% | 89.8% | 89.4% | 90.6% | 89.7% | 89.8% |

| … | … | … | … | … | … | … | … | … | … | … |

| Accuracy (K = 1) | 61.8% | 66.5% | 70.2% | … | 90.3% | 89.1% | 89.5% | 88.8% | 89.5% | 89.9% |

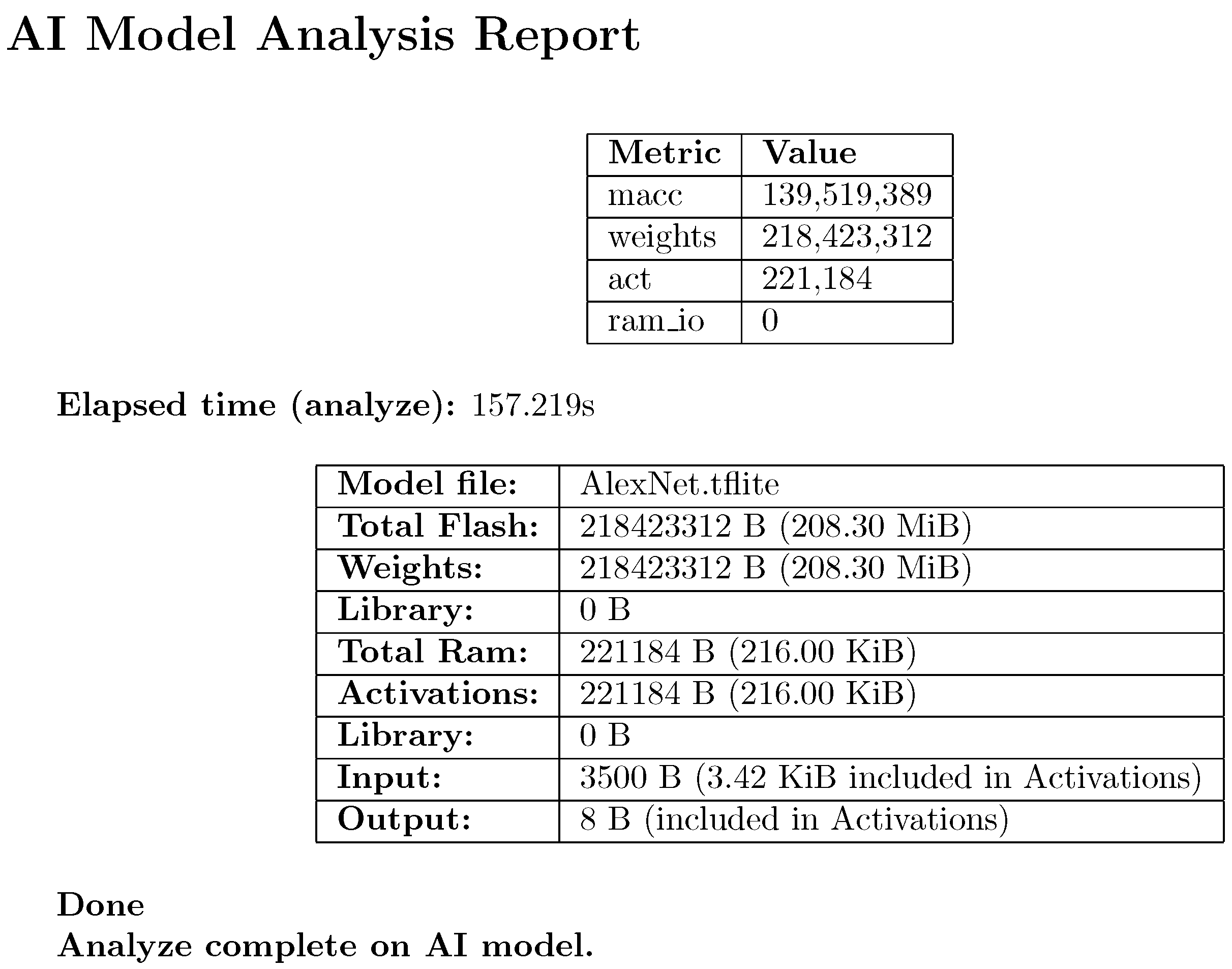

| Network Structure | Initial Learning Rate | Lr_Decay (0.9) | Batch_Size | Epochs |

|---|---|---|---|---|

| Conv(1,16)-Conv(16,32) -Conv(32,64)-MLP 128-MLP 4 | 0.01 | 2500 | 400 | 60 |

| Storage Method | Accurate Storage | Approximate Storage |

|---|---|---|

| Time taken to reach destination (s) | 12.17 | 12.56 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liu, M.; Feng, S.; Shan, W.; Que, H.; Wang, J.; Yang, X. A New Low-Power Circuit Design Optimization for Image Processing. Electronics 2025, 14, 277. https://doi.org/10.3390/electronics14020277

Liu M, Feng S, Shan W, Que H, Wang J, Yang X. A New Low-Power Circuit Design Optimization for Image Processing. Electronics. 2025; 14(2):277. https://doi.org/10.3390/electronics14020277

Chicago/Turabian StyleLiu, Mingkai, Shuo Feng, Weihao Shan, Haohua Que, Jianchao Wang, and Xinghua Yang. 2025. "A New Low-Power Circuit Design Optimization for Image Processing" Electronics 14, no. 2: 277. https://doi.org/10.3390/electronics14020277

APA StyleLiu, M., Feng, S., Shan, W., Que, H., Wang, J., & Yang, X. (2025). A New Low-Power Circuit Design Optimization for Image Processing. Electronics, 14(2), 277. https://doi.org/10.3390/electronics14020277