Grid-Forming Converter Overcurrent Limiting Strategy Based on Additional Current Loop

Abstract

1. Introduction

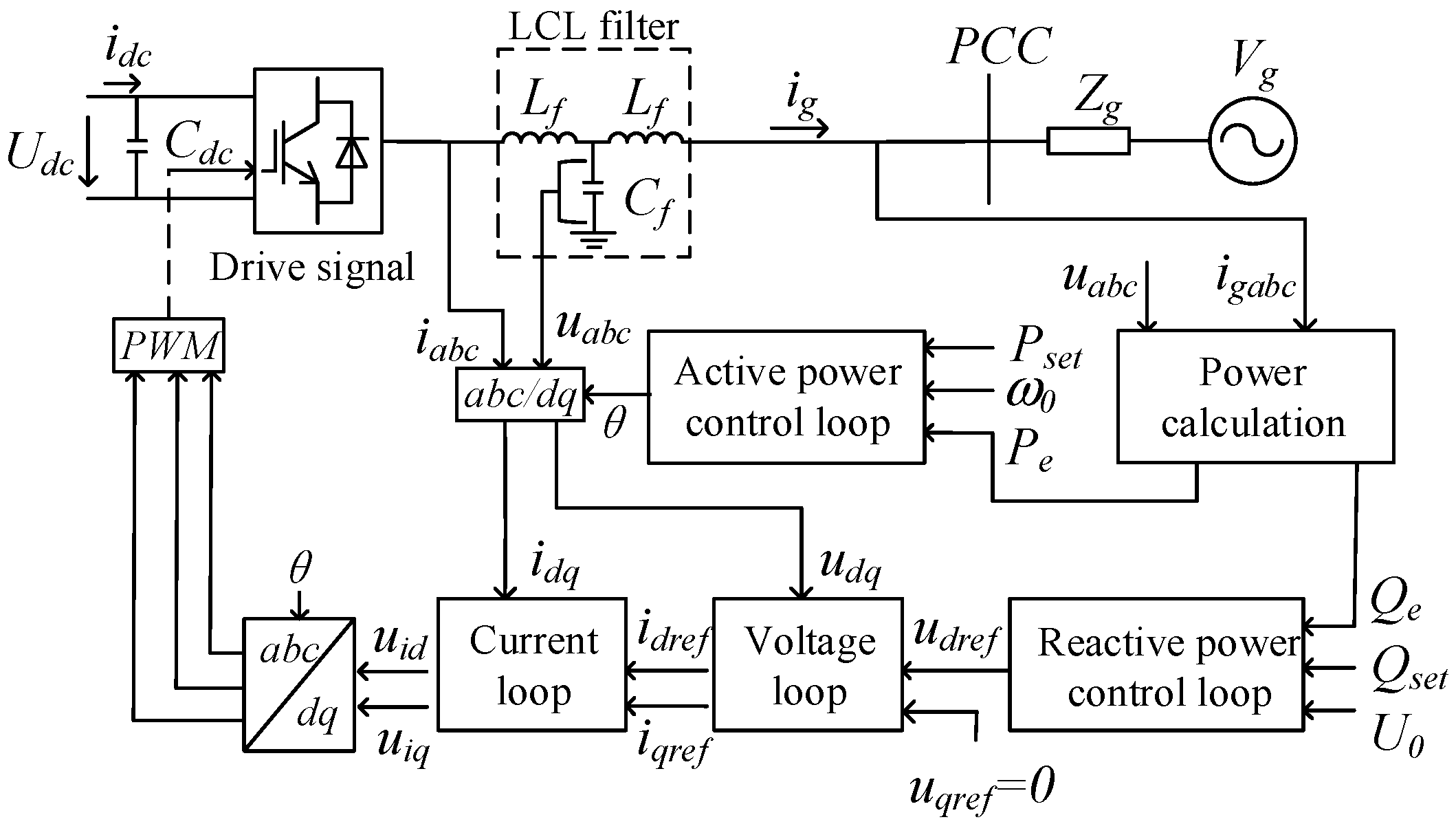

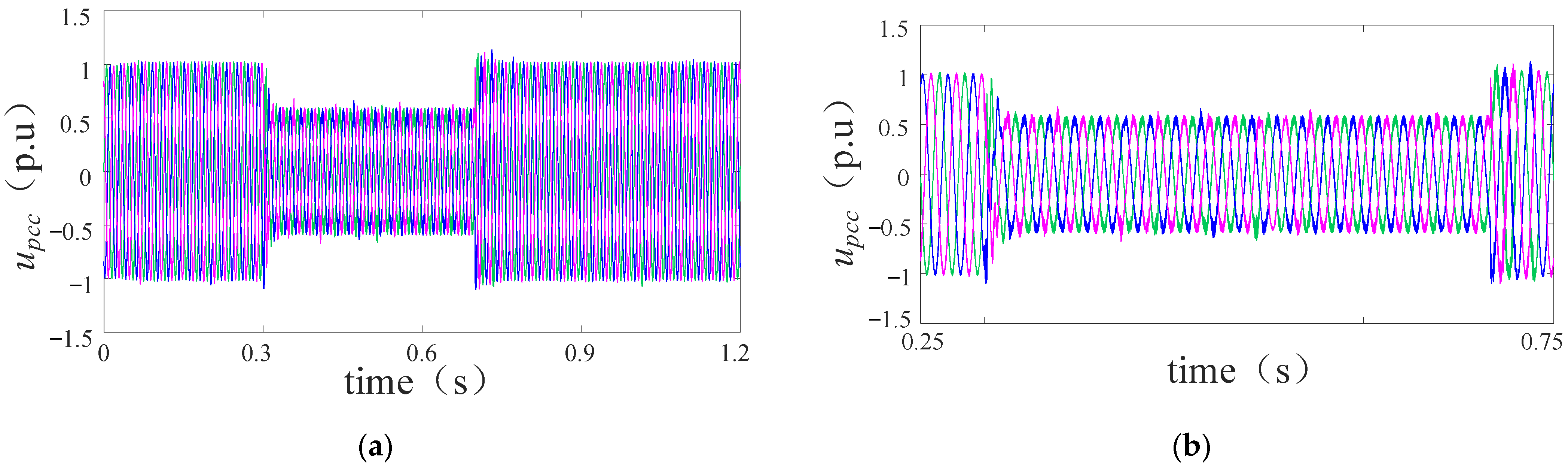

2. Proposed Current Limiting Strategy

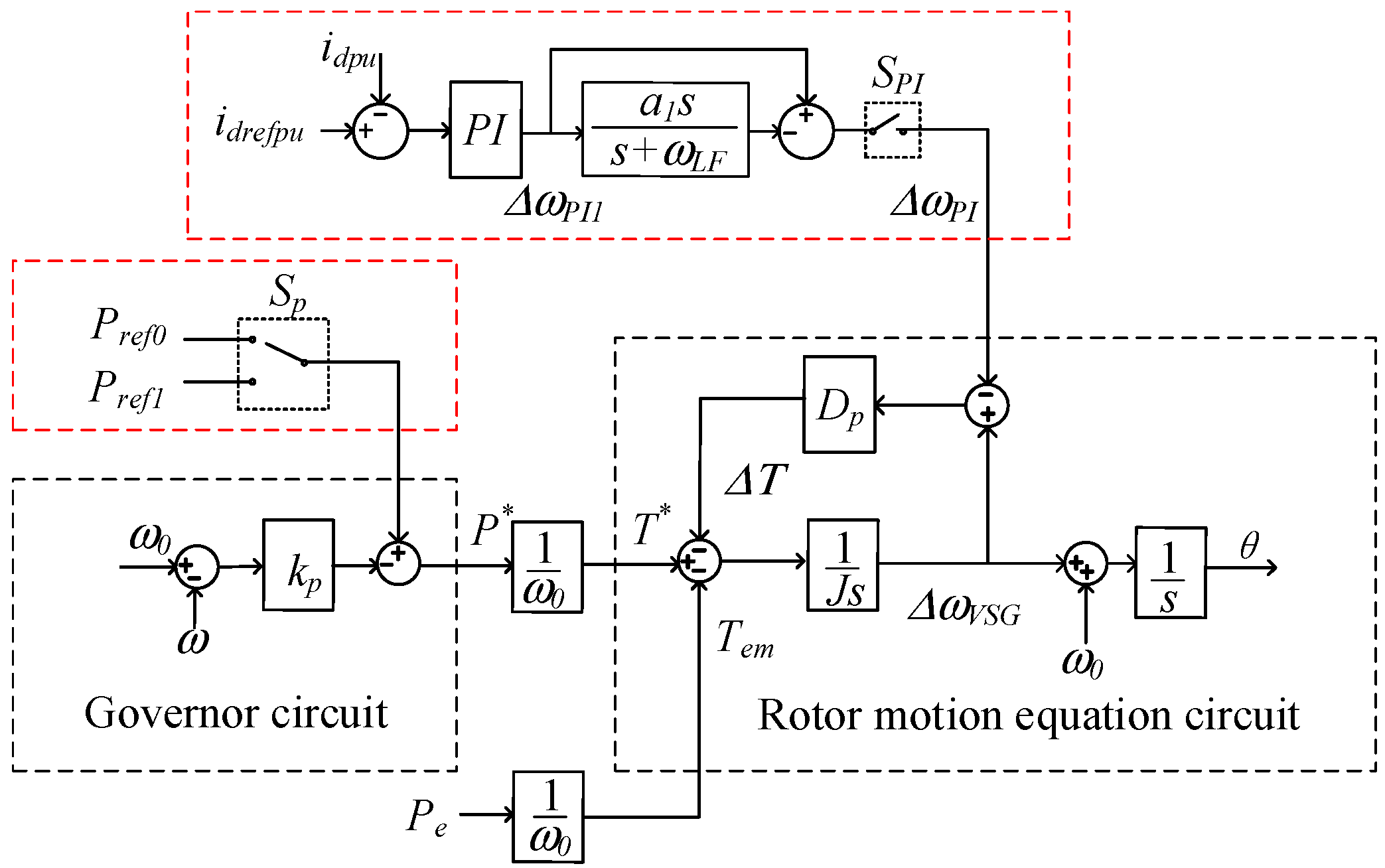

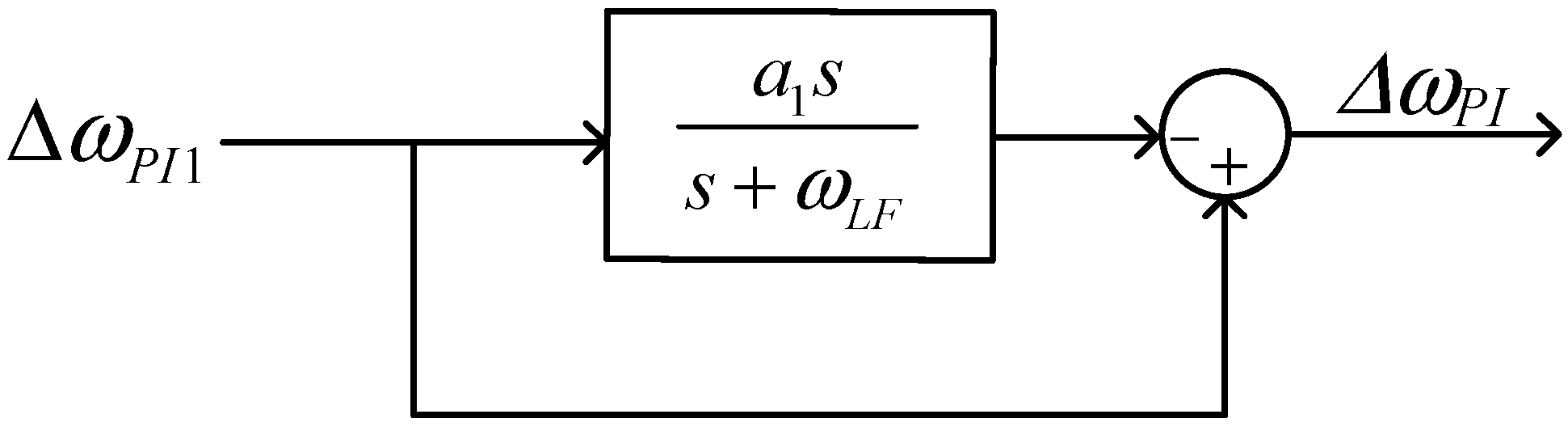

2.1. Active-Frequency Control Strategy

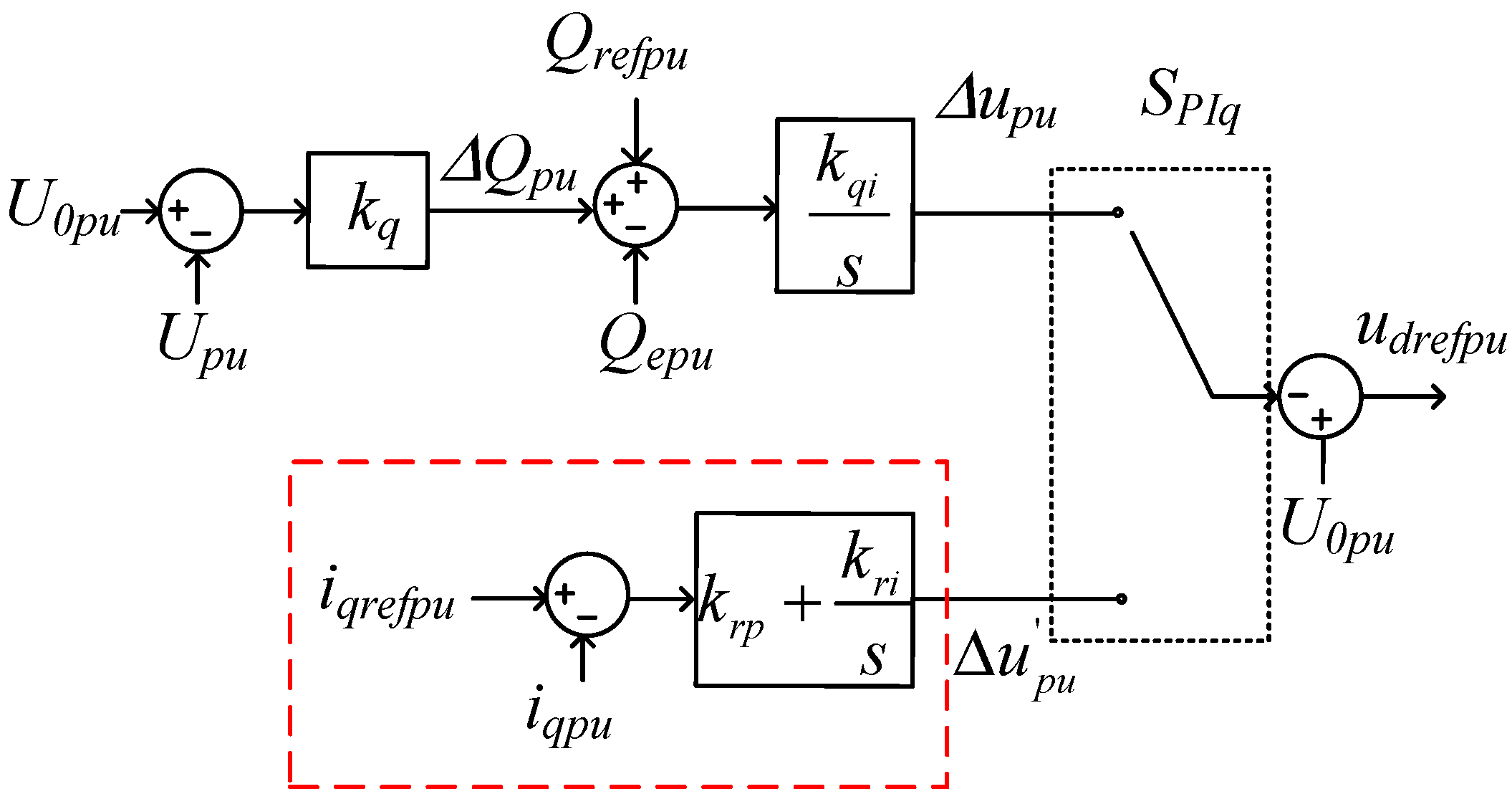

2.2. Reactive-Voltage Control Strategy

2.3. Selection of the dq-Axis Current Reference

3. Simulation Results

3.1. Test System Parameters

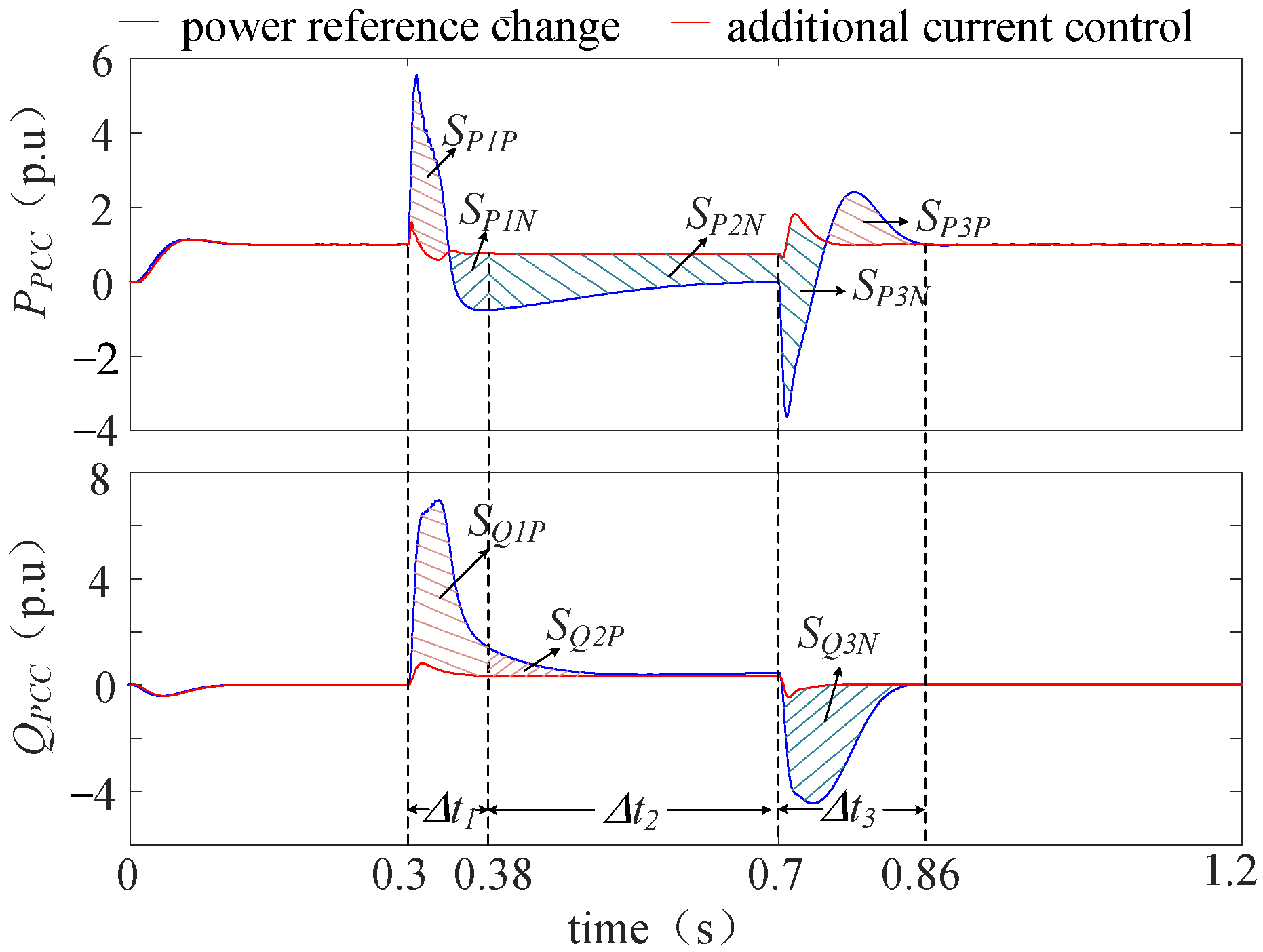

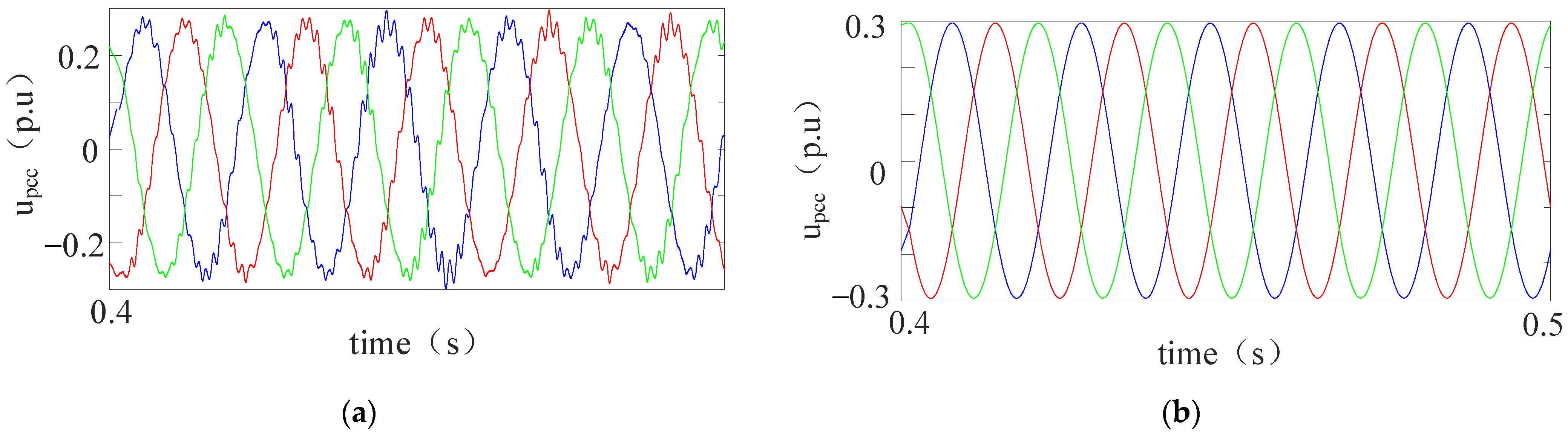

3.2. Comparative Analysis between Additional Current Control and Power Reference Changing

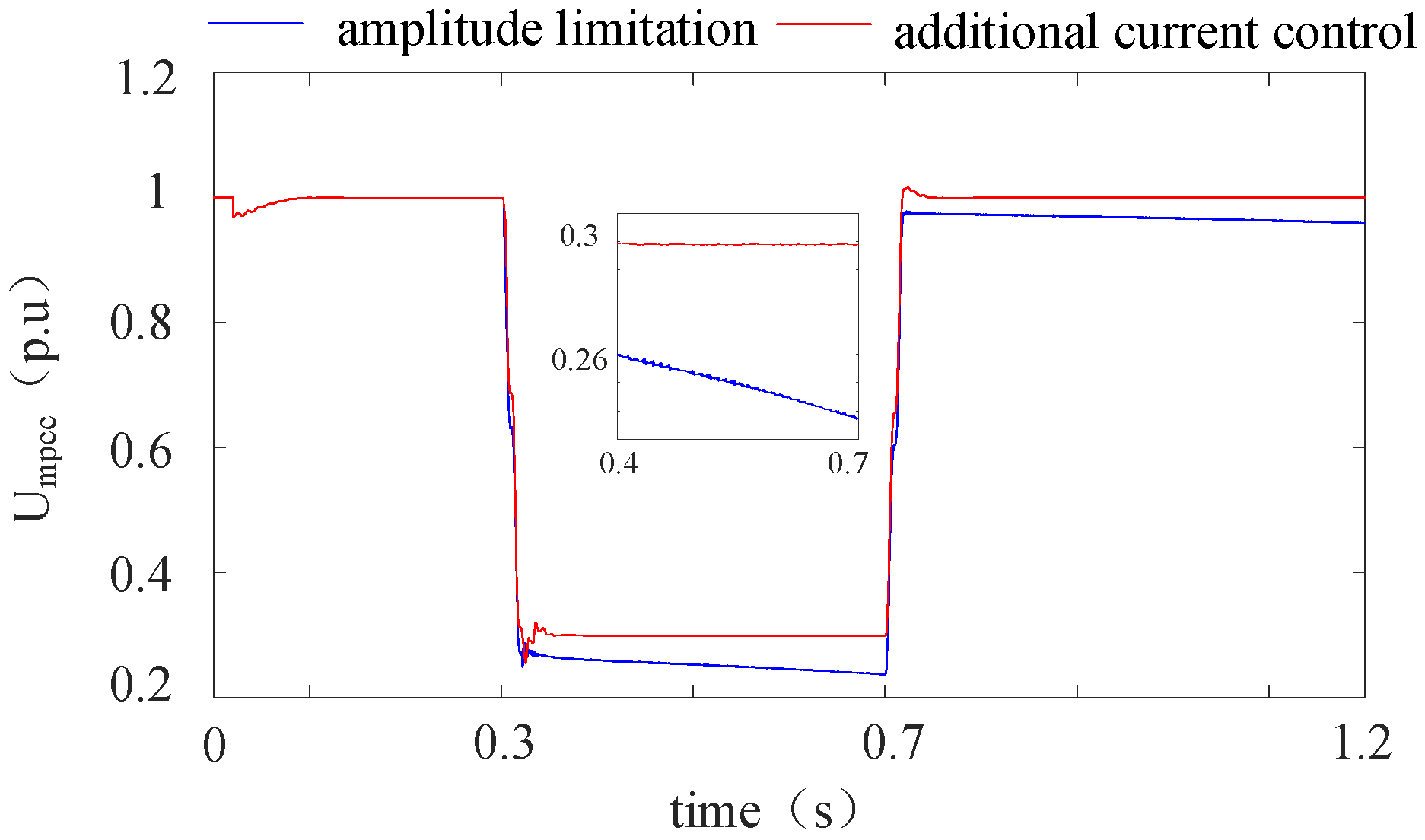

3.3. Comparative Analysis between Additional Current Control and Amplitude Limitation

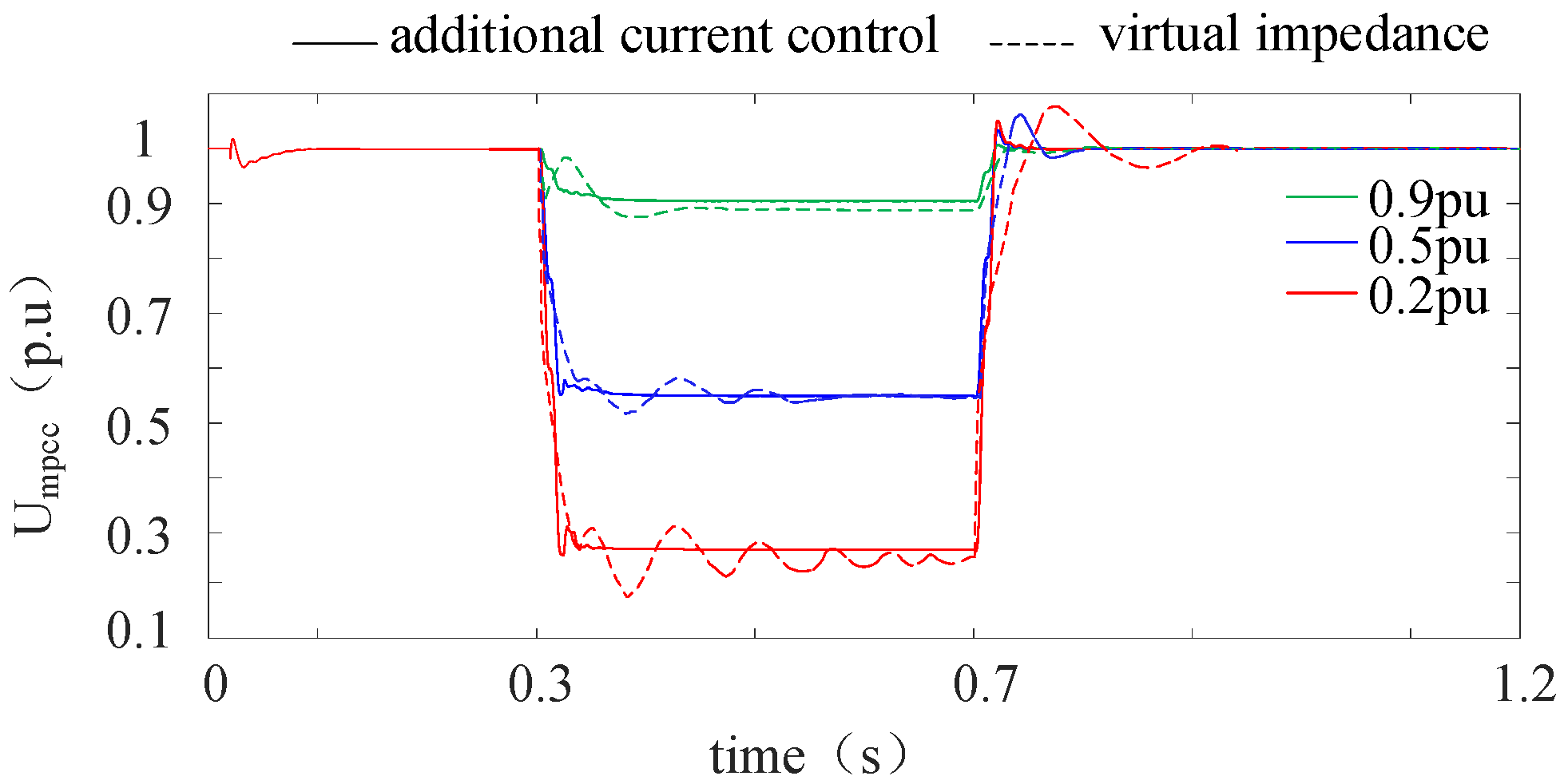

3.4. Comparative Analysis between Additional Current Control and Virtual Impedance

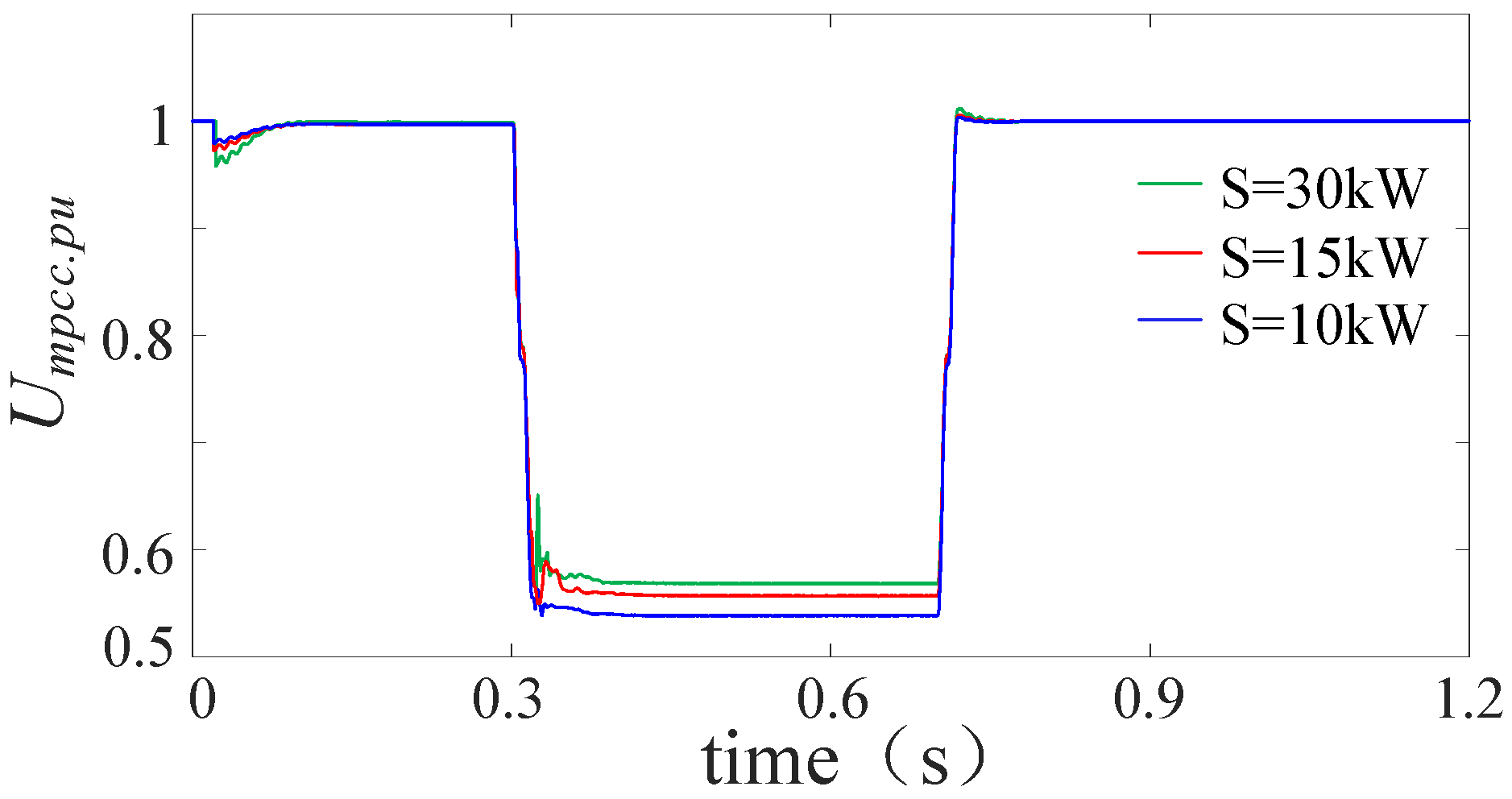

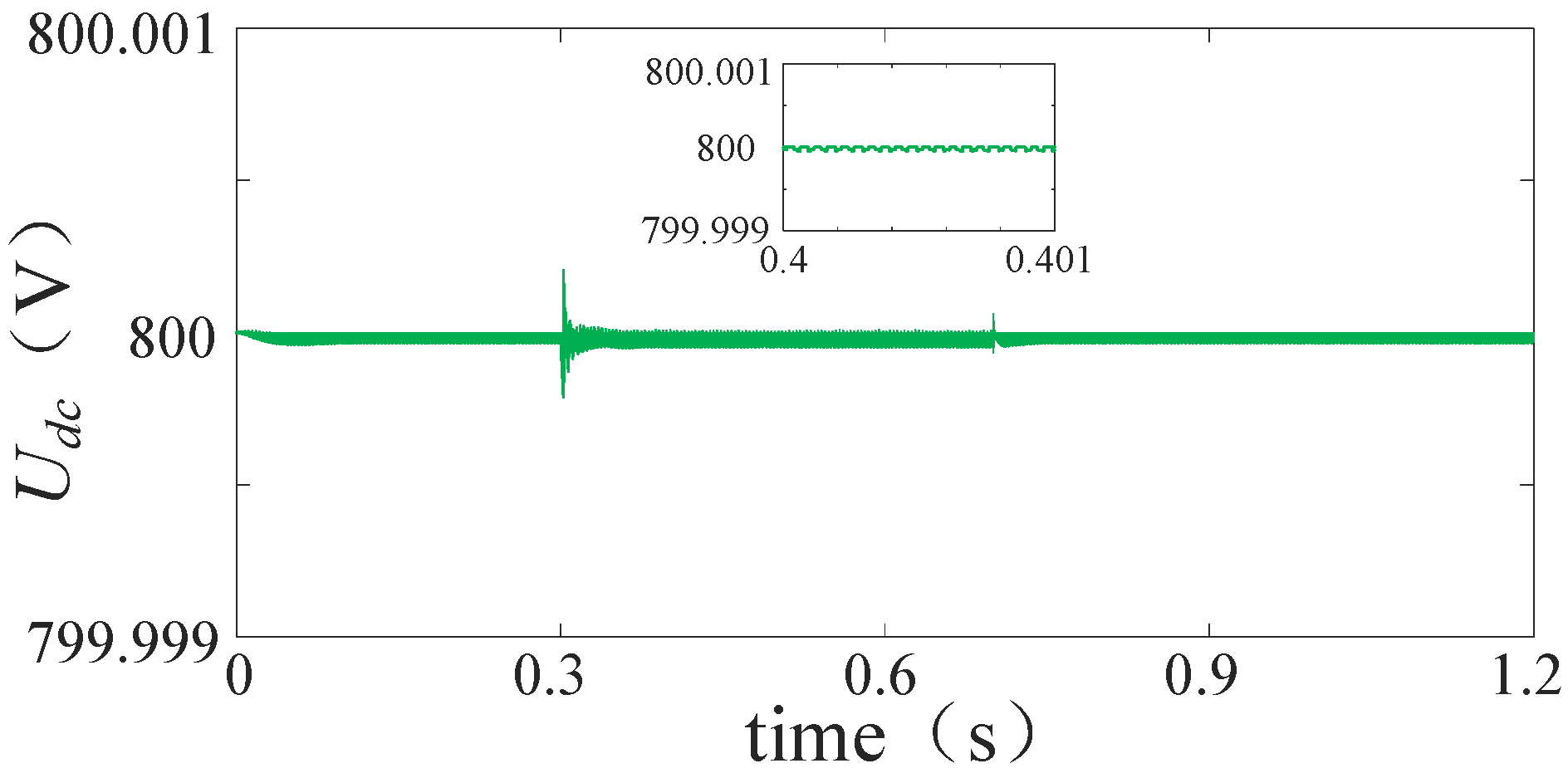

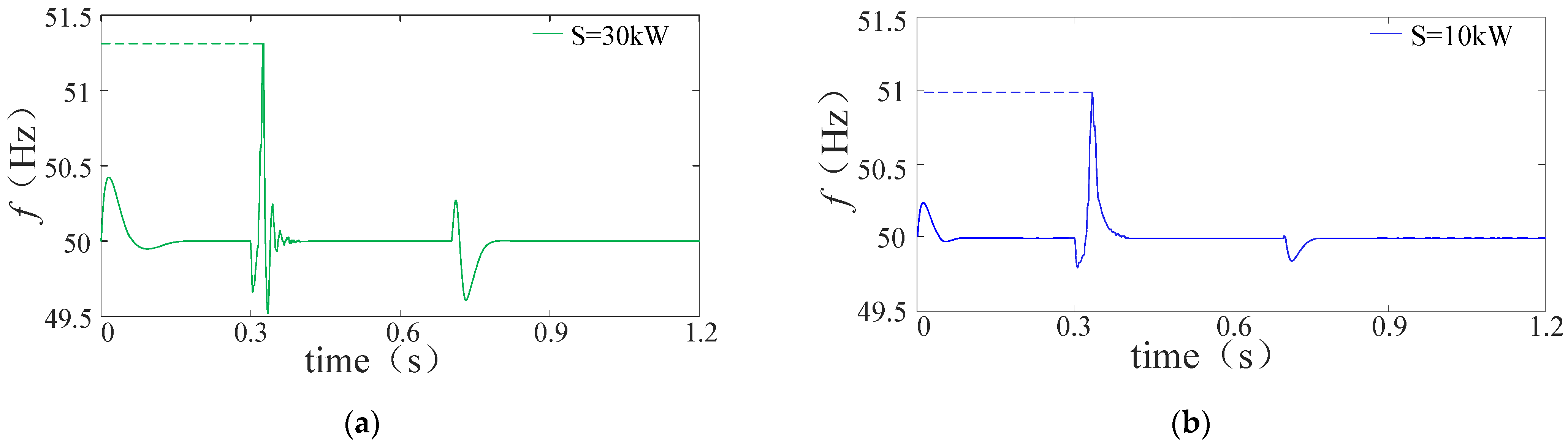

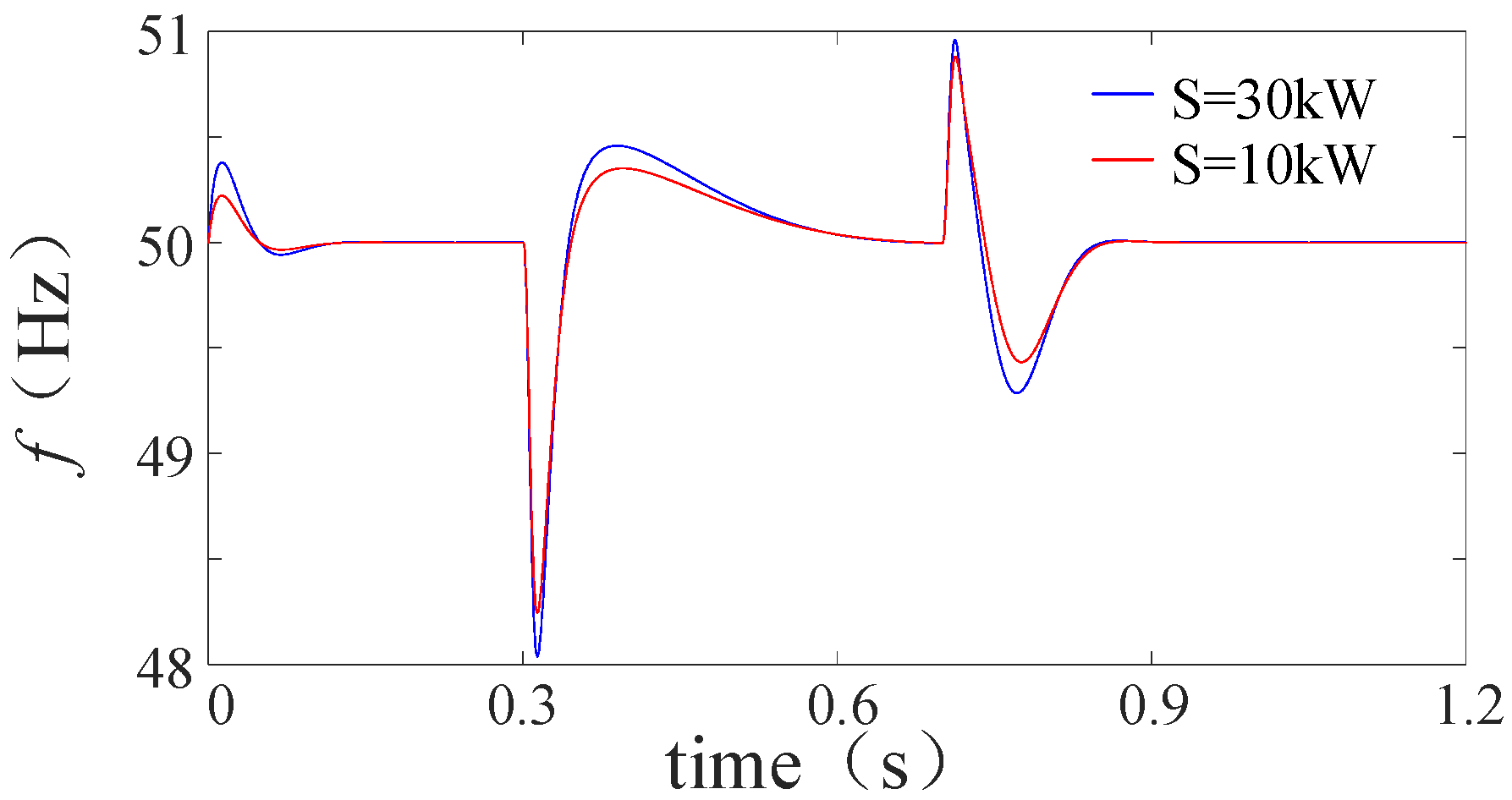

3.5. Current Limitation Effect under Different Capacities

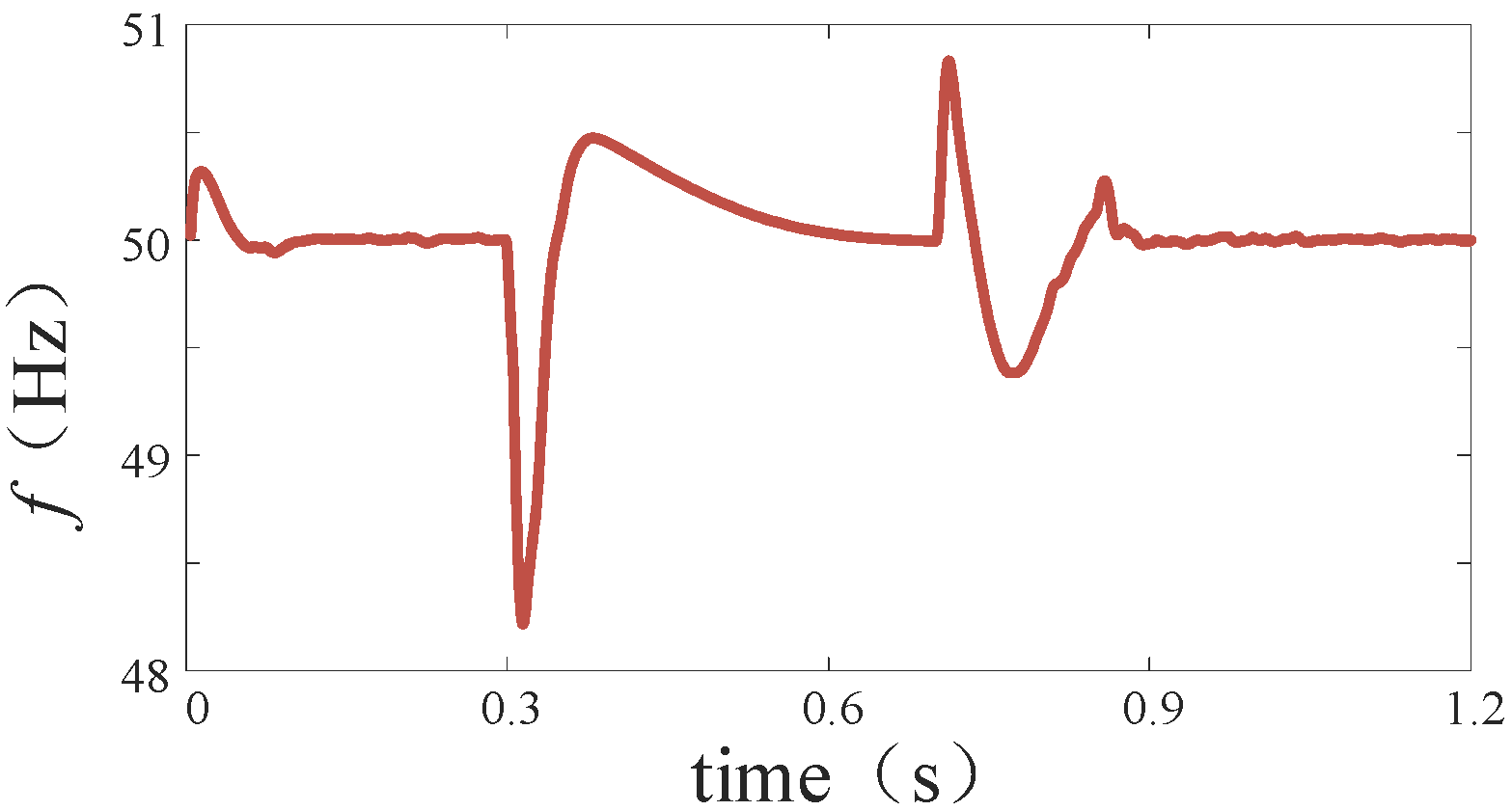

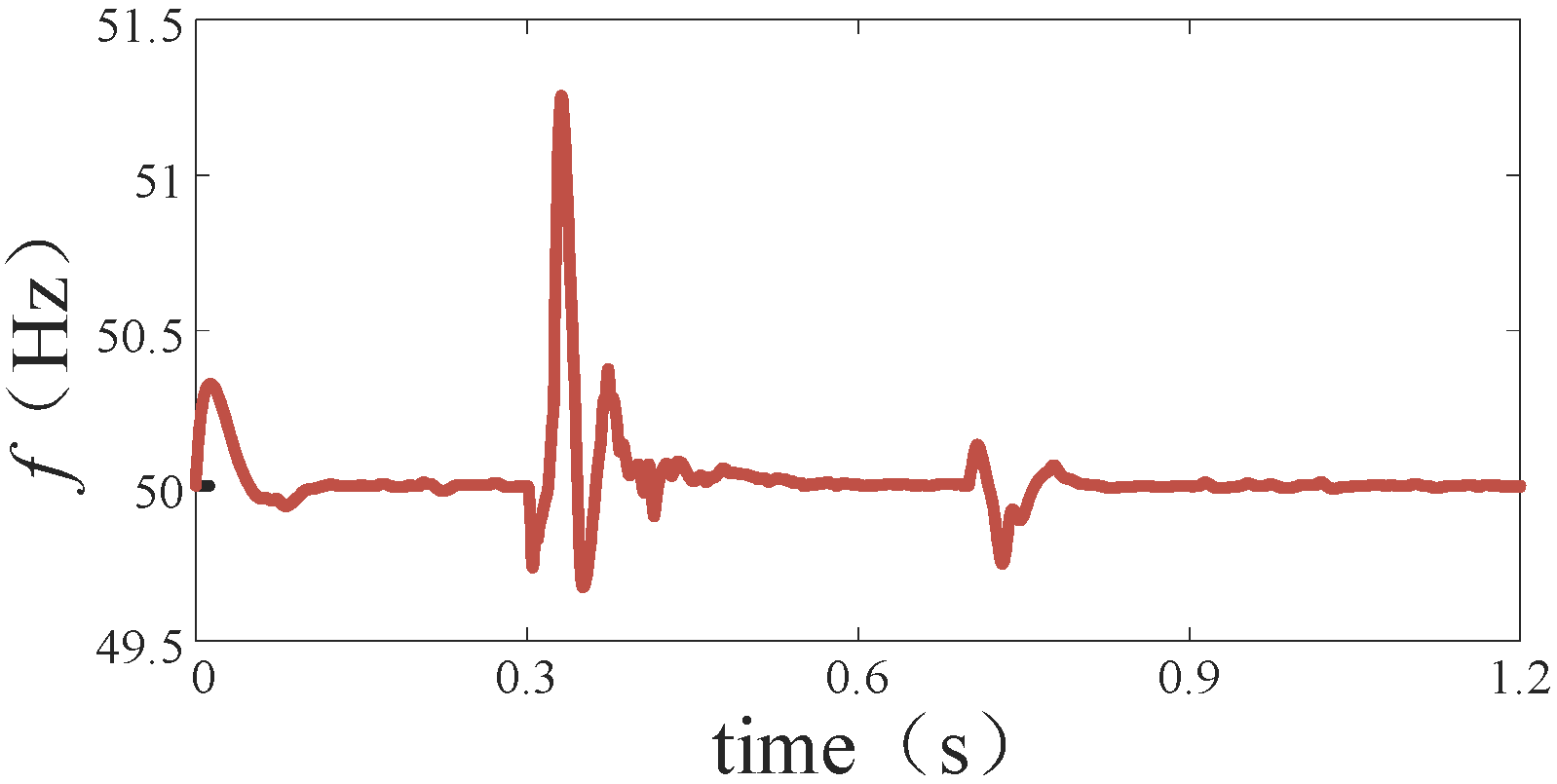

- Fast response speed: the proposed control can achieve stability within 0.1 s after a fault.

- The control method proposed in this paper can maintain the frequency deviation within 1.5 Hz compared to a frequency change of 2 Hz under a conventional controller.

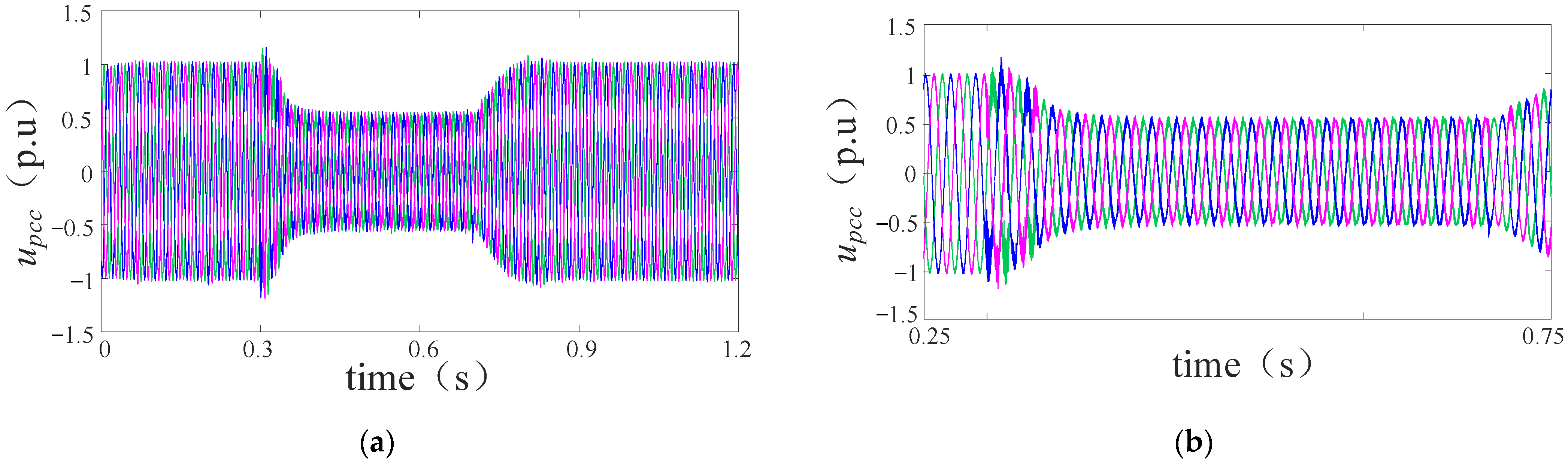

- The proposed control can promote voltage stabilization faster than a conventional controller and keep the voltage at a higher level. Hence, the proposed control can provide uninterrupted voltage support for the grid and facilitate fault recovery.

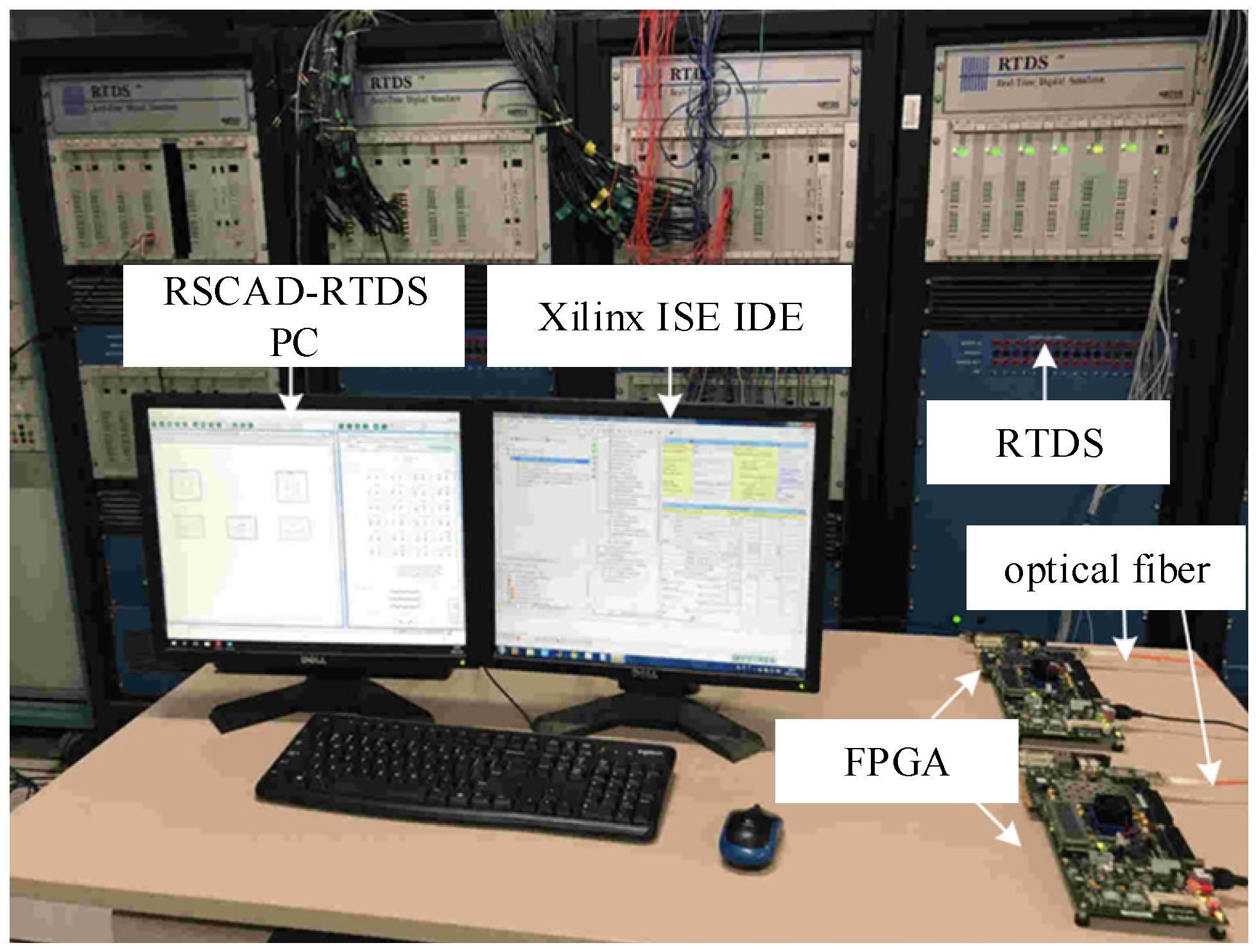

4. HIL Validation

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

Appendix A

| Generator G2 | Sn/kVA | 400 |

| UN/V | 380 | |

| fN/Hz | 50 | |

| Kp | 0.045 | |

| J | 3.6 | |

| Dp | 0.41 | |

| Generator G3 | Sn/kVA | 400 |

| UN/V | 380 | |

| fN/Hz | 50 | |

| Kp | 0.045 | |

| J | 3.6 | |

| Dp | 0.41 |

| R (Ω) | L (mH) | |

|---|---|---|

| L1 | 0.45 | 0.9 |

| L2 | 0.62 | 1.24 |

| L3 | 0.55 | 1.1 |

| L4 | 0.25 | 0.5 |

| L5 | 0.3 | 0.6 |

| L6 | 0.35 | 0.7 |

| S1 | 0.5 | |

| S2 | 0.4 | |

| S3 | 0.4 | |

| S4 | 0.3 | |

| S5 | 0.3 | |

| S6 | 0.5 |

References

- Huang, L.B.; Xin, H.H.; Ju, P.; Hu, J.B. Synchronization Stability Analysis and Unified Synchronization Control Structure of Grid-connected Power Electronic Devices. Electr. Power Autom. Equip. 2020, 40, 10–25. [Google Scholar]

- Cen, Y.; Huang, M.; Zha, X.M. The Transient Response Analysis of SRF-PLL under the Unbalance Grid Voltage Sag. Trans. China Electrotech. Soc. 2016, 31, 28–38. [Google Scholar]

- Pattabiraman, D.; Lasseter, R.H.; Jahns, T.M. Comparison of Grid Following and Grid Forming Control for a High Inverter Penetration Power System. In Proceedings of the 2018 IEEE Power & Energy Society General Meeting (PESGM), Portland, OR, USA, 5–10 August 2018; pp. 1–5. [Google Scholar]

- Rosso, R.; Wang, X.; Liserre, M.; Lu, X.; Engelken, S. Grid-Forming Converters: Control Approaches, Grid-Synchronization, and Future Trends—A Review. IEEE Open J. Ind. Appl. 2021, 2, 93–109. [Google Scholar] [CrossRef]

- Ackermann, T.; Prevost, T.; Vittal, V.; Roscoe, A.J.; Matevosyan, J.; Miller, N. Paving the Way: A Future Without Inertia Is Closer Than You Think. IEEE Power Energy Mag. 2017, 15, 61–69. [Google Scholar] [CrossRef]

- Erickson, M.J. Improved Power Control of Inverter Sources in Mixed-Source Micro-Grids; The University of Wisconsin-Madison: Madison, WI, USA, 2012. [Google Scholar]

- Shuai, Z.; Huang, W.; Shen, C.; Ge, J.; Shen, Z.J. Characteristics and Restraining Method of Fast Transient Inrush Fault Currents in Synchronverters. IEEE Trans. Ind. Electron. 2017, 64, 7487–7497. [Google Scholar] [CrossRef]

- Taoufik, Q.; François, G.; Fréderic, C.; Guillaume, D.; Thibault, P.; Xavier, G. Critical Clearing Time Determination and Enhancement of Grid-Forming Converters Embedding Virtual Impedance as Current Limitation Algorithm. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 1050–1061. [Google Scholar]

- Qoria, T.; Gruson, F.; Colas, F.; Denis, G.; Prevost, T.; Guillaud, X.A. Current Limiting Strategy to Improve Fault Ride-Through of Inverter Interfaced Autonomous Micro-grids. IEEE Trans. Smart Grid 2017, 8, 2138–2148. [Google Scholar]

- Yu, M.; Huang, W.; Tai, N.; Zheng, X.; Wu, P.; Chen, W. Transient Stability Mechanism of Grid-connected Inverter-interfaced Distributed Generators Using Droop Control Strategy. Appl. Energy 2018, 210, 737–747. [Google Scholar] [CrossRef]

- Zhong, Q.C.; Konstantopoulos, G.C. Current-Limiting Droop Control of Grid-Connected Converters. IEEE Trans. Ind. Electron. 2017, 64, 5963–5973. [Google Scholar] [CrossRef]

- Paquette, A.D.; Divan, D.M. Virtual Impedance Current Limiting for Converters in Micro-grids with Synchronous Generators. IEEE Trans. Ind. Appl. 2015, 51, 1630–1638. [Google Scholar] [CrossRef]

- He, J.; Li, Y.W. Analysis, Design and Implementation of Virtual Impedance for Power Electronics Interfaced Distributed Generation. IEEE Trans. Ind. Appl. 2011, 47, 2525–2538. [Google Scholar] [CrossRef]

- Wang, X.M.; Wang, Y.B.; Liu, Y.T.; Liu, C.; Wang, S.J.; Hu, B. Low Voltage Ride Through Control Method of Actively Supported New Energy Unit Based on Virtual Reactance. Power Syst. Technol. 2022, 46, 4435–4444. [Google Scholar]

- Li, Y.W.; Vilathgamuwa, D.M.; Loh, P.C.; Blaabjerg, F. A Dual-Functional Medium Voltage Level DVR to Limit Downstream Fault Currents. IEEE Trans. Power Electron. 2007, 22, 1330–1340. [Google Scholar] [CrossRef]

- Afshari, E.; Moradi, G.R.; Rahimi, R.; Farhangi, B.; Yang, Y.; Blaabjerg, F.; Farhangi, S. Control Strategy for Three-Phase Grid-Connected PV Converters Enabling Current Limitation Under Unbalanced Faults. IEEE Trans. Ind. Electron. 2017, 64, 8908–8918. [Google Scholar] [CrossRef]

- Taul, M.G.; Wang, X.; Davari, P.; Blaabjerg, F. Current Limiting Control with Enhanced Dynamics of Grid-Forming Converters During Fault Conditions. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 1062–1073. [Google Scholar] [CrossRef]

- Wu, H.; Wang, X. Transient Stability Analysis of Grid-connected Converter System Considering Frequency Disturbance of Power Grid. Autom. Electr. Power Syst. 2021, 45, 78–84. [Google Scholar]

- Xi, L.Y.; Wang, J.F.; Hou, C.C.; Qiu, Z.L. Design of phase locked loop based on third-order general-integrator. Power Syst. Prot. Control 2016, 44, 184–189. [Google Scholar]

- Glöckler, C.; Duckwitz, D.; Welck, F. Virtual Synchronous Machine Control with Virtual Resistor for Enhanced Short Circuit Capability. In Proceedings of the 2017 IEEE PES Innovative Smart Grid Technologies Conference Europe (ISGT-Europe), Turin, Italy, 26–29 September 2017; pp. 1–6. [Google Scholar]

- Welck, F.; Duckwitz, D.; Gloeckler, C. Influence of Virtual Impedance on Short Circuit Performance of Virtual Synchronous Machines in the 9-Bus System. In Proceedings of the NEIS 2017, Conference on Sustainable Energy Supply and Energy Storage Systems, Hamburg, Germany, 21–22 September 2017; pp. 1–7. [Google Scholar]

- Gkountaras, A.; Dieckerhoff, S.; Sezi, T. Evaluation of Current Limiting Methods for Grid Forming Converters in Medium Voltage Micro-grids. In Proceedings of the 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, Canada, 20–24 September 2015; pp. 1223–1230. [Google Scholar]

- Zhong, Q.C. Virtual Synchronous Machines and Autonomous Power Systems. Proc. CSEE 2017, 37, 336–348. [Google Scholar]

- Lan, Z.; Long, Y.; Zeng, J.H.; Tu, C.M.; Xiao, F.; Guo, Q. Transient Power Oscillation Suppression Strategy of Virtual Synchronous Generator Considering Overshoot. Autom. Electr. Power Syst. 2022, 46, 131–141. [Google Scholar]

- Remon, D.; Cantarellas, A.M.; Rakhshani, E.; Candela, I.; Rodriguez, P. An Active Power Synchronization Control Loop for Grid-connected Converters. In Proceedings of the 2014 IEEE PES General Meeting|Conference & Exposition, National Harbor, MD, USA, 27–31 July 2014; pp. 1–5. [Google Scholar]

- Rodríguez, P.; Citro, C.; Candela, J.I.; Rocabert, J.; Luna, A. Flexible Grid Connection and Islanding of SPC-based PV Power Converters. IEEE Trans. Ind. Appl. 2018, 54, 2690–2702. [Google Scholar] [CrossRef]

- Zhang, Z.K.; Huang, Z.; Chi, Y.N.; Wang, J.; Li, Y. Explanation of Technical Rule for Connecting Offshore Wind Farm into Power Grid. Smart Grid. 2016, 4, 345–350. [Google Scholar]

| Symbol/Unit | Quantity |

|---|---|

| f0/Hz | 50 |

| U0/V | 380 |

| Vdc/V | 800 |

| Lf/mH | 1.5 |

| Cf/uF | 30 |

| Lg/H | 1 |

| RL/Ω | 0.3 |

| LL/mH | 0.4 |

| Sn/kVA | 15 |

| Pref0/kW | 15 |

| Qref/kVar | 0 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liu, C.; Xi, J.; Hao, Q.; Li, J.; Wang, J.; Dong, H.; Su, C. Grid-Forming Converter Overcurrent Limiting Strategy Based on Additional Current Loop. Electronics 2023, 12, 1112. https://doi.org/10.3390/electronics12051112

Liu C, Xi J, Hao Q, Li J, Wang J, Dong H, Su C. Grid-Forming Converter Overcurrent Limiting Strategy Based on Additional Current Loop. Electronics. 2023; 12(5):1112. https://doi.org/10.3390/electronics12051112

Chicago/Turabian StyleLiu, Chongru, Jiahui Xi, Qi Hao, Jufeng Li, Jinyuan Wang, Haoyun Dong, and Chenbo Su. 2023. "Grid-Forming Converter Overcurrent Limiting Strategy Based on Additional Current Loop" Electronics 12, no. 5: 1112. https://doi.org/10.3390/electronics12051112

APA StyleLiu, C., Xi, J., Hao, Q., Li, J., Wang, J., Dong, H., & Su, C. (2023). Grid-Forming Converter Overcurrent Limiting Strategy Based on Additional Current Loop. Electronics, 12(5), 1112. https://doi.org/10.3390/electronics12051112