Modified RPWM Strategy Based on Level-Shifted Random Carrier and Power Balance to Reduce the PWM Voltage Noise in Three-Phase CHB Inverters

Abstract

:1. Introduction

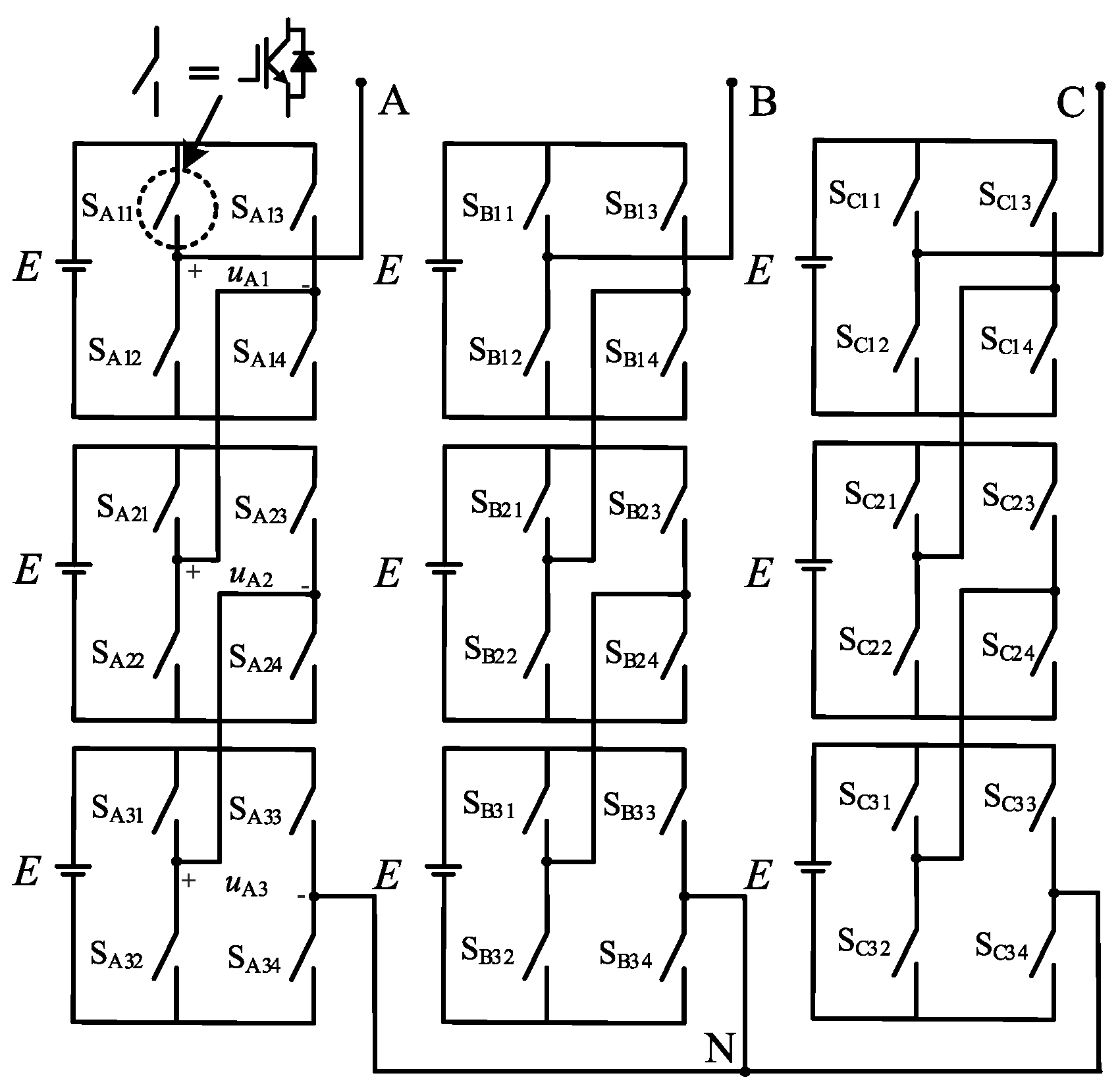

2. Introduction of the PB-RPWM Strategy

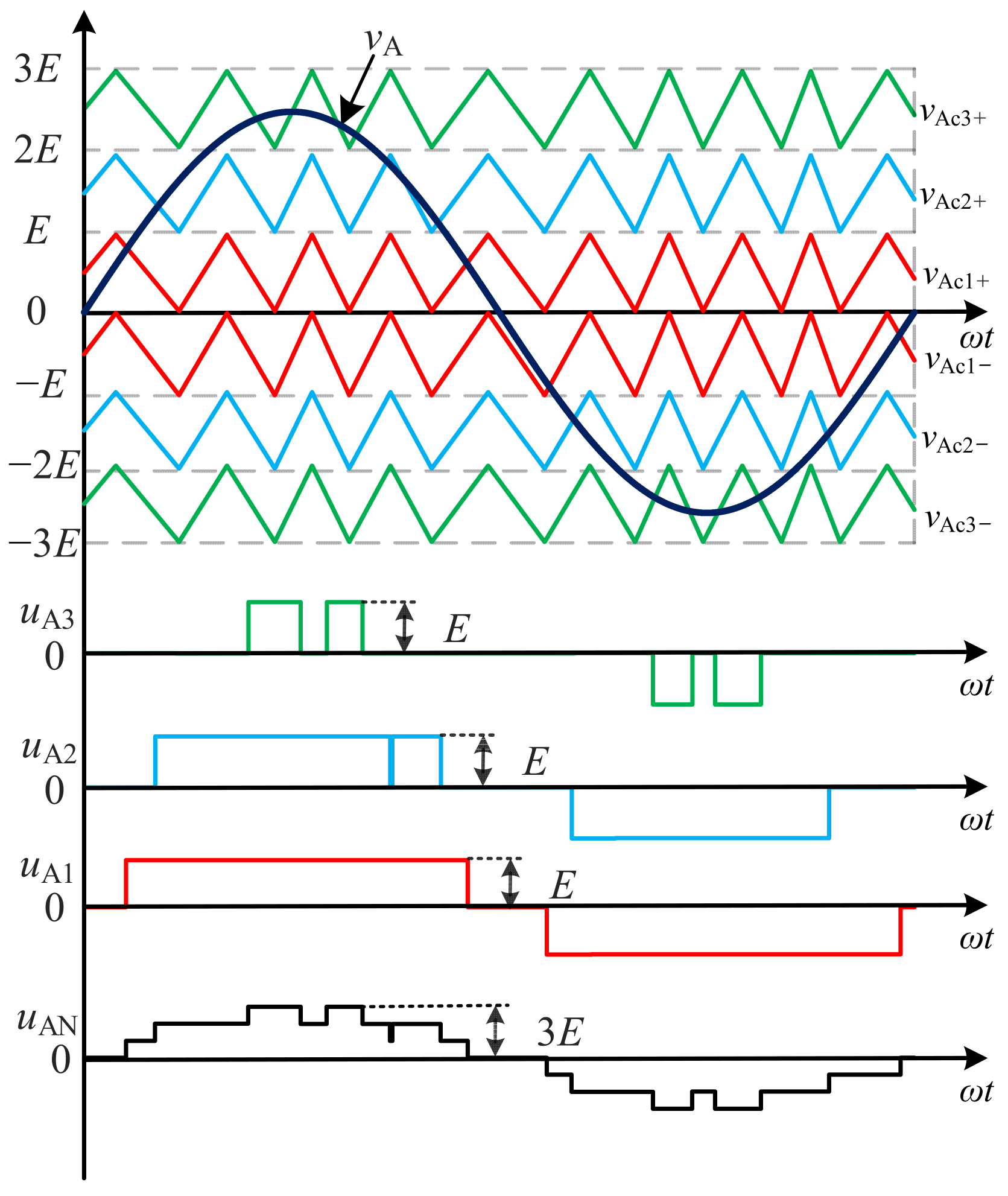

2.1. PWM Voltage Noise Reduction

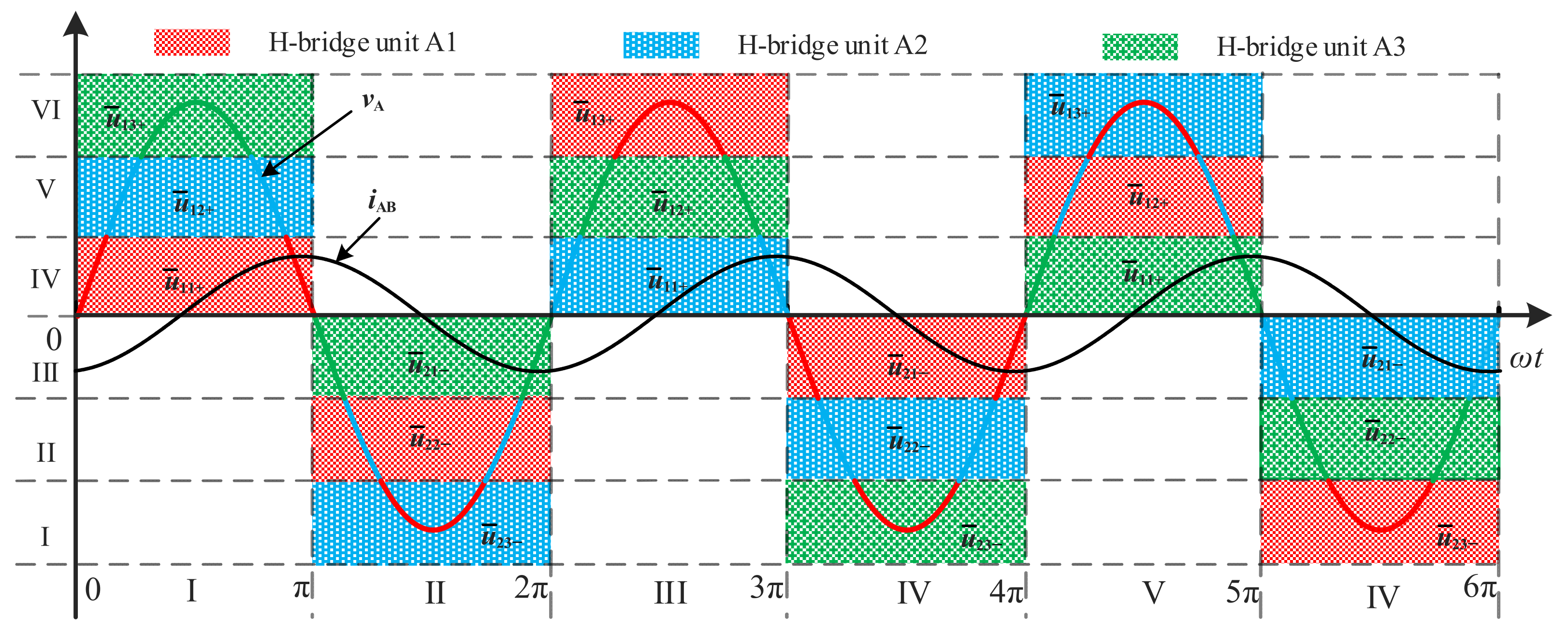

2.2. Power Balance Optimization

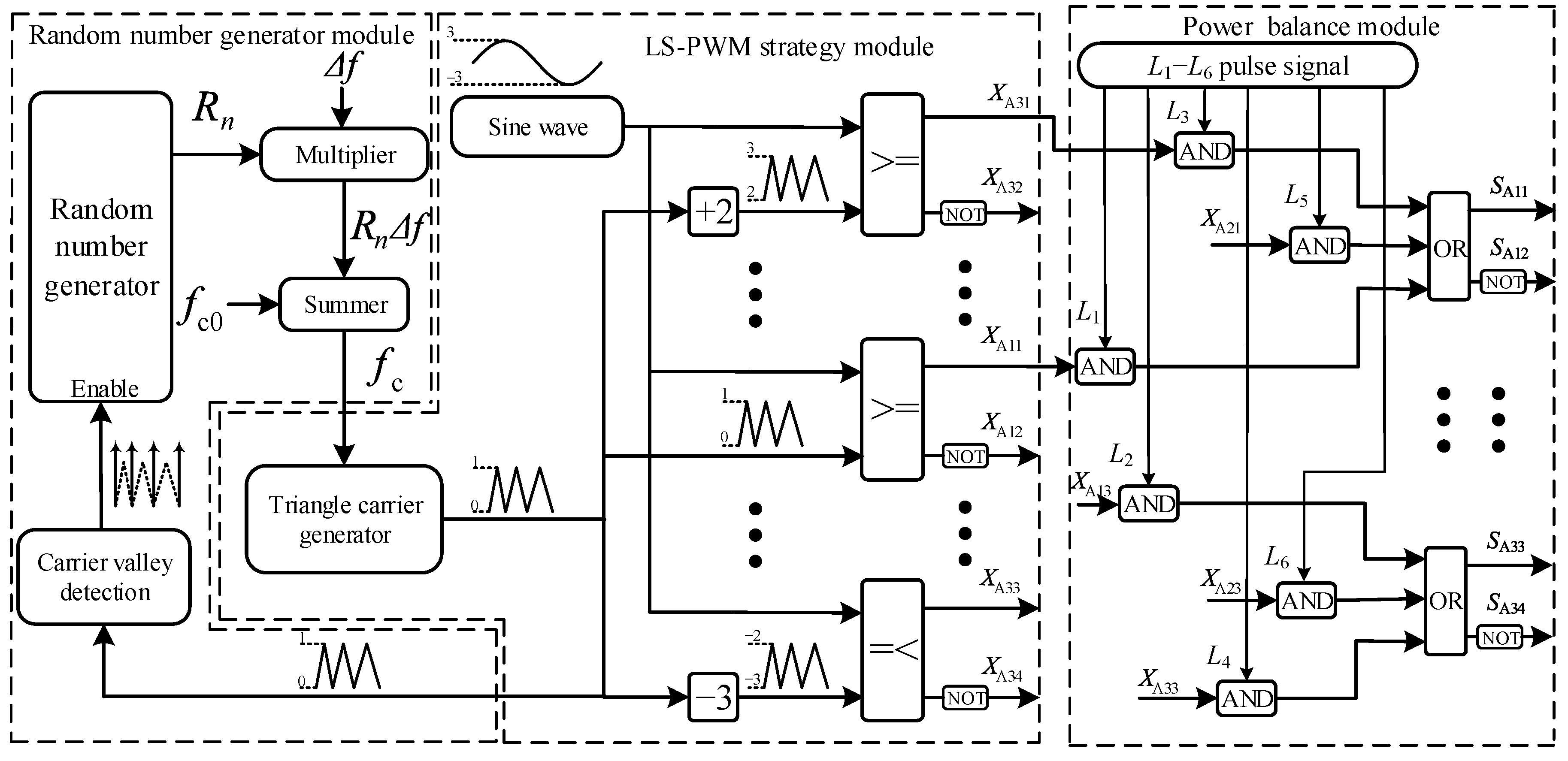

2.3. Digital Implementation of the PB-RPWM Strategy

3. Simulation and Contrast

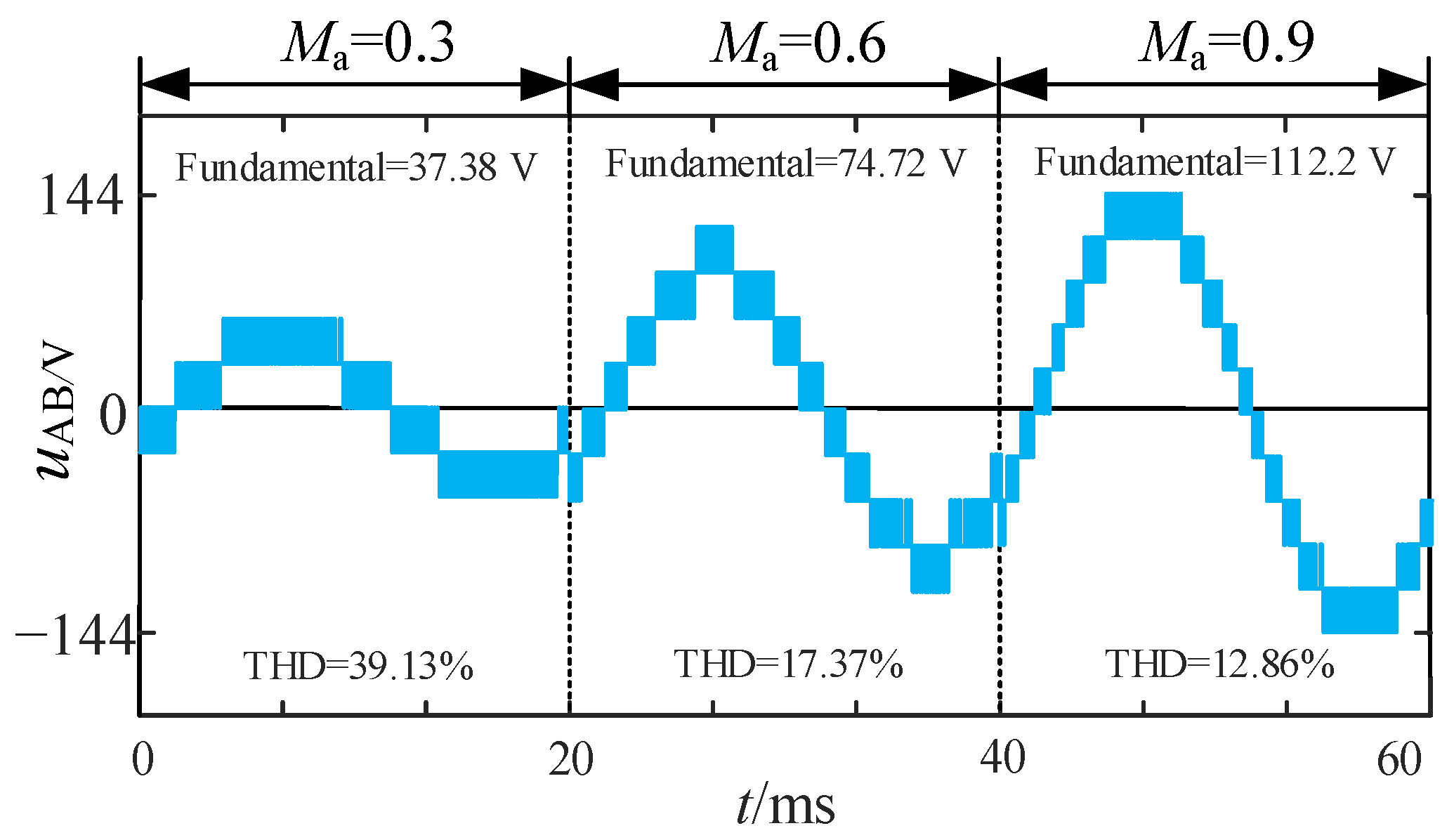

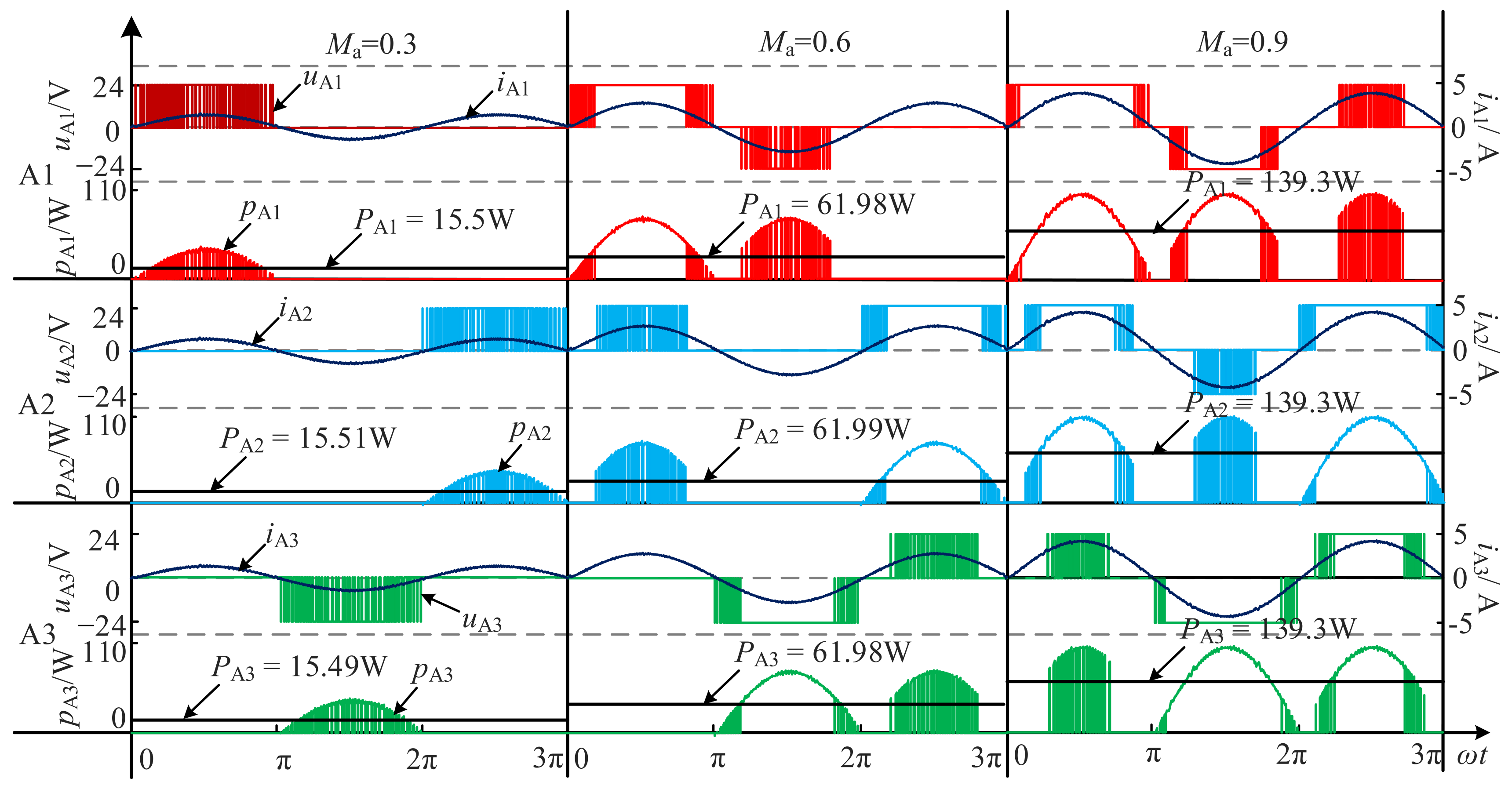

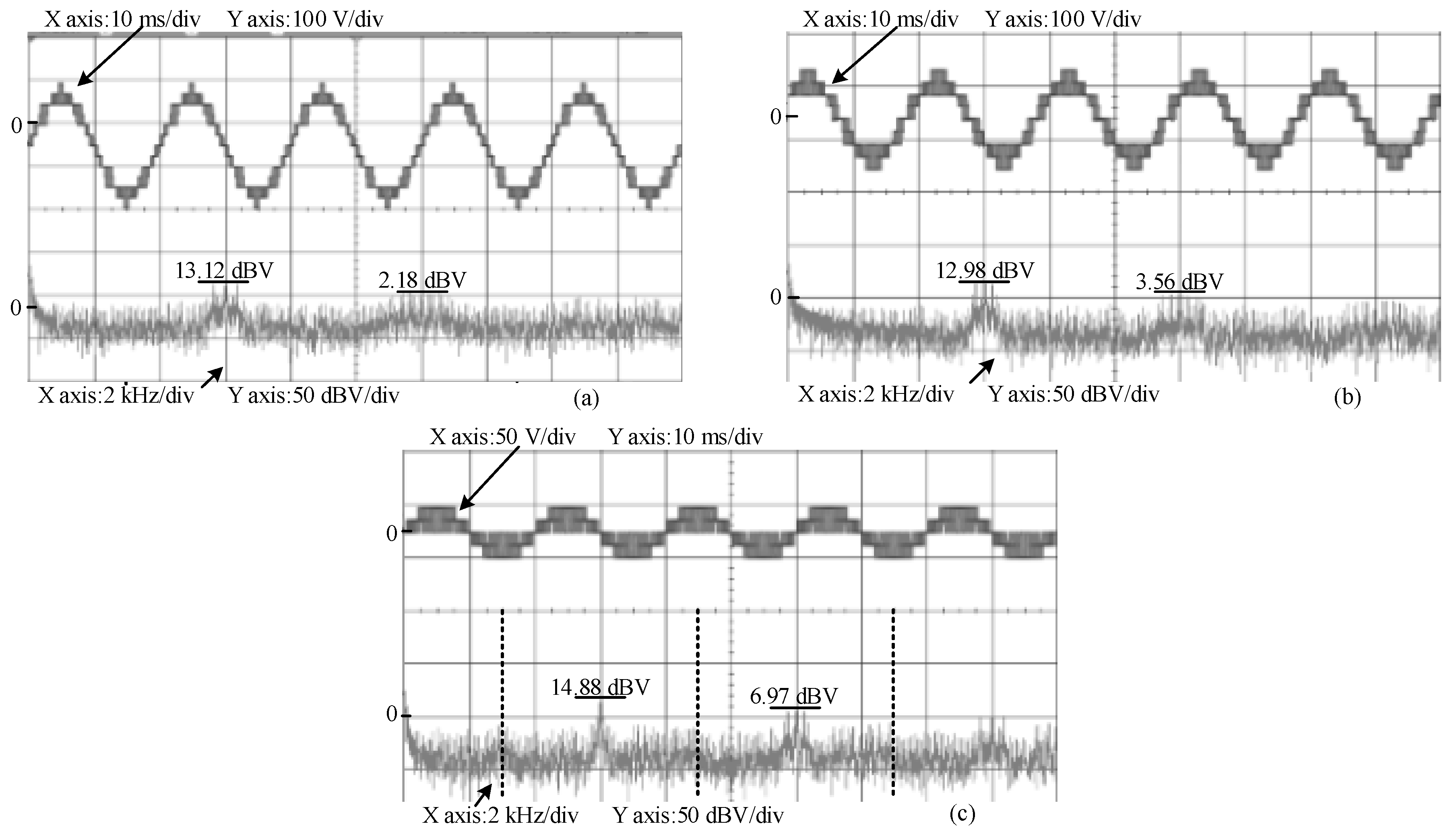

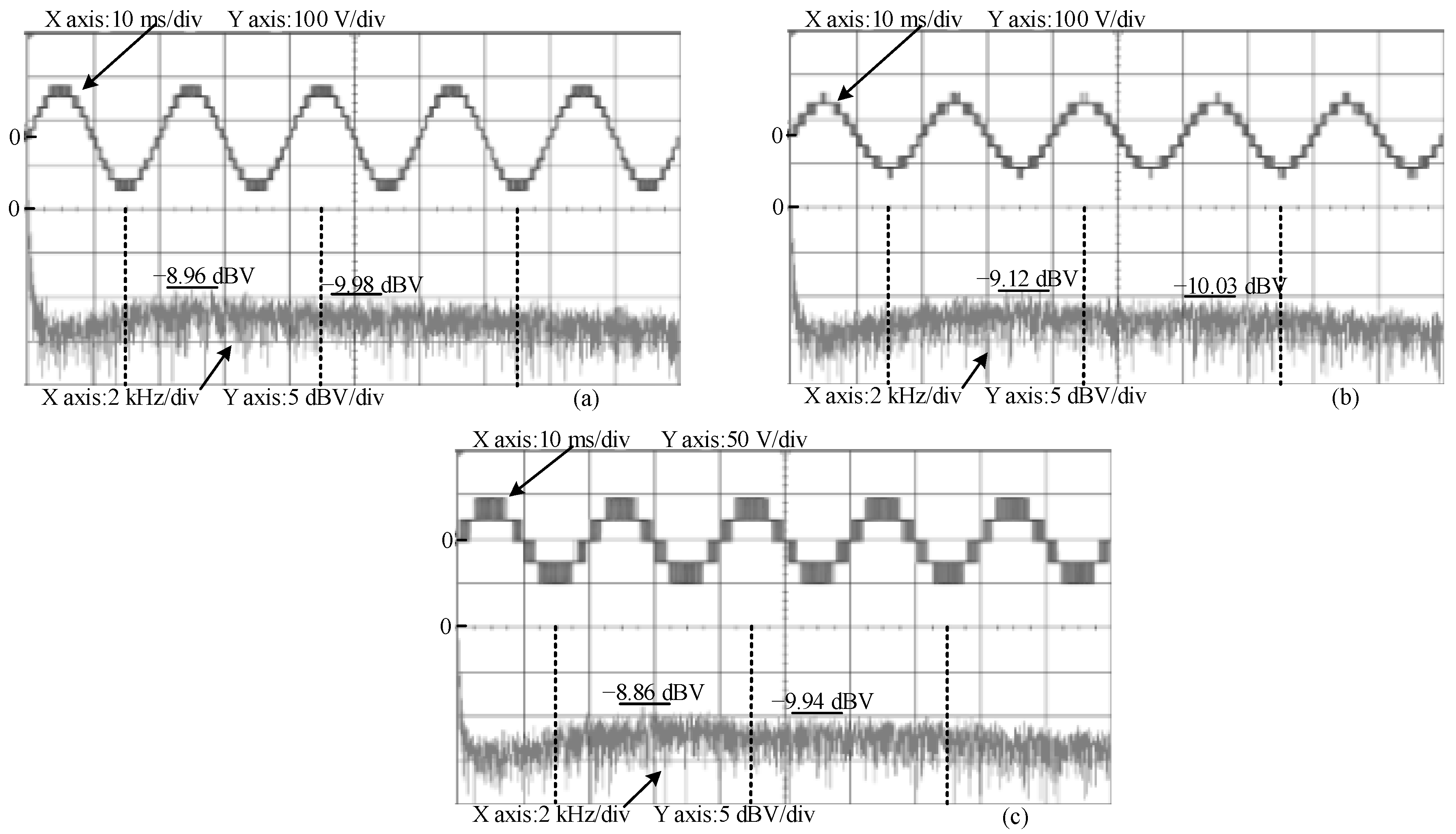

3.1. Characteristics of the PB-RPWM Strategy

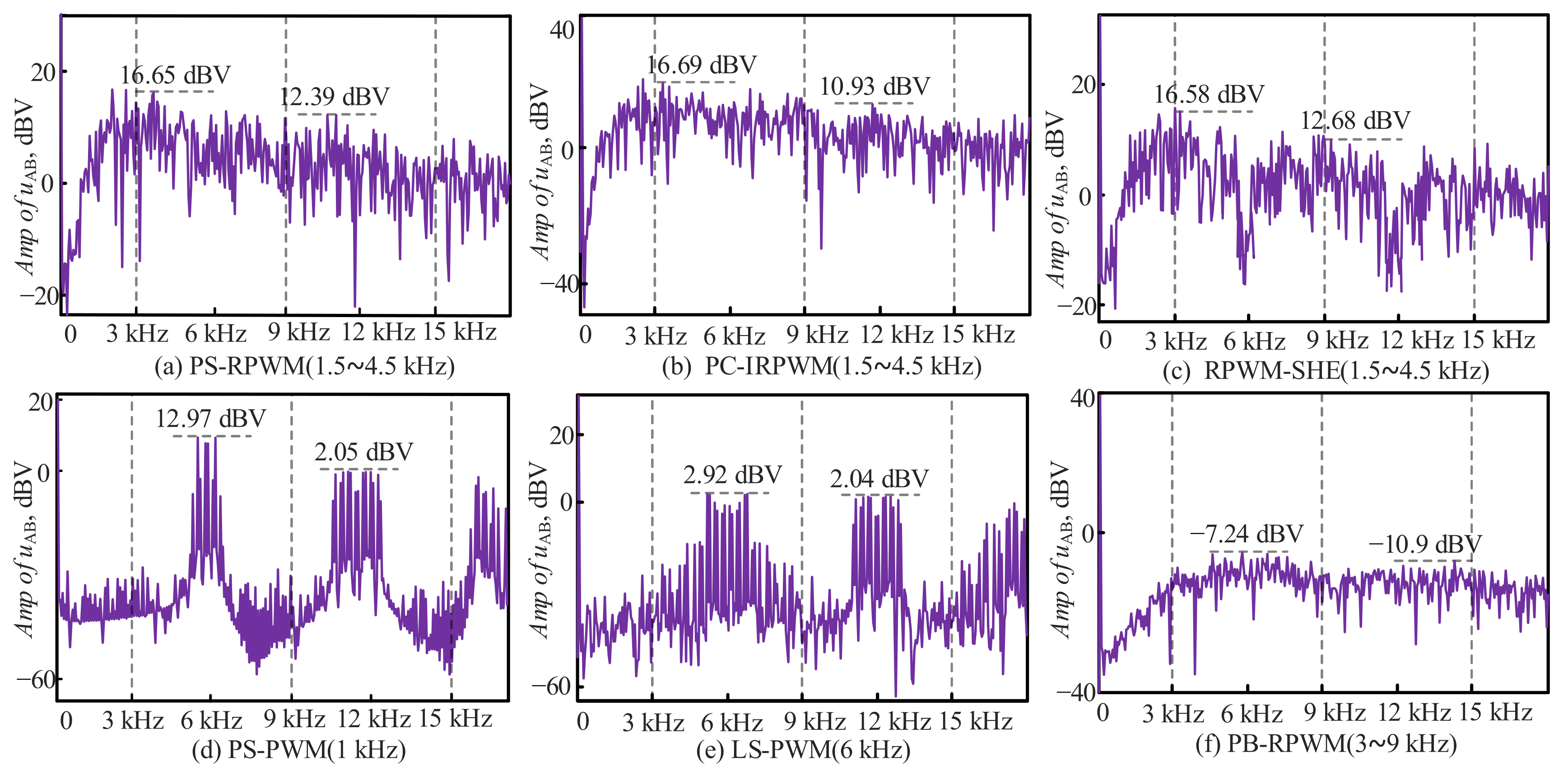

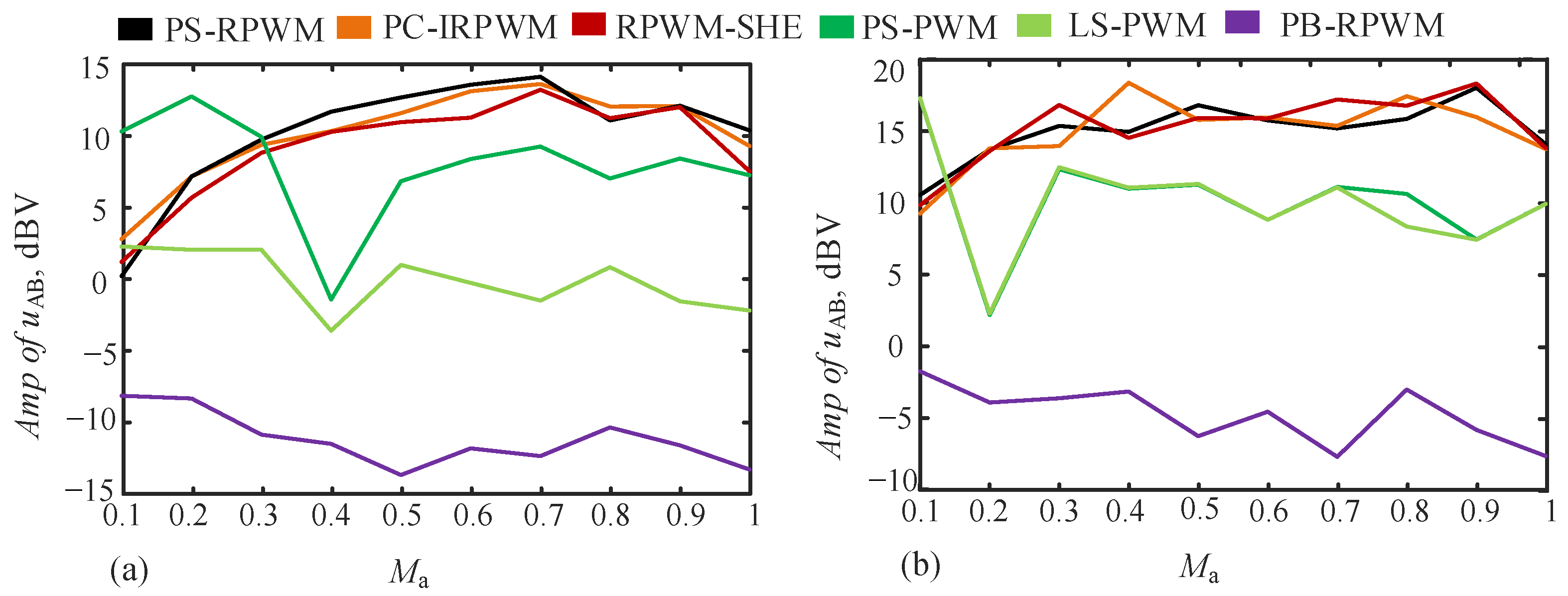

3.2. Contrast

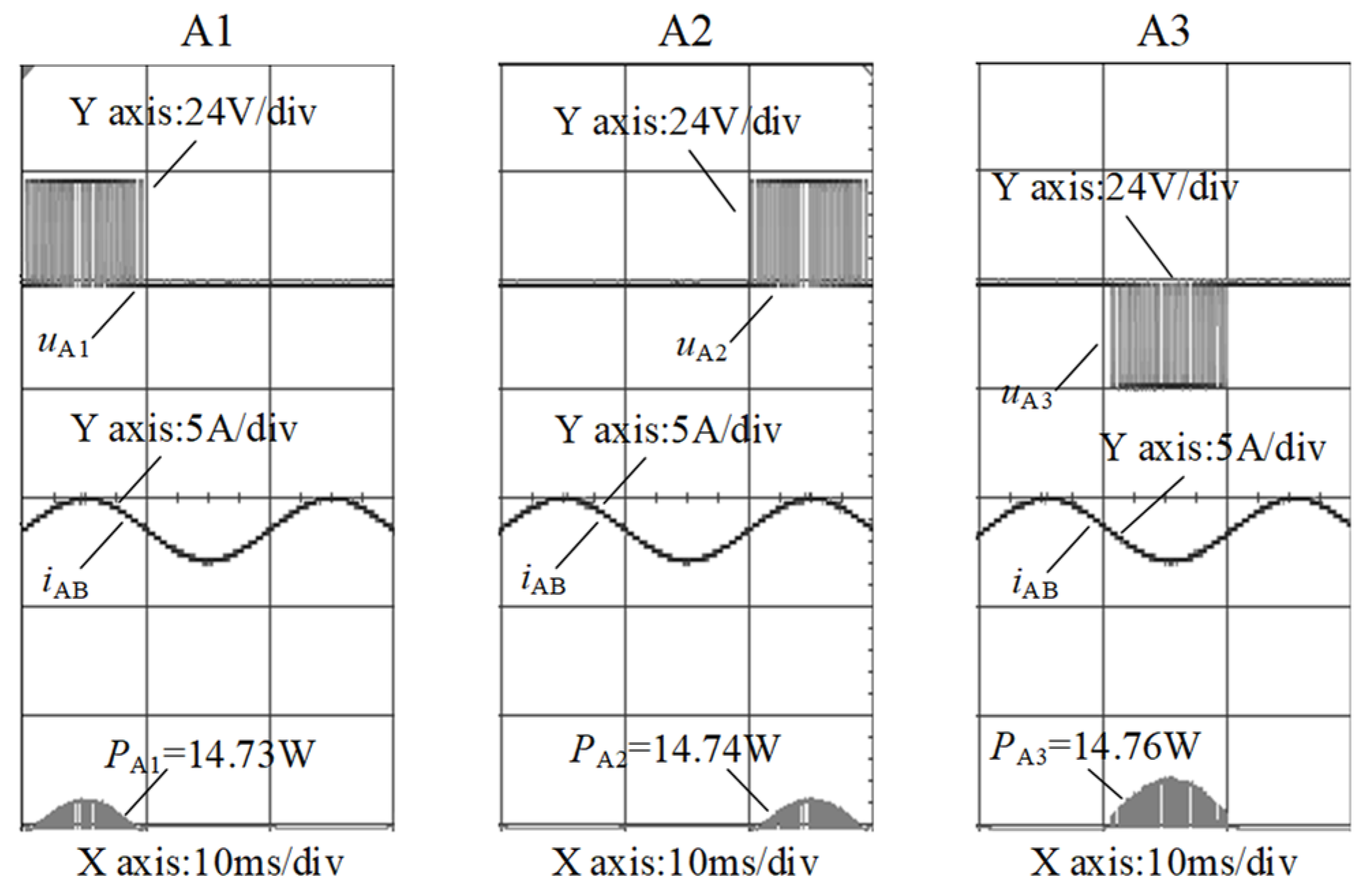

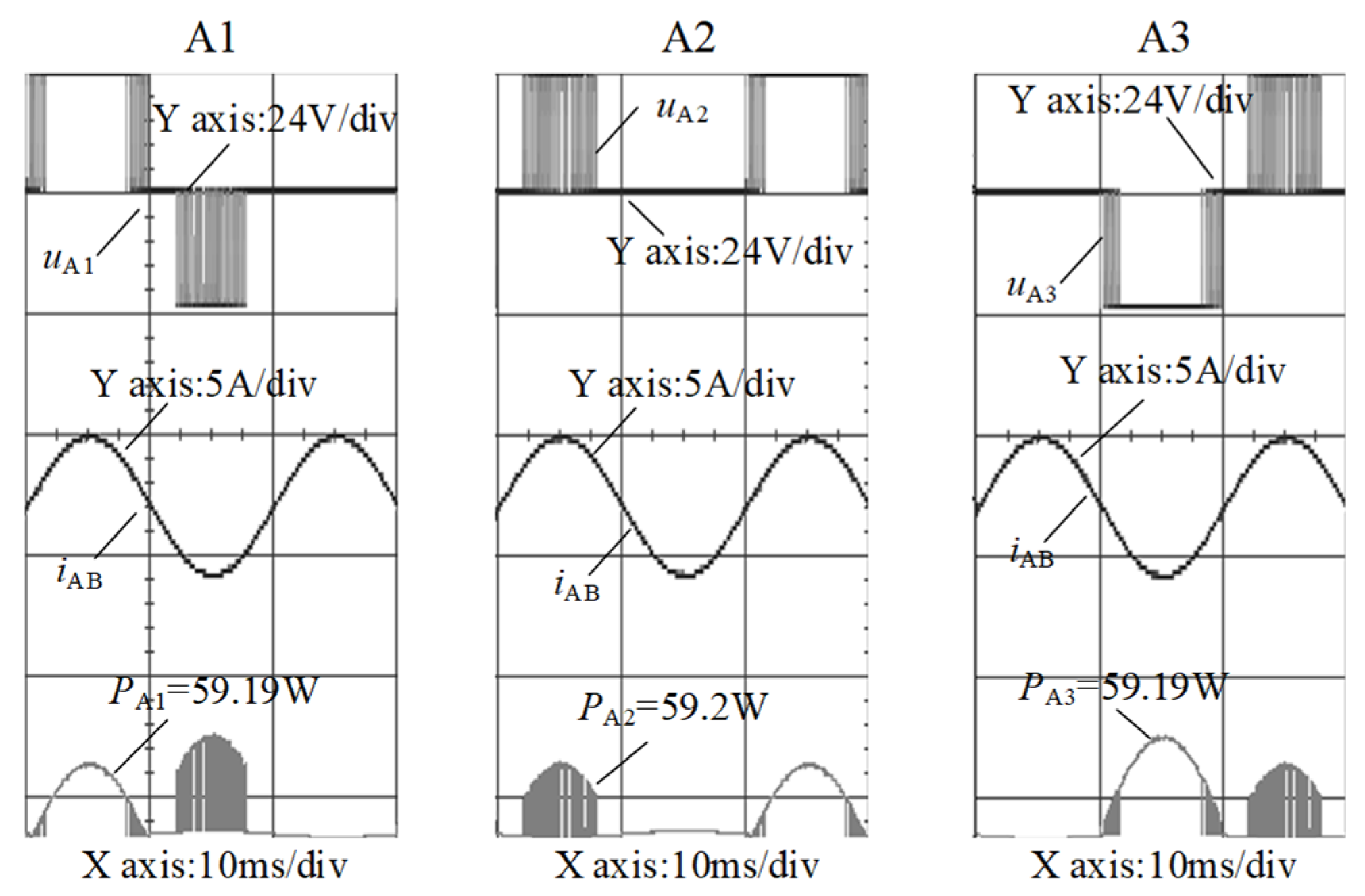

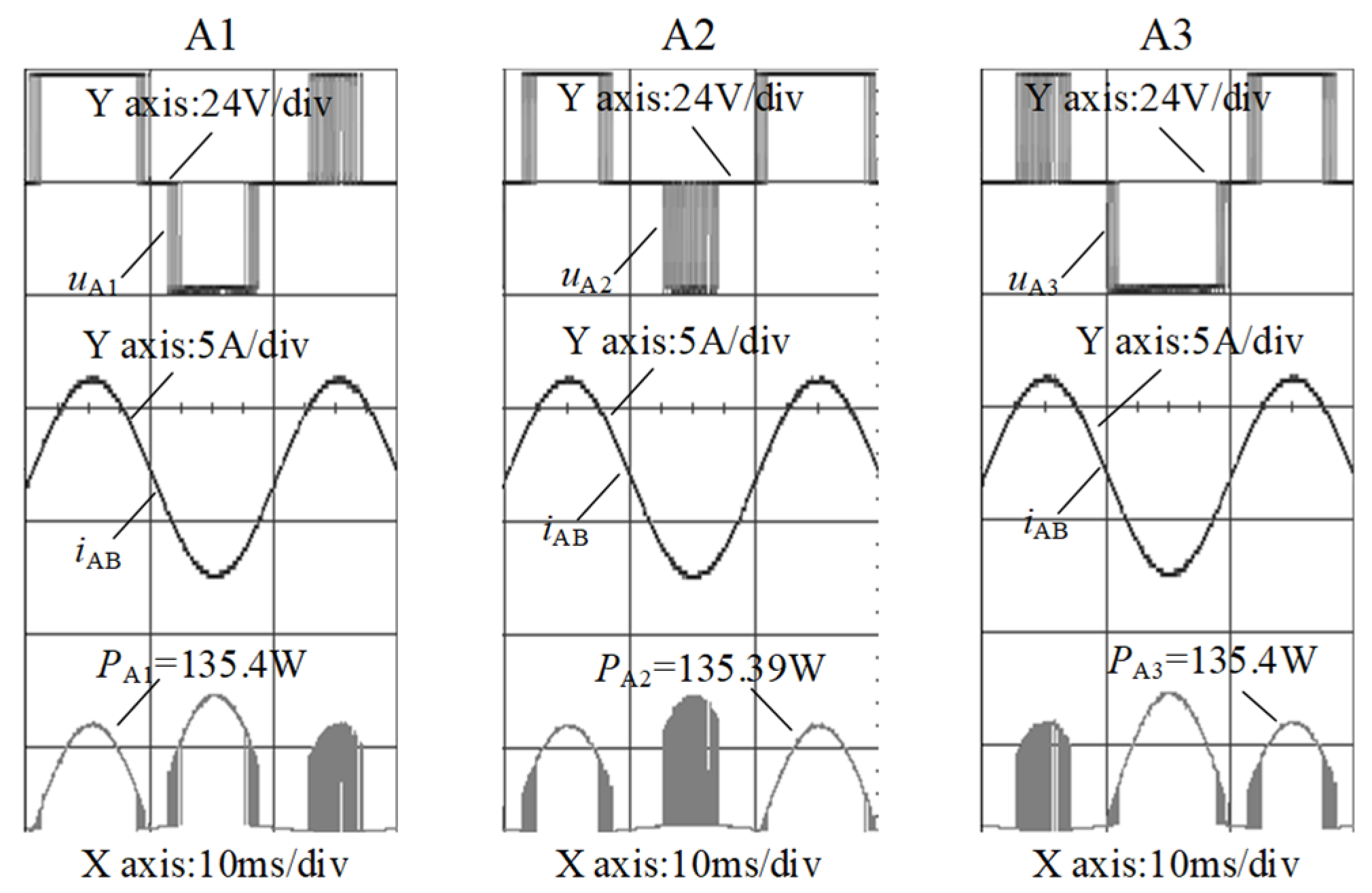

4. Experimental Verification

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Liu, S.; Liu, C. Virtual-vector-based robust predictive current control for dual three-phase PMSM. IEEE Trans. Ind. Electron. 2021, 68, 2048–2058. [Google Scholar] [CrossRef]

- Zhang, W.; Xu, Y.; Huang, H.; Zou, J. Vibration reduction for dual-branch three-phase permanent magnet synchronous motor with carrier phase-shift technique. IEEE Trans. Power Electron. 2020, 35, 607–618. [Google Scholar] [CrossRef]

- Lee, K.; Shen, G.; Yao, W.; Lu, Z. Performance characterization of random pulse width modulation algorithms in industrial and commercial adjustable-speed drives. IEEE Trans. Ind. Appl. 2017, 53, 1078–1108. [Google Scholar] [CrossRef]

- Kumar, A.B.C.; Narayanan, G. Variable-switching frequency PWM technique for induction motor drive to spread acoustic noise spectrum with reduced current ripple. IEEE Trans. Ind. Appl. 2016, 52, 3927–3938. [Google Scholar] [CrossRef]

- Lin, F.; Zuo, S.; Deng, W.; Wu, S. Modeling and analysis of electromagnetic force, vibration, and noise in permanent-magnet synchronous motor considering current harmonics. IEEE Trans. Ind. Electron. 2016, 63, 7455–7466. [Google Scholar] [CrossRef]

- Dove, A.; Naude, J.; Hofajer, I. An argument for the relationship between spectral spreading and probability spreading for EMI-reduction in DC–DC converter. IEEE Trans. Power Electron. 2020, 35, 1459–1472. [Google Scholar] [CrossRef]

- Kirlin, R.L.; Bech, M.M.; Trzynadlowski, A.M. Analysis of power and power spectral density in PWM inverters with randomized switching frequency. IEEE Trans. Ind. Electron. 2002, 49, 486–499. [Google Scholar] [CrossRef]

- Deng, W.; Zou, S. Electromagnetic vibration and noise of the permanent-magnet synchronous motors for electric vehicles: An overview. IEEE Trans. Transport. Electrific. 2019, 5, 59–70. [Google Scholar] [CrossRef]

- Kouro, S.; Malinowski, M.; Gopakumar, K.; Pou, J.; Franquelo, L.G.; Wu, B.; Rodriguez, J.; Perez, M.A.; Leon, J.I. Recent advances and industrial applications of multilevel converters. IEEE Trans. Ind. Electron. 2010, 57, 2553–2580. [Google Scholar] [CrossRef]

- Abu-Rub, H.; Holtz, J.J.; Rodriguez, J.; Baoming, G. Medium-voltage multilevel converters-state of the art challenges and requirements in industrial applications. IEEE Trans. Ind. Electron. 2010, 57, 2581–2596. [Google Scholar] [CrossRef]

- Li, G.; Liu, C.; Wang, Y. A novel RPWN selective harmonic elimination method for single-phase inverter. Electronics 2020, 9, 489. [Google Scholar] [CrossRef]

- Li, H.; Yang, Z.; Wang, B.; Agelidis, V.G.; Zhang, B. On thermal impact of chaotic frequency modulation SPWM techniques. IEEE Trans. Ind. Electron. 2017, 64, 2032–2043. [Google Scholar] [CrossRef]

- Xiong, J.; Li, R.; Wang, T.; Gao, J. Improved random PWM modulation method based on preset carrier switching frequency. J. Intell. Fuzzy Syst. 2020, 38, 311–318. [Google Scholar] [CrossRef]

- Hu, W.; Liu, J. A new scheme of hybrid H-bridge cascaded inverter. Proc. CSEE 2019, 39, 6044–6055. [Google Scholar]

- Adam, G.P.; Abdelsalam, I.A.; Ahmed, K.H.; Williams, B.W. Hybrid multilevel converter with cascaded H-bridge cells for HVDC applications: Operating principle and scalability. IEEE Trans. Power Electron. 2015, 30, 65–77. [Google Scholar] [CrossRef]

- Guo, X.; Wang, X.; Wang, C.; Lu, Z.; Hua, C.; Blaabjerg, F. Improved modulation strategy for singe-phase cascaded H-bridge multilevel inverter. IEEE Trans. Power Electron. 2022, 37, 2470–2474. [Google Scholar] [CrossRef]

- Meraj, M.; Rahman, S.; Iqbal, A.; Ben-Brahim, L.; Abu-Rub, H. Novel level shifted PWM technique for equal power sharing among quasi Z source modules in cascaded multilevel inverter. IEEE Trans. Power Electron. 2022, 36, 4766–4777. [Google Scholar] [CrossRef]

- Ye, M.; Peng, R.; Tong, Z.; Chen, Z.; Miao, Z. A generalized scheme with linear power balance and uniform switching loss for asymmetric cascaded H-bridge multilevel inverters. IEEE Trans. Power Electron. 2022, 37, 2719–2730. [Google Scholar] [CrossRef]

- Chen, Z.; Xu, Y.; Na, X.; Sun, J. Power balance control and optimization methods with output voltage rotation for cascaded multilevel inverter. Proc. CSEE 2018, 38, 1132–1142. [Google Scholar]

- Lopez-Santos, O.; Jacanamejoy-Jamioy, C.A.; Salazar-D’Antonio, D.F.; Corredor-ramirez, J.R.; Garcia, G.; Martinez-Salamero, L. A single-phase transformer-based cascaded asymmetric multilevel inverter with balanced power distribution. IEEE Access. 2019, 7, 98182–98196. [Google Scholar] [CrossRef]

| Parameter | Value | |

|---|---|---|

| DC voltage | 1 H-bridge | 72 V |

| 3 H-bridge | 24 V | |

| Carrier frequency | PS | 1.5–4.5 kHz |

| LS | 3–9 kHz | |

| Output frequency | 50 Hz | |

| Three-phase Load | R = 15 Ω | L = 3 mH |

| Ma | 0.1 | 0.2 | 0.3 | 0.4 | 0.5 | 0.6 | 0.7 | 0.8 | 0.9 | 1 |

|---|---|---|---|---|---|---|---|---|---|---|

| PS-RPWM | 3.69 | 2.52 | 1.98 | 1.64 | 1.39 | 1.20 | 1.05 | 0.914 | 0.796 | 0.685 |

| PC-IRPWM | 3.72 | 2.52 | 1.98 | 1.63 | 1.39 | 1.21 | 1.05 | 0.916 | 0.797 | 0.687 |

| RPWM-SHE | 3.71 | 2.52 | 1.98 | 1.64 | 1.39 | 1.20 | 1.05 | 0.917 | 0.796 | 0.685 |

| PS-PWM | 1.70 | 0.967 | 0.538 | 0.258 | 0.292 | 0.287 | 0.240 | 0.198 | 0.183 | 0.150 |

| LS-PWM | 1.21 | 0.493 | 0.392 | 0.255 | 0.234 | 0.174 | 0.166 | 0.132 | 0.128 | 0.107 |

| PB-RPWM | 1.20 | 0.493 | 0.391 | 0.255 | 0.233 | 0.174 | 0.166 | 0.133 | 0.129 | 0.107 |

| Ma | x | 0.1 | 0.2 | 0.3 | 0.4 | 0.5 | 0.6 | 0.7 | 0.8 | 0.9 | 1 |

|---|---|---|---|---|---|---|---|---|---|---|---|

| dB1st,x/dBV | PS-PWM | 14.88 | 17.34 | 14.5 | 3.04 | 11.38 | 12.93 | 13.81 | 11.56 | 12.97 | 11.80 |

| ΔdB1st,x/dBV | PS-RPWM | −7.58 | −5.64 | −0.57 | 11.87 | 4.78 | 4.78 | 4.41 | 5.08 | 3.68 | 2.06 |

| PC-IRPWM | −10.19 | −5.63 | −0.19 | 13.24 | 5.89 | 5.23 | 4.92 | 4.09 | 3.72 | 3.15 | |

| RPWM-SHE | −9.20 | −7.12 | −1.12 | 11.81 | 4.15 | 2.91 | 4.00 | 4.25 | 3.61 | 0.28 | |

| LS-PWM | −8.1 | −10.8 | −7.95 | −2.19 | −5.9 | −8.72 | −10.85 | −6.24 | −10.05 | −9.53 | |

| PB-RPWM | −18.63 | −21.28 | −20.99 | −10.16 | −20.70 | −20.38 | −21.80 | −17.53 | −20.21 | −20.73 | |

| dB2nd,x/dBV | PS-PWM | 11.66 | −3.08 | 6.84 | 5.52 | 5.78 | 3.40 | 5.64 | 5.17 | 2.05 | 4.49 |

| ΔdB2nd,x/dBV | PS-RPWM | −6.56 | 11.26 | 2.95 | 3.86 | 5.42 | 6.76 | 3.98 | 5.10 | 10.34 | 4.04 |

| PC-IRPWM | −7.83 | 11.35 | 1.57 | 7.21 | 4.41 | 6.96 | 4.14 | 6.63 | 8.34 | 3.73 | |

| RPWM-SHE | −7.26 | 11.16 | 4.37 | 3.46 | 4.55 | 6.89 | 5.95 | 5.99 | 10.63 | 3.79 | |

| LS-PWM | 0.01 | 010 | 0.14 | 0.06 | 0.06 | 0 | −0.04 | −2.24 | −0.01 | 0 | |

| PB-RPWM | −18.56 | −5.94 | −15.59 | −13.80 | −17.10 | −13.05 | −18.36 | −13.31 | −12.95 | −17.17 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liu, J.; Gong, R.; Zhang, Y. Modified RPWM Strategy Based on Level-Shifted Random Carrier and Power Balance to Reduce the PWM Voltage Noise in Three-Phase CHB Inverters. Electronics 2023, 12, 744. https://doi.org/10.3390/electronics12030744

Liu J, Gong R, Zhang Y. Modified RPWM Strategy Based on Level-Shifted Random Carrier and Power Balance to Reduce the PWM Voltage Noise in Three-Phase CHB Inverters. Electronics. 2023; 12(3):744. https://doi.org/10.3390/electronics12030744

Chicago/Turabian StyleLiu, Jianfeng, Renxi Gong, and Yuanyuan Zhang. 2023. "Modified RPWM Strategy Based on Level-Shifted Random Carrier and Power Balance to Reduce the PWM Voltage Noise in Three-Phase CHB Inverters" Electronics 12, no. 3: 744. https://doi.org/10.3390/electronics12030744

APA StyleLiu, J., Gong, R., & Zhang, Y. (2023). Modified RPWM Strategy Based on Level-Shifted Random Carrier and Power Balance to Reduce the PWM Voltage Noise in Three-Phase CHB Inverters. Electronics, 12(3), 744. https://doi.org/10.3390/electronics12030744