Characterization and Reliability Analysis of Enhancement-Mode PEALD AlN/LPCVD SiNx GaN MISFET with In Situ H2/N2 Plasma Pretreatment

Abstract

:1. Introduction

2. Device Fabrication

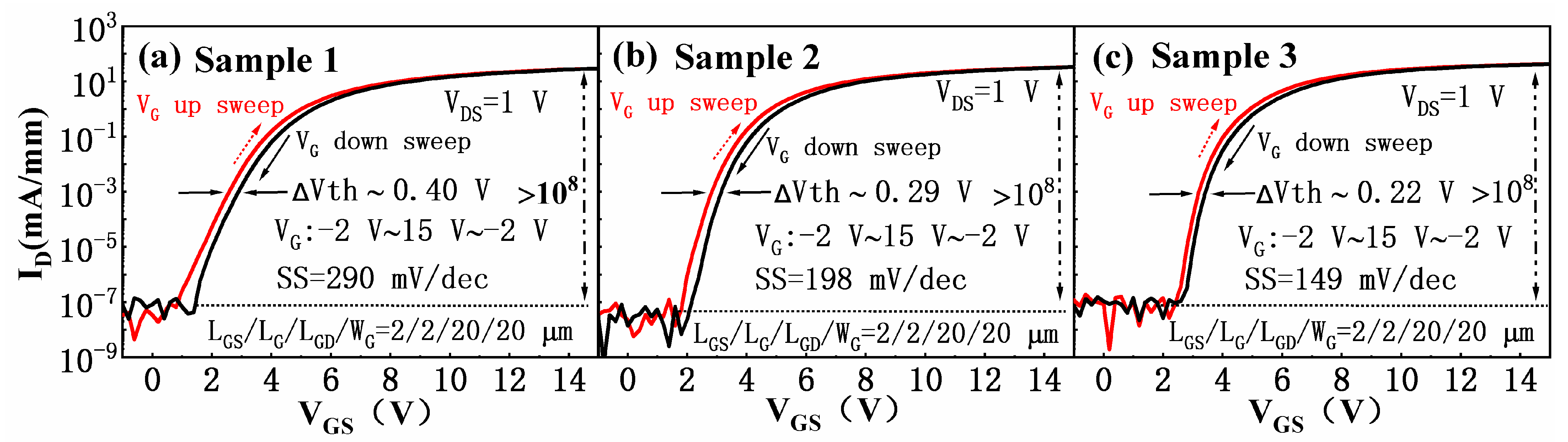

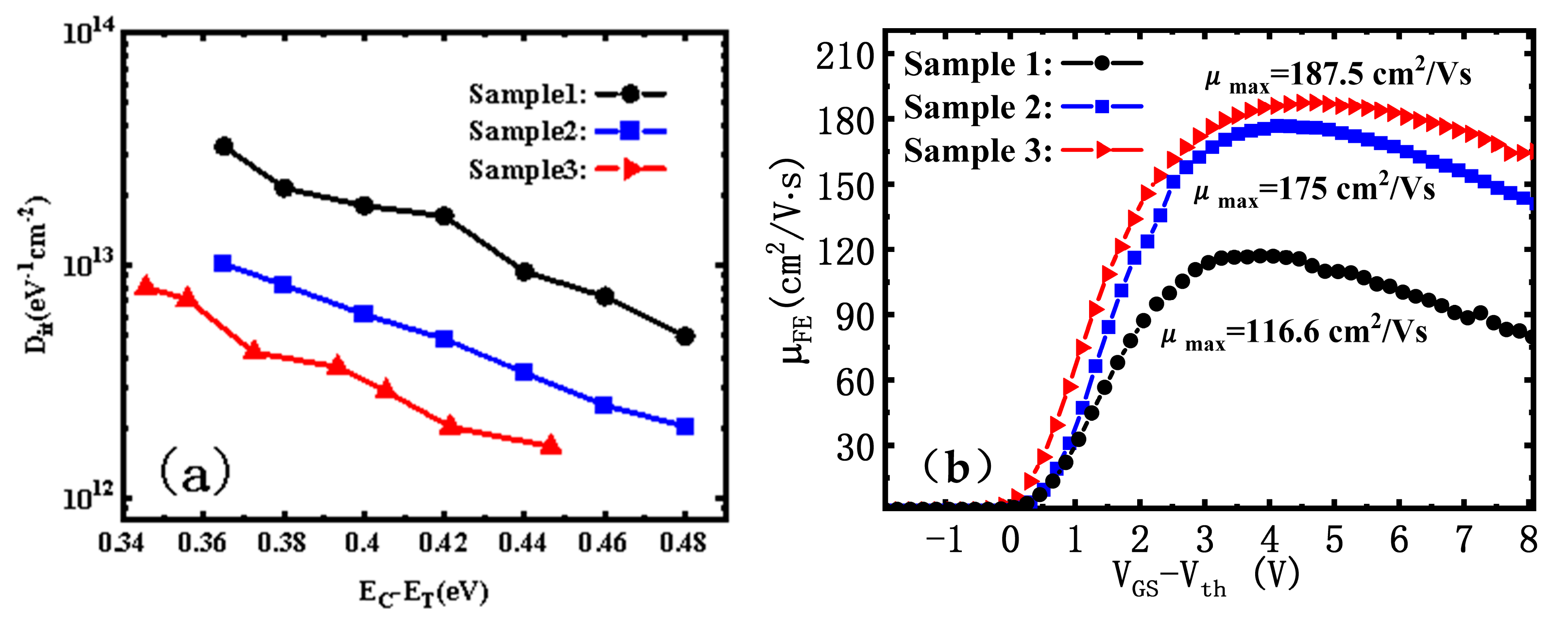

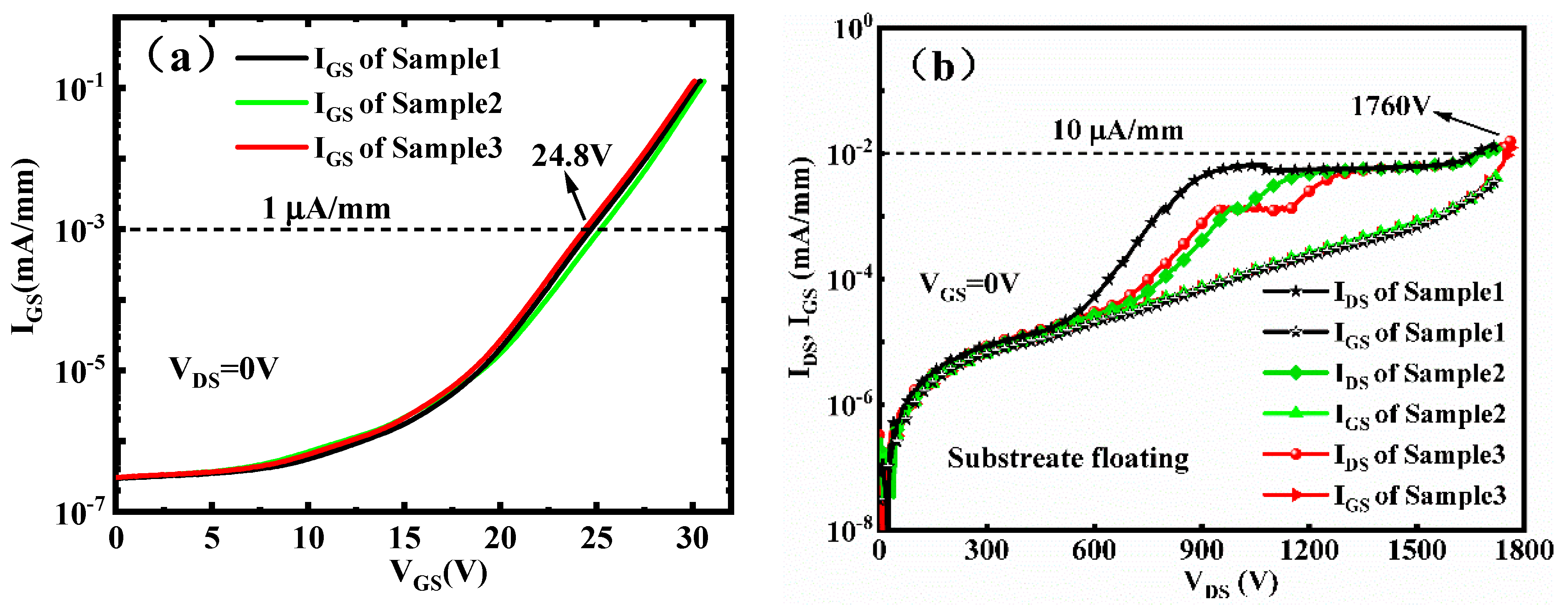

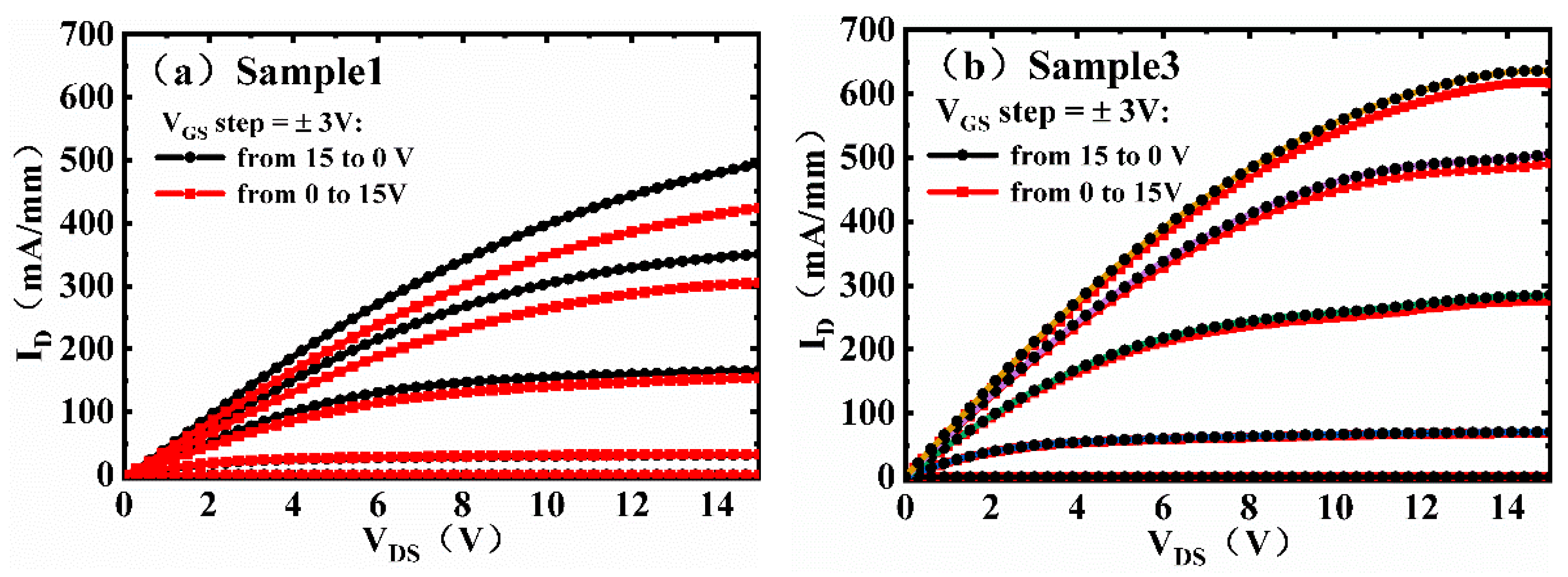

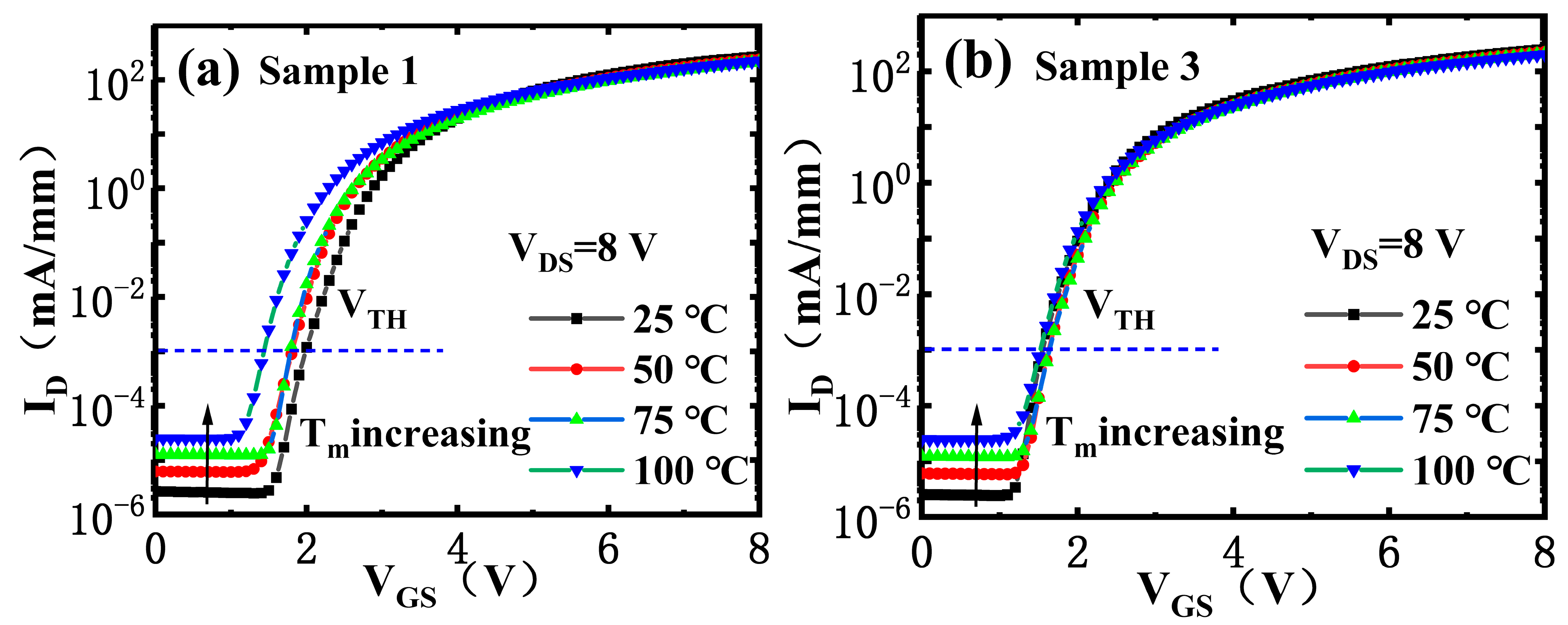

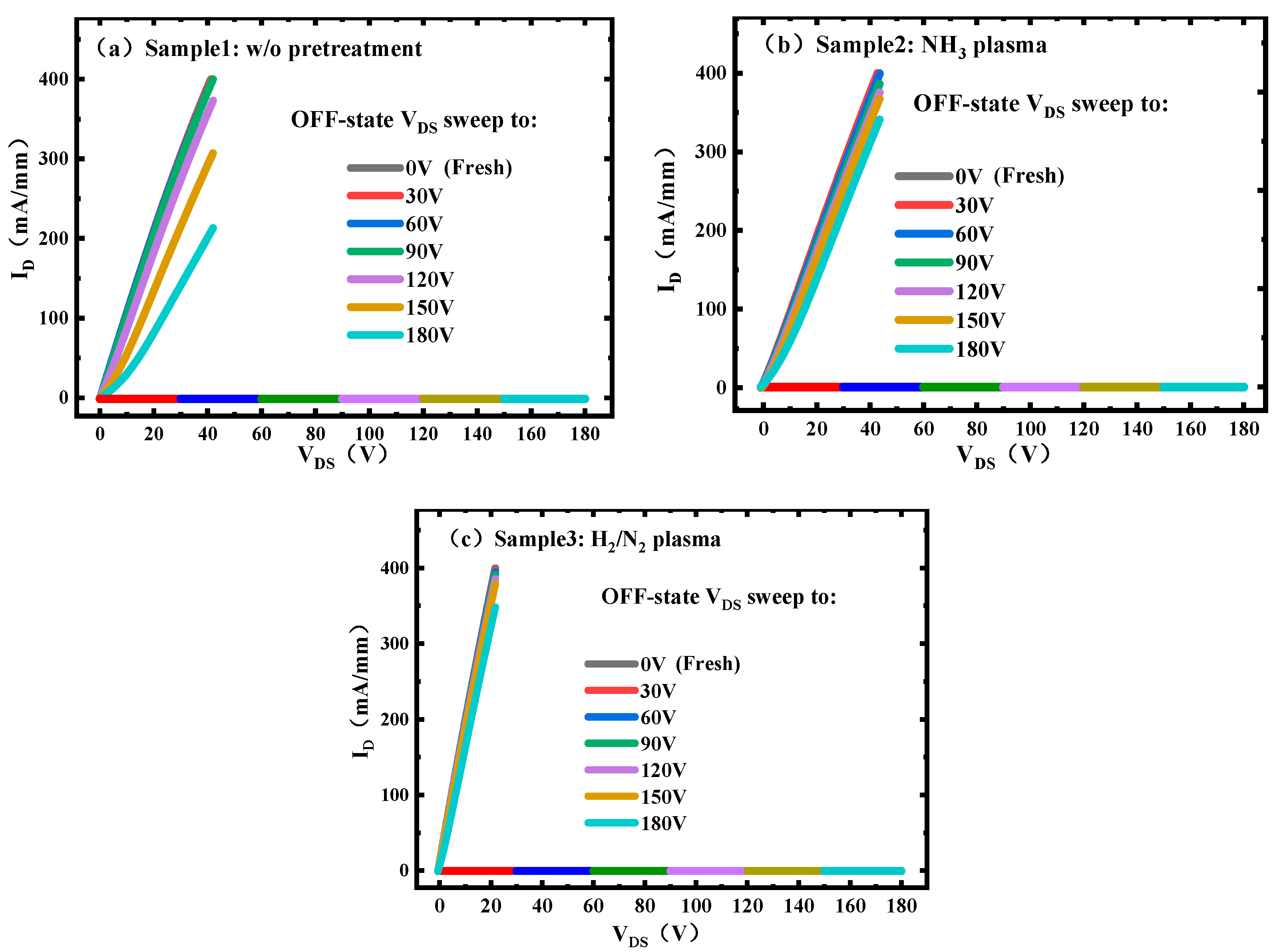

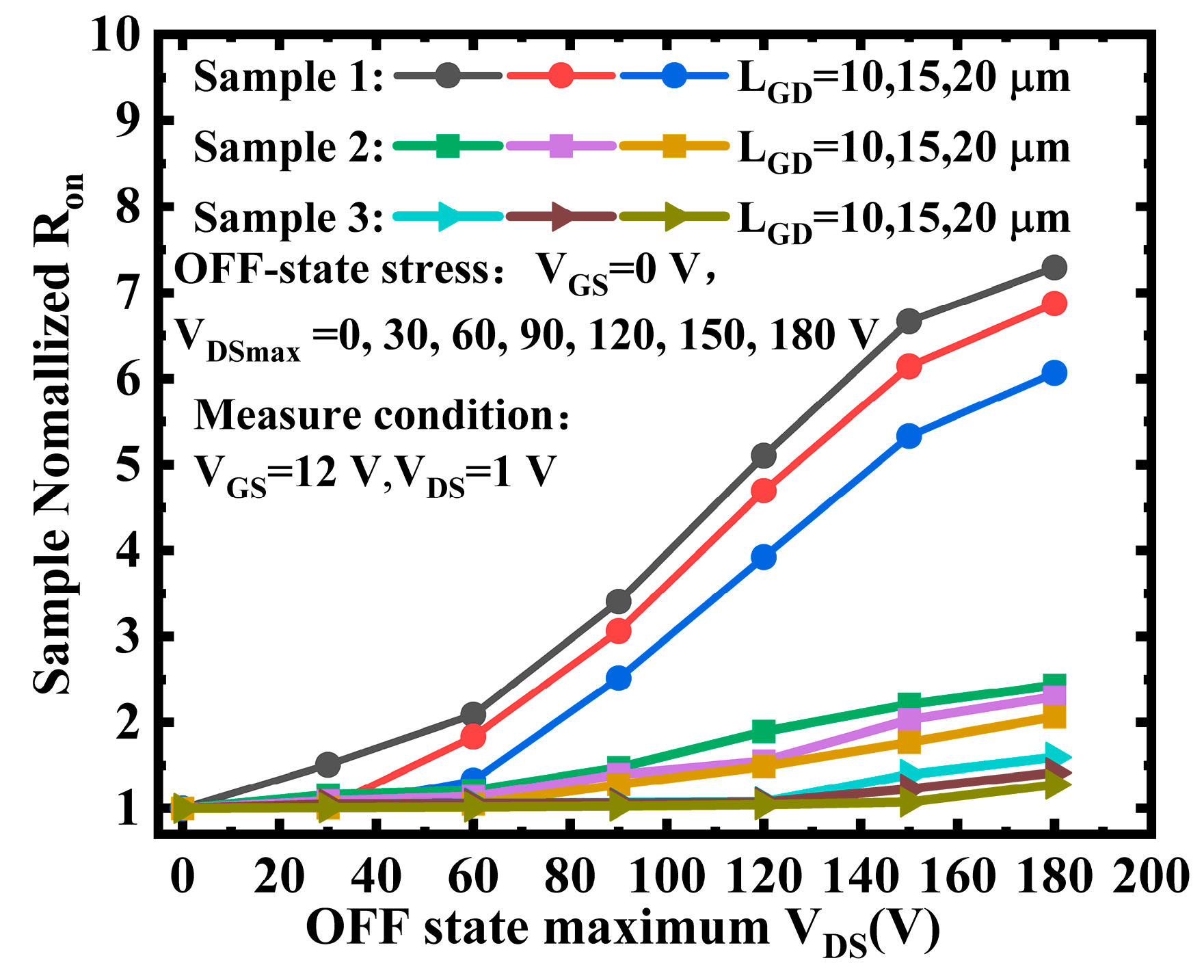

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Chen, K.; Haberlen, O.; Lidow, A.; Tsai, C.; Ueda, T.; Uemoto, Y.; Wu, Y. GaN-on-Si Power Technology: Devices and Applications. IEEE Trans. Electron. Devices 2017, 64, 779–795. [Google Scholar] [CrossRef]

- Liu, W.; Sayed, I.; Gupta, C.; Li, H.; Keller, S.; Mishra, U. An improved methodology for extracting interface state density at Si3N4/GaN. Appl. Phys. Lett. 2020, 116, 22104–22107. [Google Scholar] [CrossRef]

- Jiang, H.; Liu, C.; Chen, Y.; Lu, X.; Tang, C.; Lau, K. Investigation of In Situ SiN as Gate Dielectric and Surface Passivation for GaN MISHEMTs. IEEE Trans. Electron. Devices 2017, 64, 832–839. [Google Scholar] [CrossRef]

- Jauss, S.; Hallaceli, K.; Mansfeld, S.; Schwaiger, S.; Daves, W.; Ambacher, O. Reliability Analysis of LPCVD SiN Gate Dielectric for AlGaN/GaN MIS-HEMTs. IEEE Trans. Electron. Devices 2017, 64, 2298–2305. [Google Scholar] [CrossRef]

- Choi, Y.; Pophristic, M.; Cha, H.; Peres, B.; Spencer, M.; Eastman, L. The Effect of an Fe-doped GaN Buffer on off-State Breakdown Characteristics in AlGaN/GaN HEMTs on Si Substrate. IEEE Trans. Electron. Devices 2006, 53, 2926–2931. [Google Scholar] [CrossRef]

- Hsieh, T.; Chang, E.; Song, Y.; Lin, Y.; Wang, H.; Liu, S.; Salahuddin, S.; Hu, C. Gate Recessed Quasi-Normally OFF Al2O3/AlGaN/GaN MIS-HEMT with Low Threshold Voltage Hysteresis Using PEALD AlN Interfacial Passivation Layer. IEEE Electron. Device Lett. 2014, 35, 732–734. [Google Scholar]

- Zhu, J.; Zhu, Q.; Chen, L.; Hou, B.; Yang, L.; Zhou, X.; Ma, X.; Hao, Y. Impact of Recess Etching on the Temperature-Dependent Characteristics of GaN-Based MIS-HEMTs with Al2O3/AlN Gate-Stack. IEEE Trans. Electron. Devices 2017, 64, 840–847. [Google Scholar] [CrossRef]

- Hua, M.; Lu, Y.; Liu, S.; Liu, C.; Fu, K.; Cai, Y.; Zhang, B.; Chen, K. Compatibility of AlN/SiNxPassivation with LPCVD-SiNxGate Dielectric in GaN-Based MIS-HEMT. IEEE Electron. Device Lett. 2016, 37, 265–268. [Google Scholar] [CrossRef]

- Kim, K.; Jung, S.; Kim, D.; Kang, H.; Im, K.; Oh, J.; Ha, J.; Shin, J.; Lee, J. Effects of TMAH Treatment on Device Performance of Normally Off Al2O3 GaN MOSFET. IEEE Electron. Device Lett. 2011, 32, 1376–1378. [Google Scholar] [CrossRef]

- Jiang, Y.; Wang, Q.; Zhang, F.; Li, L.; Zhou, D.; Liu, Y.; Wang, D.; Ao, J. Reduction of leakage current by O2 plasma treatment for device isolation of AlGaN/GaN heterojunction field-effect transistors. Appl. Surf. Sci. 2015, 351, 1155–1160. [Google Scholar] [CrossRef]

- Liu, C.; Yang, S.; Liu, S.; Tang, Z.; Wang, H.; Jiang, Q.; Chen, K. Thermally Stable Enhancement-Mode GaN Metal-Isolator-Semiconductor High-Electron-Mobility Transistor with Partially Recessed Fluorine-Implanted Barrier. IEEE Electron. Device Lett. 2015, 36, 318–320. [Google Scholar] [CrossRef]

- Choi, W.; Ryu, H.; Jeon, N.; Lee, M.; Cha, H.; Seo, K. Improvement of Vth Instability in Normally-Off GaN MIS-HEMTs Employing PEALD-SiNx as an Interfacial Layer. IEEE Electron. Device Lett. 2014, 35, 30–32. [Google Scholar] [CrossRef]

- Lee, J.; Park, C.; Kim, K.; Kim, D.; Lee, J. Performance of Fully Recessed AlGaN/GaN MOSFET Prepared on GaN Buffer Layer Grown with AlSiC Precoverage on Silicon Substrate. IEEE Electron. Device Lett. 2013, 34, 975–977. [Google Scholar] [CrossRef]

- Zhou, Q.; Liu, L.; Zhang, A.; Chen, B.; Jin, Y.; Shi, Y.; Wang, Z.; Chen, W.; Zhang, B. 7.6 V Threshold Voltage High-Performance Normally-Off Al2O3/GaN MOSFET Achieved by Interface Charge Engineering. IEEE Electron. Device Lett. 2016, 37, 165–168. [Google Scholar] [CrossRef]

- Feng, Q.; Tian, Y.; Bi, Z.; Yue, Y.; Ni, J.; Zhang, J.; Hao, Y.; Yang, L. The improvement of Al2O3/AlGaN/GaN MISHEMT performance by N2 plasma pretreatment. Chin. Phys. B 2009, 18, 3014–3017. [Google Scholar]

- Zhang, Z.; Li, W.; Fu, K.; Yu, G.; Zhang, X.; Zhao, Y.; Sun, S.; Song, L.; Deng, X.; Xing, Z.; et al. AlGaN/GaN MIS-HEMTs of Very-Low Vth Hysteresis and Current Collapse with In-Situ Pre-Deposition Plasma Nitridation and LPCVD-Si3N4 Gate Insulator. IEEE Electron. Device Lett. 2017, 38, 236–239. [Google Scholar] [CrossRef]

- Zhang, Z.; Hua, M.; He, J.; Tang, G.; Qian, Q.; Chen, K. Ab initio study of impact of nitridation at amorphous-SiNx/GaN interface. Appl. Phys. Express 2018, 11, 81003–81006. [Google Scholar] [CrossRef]

- Sun, N.; Huang, H.; Sun, Z.; Wang, R.; Li, S.; Tao, P.; Ren, Y.; Song, S.; Wang, H.; Li, S.; et al. Improving Gate Reliability of 6-In E-Mode GaN-Based MIS-HEMTs by Employing Mixed Oxygen and Fluorine Plasma Treatment. IEEE Trans. Electron. Devices 2022, 69, 82–87. [Google Scholar] [CrossRef]

- Saito, W.; Takada, Y.; Kuraguchi, M.; Tsuda, K.; Omura, I. Recessed-gate structure approach toward normally off high-Voltage AlGaN/GaN HEMT for power electronics applications. IEEE Trans. Electron. Devices 2006, 53, 356–362. [Google Scholar] [CrossRef]

- Setera, B.; Christou, A. Challenges of Overcoming Defects in Wide Bandgap Semiconductor Power Electronics. Electronics 2021, 11, 10. [Google Scholar] [CrossRef]

- Wang, Y.; Liang, Y.; Samudra, G.; Huang, H.; Huang, B.; Huang, S.; Chang, T.; Huang, C.; Kuo, W.; Lo, G. 6.5 V High Threshold Voltage AlGaN/GaN Power Metal-Insulator-Semiconductor High Electron. Mobility Transistor Using Multilayer Fluorinated Gate Stack. IEEE Electron. Device Lett. 2015, 36, 381–383. [Google Scholar] [CrossRef]

- Oka, T.; Nozawa, T. AlGaN/GaN Recessed MIS-Gate HFET with High-Threshold-Voltage Normally-Off Operation for Power Electronics Applications. IEEE Electron. Device Lett. 2008, 29, 668–670. [Google Scholar] [CrossRef]

- Zhou, Q.; Chen, B.; Jin, Y.; Huang, S.; Wei, K.; Liu, X.; Bao, X.; Mou, J.; Zhang, B. High-Performance Enhancement-Mode Al2O3/AlGaN/GaN-on-Si MISFETs with 626 MW/cm2 Figure of Merit. IEEE Trans. Electron. Devices 2015, 62, 776–781. [Google Scholar] [CrossRef]

- Li, P.; Wei, S.; Kang, X.; Zheng, Y.; Zhang, J.; Wu, H.; Wei, K.; Yan, J.; Liu, X. Optimization of Oxygen Plasma Treatment on Ohmic Contact for AlGaN/GaN HEMTs on High-Resistivity Si Substrate. Electronics 2021, 10, 855. [Google Scholar] [CrossRef]

- Shul, R.J.; McClellan, G.B.; Casalnuovo, S.A.; Rieger, D.J.; Pearton, S.J.; Constantine, C.; Barratt, C.; Karlicek, R.F., Jr.; Tran, C.; Schurman, M. Inductively coupled plasma etching of GaN. Appl. Phys. Lett. 1996, 69, 1119–1121. [Google Scholar] [CrossRef]

- Wang, W.; Cai, Y.; Zhang, B.; Huang, W.; Li, H. Control of Inductively Coupled Plasma Etching GaN Sidewall Profiles and Etch Rate. Res. Prog. SSE 2012, 32, 219–224. [Google Scholar]

- Zhang, B.; Wang, J.; Wang, X.; Wang, C.; Huang, C.; He, J.; Wang, M.; Mo, J.; Hu, Y.; Wu, W. Improved Performance of Fully-Recessed High-Threshold-Voltage GaN MIS-HEMT with in Situ H2/N2 Plasma Pretreatment. IEEE Electron. Device Lett. 2022, 43, 1021–1024. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Huang, C.; Wang, J.; Wang, M.; He, J.; Li, M.; Zhang, B.; He, Y. Characterization and Reliability Analysis of Enhancement-Mode PEALD AlN/LPCVD SiNx GaN MISFET with In Situ H2/N2 Plasma Pretreatment. Electronics 2023, 12, 4482. https://doi.org/10.3390/electronics12214482

Huang C, Wang J, Wang M, He J, Li M, Zhang B, He Y. Characterization and Reliability Analysis of Enhancement-Mode PEALD AlN/LPCVD SiNx GaN MISFET with In Situ H2/N2 Plasma Pretreatment. Electronics. 2023; 12(21):4482. https://doi.org/10.3390/electronics12214482

Chicago/Turabian StyleHuang, Chengyu, Jinyan Wang, Maojun Wang, Jin He, Mengjun Li, Bin Zhang, and Yandong He. 2023. "Characterization and Reliability Analysis of Enhancement-Mode PEALD AlN/LPCVD SiNx GaN MISFET with In Situ H2/N2 Plasma Pretreatment" Electronics 12, no. 21: 4482. https://doi.org/10.3390/electronics12214482

APA StyleHuang, C., Wang, J., Wang, M., He, J., Li, M., Zhang, B., & He, Y. (2023). Characterization and Reliability Analysis of Enhancement-Mode PEALD AlN/LPCVD SiNx GaN MISFET with In Situ H2/N2 Plasma Pretreatment. Electronics, 12(21), 4482. https://doi.org/10.3390/electronics12214482