Design Technique of K-Band CMOS Phase Shifter with L-C-L T-Type Low Pass Structure

Abstract

:1. Introduction

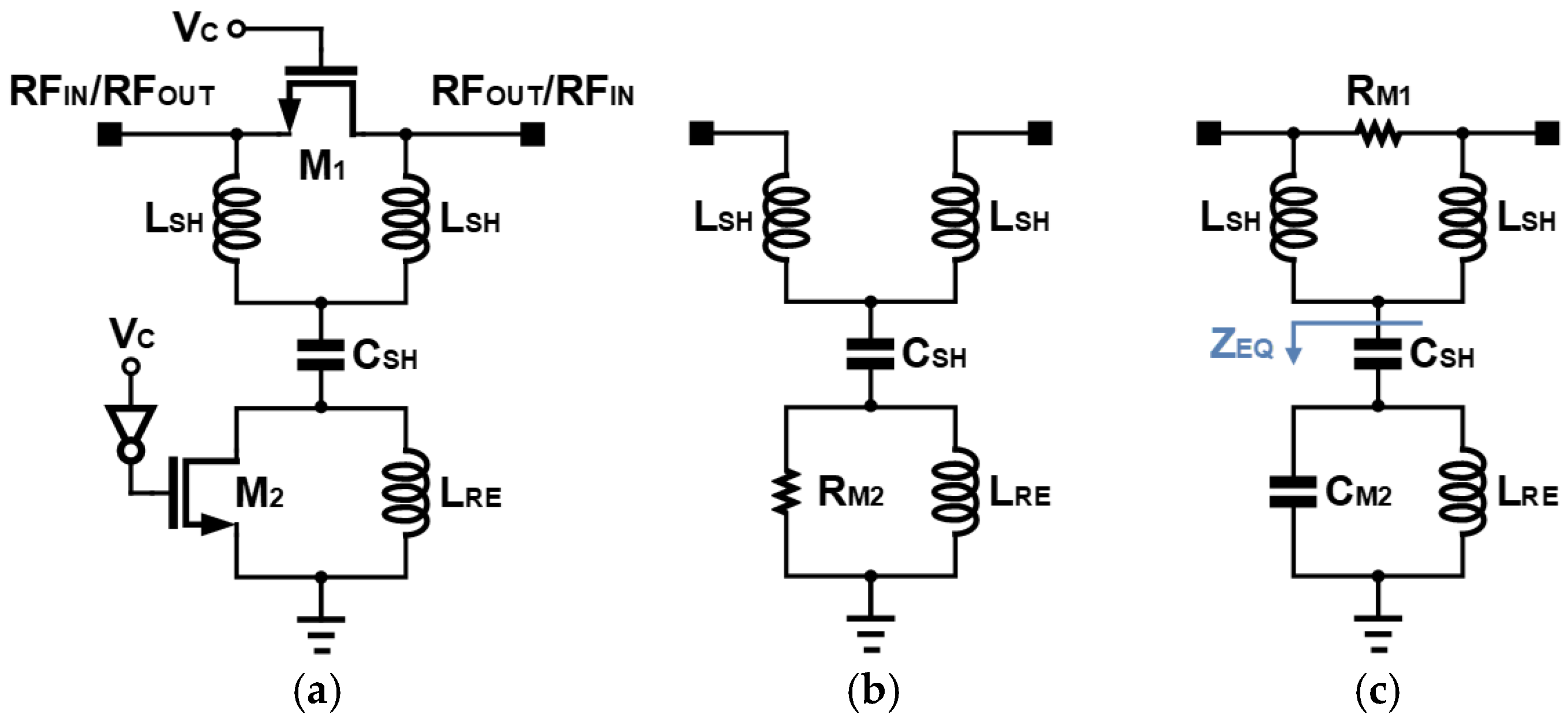

2. Proposed Design Technique of the T-Type Phase Shifter

2.1. Analysis of the Operation of the Phase Shifter

2.2. Design Technique for Securing the Required Phase

2.3. Design Technique for Minimizing Gain Error

- Step 1: In the pass mode, the LRECM2 value is set so that ωZEQ = ∞, the frequency at which ZEQ becomes infinite, becomes the desired operating frequency. This process allows the phase in the pass mode to become zero.

- Step 2: In the shift mode, the frequency of the ωP determined by LSHCSH is adjusted to secure the desired phase difference at the desired operating frequency.

- Step 3: In the pass mode, ωM, the frequency at which ZEQ becomes zero, is adjusted so that gains in shift and pass modes are the same at the desired operating frequency. In this case, the value of LRE(CSH + CM2) is used to adjust the ωM.

- Step 4: Finally, the initial values of the inductors and capacitors constituting the unit-bit are set with LRE, LSH, CSH, and CM2 values satisfying the previous steps 1, 2, and 3.

3. Design Results of the Designed Phase Shifter

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Lee, S.; Park, J.; Hong, S. Millimeter-Wave Multi-Band Reconfigurable Differential Power Divider for 5G Communication. IEEE Trans. Microw. Theory Tech. 2022, 70, 886–894. [Google Scholar] [CrossRef]

- Alhamed, A.; Kazan, O.; Gültepe, G.; Rebeiz, G.M. A Multiband/Multistandard 15–57 GHz Receive Phased-Array Module Based on 4 × 1 Beamformer IC and Supporting 5G NR FR2 Operation. IEEE Trans. Microw. Theory Tech. 2022, 70, 1732–1744. [Google Scholar] [CrossRef]

- Khan, B.; Tervo, N.; Jokinen, M.; Pärssinen, A.; Juntti, M. Statistical Digital Predistortion of 5G Millimeter-Wave RF Beamforming Transmitter Under Random Amplitude Variations. IEEE Trans. Microw. Theory Tech. 2022, 70, 4284–4296. [Google Scholar] [CrossRef]

- Lin, Y.-H.; Tsai, Z.-M. A Wideband Compact 5-Bit Phase Shifter with Low Loss and RMS Errors for 5G Applications. IEEE Microw. Wirel. Compon. Lett. 2021, 31, 1134–1137. [Google Scholar] [CrossRef]

- Wang, S.; Park, J.; Hong, S. A K-Band Variable-Gain Phase Shifter Based on Gilbert-Cell Vector Synthesizer with RC–RL Poly-Phase Filter. IEEE Microw. Wirel. Compon. Lett. 2021, 31, 393–396. [Google Scholar] [CrossRef]

- Liang, C.-J.; Zhang, Y.; Chiang, C.-W.; Huang, R.; Zhou, J.; Du, J.; Wen, K.-A.; Chang, M.-C.F.; Kuan, Y.-C. A K/Ka/V Triband Single-Signal-Path Receiver with Variable-Gain Low-Noise Amplifier and Constant-Gain Phase Shifter in 28-nm CMOS. IEEE Trans. Microw. Theory Tech. 2021, 69, 2579–2593. [Google Scholar] [CrossRef]

- Meghdadi, M.; Azizi, M.; Kiani, M.; Medi, A.; Atarodi, M. A 6-Bit CMOS Phase Shifter for S-Band. IEEE Trans. Microw. Theory Tech. 2020, 58, 3519–3526. [Google Scholar] [CrossRef]

- Sim, S.; Jeon, L.; Kim, J.-G. A Compact X-Band Bi-Directional Phased-Array T/R Chipset in 0.13 μm CMOS Technology. IEEE Trans. Microw. Theory Tech. 2013, 61, 562–569. [Google Scholar] [CrossRef]

- Kim, E.; Jeon, S. A Compact 275–320-GHz Reflection-Type Phase Shifter. IEEE Microw. Wirel. Compon. Lett. 2022, 32, 991–994. [Google Scholar] [CrossRef]

- Li, X.; Fu, H.; Ma, K.; Hu, J. A 2.4–4-GHz Wideband 7-Bit Phase Shifter with Low RMS Phase/Amplitude Error in 0.5-μm GaAs Technology. IEEE Trans. Microw. Theory Tech. 2022, 70, 1292–1301. [Google Scholar] [CrossRef]

- Kang, D.-W.; Lee, H.D.; Kim, C.-H.; Hong, S. Ku-band MMIC Phase Shifter Using a Parallel Resonator with 0.18-μm CMOS Technology. IEEE Trans. Microw. Theory Tech. 2006, 54, 294–301. [Google Scholar] [CrossRef]

- Jeong, H.; Lee, H.D.; Park, B.; Jang, S.; Kong, S.; Park, C. Three-Stacked CMOS Power Amplifier to Increase Output Power with Stability Enhancement for mm-Wave Beamforming Systems. IEEE Trans. Microw. Theory Tech. 2023, 71, 2450–2464. [Google Scholar] [CrossRef]

- Jang, S.; Lee, J.; Lee, J.-W.; Park, C. Design of K-Band Power Amplifier with 180-Degree Phase- Shift Function Using Low-Power CMOS Process. Appl. Sci. 2023, 13, 2501. [Google Scholar] [CrossRef]

- Jang, S.; Lee, J.; Park, C. K-Band CMOS Low-Noise Amplifier with 180° Phase Shift Function Using Cascode Structure. Electron. Lett. 2023, 59, e12908. [Google Scholar] [CrossRef]

- Kim, S.; Jang, S.; Lee, J.; Jeong, H.; Kim, K.-J.; Park, C. Ka-Band GaN HEMT Phase Shifter with T-Type Structure for Beamforming Applications. IEEE Microw. Wirel. Technol. Lett. 2023, 33, 743–746. [Google Scholar] [CrossRef]

- Shin, G.-S.; Kim, J.-S.; Oh, H.-M.; Choi, S.; Byeon, C.W.; Son, J.H.; Lee, J.H.; Kim, C.-Y. Low Insertion Loss, Compact 4-bit Phase Shifter in 65 nm CMOS for 5G Applications. IEEE Microw. Wirel. Compon. Lett. 2016, 26, 37–39. [Google Scholar] [CrossRef]

- Jung, M.; Min, B.-W. A Compact Ka-Band 4-bit Phase Shifter with Low Group Delay Deviation. IEEE Microw. Wirel. Compon. Lett. 2020, 30, 414–416. [Google Scholar] [CrossRef]

- Tsai, J.-H.; Tung, Y.-L.; Lin, Y.-H. A 27–42-GHz Low Phase Error 5-Bit Passive Phase Shifter in 65-nm CMOS Technology. IEEE Microw. Wirel. Compon. Lett. 2020, 30, 900–903. [Google Scholar] [CrossRef]

- Meng, F.; Ma, K.; Yeo, K.S.; Xu, S. A 57-to-64-GHz 0.094-mm2 5-bit Passive Phase Shifter in 65-nm CMOS. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2016, 24, 1917–1925. [Google Scholar] [CrossRef]

- Li, W.-T.; Chiang, Y.-C.; Tsai, J.-H.; Yang, H.-Y.; Cheng, J.-H.; Huang, T.-W. 60-GHz 5-bit Phase Shifter with Integrated VGA Phase-Error Compensation. IEEE Trans. Microw. Theory Tech. 2013, 61, 1224–1235. [Google Scholar] [CrossRef]

- Tsai, J.-H.; Lin, F.-M.; Xiao, H. Low RMS Phase Error 28 GHz 5-bit Switch Type Phase Shifter for 5G Applications. Electron. Lett. 2018, 54, 1184–1185. [Google Scholar] [CrossRef]

| Bits | 90° | 45° | 22.5° | 11.25° | 5.625° |

|---|---|---|---|---|---|

| M1 (μm) (1) | 48 | 180 | 360 | 384 | 384 |

| M2 (μm) (1) | 36 | 28 | 78 | 54 | 128 |

| CSH (fF) | 143.8 | 88.54 | 101.0 | 47.3 | 34.2 |

| LSH (pH) | 138.0 | 72.2 | 10.0 | 33.0 | 10.5 |

| LRE (pH) | 274.6 | 566.4 | 495.8 | 782.7 | 483.4 |

| Ref. | Tech. (nm) | Freq. (GHz) | Total Phase (°)/bits | Insertion Loss (dB) | RMS Phase Error (°) | RMS Gain Error (dB) | Core Size (mm2) | Topology |

|---|---|---|---|---|---|---|---|---|

| [16] | 65 | 27.5–28.35 | 360/4 | <7.6 | <9.0 | N/A | 0.23 | STPS |

| [17] | 28 | 29–37 | 360/4 | 12.8 ± 2.5 (@ 33 GHz) | 8.8 (1) | N/A | 0.08 | STPS |

| [18] | 65 | 27–42 | 360/5 | <14.5 | <3.8 | <2.1 | 0.395 | STPS |

| [19] | 65 | 57–64 | 360/5 | 14.3 ± 2 | <9.5 | <1.1 | 0.094 | RTPS & STPS |

| [20] | 90 | 57–64 | 360/5 | 14.6 ± 3 | <10 | <1.8 | 0.34 | STPS |

| [21] | 180 | 26–30 | 360/5 | <17.4 | <3.3 | <0.85 | 0.84 (2) | STPS |

| This work | 65 | 22.0–23.0 | 180/5 | 7.44 ± 2.0 | <2.6 | <1.2 | 0.16 | STPS |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jang, S.; Kim, C.-Y.; Park, C. Design Technique of K-Band CMOS Phase Shifter with L-C-L T-Type Low Pass Structure. Electronics 2023, 12, 3678. https://doi.org/10.3390/electronics12173678

Jang S, Kim C-Y, Park C. Design Technique of K-Band CMOS Phase Shifter with L-C-L T-Type Low Pass Structure. Electronics. 2023; 12(17):3678. https://doi.org/10.3390/electronics12173678

Chicago/Turabian StyleJang, Seongjin, Choul-Young Kim, and Changkun Park. 2023. "Design Technique of K-Band CMOS Phase Shifter with L-C-L T-Type Low Pass Structure" Electronics 12, no. 17: 3678. https://doi.org/10.3390/electronics12173678

APA StyleJang, S., Kim, C.-Y., & Park, C. (2023). Design Technique of K-Band CMOS Phase Shifter with L-C-L T-Type Low Pass Structure. Electronics, 12(17), 3678. https://doi.org/10.3390/electronics12173678