A Review on Direct Digital Conversion Techniques for Biomedical Signal Acquisition

Abstract

:1. Introduction

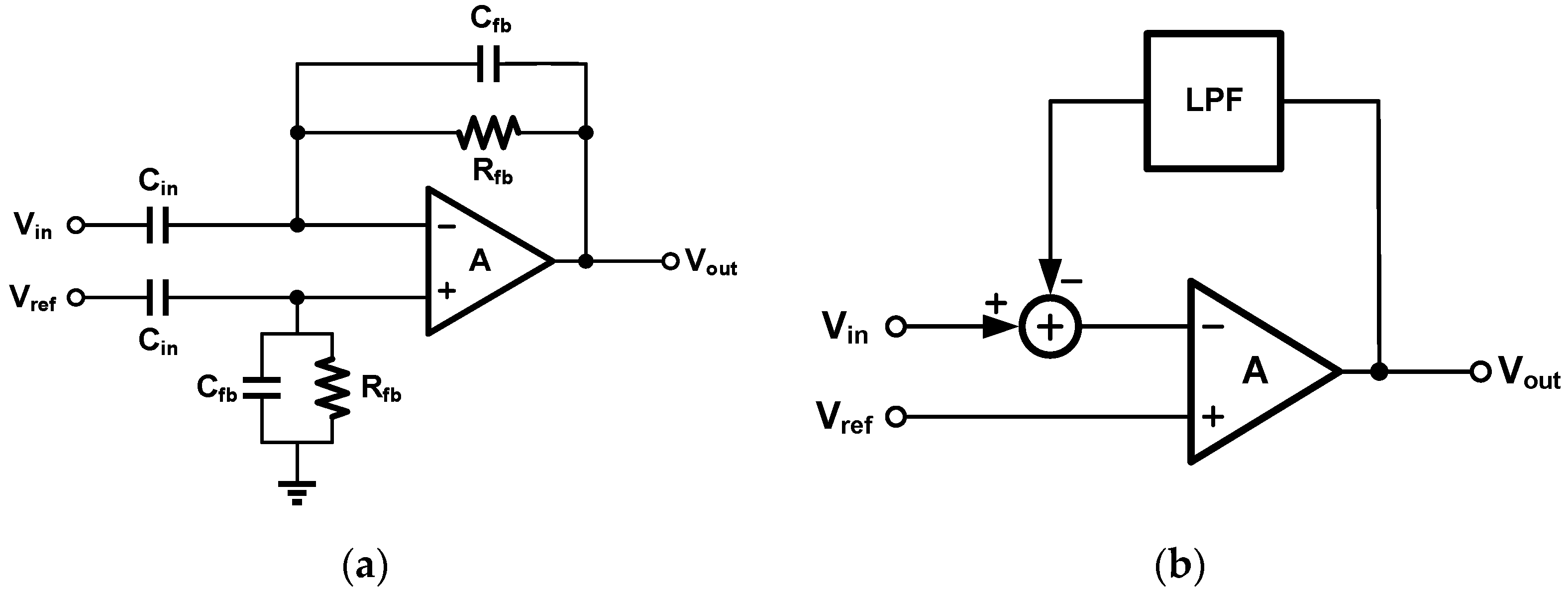

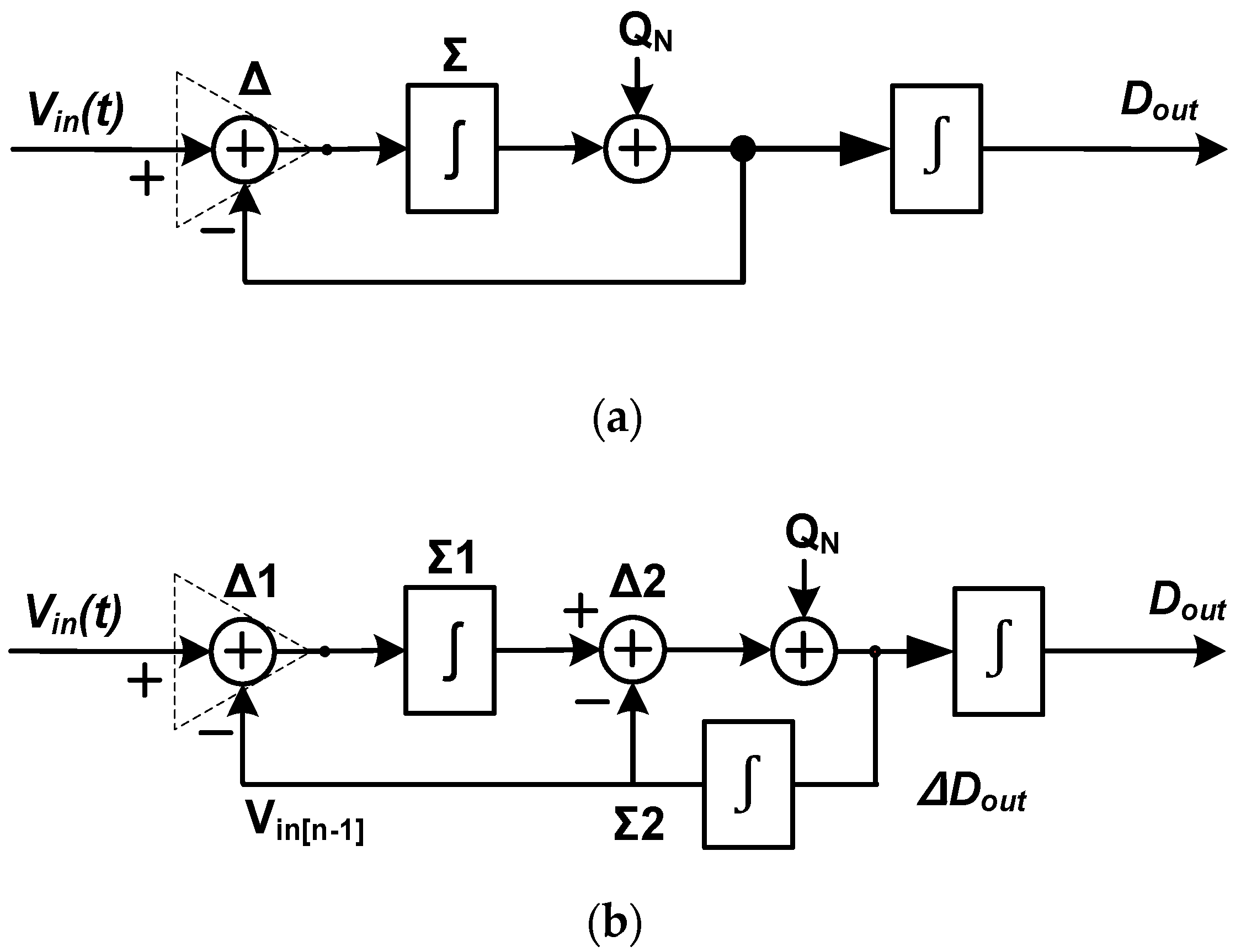

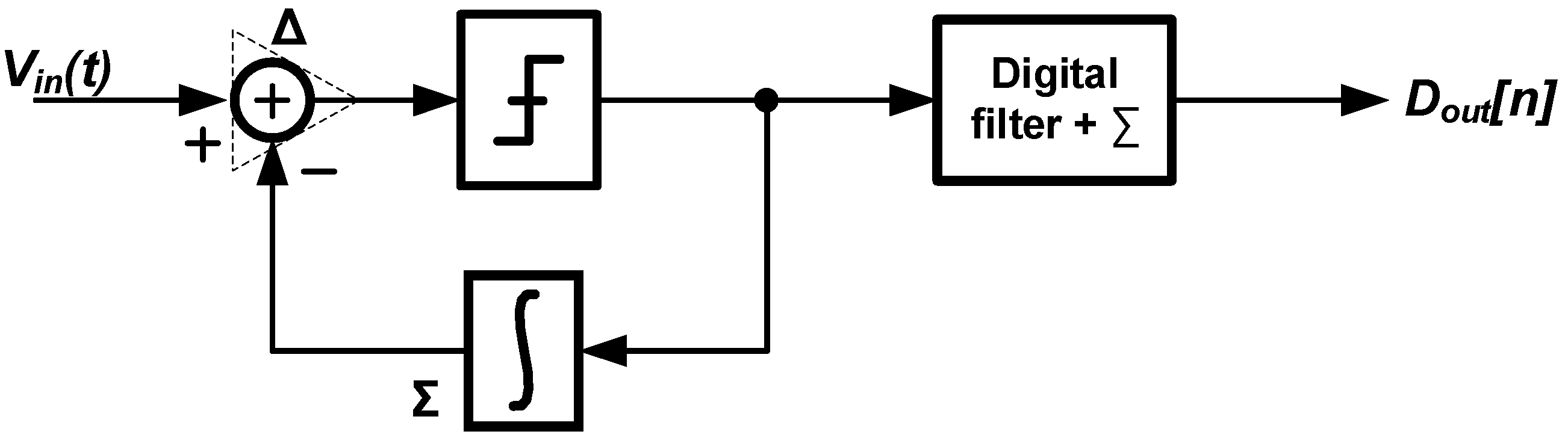

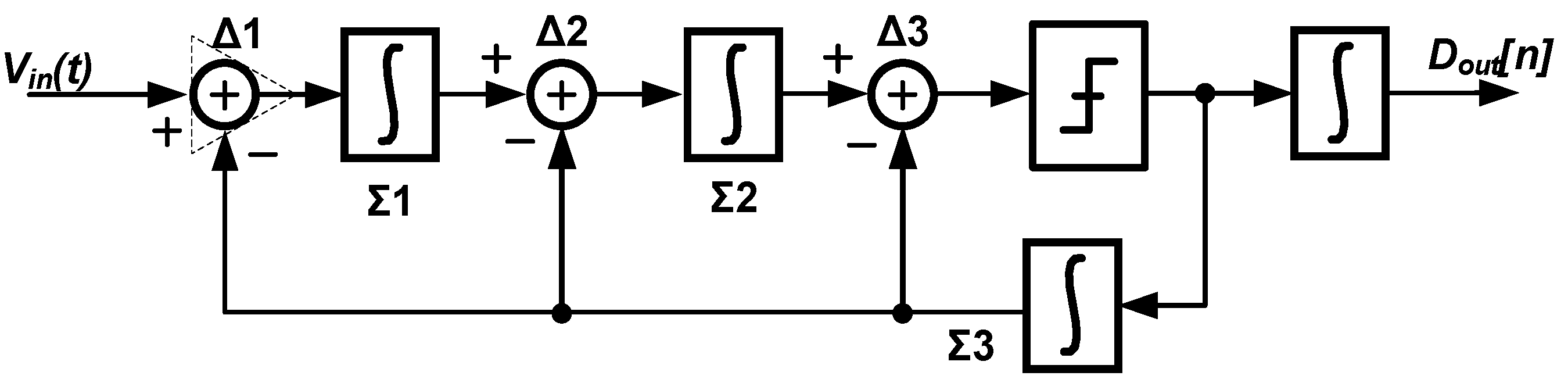

2. Techniques for Biopotential Signal Recording

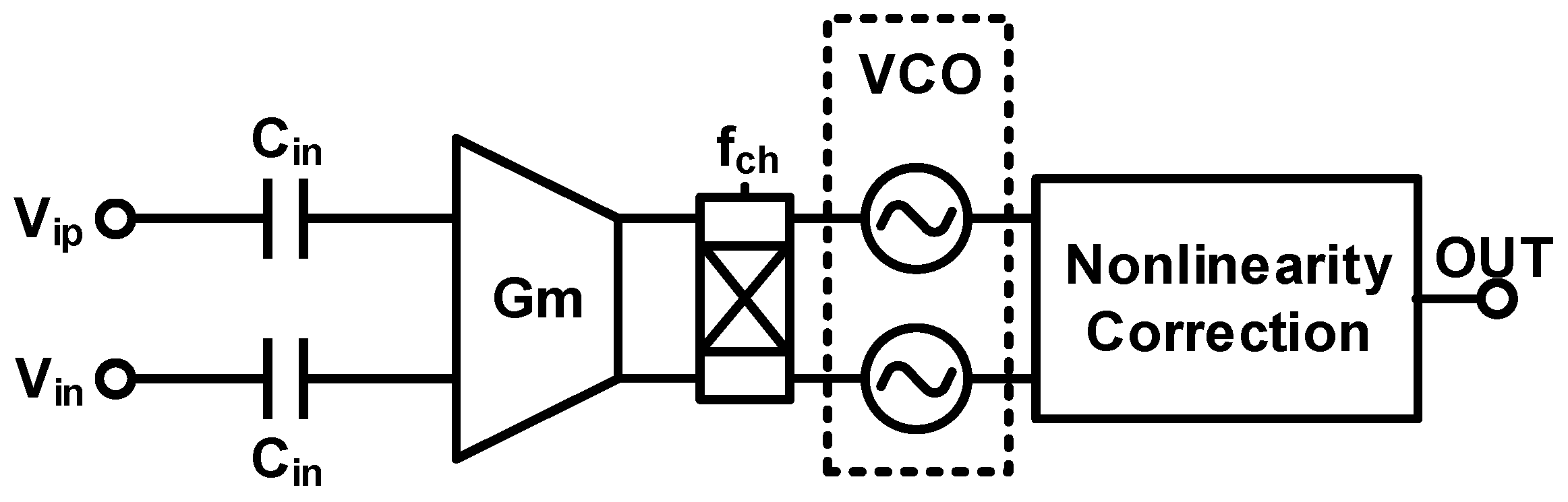

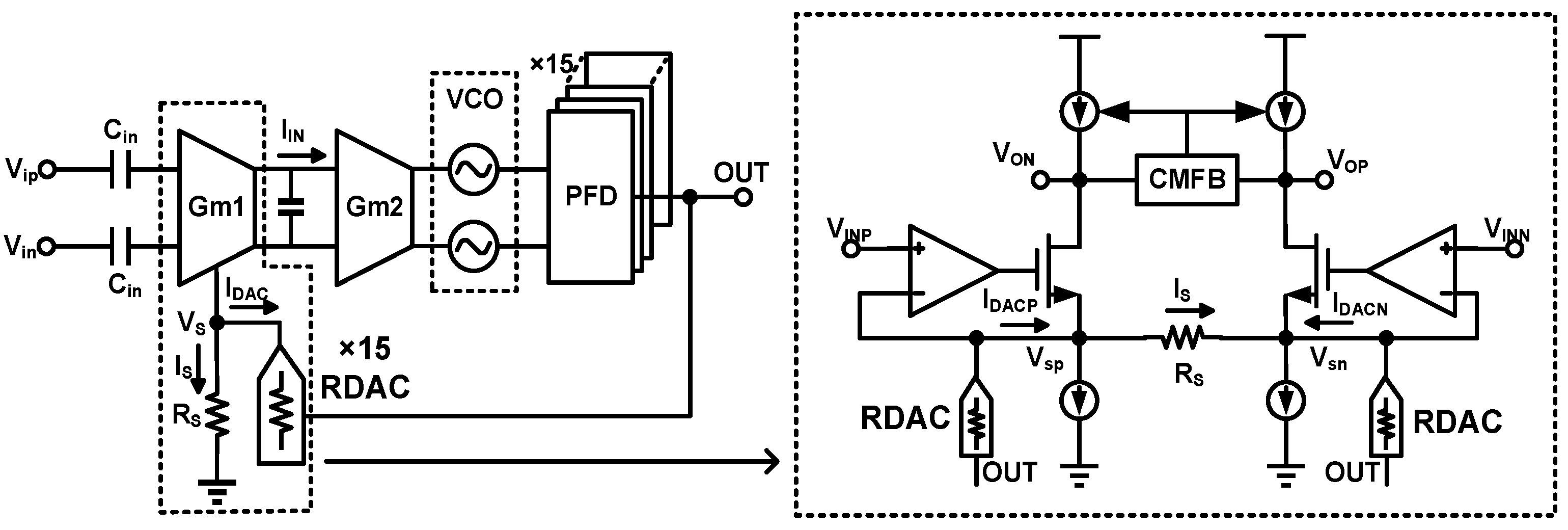

3. Techniques for Voltage-Controlled Oscillator (VCO)-Based Signal Recording

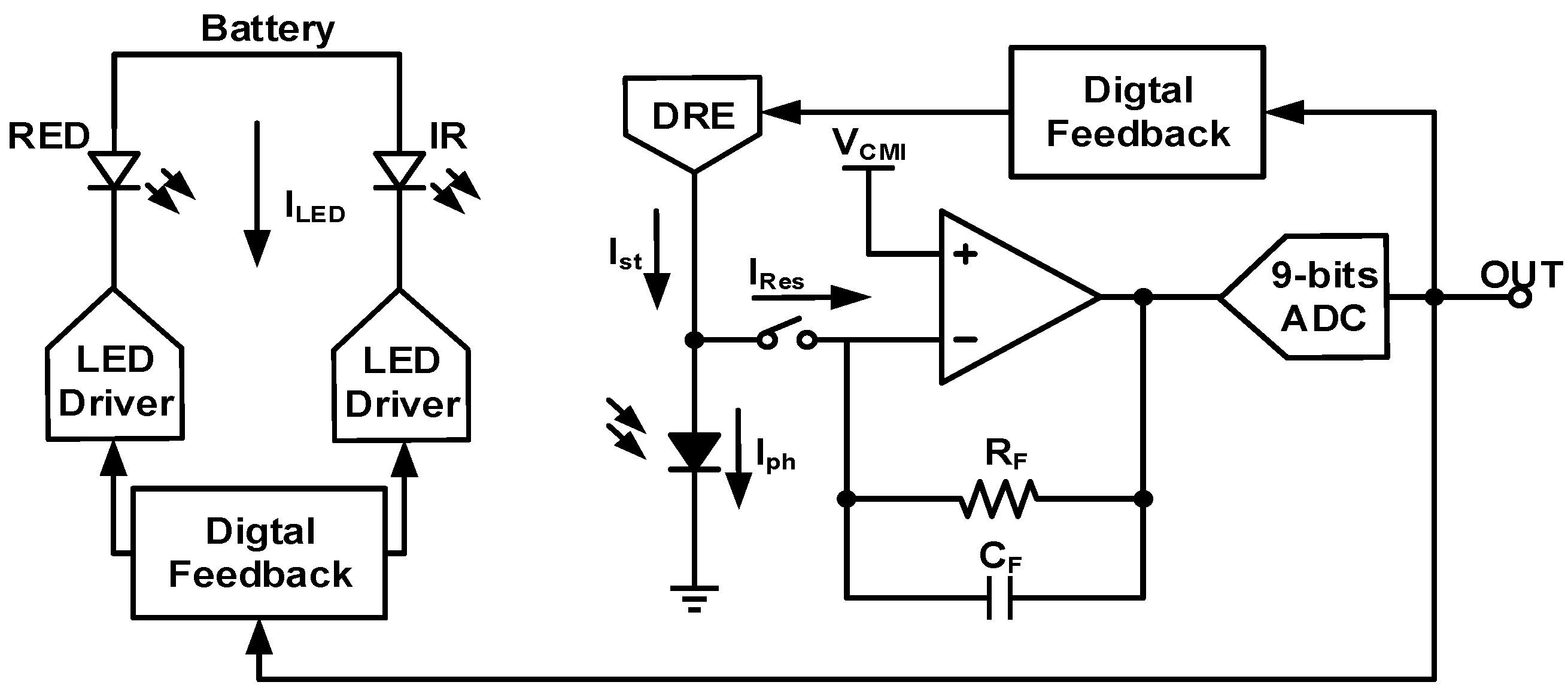

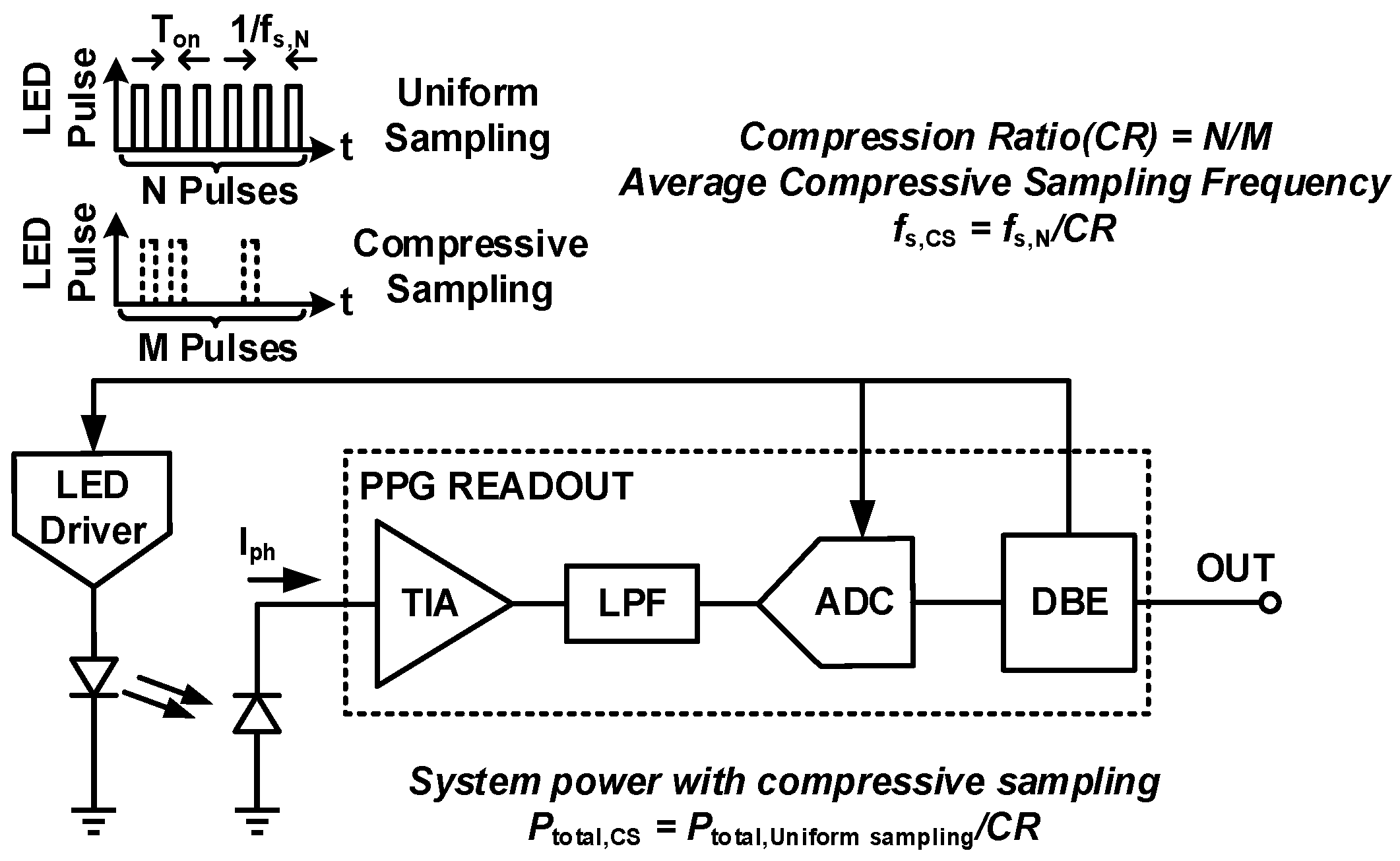

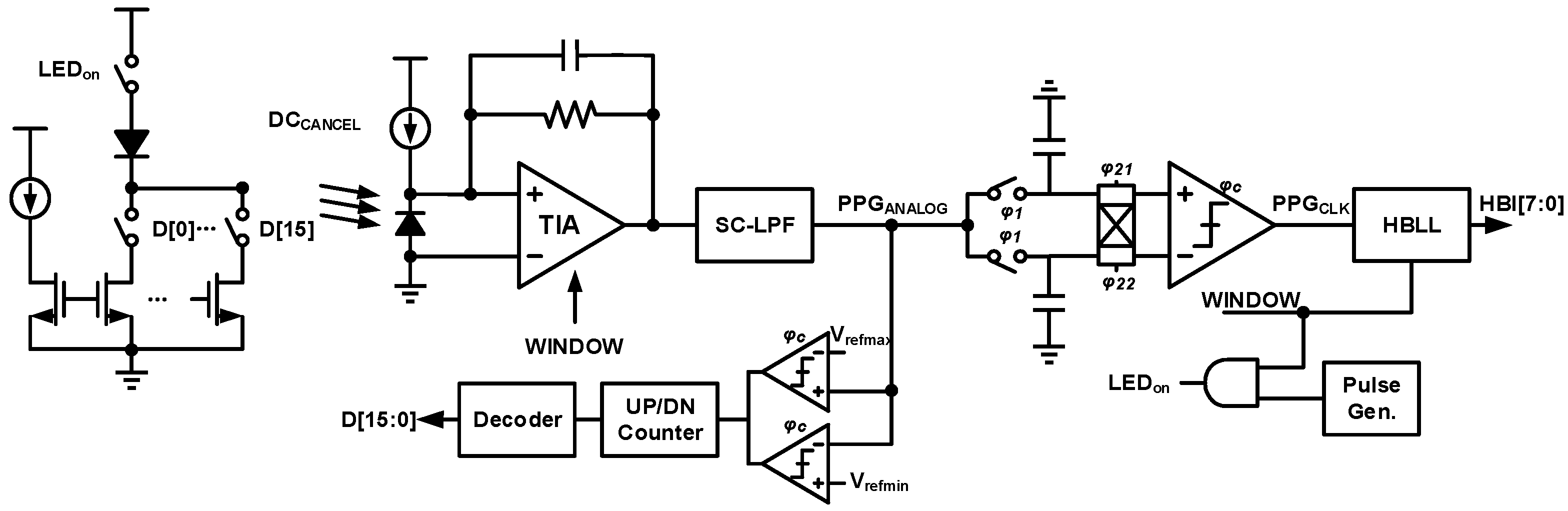

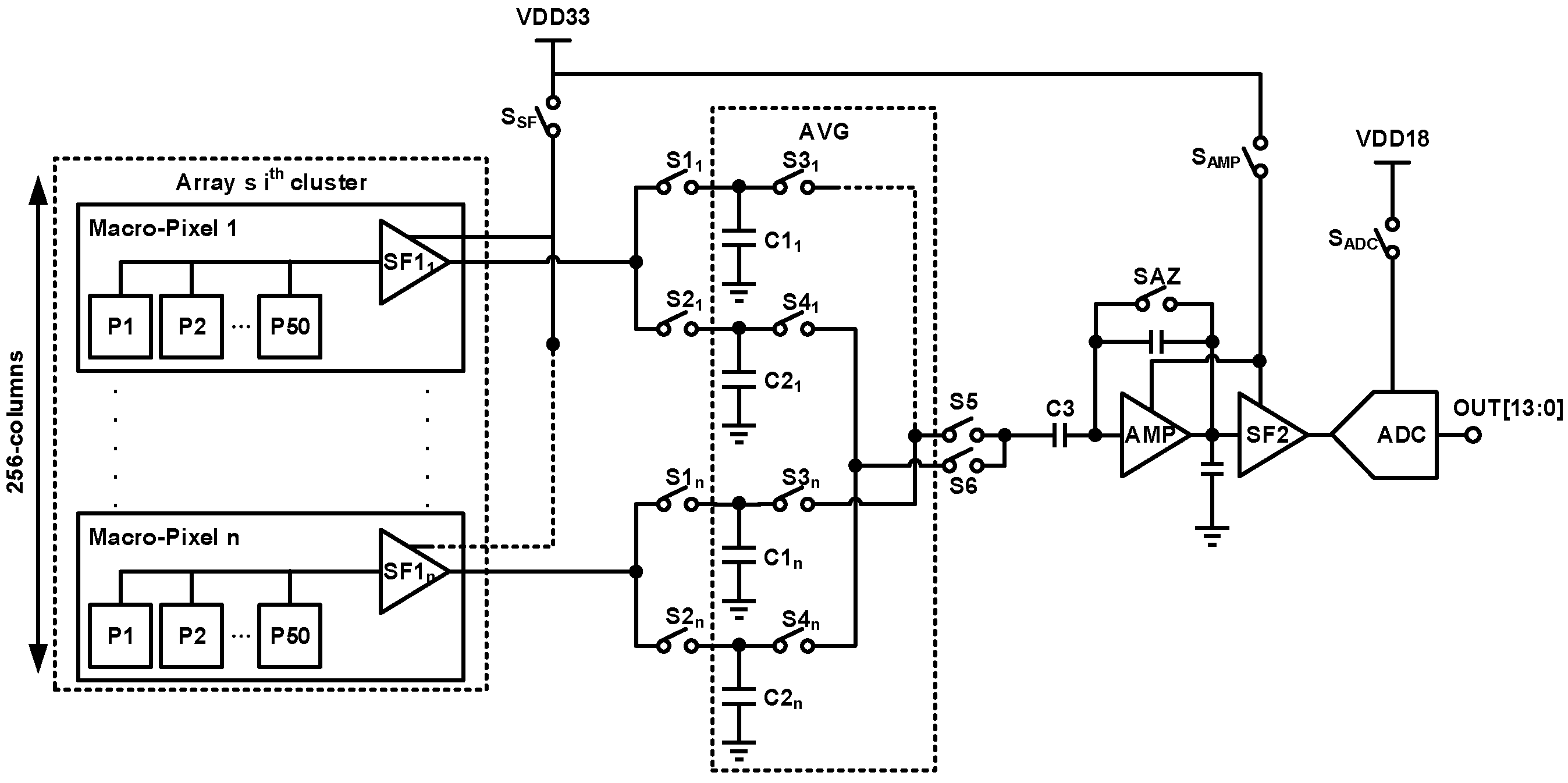

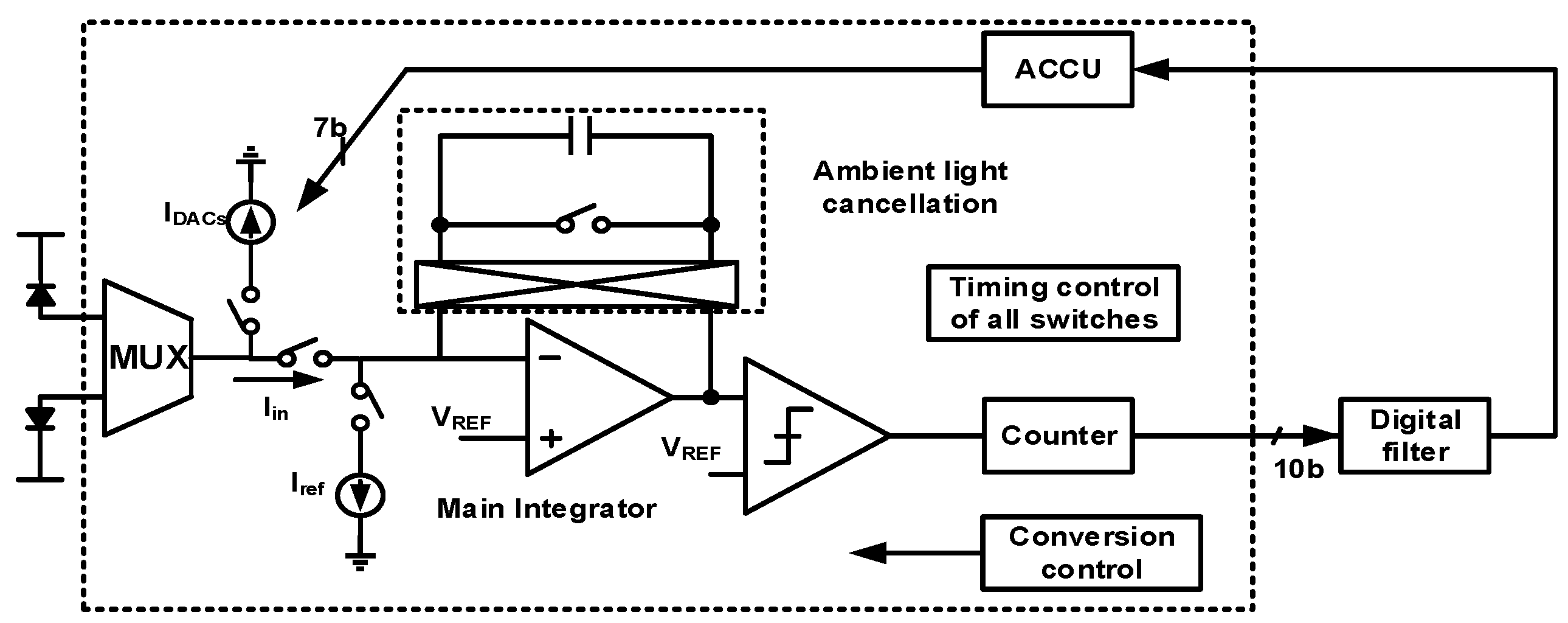

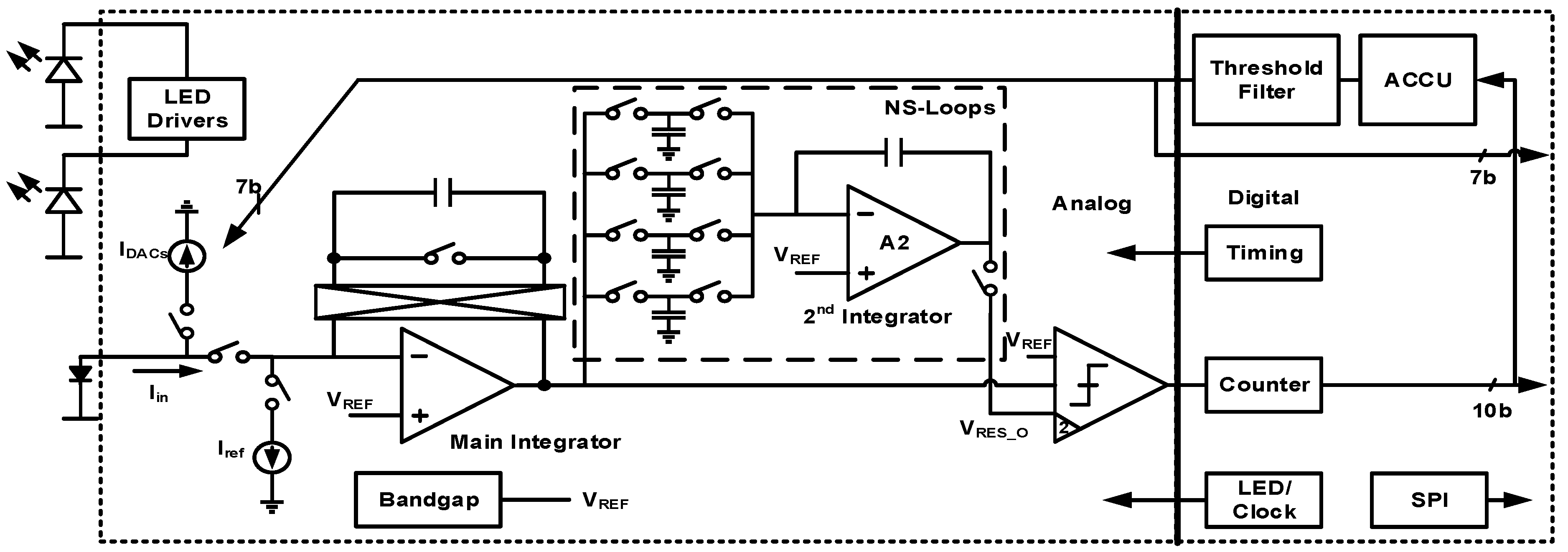

4. Techniques for Bio-Optical Signal Recording

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Song, S.; Konijnenburg, M.; Van, W.R.; Xu, J.; Ha, H.; Sijbers, W.; Stanzione, S.; Biswas, D.; Breeschoten, A.; Vis, P.; et al. A 769 μW Battery-Powered Single-Chip SoC with BLE for Multi-Modal Vital Sign Monitoring Health Patches. IEEE Trans. Biomed. Circuits Syst. 2019, 13, 1506–1517. [Google Scholar] [CrossRef] [PubMed]

- Van, H.N.; Konijnenburg, M.; Pettine, J.; Jee, D.W.; Kim, H.; Morgado, A.; Van, W.R.; Torfs, T.; Mohan, R.; Breeschoten, A.; et al. A 345 µW Multi-Sensor Biomedical SoC with Bio-Impedance, 3-Channel ECG, Motion Artifact Reduction, and Integrated DSP. IEEE J. Solid-State Circuit 2015, 50, 230–244. [Google Scholar]

- Xu, J.; Konijnenburg, M.; Song, S.; Ha, H.; Van, W.R.; Mazzillo, M.; Fallica, G.; Van, H.C.; De, R.W.; Van, H.N. A 665 μW Silicon Photomultiplier-Based NIRS/EEG/EIT Monitoring ASIC for Wearable Functional Brain Imaging. IEEE Trans. Biomed. Circuits Syst. 2018, 12, 1267–1277. [Google Scholar] [CrossRef] [PubMed]

- Mora, L.C.; Putzeys, J.; Raducanu, B.C.; Ballini, M.; Wang, S.; Andrei, A.; Rochus, V.; Vandebriel, R.; Severi, S.; Van, H.C.; et al. A Neural Probe with Up to 966 Electrodes and Up to 384 Configurable Channels in 0.13 μm SOI CMOS. IEEE Trans. Biomed. Circuits Syst. 2017, 11, 510–522. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Raducanu, B.; Van, H.C.; Kloosterman, F. Massive Parallel Readout Circuits for In-Vivo Signal Acquisition. In Sterk Geparallelliseerde Uitleesschakelingen Voor In-Vivo Signaalacquisitie; 2018. Available online: https://imec-publications.be/handle/20.500.12860/31591 (accessed on 26 October 2021).

- Chandrakumar, H.; Markovic, D. A 2 μW 40 mVpp linear input-range chopper-stabilized bio-signal amplifier with boosted input impedance of 300 MΩ and electrode-offset filtering. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 96–97. [Google Scholar]

- Kassiri, H.; Pazhouhandeh, R.; Soltani, N.; Salam, M.T.; Carlen, P.; Velazquez, J.L.P.; Genov, R. All-wireless 64-channel 0.013 mm2/ch closed-loop neurostimulator with rail-to-rail DC offset removal. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 11–15 February 2017; pp. 452–453. [Google Scholar]

- Pazhouhandeh, M.R.; Kassiri, H.; Shoukry, A.; Weisspapir, I.; Carlen, P.L.; Genov, R. Opamp-Less Sub-μW/Channel Δ-Modulated Neural-ADC with Super-GΩ Input Impedance. IEEE J. Solid-State Circuit 2021, 56, 1565–1575. [Google Scholar] [CrossRef]

- Yang, X.; Xu, J.; Ballini, M.; Chun, H.; Zhao, M.; Wu, X.; Van, H.C.; Mora, L.C.; Van Helleputte, N. A 108 dB DR Δ∑-∑M Front-End with 720 mVpp Input Range and >±300 mV Offset Removal for Multi-Parameter Biopotential Recording. IEEE Trans. Biomed. Circuits Syst. 2021, 15, 199–209. [Google Scholar] [CrossRef] [PubMed]

- Kim, C.; Joshi, S.; Courellis, H.; Wang, J.; Miller, C.; Cauwenberghs, G. Sub μVrms-Noise Sub μW/Channel ADC-Direct Neural Recording with 200-mV/ms Transient Recovery Through Predictive Digital Autoranging. IEEE J. Solid-State Circuit 2018, 53, 3101–3110. [Google Scholar] [CrossRef] [Green Version]

- Van Wegberg, R.; Sijbers, W.; Song, S.; Breeschoten, A.; Vis, P.; Konijnenburg, M.; Jiang, H.; Rooijakkers, M.; Berset, T.; Penders, J.; et al. A 5-Channel Unipolar Fetal-ECG Readout IC for Patch-Based Fetal Monitoring. IEEE Solid-State Circ. Lett. 2019, 2, 71–74. [Google Scholar] [CrossRef]

- Wang, S.; Ballini, M.; Yang, X.; Sawigun, C.; Weijers, J.W.; Biswas, D.; Van Helleputte, N.; Lopez, C.M. A Compact Chopper Stabilized Δ-ΔΣ Neural Readout IC with Input Impedance Boosting. IEEE Open J. Solid-State Circuits Soc. 2021, 1, 67–78. [Google Scholar] [CrossRef]

- Sporer, M.; Reich, S.; Kauffman, J.G.; Ortmanns, M. A Direct Digitizing Chopped Neural Recorder Using a Body-Induced Offset Based DC Servo Loop. IEEE Trans. Biomed. Circuits Syst. 2022, 16, 409–418. [Google Scholar] [CrossRef] [PubMed]

- Wendler, D.; Dorigo, D.D.; Amayreh, M.; Bleitner, A.; Marx, M.; Manoli, Y. A 0.00378 mm2 Scalable Neural Recording Front-End for Fully Immersible Neural Probes Based on a Two-Step Incremental Delta-Sigma Converter with Extended Counting and Hardware Reuse. In Proceedings of the 2021 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021; pp. 398–400.

- Jiang, H.; Makinwa, K.A.A.; Nihtianov, S. An energy-efficient 3.7 nV/√Hz bridge-readout IC with a stable bridge offset compensation scheme. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 11–15 February 2017; pp. 172–173.

- Jiang, H.; Liu, Y.; Middelburg, L.; Mansouri, B.E.; Nihtianov, S. A Continuous-Time Readout IC with 0.12 aF/√Hz for Capacitive Inertial Sensors. In Proceedings of the 2021 IEEE International Conference on Integrated Circuits, Technologies and Applications (ICTA), Zhuhai, China, 24–26 November 2021; pp. 14–15.

- Mark, K.L. Deep Brain Stimulation: Current and Future Clinical Applications. Mayo Clin. Proc. 2011, 86, 662–672. [Google Scholar]

- Jiang, W.; Hokhikyan, V.; Chandrakumar, H.; Karkare, V.; Markovic, D. A ±50 mV linear-input-range VCO-based neural-recording front-end with digital nonlinearity correction. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 484–485. [Google Scholar]

- Li, S.; Zhao, W.; Xu, B.; Yang, X.; Tang, X.; Shen, L.; Lu, N.; Pan, D.Z.; Sun, N. A 0.025-mm2 0.8-V 78.5 dB-SNDR VCO-Based Sensor Readout Circuit in a Hybrid PLL-ΔΣM Structure. In Proceedings of the 2019 IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 14–17 April 2019; pp. 1–3.

- Huang, J.; Mercier, P.P. A 112-dB SFDR 89-dB SNDR VCO-Based Sensor Front-End Enabled by Background-Calibrated Differential Pulse Code Modulation. IEEE J. Solid-State Circuit 2021, 56, 1046–1057. [Google Scholar] [CrossRef]

- Pochet, C.; Hall, D.A. A 4.4 μW 2.5 kHz-BW 92.1 dB-SNDR 3rd-Order VCO-Based ADC with Pseudo Virtual Ground Feedforward Linearization. In Proceedings of the 2022 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 20–26 February 2022; pp. 408–410.

- Lee, C.; Jeon, T.; Jang, M.; Park, S.; Kim, J.; Lim, J.; Ahn, J.H.; Huh, Y.; Chae, Y. A 6.5-μW 10-kHz BW 80.4-dB SNDR Gm-C-Based CT ∆∑ Modulator with a Feedback-Assisted Gm Linearization for Artifact-Tolerant Neural Recording. IEEE J. Solid-State Circuit 2020, 55, 2889–2901. [Google Scholar] [CrossRef]

- Huang, X.; Zeng, K.; Liu, Y.; Rhee, W.; Kim, T.; Wang, Z. A 5GHz 200kHz/5000ppm Spread-Spectrum Clock Generator with Calibration-Free Two-Point Modulation Using a Nested-Loop BBPLL. In Proceedings of the 2019 IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 14–17 April 2019; pp. 1–4. [Google Scholar]

- Huang, X.; Wang, B.; Rhee, W.; Wang, Z. A 5.4GHz ΔΣ Bang-Bang PLL with 19dB In-Band Noise Reduction by Using a Nested PLL Filter. In Proceedings of the 2020 International Symposium on VLSI Design, Automation and Test (VLSI-DAT), Hsinchu, Taiwan, 10–13 August 2020; pp. 1–2.

- Antonino, C. An Ultra Low-Noise Micropower PPG Sensor; EPFL: Lausanne, Switzerland, 2020. [Google Scholar]

- Glaros, K.N.; Drakakis, E.M. A Sub-mW Fully-Integrated Pulse Oximeter Front-End. IEEE Trans. Biomed. Circuits Syst. 2013, 7, 363–375. [Google Scholar] [CrossRef] [PubMed]

- Sharma, A.; Bae, L.S.; Polley, A.; Narayanan, S.; Li, W.; Sculley, T.; Ramaswamy, S. Multi-modal smart bio-sensing SoC platform with >80 dB SNR 35 µA PPG RX chain. In Proceedings of the 2016 IEEE Symposium on VLSI Circuits (VLSI-Circuits), Honolulu, HI, USA, 15–17 June 2016; pp. 1–2. [Google Scholar]

- Schönle, P.; Fateh, S.; Burger, T.; Huang, Q. A power-efficient multi-channel PPG ASIC with 112 dB receiver DR for pulse oximetry and NIRS. In Proceedings of the 2017 IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 30 April–3 May 2017; pp. 1–4. [Google Scholar]

- Harpe, P.; Cantatore, E.; Van Roermund, A. An oversampled 12/14b SAR ADC with noise reduction and linearity enhancements achieving up to 79.1dB SNDR. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 194–195. [Google Scholar]

- Atef, M.; Wang, M.; Wang, G. A Fully Integrated High-Sensitivity Wide Dynamic Range PPG Sensor with an Integrated Photodiode and an Automatic Dimming Control LED Driver. IEEE Sens. J. 2018, 18, 652–659. [Google Scholar] [CrossRef]

- Marefat, F.; Erfani, R.; Mohseni, P. A 1-V 8.1-μW W PPG-Recording Front-End with > 92-dB DR Using Light-to-Digital Conversion with Signal-Aware DC Subtraction and Ambient Light Removal. IEEE Solid-State Circ. Lett. 2020, 3, 17–20. [Google Scholar] [CrossRef]

- Alhawari, M.; Albelooshi, N.A.; Perrott, M.H. A 0.5 V < 4 μW CMOS Light-to-Digital Converter Based on a Nonuni-form Quantizer for a Photoplethysmographic Heart-Rate Sensor. IEEE J. Solid-State Circuit 2014, 49, 271–288. [Google Scholar]

- Winokur, E.S.; O’dwyer, T.; Sodini, C.G. A Low-Power, Dual-Wavelength Photoplethysmogram (PPG) SoC with Static and Time-Varying Interferer Removal. IEEE Trans. Biomed. Circuits Syst. 2015, 9, 581–589. [Google Scholar] [CrossRef] [PubMed]

- Rajesh, P.V.; Valero-Sarmiento, J.M.; Yan, L.; Bozkurt, A.; Van Hoof, C.; Van Helleputte, N.; Yazicioglu, R.F.; Verhelst, M. A 172 µW compressive sampling photoplethysmographic readout with embedded direct heart-rate and variability extraction from compressively sampled data. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 386–387. [Google Scholar]

- Jang, D.H.; Cho, S. A 43.4 μW photoplethysmogram-based heart-rate sensor using heart-beat-locked loop. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 474–476.

- Caizzone, A.; Boukhayma, A.; Enz, C. A 2.6 μW Monolithic CMOS Photoplethysmographic Sensor Operating with 2 μW LED Power. In Proceedings of the 2019 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 17–21 February 2019; pp. 290–291.

- Marefat, F.; Erfani, R.; Kilgore, K.L.; Mohseni, P. A 280 µW 108 dB DR Readout IC with Wireless Capacitive Powering Using a Dual-Output Regulating Rectifier for Implantable PPG Recording. In Proceedings of the 2020 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 412–414. [Google Scholar]

- Lin, Q.; Xu, J.; Song, S.; Breeschoten, A.; Konijnenburg, M.; Van Hoof, C.; Tavernier, F.; Van Helleputte, N. A 119 dB Dynamic Range Charge Counting Light-to-Digital Converter For Wearable PPG/NIRS Monitoring Applications. IEEE Trans. Biomed. Circuits Syst. 2020, 14, 800–810. [Google Scholar] [CrossRef] [PubMed]

- Lin, Q.; Song, S.; Wegberg, R.V.; Konijnenburg, M.; Biswas, D.; Hoof, C.V.; Tavernier, F.; Helleputte, N.V. A 28 μW 134 dB DR 2nd-Order Noise-Shaping Slope Light-to-Digital Converter for Chest PPG Monitoring. In Proceedings of the 2021 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021; pp. 390–392. [Google Scholar]

| [7] | [9] | [10] | [8] | [12] | [13] | [14] | |

|---|---|---|---|---|---|---|---|

| Technology (nm) | 130 | 180 | 65 | 130 | 55 | 180 | 180 |

| Supply (V) | 1.2/2.5 | 1.8 | 0.8 | 0.6/1.2/3.3 | 1.2 | 1.8 | 1.8 |

| Architecture | ∆2∑ | ∆∑2 | ∆2∑ | ∆ | ∆2∑ | 2nd order ∆∑ | Gm-C I-∆∑ |

| NO. of channel | 64 | - | 16 | 16 | 16 | 16 | 8–24 |

| Zin (MΩ) | <100 | 34 | >26 | 2960 | 663 | 238 | - |

| Input range (mVpp) | - | 720 | 260 | - | 148 | 19 | 14 |

| Input noise (µVrms) | 1.13 | 0.98 | 0.98 | 2.6 | 5.53 1 | 5.55 1 | 3.93 1 |

| Bandwidth (kHz) | 0.5 | 0.1 | 0.5 | 0.5 | 10 | 10 | 10 |

| EDO tolerance (mV) | ±1200 | >±300 | ±130 | ±1500 | ±70 | ±100 | ±100 |

| SNDR (dB) | 72.2 | 66.2 | 66 | 60 | 59.5 | 61.1 | 57.5 |

| Power/channel (μW) | 0.63 | 73.8 | 0.8 | 0.99 | 61.2 | 12.8 | 14.94 |

| Area/channel (mm2) | 5.98 | 0.48 | 0.024 | 0.011 | 0.0077 | 0.02 | 0.0046 |

| [18] | [19] | [22] | [20] | [21] | |

|---|---|---|---|---|---|

| Technology (nm) | 130 | 40 | 55 | 65 | 65 |

| Supply (V) | 1.2A/0.45D 1 | 0.8A/0.6D 1 | 1 | 1.2A/0.7D 1 | 0.8 |

| Fs (Hz) | 5 K | 2.5 M | 1.28 M | 32 K | 400 K |

| Zin (MΩ) | ∞ 2 | 0.22 | 13.3 3 | 4 | - |

| Input range (mVpp) | 50 | 100 | 300 | 250 | 1800 |

| Input noise (nV/√Hz) | 95 | 36 | 95 | 53 | |

| Bandwidth (kHz) | 0.2 | 10 | 10 | 0.5 | 2.5 |

| SNDR (dB) | 76 | 78.5 | 80.4 | 89.2 | 92.1 |

| CMRR (dB) | 66 | 83 | 76 | 98 | 80–93 |

| Power (μW) | 7 | 4.5 | 6.5 | 3.2 | 4.4 |

| Area (mm2) | 0.135 | 0.025 | 0.078 | 0.08 | 0.1 |

| FOM 4 (dB) | 150.5 | 172 | 172.3 | 171.2 | 179.6 |

| [33] | [34] | [35] | [36] | |

|---|---|---|---|---|

| Technology (nm) | 180 | 180 | 180 | 180 |

| Supply (V) | 1.8 | 1.2 | 3.3 | 1.8A/3.3D 1 |

| Pulse Frequency (Hz) | 165 | 4–128 | 40–100 | 40 |

| LED Duty cycle | 0.7% | - | 0.0175–1.75% | 0.07% |

| LED Power (μW) | 120–1125 | 43–1200 | 16–520 | 1.97 2 |

| AFE Power (μW) | 216 | 172 | 27.4 | 2.63 |

| Area (mm2) | 1.84 | 10 | 1.51 | 20 |

| [31] | [37] | [38] | [39] | |

|---|---|---|---|---|

| Technology (nm) | 180 | 180 | 180 | 180 |

| Supply (V) | 1A/2.5D 1 | 1.5A/2.5D 1 | 1.2/3.3 1 | 1.2A/3.3D 1 |

| Amb. Remove (μA) | 28.2 | 25.6 2 | 50 | 50 |

| Architecture | LDC (ISDM) | LDC (ISDM) | LDC (Slope) | LDC (NS-Slope) |

| Input range (μA) | 51.2 | 51.2 | 200 | 200 |

| Pulse Frequency (Hz) | 100 | 250 | 512 | 2048 |

| Noise BW | 0.5–10 | 0.5–10 | - | 0.5–20 |

| DR (dB) | 92.7 | 108.2 | 119 | 134 |

| LED Duty cycle | 10.24% 3 | 3.2% | 1% | 1% |

| LED Power (μW) | 1950 | 264 | 107 | 305 |

| AFE Power (μW) | 8.1 | 15.7 | 89 | 28 |

| Area (mm2) | 4.8 | - | 7 4 | 8.4 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhou, Y.; Song, S.; Wang, S.; Wan, Y.; Yang, T.; Yu, X.; Zhao, M. A Review on Direct Digital Conversion Techniques for Biomedical Signal Acquisition. Electronics 2023, 12, 2676. https://doi.org/10.3390/electronics12122676

Zhou Y, Song S, Wang S, Wan Y, Yang T, Yu X, Zhao M. A Review on Direct Digital Conversion Techniques for Biomedical Signal Acquisition. Electronics. 2023; 12(12):2676. https://doi.org/10.3390/electronics12122676

Chicago/Turabian StyleZhou, Yizhao, Shuang Song, Shiwei Wang, Yalong Wan, Tian Yang, Xiaopeng Yu, and Menglian Zhao. 2023. "A Review on Direct Digital Conversion Techniques for Biomedical Signal Acquisition" Electronics 12, no. 12: 2676. https://doi.org/10.3390/electronics12122676

APA StyleZhou, Y., Song, S., Wang, S., Wan, Y., Yang, T., Yu, X., & Zhao, M. (2023). A Review on Direct Digital Conversion Techniques for Biomedical Signal Acquisition. Electronics, 12(12), 2676. https://doi.org/10.3390/electronics12122676