GPR-Based Framework for Statistical Analysis of Gate Delay under NBTI and Process Variation Effects

Abstract

1. Introduction

- Derive an abstract expression related to gate delay. From the expression, the main factors affecting the variation of gate delay are explicit, and the predictor variables and targets of ML can be determined easily. Using the ML model, we can eliminate the time-consuming SPICE simulations by the traditional process.

- Apply the ML model to a fast Monte–Carlo simulation. Our goal is not only to predict the individual outcome for a specified set of input features but also to evaluate the distribution of gate delay from numerous outputs. With the ML model, a predicting process can be completed with fast runtime, which enables the designers to evaluate the statistical characteristics of gate delay in a Monte-Carlo fashion.

2. Background and Related Work

2.1. NBTI Degradation

2.2. Process Variations

2.3. Explicit Analytical Model

2.3.1. Explicit Analytical Model

2.3.2. Implicit Analytical Model

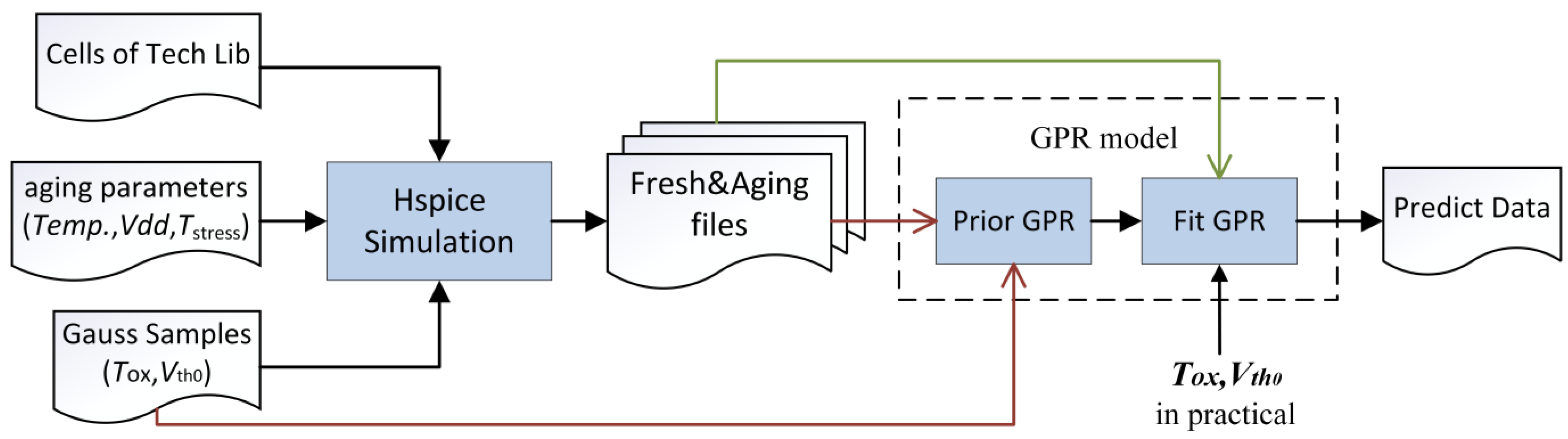

3. SGDE: GPR-Based Framework for Statistical Analysis of Gate Delay under NBTI and Process Variation Effects

3.1. The Effect of PV on NBTI

- Compared with the result of single variation (shown in Table 2), the combination of ( + ) or (+) has the same effect on the variation of .

- Compared with the result of single variation, when the combination of (+) is considered, the standard deviation of ∆ will increase by nearly 8%. In this context, NBTI and the combined PV of (+) have become the most prominent effects able to affect the statistical characteristics of .

| PV Sources | μ (mV) | σ (mV) |

|---|---|---|

| Tox + Vth0 | 59.1 | 2.4921 |

| Tox + XL | 59.1 | 2.3026 |

| Tox + XW | 59.1 | 2.3013 |

3.2. Problem Formulation of Gate Delay

3.3. GPR: An Efficiency Predictive Model

3.3.1. Introduction of GPR

3.3.2. Use of GPR in NBTI and Process Variation-Aware Gate Delay Estimation

3.4. SGDE: A Framework for Statistical Analysis of Gate Delay

4. Numerical Experiment

4.1. Experiment Setup

4.2. Experiment Result

4.2.1. Kernel Selection of GPR Model

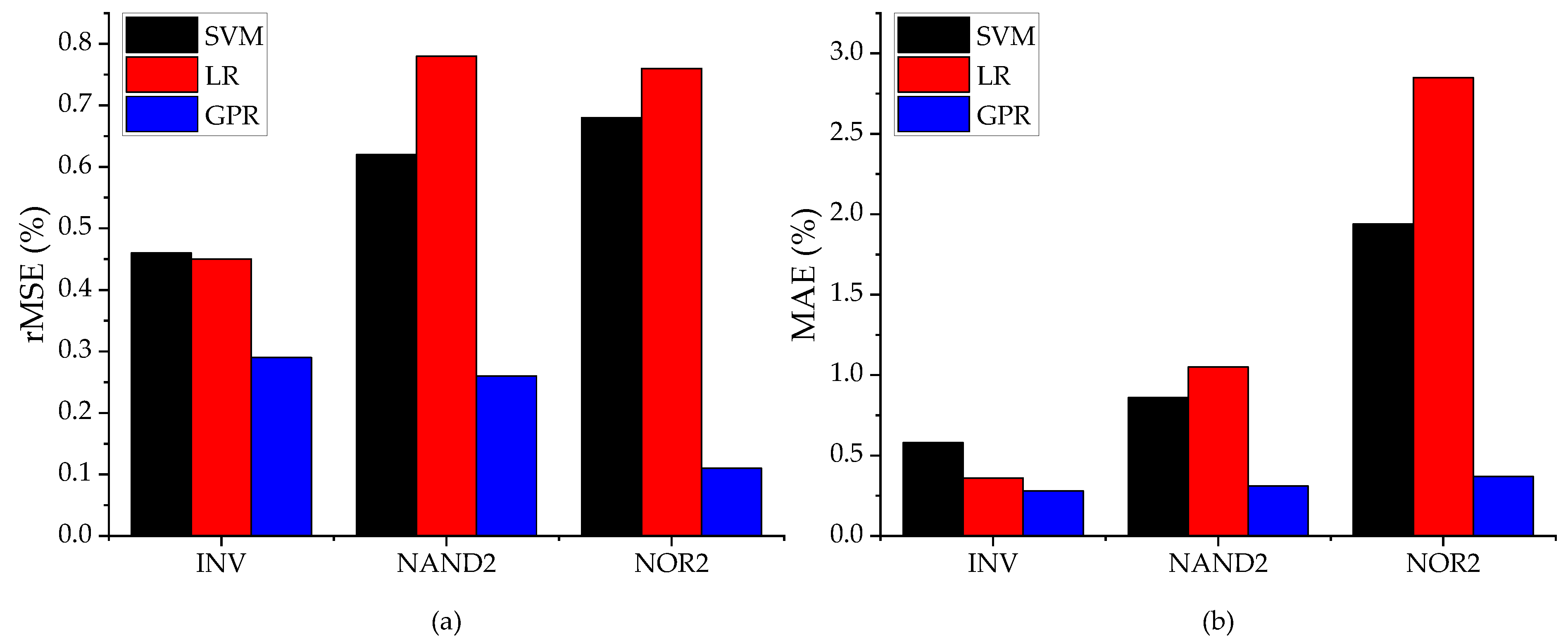

4.2.2. Accuracy Comparation with SVM and LR Model

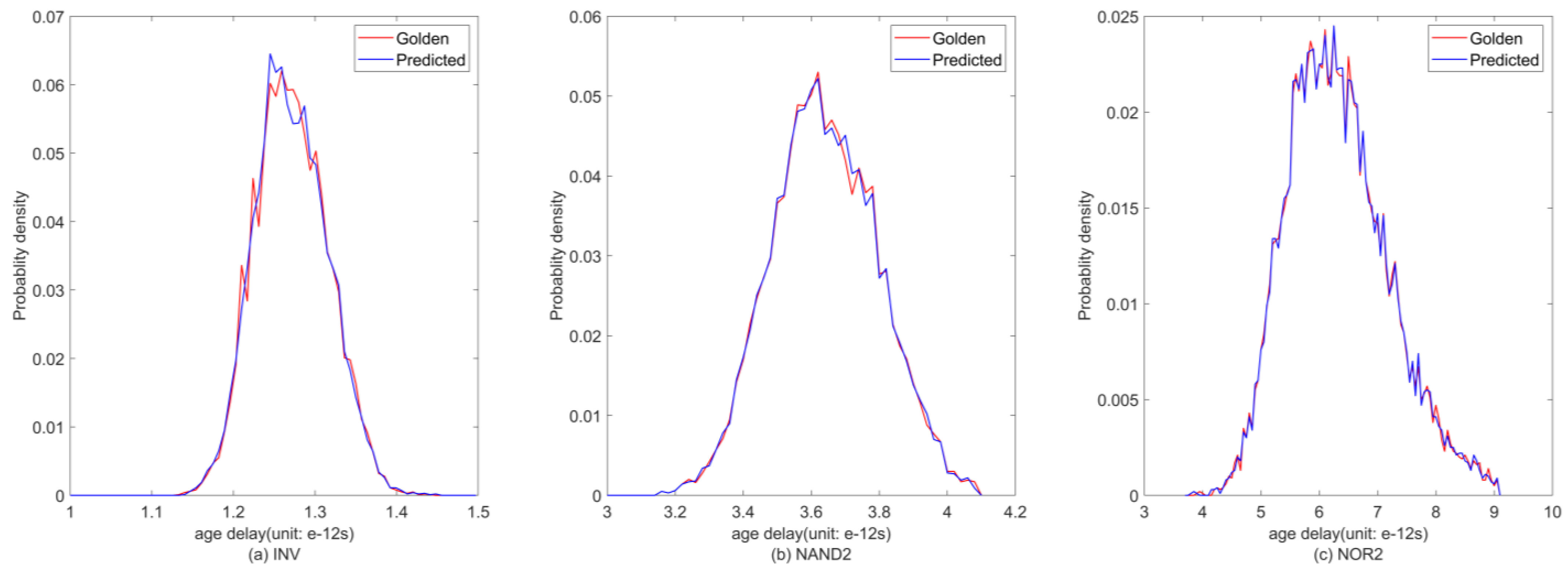

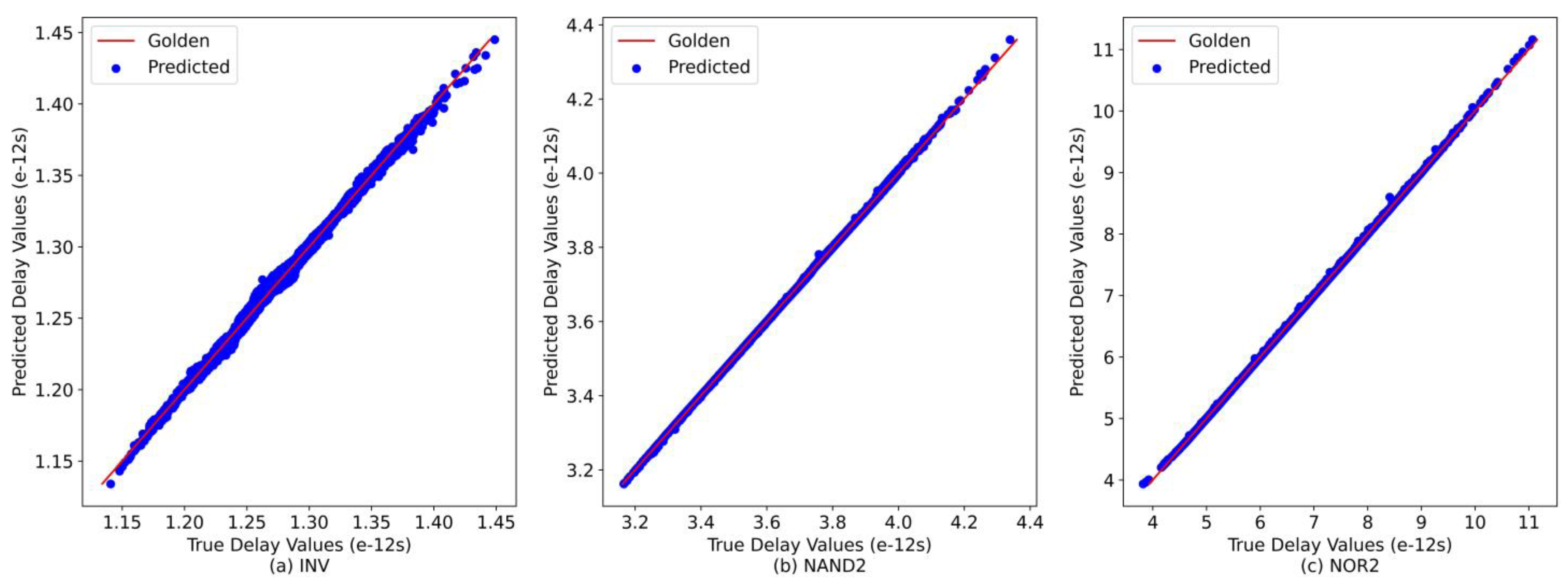

4.2.3. Verification of the SGED Framework

4.2.4. Accuracy Comparation between SGED and Other Literature

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Khalil, K.; Eldash, O.; Kumar, A.; Bayoumi, M. Machine Learning-Based Approach for Hardware Faults Prediction. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 3880–3892. [Google Scholar] [CrossRef]

- Moghaddasi, I.; Nasab, M.E.S.; Kargahi, M. Aging-Aware Instruction-Level Statistical Dynamic Timing Analysis for Embedded Processors. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2020, 28, 433–442. [Google Scholar] [CrossRef]

- Hiroaki, K.; Yukio, M.; Masanori, H.; Takao, O. Comparative study on delay degrading estimation due to NBTI with circuit/instance/transistor-level stress probability consideration. In Proceedings of the 11th International Symposium on Quality Electronic Design, San Jose, CA, USA, 22–24 March 2010; pp. 646–651. [Google Scholar]

- Copetti, T.; Medeiros, G.; Poehls, L.B.; Vargas, F.; Kostin, S.; Jenihhin, M.; Raik, J.; Ubar, R. Gate-level modelling of NBTI-induced delays under process variations. In Proceedings of the 2016 17th Latin-American Test Symposium (LATS), Foz do Iguacu, Brazil, 6–8 April 2016; pp. 75–80. [Google Scholar]

- Yinghai, L.; Li, S.; Hai, Z.; Hengliang, Z.; Fan, Y.; Xuan, Z. Statistical reliability analysis under process variation and aging effects. In Proceedings of the 2009 46th ACM/IEEE Design Automation Conference, San Francisco, CA, USA, 26–31 July 2009; pp. 514–519. [Google Scholar]

- Naphade, T.; Goel, N.; Nair, P.R.; Mahapatra, S. Investigation of stochastic implementation of reaction diffusion (RD) models for NBTI related interface trap generation. In Proceedings of the 2013 IEEE International Reliability Physics Symposium, Anaheim, CA, USA, 14–18 April 2013; pp. XT.5.1–XT.5.11. [Google Scholar]

- Vattikonda, R.; Wang, W.; Cao, Y. Modeling and minimization of PMOS NBTI effect for robust naometer design. In Proceedings of the 2006 Design Automation Conference, San Francisco, CA, USA, 24–28 July 2006; pp. 1047–1052. [Google Scholar]

- Bhardwaj, S.; Wang, W.; Vattikonda, R.; Cao, Y.; Vrudhula, S. Predictive Modeling of the NBTI Effect for Reliable Design. In Proceedings of the IEEE Custom Integrated Circuits Conference 2006, San Jose, CA, USA, 10–13 September 2006; pp. 189–192. [Google Scholar]

- Siddiqua, T.; Gurumurthi, S.; Stan, M.R. Modeling and analyzing NBTI in the presence of Process Variation. In Proceedings of the 2011 12th International Symposium on Quality Electronic Design, Santa Clara, CA, USA, 14–16 March 2011; pp. 1–8. [Google Scholar]

- Li, B.; Hashimoto, M.; Schlichtmann, U. From Process Variations to Reliability: A Survey of Timing of Digital Circuits in the Nanometer Era. IPSJ Trans. Syst. LSI Des. Methodol. 2018, 11, 2–15. [Google Scholar] [CrossRef][Green Version]

- Khalid, U.; Mastrandrea, A.; Olivieri, M. Effect of NBTI/PBTI aging and process variations on write failures in MOSFET and FinFET flip-flops. Microelectron. Reliab. 2015, 55, 2614–2626. [Google Scholar] [CrossRef]

- Han, S.; Kim, J. NBTI-aware statistical timing analysis framework. In Proceedings of the 23rd IEEE International SOC Conference, Las Vegas, NV, USA, 27–29 September 2010; pp. 158–163. [Google Scholar]

- Kleeberger, V.B.; Graeb, H.; Schlichtmann, U. Predicting future product performance: Modeling and evaluation of standard cells in FinFET technologies. In Proceedings of the 50th ACM/EDAC/IEEE Design Automation Conference (DAC), San Francisco, CA, USA, 29 May–7 June 2013; pp. 1–6. [Google Scholar]

- Alpaydin, E. Introduction to Machine Learning, 4th ed.; MIT Press: Cambridge, MA, USA, 2020. [Google Scholar]

- Geyik, C.S.; Zhang, Z.; Aygün, K.; Aberle, J.T. Machine Learning for Evaluating the Impact of Manufacturing Process Variations in High-Speed Interconnects. In Proceedings of the 2021 22nd International Symposium on Quality Electronic Design (ISQED), Santa Clara, CA, USA, 7–9 April 2021; pp. 160–163. [Google Scholar]

- Tripathi, J.N.; Vaghasiya, H.; Junjariya, D.; Chordia, A. Machine Learning Techniques for Modeling and Performance Analysis of Interconnects. IEEE Open J. Nanotechnol. 2021, 2, 178–190. [Google Scholar] [CrossRef]

- Nguyen, T.A.; Shi, B.; Ma, H.; Li, E.P.; Chen, X.; Cangellaris, A.C.; Schutt-Ainé, J. Comparative Study of Surrogate Modeling Methods for Signal Integrity and Microwave Circuit Applications. IEEE Trans. Compon. Packag. Manuf. Technol. 2021, 11, 1369–1379. [Google Scholar] [CrossRef]

- Koriyama, T.; Oshio, S.; Kobayashi, T. A speaker adaptation technique for Gaussian process regression based speech synthesis using feature space transform. In Proceedings of the 2016 IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP), Shanghai, China, 20–25 March 2016; pp. 5610–5614. [Google Scholar]

- Li, Z.; Deng, C.; Zhao, B.; Tian, Y.; Huang, Y. Hyperspectral inversion for soil moisture and temperature based on Gaussian process regression. In Proceedings of the 2019 IEEE International Conference on Signal, Information and Data Processing (ICSIDP), Chongqing, China, 11–13 December 2019; pp. 1–4. [Google Scholar]

- Fezai, R.; Mansouri, M.; Bouguila, N.; Nounou, H.; Nounou, M. Reduced Gaussian process regression for fault detection of chemical processes. In Proceedings of the 2019 International Conference on Internet of Things, Embedded Systems and Communications, IINTEC 2019, Gammarth, Tunisia, 20–22 December 2019; pp. 186–191. [Google Scholar]

- Trinchero, R.; Canavero, F. Machine Learning Regression Techniques for the Modeling of Complex Systems: An Overview. IEEE Electromagn. Compat. Mag. 2021, 10, 71–79. [Google Scholar] [CrossRef]

- Gpflow. Available online: https://www.gpflow.org/ (accessed on 11 April 2022).

- Pedregosa, F.; Varoquaux, G.; Gramfort, A.; Michel, V.; Thirion, B.; Grisel, O.; Blondel, M.; Prettenhofer, P.; Weiss, R.; Dubourg, V.; et al. Scikit-learn: Machine Learning in Python. J. Mach. Learn. Res. 2011, 12, 2825–2830. [Google Scholar]

| PV Source | ||

|---|---|---|

| −0.39 V | ||

| 1.485 nm | 0.05 u | |

| XL | 3.5 nm | 0.05 u |

| XW | 18 nm | 0.05 u |

| PV Source | μ (mV) | σ (mV) |

|---|---|---|

| Vth0 | 59.1 | 0.53559 |

| Tox | 59.1 | 2.3012 |

| XL | 59.1 | 2.9589 × 10−3 |

| XW | 59.1 | 1.0208 × 10−3 |

| Golden | Proposed | Abs.E | Golden | Proposed | Abs.E | |

|---|---|---|---|---|---|---|

| INV | 1.2749 | 1.2755 | 0.087% | 0.04413 | 0.04382 | 0.621% |

| NAND | 3.6517 | 3.6540 | 0.026% | 0.15879 | 0.16012 | 0.011% |

| NOR | 6.3836 | 6.3781 | 0.033% | 0.91522 | 0.90518 | 0.583% |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bu, A.; Wang, R.; Jia, S.; Li, J. GPR-Based Framework for Statistical Analysis of Gate Delay under NBTI and Process Variation Effects. Electronics 2022, 11, 1336. https://doi.org/10.3390/electronics11091336

Bu A, Wang R, Jia S, Li J. GPR-Based Framework for Statistical Analysis of Gate Delay under NBTI and Process Variation Effects. Electronics. 2022; 11(9):1336. https://doi.org/10.3390/electronics11091336

Chicago/Turabian StyleBu, Aiguo, Rongke Wang, Shuhao Jia, and Jie Li. 2022. "GPR-Based Framework for Statistical Analysis of Gate Delay under NBTI and Process Variation Effects" Electronics 11, no. 9: 1336. https://doi.org/10.3390/electronics11091336

APA StyleBu, A., Wang, R., Jia, S., & Li, J. (2022). GPR-Based Framework for Statistical Analysis of Gate Delay under NBTI and Process Variation Effects. Electronics, 11(9), 1336. https://doi.org/10.3390/electronics11091336