A 1200 V SiC Trench MOSFET with a Laterally Widened P-Shield Region to Enhance the Short-Circuit Ruggedness

Abstract

:1. Introduction

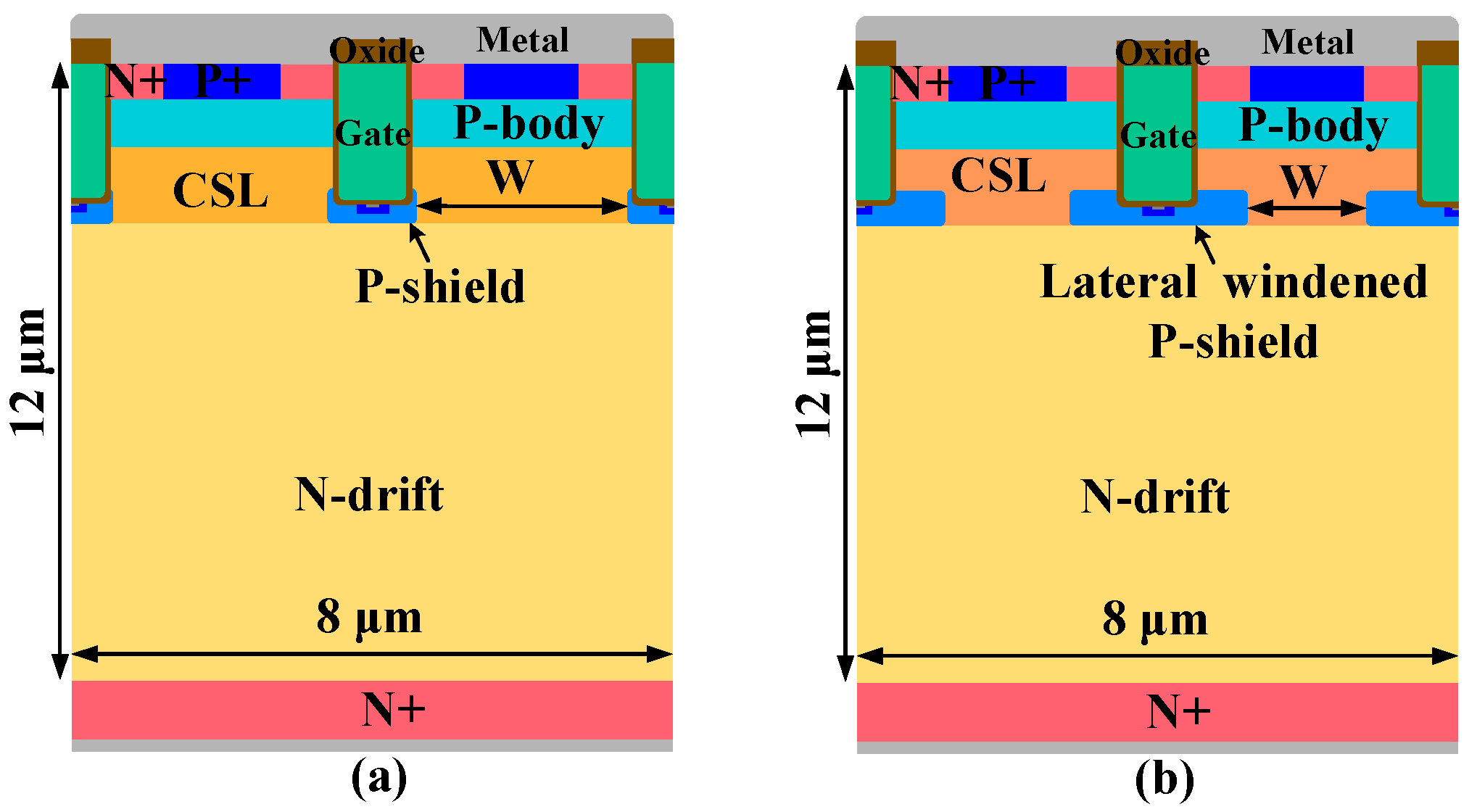

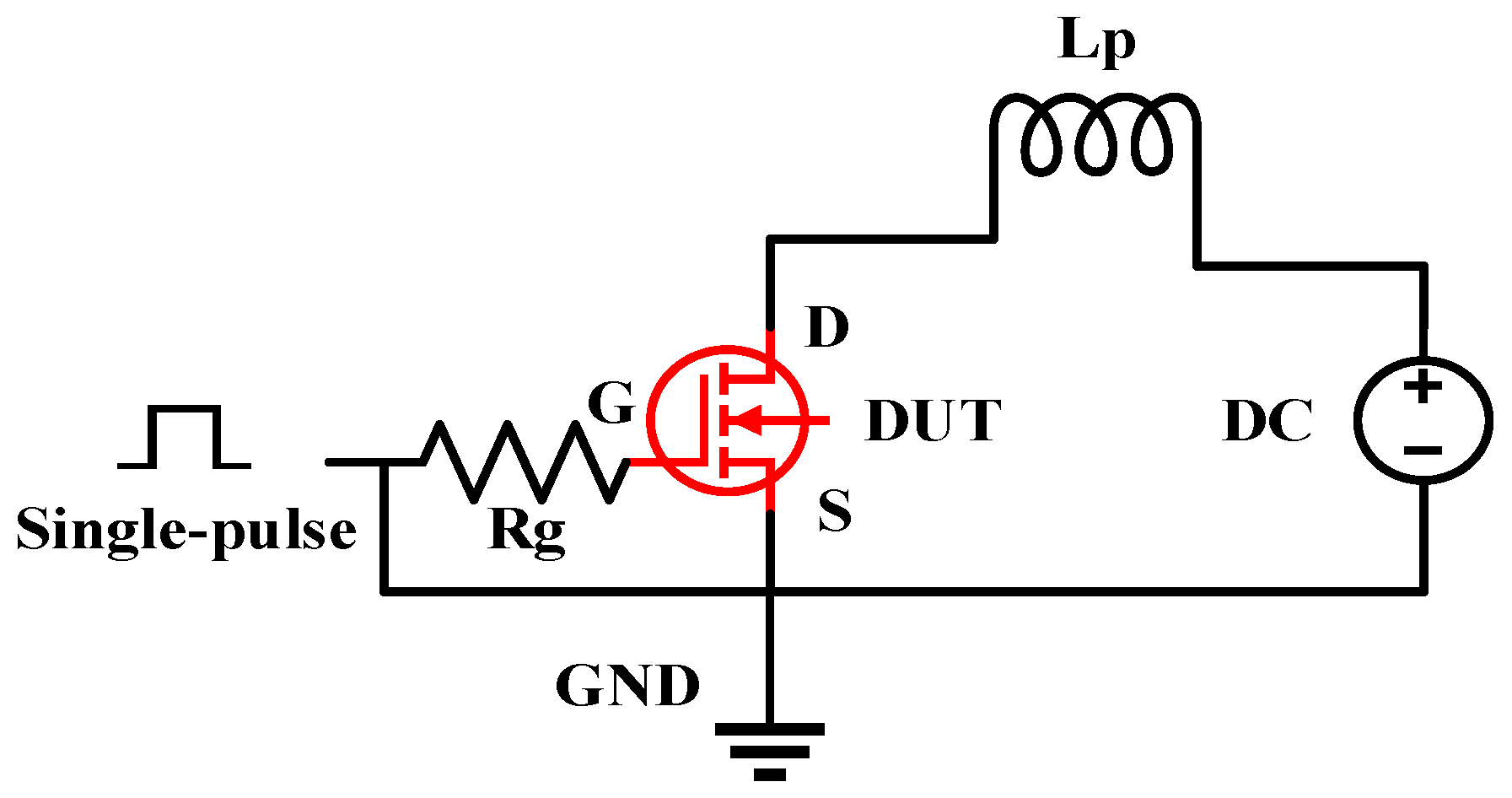

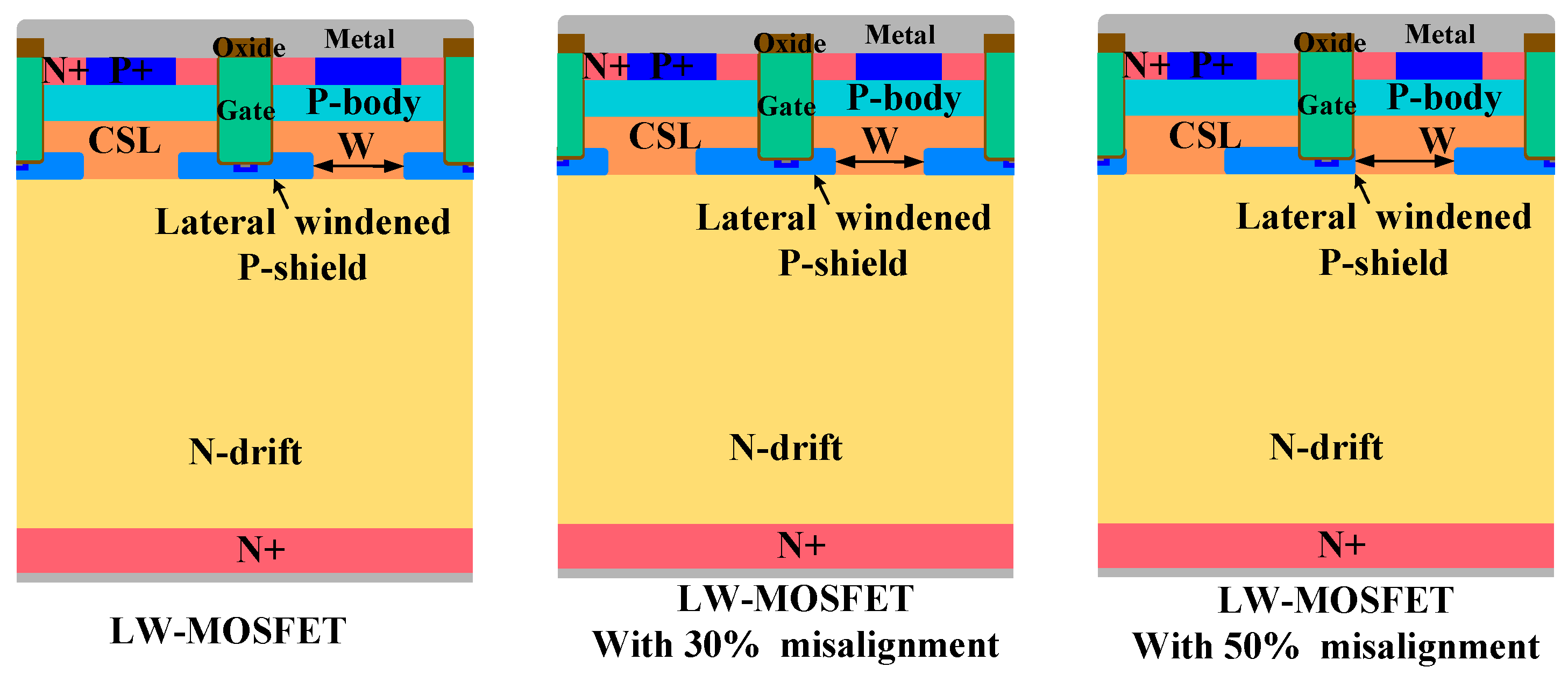

2. Device Structures and Simulation Models

3. Results and Discussion

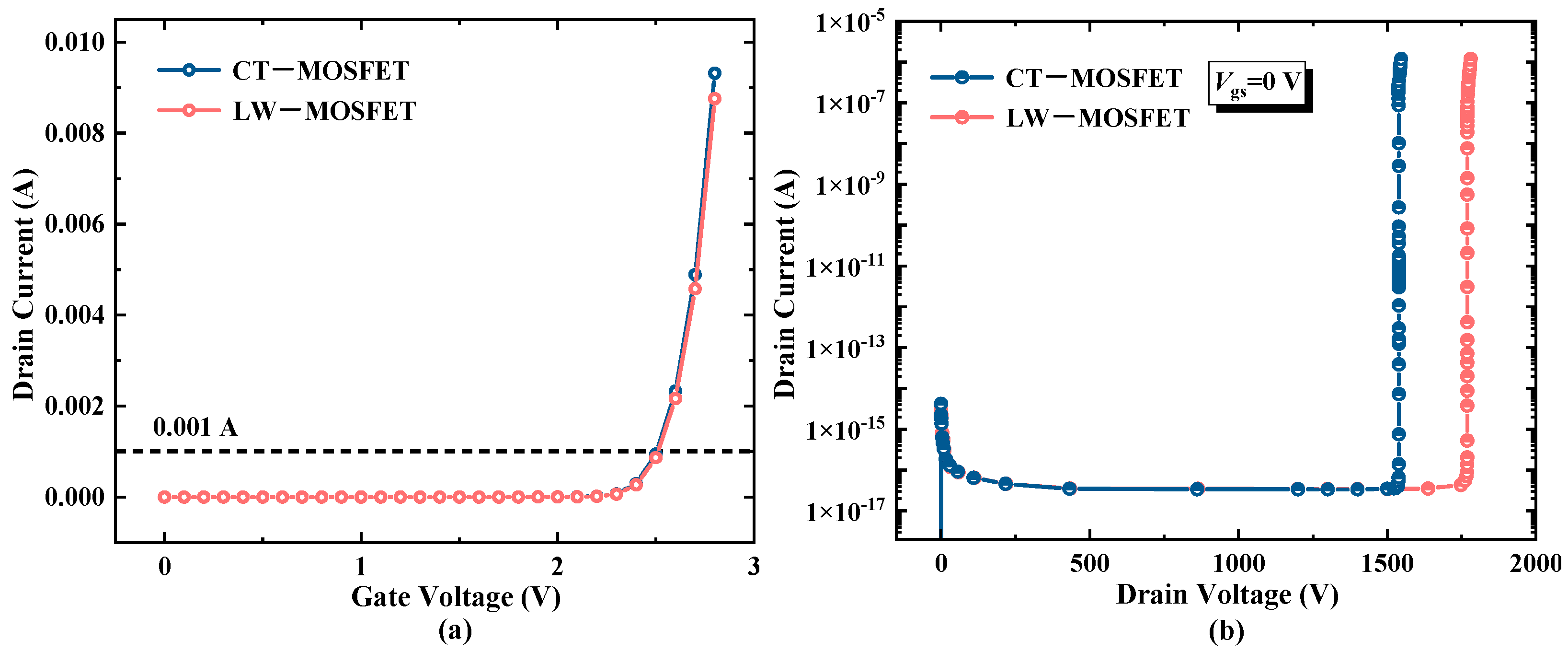

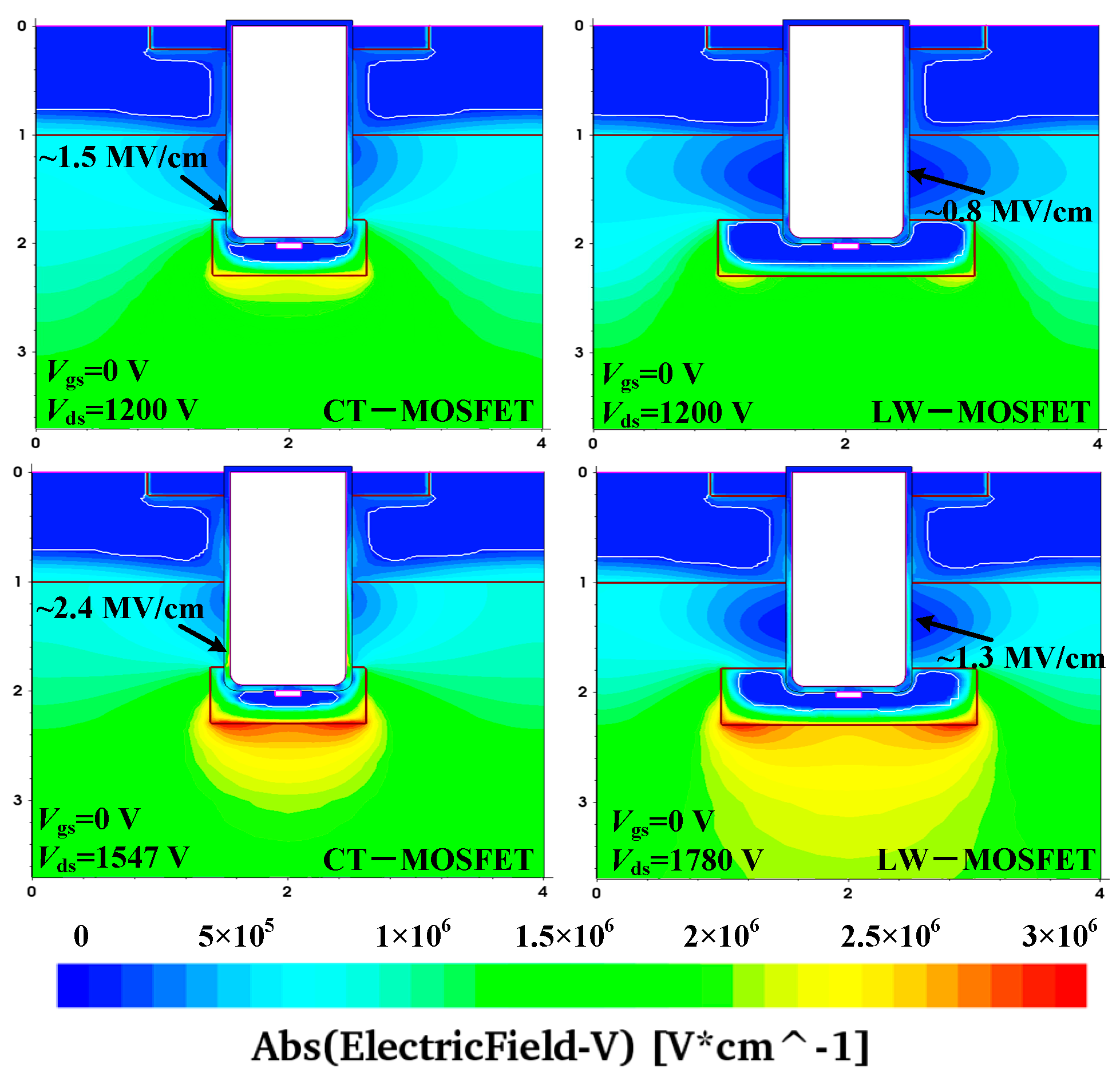

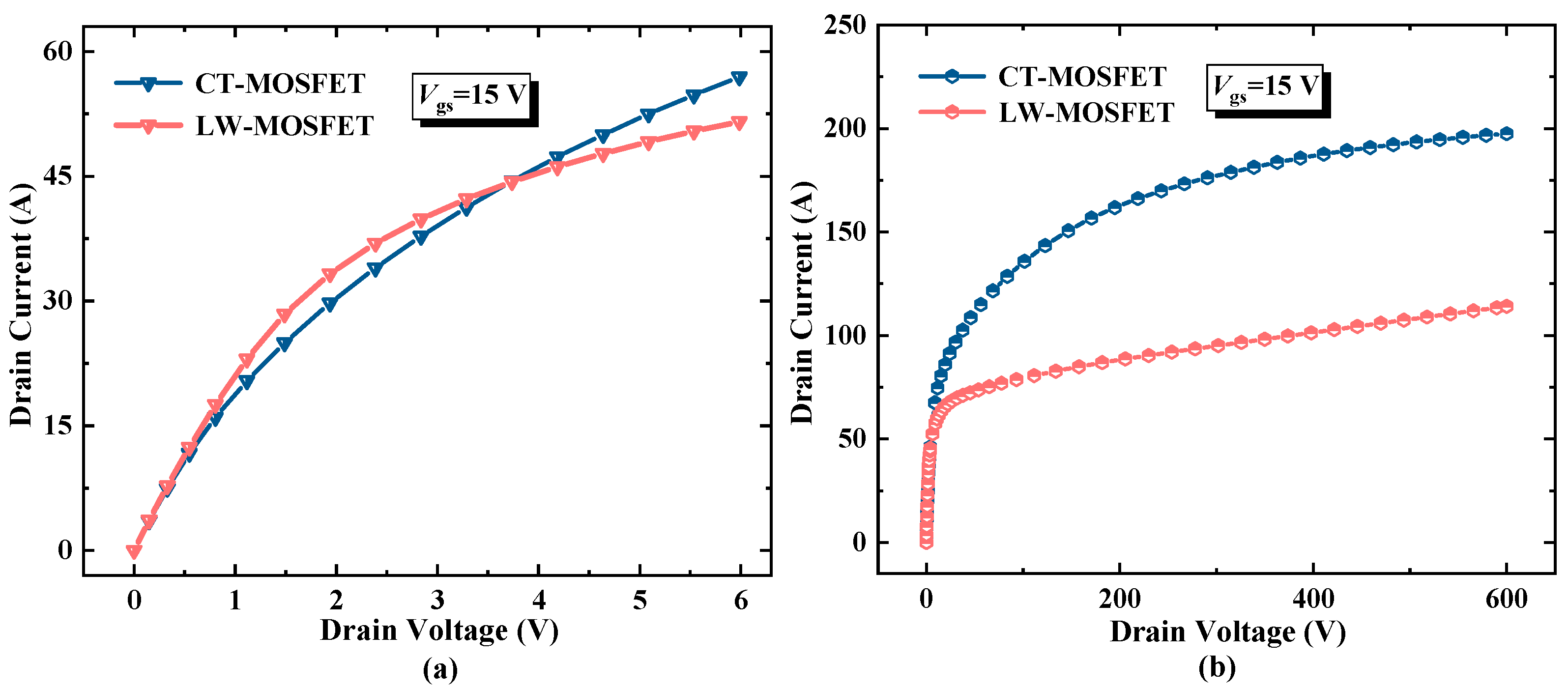

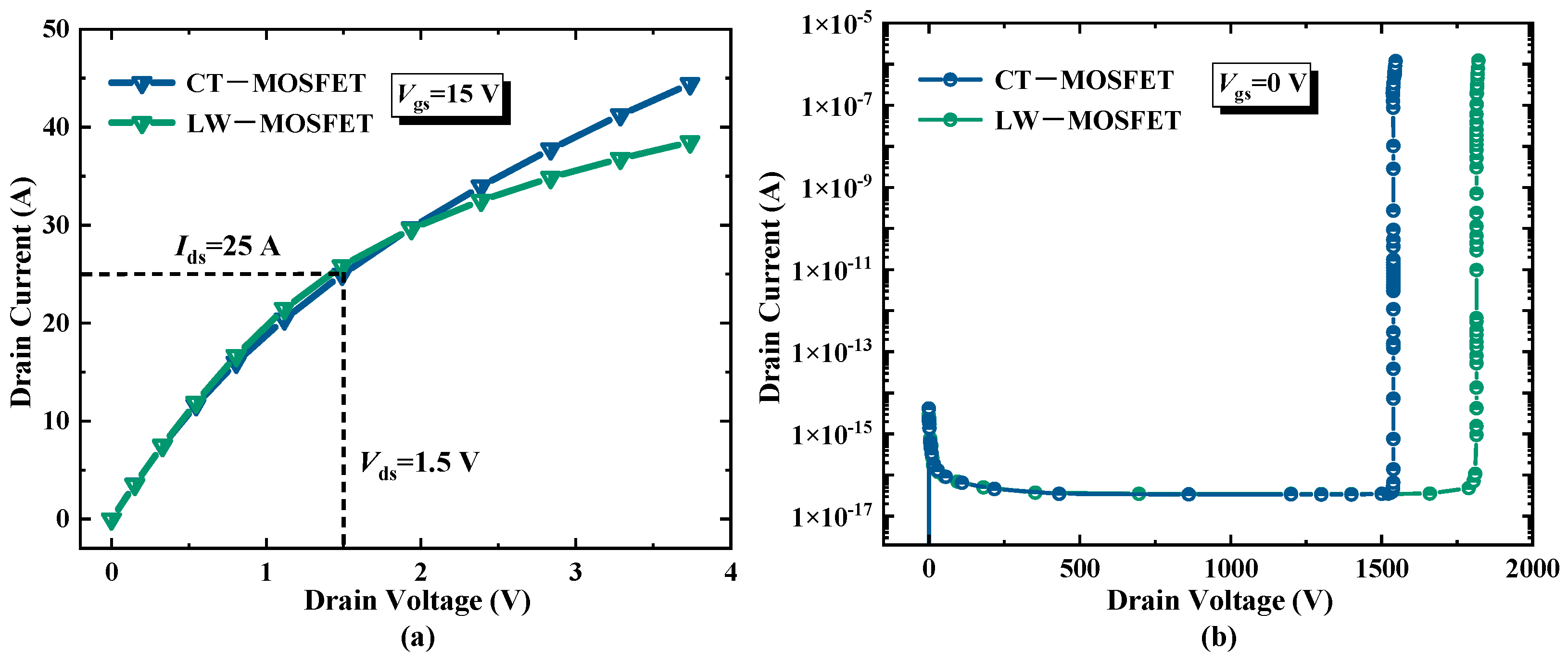

3.1. Static Parameters

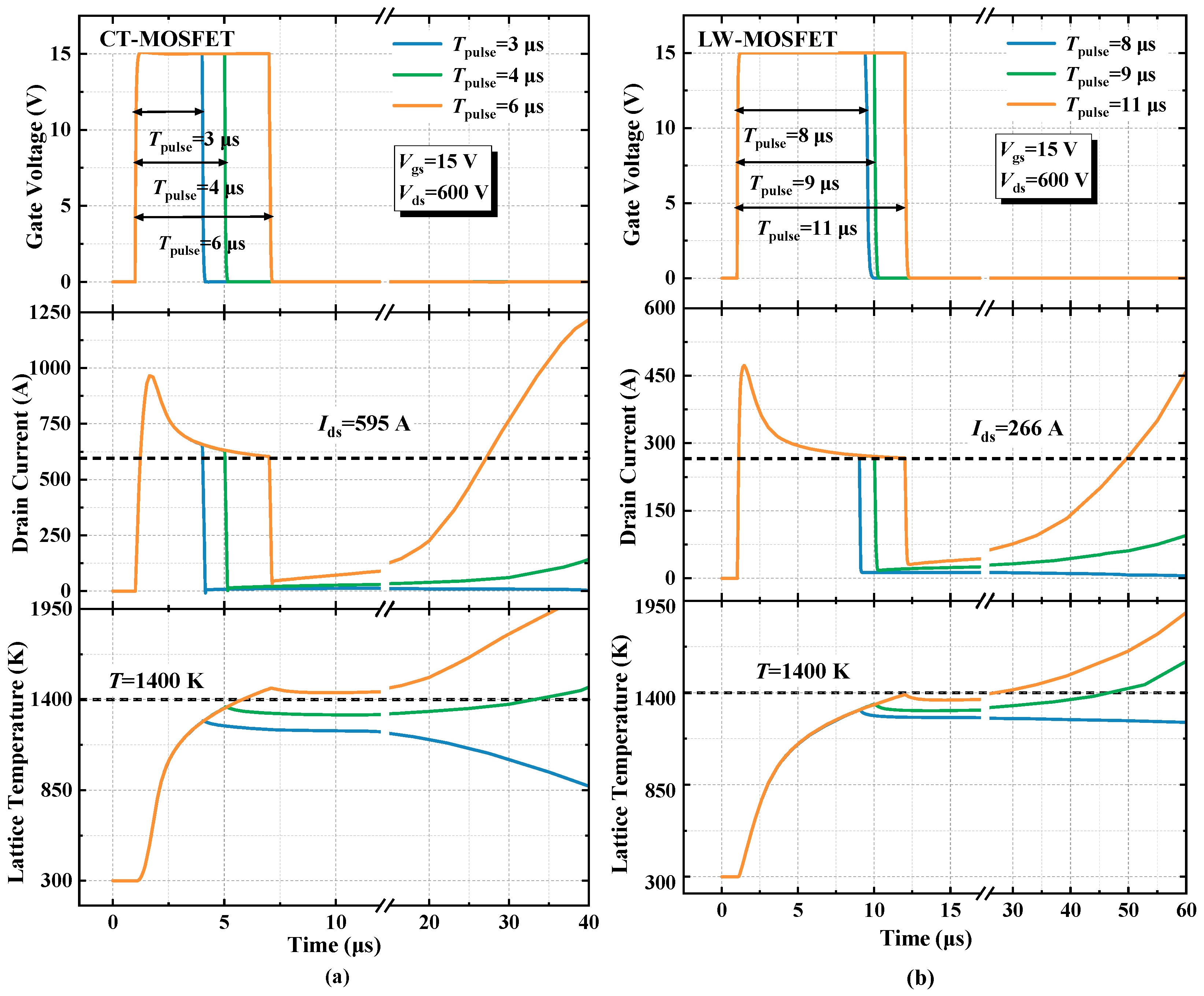

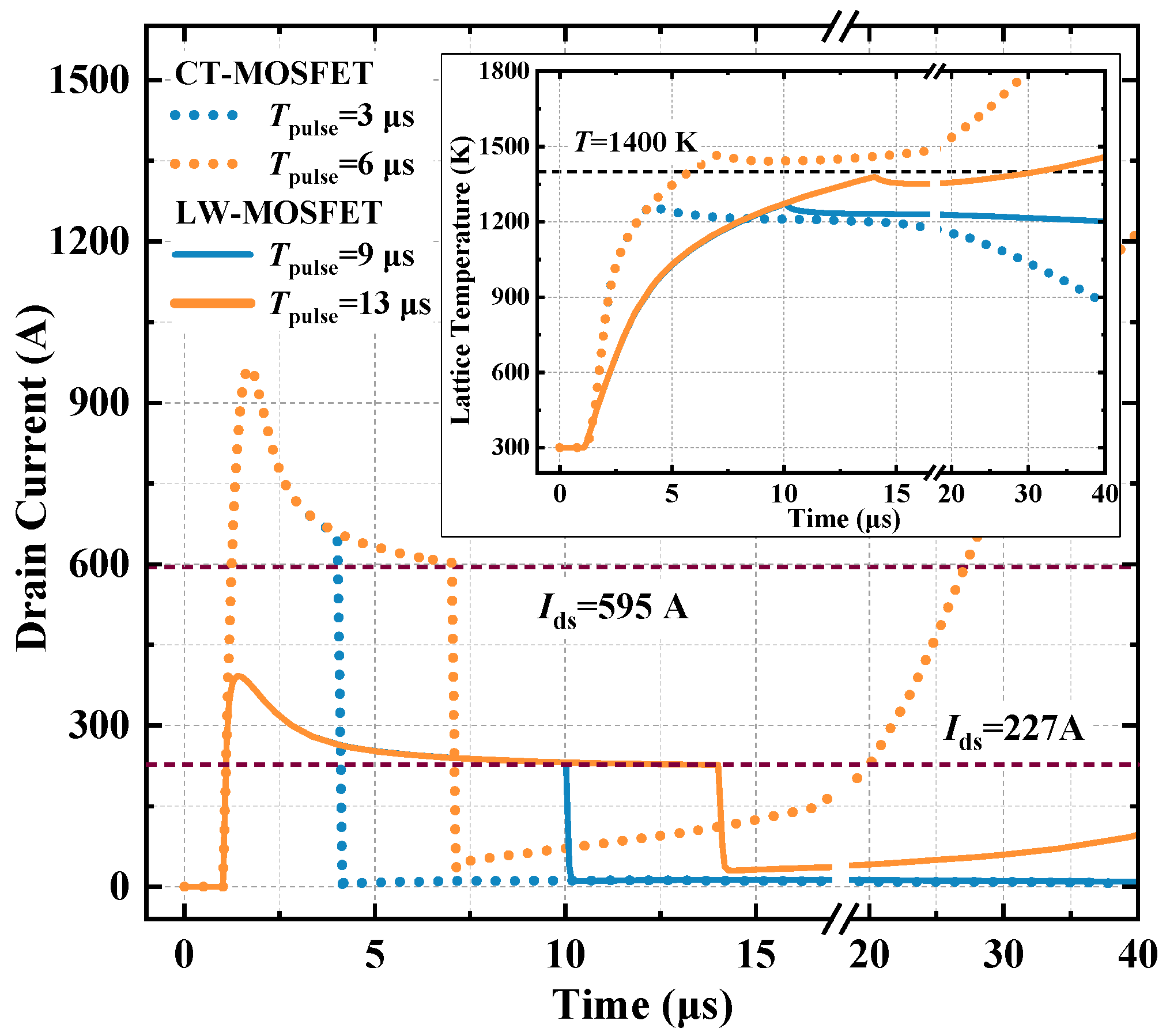

3.2. SC Simulation Results and Analysis

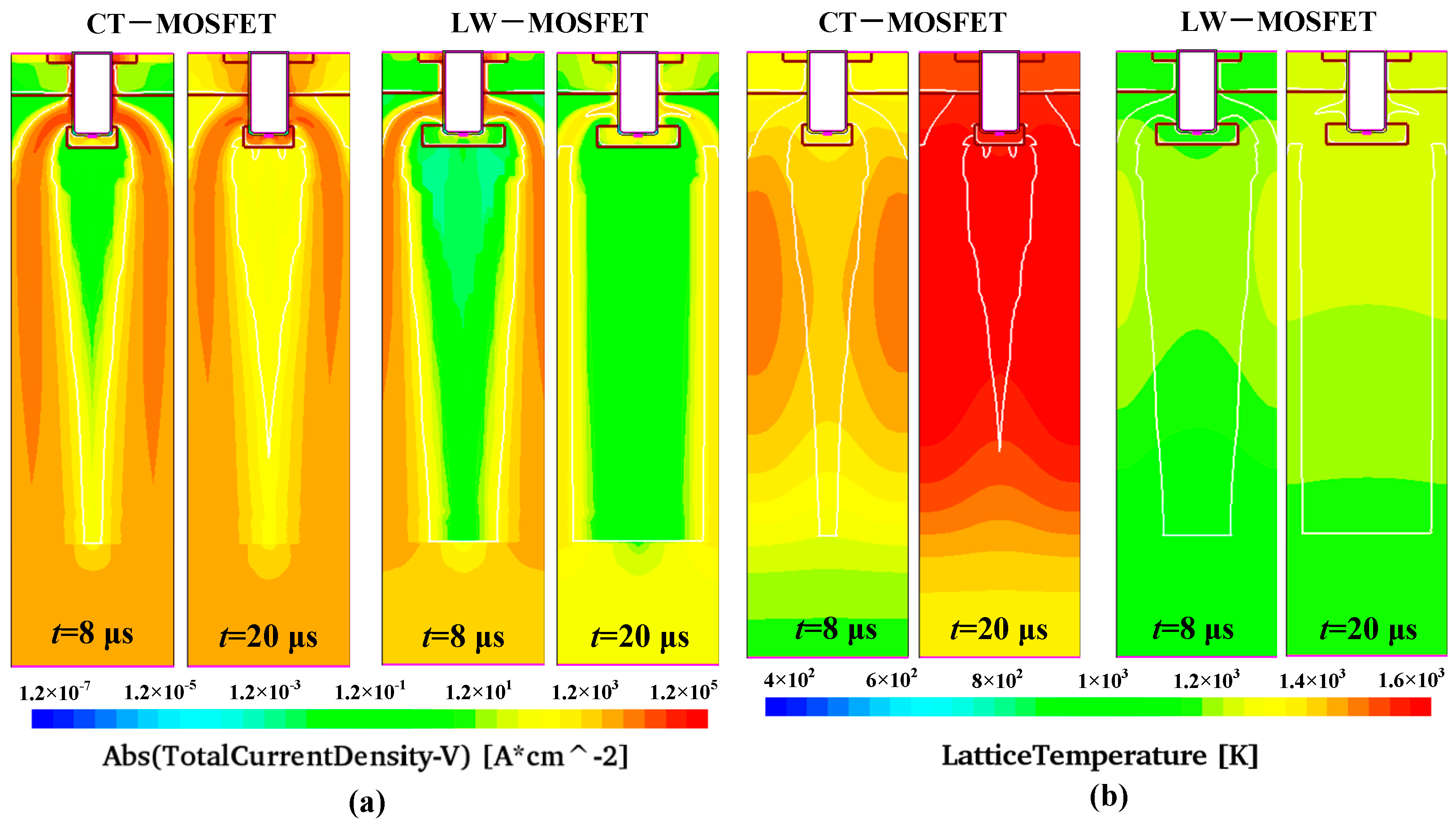

3.3. Analysis of the Internal Physical Mechanism

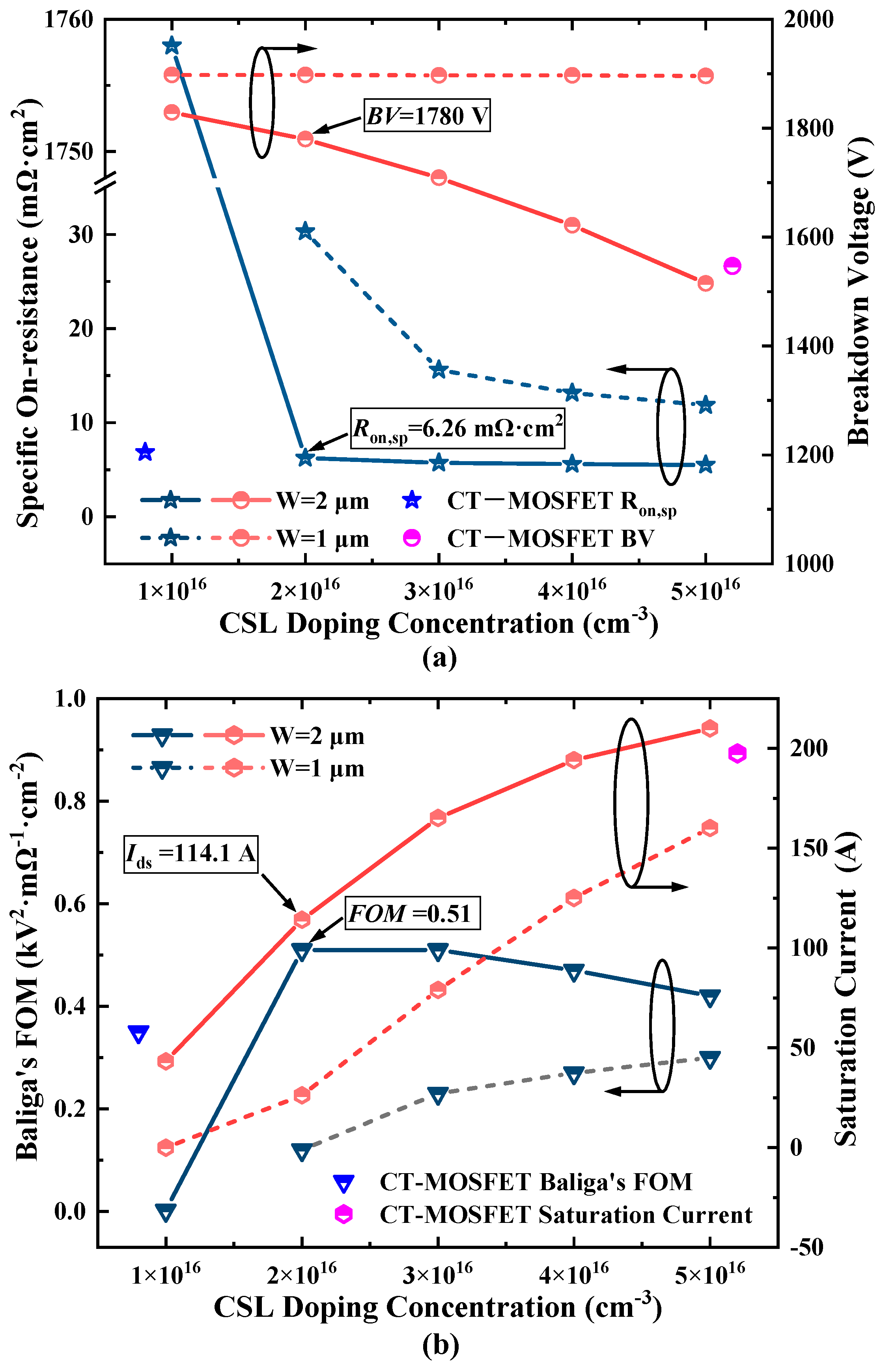

3.4. Structure Parameters Optimization in LW-MOSFET

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Baliga, B.J. Fundamentals of Power Semiconductor Devices; Springer: Boston, MA, USA, 2008. [Google Scholar]

- Kimoto, T.; Cooper, J.A. Fundamentals of Silicon Carbide Technology: Growth, Characterization, Devices and Applications; Wiley: Singapore, 2014. [Google Scholar]

- Ji, S.; Zhang, Z.; Wang, F. Overview of high voltage sic power semiconductor devices: Development and application. CES Trans. Electr. Mach. Syst. 2017, 1, 254–264. [Google Scholar] [CrossRef]

- Tian, K.; Hallén, A.; Qi, J.; Ma, S.; Fei, X.; Zhang, A.; Liu, W. An Improved 4H-SiC Trench-Gate MOSFET With Low ON-Resistance and Switching Loss. IEEE Trans. Electron Devices 2019, 66, 2307–2313. [Google Scholar] [CrossRef]

- Kagawa, Y.; Fujiwara, N.; Sugawara, K.; Tanaka, R.; Fukui, Y.; Yamamoto, Y.; Miura, N.; Imaizumi, M.; Nakata, S.; Yamakawa, S. 4H-SiC Trench MOSFET with Bottom Oxide Protection. Trans. Tech. Publ. 2014, 778–780, 919–922. [Google Scholar] [CrossRef]

- Green, R.; Urciuoli, D.; Lelis, A. Short-circuit robustness testing of SiC MOSFETs. In Proceedings of the 2016 European Conference on Silicon Carbide & Related Materials (ECSCRM), Halkidiki, Greece, 25–29 September 2016. [Google Scholar]

- Terashima, T. Superior performance of SiC power devices and its limitation by self-heating. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016. [Google Scholar]

- Lin, C.; Wu, J.; Xu, H.; Ren, N.; Guo, Q.; Sheng, K. Comparison and Analysis of Short Circuit Performance of 1200V SiC MOSFETs. In Proceedings of the 2020 17th China International Forum on Solid State Lighting & 2020 International Forum on Wide Bandgap Semiconductors (SSLChina: IFWS), Shenzhen, China, 23–25 November 2020. [Google Scholar]

- Wang, J.; Jiang, X. Review and analysis of SiC MOSFETs’ ruggedness and reliability. IET Power Electron. 2020, 13, 445–455. [Google Scholar] [CrossRef]

- Masaki, N.; An, J.; Hiroshi, Y.; Noriyuki, I. Investigation of short-circuit failure mechanisms of SiC MOSFETs by varying DC bus voltage. Jpn. J. Appl. Phys. 2018, 57, 074102. [Google Scholar]

- Zhou, X.; Su, H.; Wang, Y.; Yue, R.; Dai, G.; Li, J. Investigations on the Degradation of 1.2-kV 4H-SiC MOSFETs Under Repetitive Short-Circuit Tests. IEEE Trans. Electron Devices 2016, 63, 4346–4351. [Google Scholar] [CrossRef]

- Wang, J.; Chen, Y.; He, Z.; En, Y.; Xu, X.; Huang, Y.; Geng, K. Investigations on the Short-Circuit Degradation and its Mechanism of 1.2-kV 19-A SiC power MOSFETs. In Proceedings of the 2019 IEEE 26th International Symposium on Physical and Failure Analysis of Integrated Circuits (IPFA), Hangzhou, China, 2–5 July 2019. [Google Scholar]

- Kakarla, B.; Ziemann, T.; Nida, S.; Doenni, E.; Grossner, U. Planar to Trench: Short Circuit Capability Analysis of 1.2 kV SiC MOSFETs. Mater. Sci. Forum 2018, 924, 782–785. [Google Scholar] [CrossRef]

- Cao, L.; Guo, Q.; Sheng, K. Comparative Evaluation of the Short circuit Capability of SiC Planar and Trench Power MOSFET. In Proceedings of the IEEE 2nd International Electrical and Energy Conference (CIEEC), Beijing, China, 4–6 November 2018. [Google Scholar]

- Green, R.; Urciuoli, D.; Lelis, A. Short-circuit robustness of SiC trench MOSFETs. Mater. Sci. Forum 2018, 924, 715–718. [Google Scholar] [CrossRef]

- Okawa, M.; Aiba, R.; Kanamori, T.; Yano, H. Experimental and Numerical Investigations of Short-Circuit Failure Mechanisms for State-of-the-Art 1.2kV SiC Trench MOSFETs. In Proceedings of the 2019 31st International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Shanghai, China, 19–23 May 2019. [Google Scholar]

- Namai, M.; An, J.; Yano, H.; Iwamuro, N. Experimental and numerical demonstration and optimized methods for SiC trench MOSFET short-circuit capability. In Proceedings of the 2017 29th International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Sapporo, Japan, 28 May–1 June 2017. [Google Scholar]

- Mori, Y.; Suto, T.; Suematsu, T.; Shimizu, H.; Watanabe, N.; Miki, H.; Hisamoto, D.; Masuda, T.; Shima, A. Device design to achieve low loss and high short-circuit capability for SiC Trench MOSFET. In Proceedings of the 2021 33th International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Nagoya, Japan, 30 May–3 June 2021. [Google Scholar]

- Yang, T.; Wang, Y.; Yue, R. SiC Trench MOSFET With Reduced Switching Loss and Increased Short-Circuit Capability. IEEE Trans. Electron. Devices 2020, 67, 3685–3690. [Google Scholar] [CrossRef]

- Sentaurus TCAD Tools Version L-2016.03 Synopsys; Mountain View, CA, USA, 2016. Available online: https://www.synopsys.com/silicon/tcad.html (accessed on 27 February 2022).

- Okawa, M.; Kyogoku, S.; Kumazawa, T.; Saito, J.; Morimoto, T.; Takei, M.; Harada, S. Superior Short-Circuit Performance of SiC Superjunction MOSFET. In Proceedings of the 2020 32st International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Vienna, Austria, 13–18 September 2020. [Google Scholar]

- Boige, F.; Richardeau, F.; Lefebvre, S.; Blaquière, J.-M.; Guibaud, G.; Bourennane, A. Ensure an original and safe ‘fail-to-open’ mode in planar and trench power SiC MOSFET devices in extreme short-circuit operation. Microelectron. Rel. 2018, 88, 598–603. [Google Scholar] [CrossRef] [Green Version]

| Parameters | CT-MOSFET | LW-MOSFET |

|---|---|---|

| Trench gate width (μm) | 1 | 1 |

| Trench gate depth (μm) | 2 | 2 |

| N+ source depth (μm) | 0.2 | 0.2 |

| N+/P+ doping (cm−3) | 1 × 1019 | 1 × 1019 |

| Gate oxide thickness (nm) | 50 | 50 |

| P-body depth (μm) | 0.8 | 0.8 |

| P-body doping (cm−3) | 1.5 × 1017 | 1.5 × 1017 |

| N-drift thickness (μm) | 9.7 | 9.7 |

| N-drift doping (cm−3) | 3 × 1015 | 3 × 1015 |

| N-CSL depth (μm) | 1.3 | 1.3 |

| N-CSL doping (cm−3) | 1 × 1016 | 2 × 1016 |

| P-shield depth (μm) | 0.3 | 0.3 |

| P-shield doping (cm−3) | 1 × 1018 | 1 × 1018 |

| W (μm) | 2.8 | 2 |

| Performance Parameters | CT-MOSFET | LW-MOSFET |

|---|---|---|

| BV (V) | 1547 | 1780 |

| Ron, sp (mΩ·cm2) | 6.86 | 6.26 |

| Baliga’s FOM (kV2·mΩ−1·cm−2) | 0.35 | 0.51 |

| Saturation Current (A) (Vds = 600 V) | 197.5 | 114.1 |

| SC Saturation Current (A) | 595 | 266 |

| SCWT (μs) | 3 | 8 |

| W (μm) | Ncsl (cm−3) | BV (V) | Ron, sp (mΩ·cm2) | Baliga’s FOM (kV2·mΩ−1·cm−2) | Saturation Current (A) (Vds = 600 V) |

|---|---|---|---|---|---|

| 2 | 1 × 1016 | 1829 | 1758 | 0.002 | 43.2 |

| 2 × 1016 | 1780 | 6.26 | 0.51 | 114.1 | |

| 3 × 1016 | 1709 | 5.73 | 0.51 | 165.1 | |

| 4 × 1016 | 1622 | 5.6 | 0.47 | 194.1 | |

| 5 × 1016 | 1515 | 5.52 | 0.42 | 210 | |

| 1 | 1 × 1016 | 1898 | Too high | null | null |

| 2 × 1016 | 1898 | 30.32 | 0.12 | 26.2 | |

| 3 × 1016 | 1897 | 15.62 | 0.23 | 79 | |

| 4 × 1016 | 1897 | 13.16 | 0.27 | 125.1 | |

| 5 × 1016 | 1896 | 11.86 | 0.30 | 160.1 | |

| 1 × 1016 | 1898 | Too high | null | null | |

| CT-MOSFET | 1547 | 6.86 | 0.35 | 202.9 | |

| Structure | BV (V) | Ron, sp (mΩ·cm2) | Baliga’s FOM (kV2·mΩ−1·cm−2) | Saturation Current (A) (Vds = 600 V) |

|---|---|---|---|---|

| CT-MOSFET | 1547 | 6.86 | 0.35 | 202.9 |

| LW-MOSFET | 1780 | 6.26 | 0.51 | 114.1 |

| LW-MOSFET with 30% misalignment | 1653 | 6.61 | 0.41 | 120.6 |

| LW-MOSFET with 40% misalignment | 1621 | 7.08 | 0.37 | 118.7 |

| LW-MOSFET with 50% misalignment | 1594 | 8.42 | 0.30 | 115.8 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zuo, X.; Lu, J.; Liu, X.; Bai, Y.; Tian, X.; Cheng, G.; Tang, Y.; Yang, C.; Chen, H. A 1200 V SiC Trench MOSFET with a Laterally Widened P-Shield Region to Enhance the Short-Circuit Ruggedness. Electronics 2022, 11, 1077. https://doi.org/10.3390/electronics11071077

Zuo X, Lu J, Liu X, Bai Y, Tian X, Cheng G, Tang Y, Yang C, Chen H. A 1200 V SiC Trench MOSFET with a Laterally Widened P-Shield Region to Enhance the Short-Circuit Ruggedness. Electronics. 2022; 11(7):1077. https://doi.org/10.3390/electronics11071077

Chicago/Turabian StyleZuo, Xinxin, Jiang Lu, Xinyu Liu, Yun Bai, Xiaoli Tian, Guodong Cheng, Yidan Tang, Chengyue Yang, and Hong Chen. 2022. "A 1200 V SiC Trench MOSFET with a Laterally Widened P-Shield Region to Enhance the Short-Circuit Ruggedness" Electronics 11, no. 7: 1077. https://doi.org/10.3390/electronics11071077

APA StyleZuo, X., Lu, J., Liu, X., Bai, Y., Tian, X., Cheng, G., Tang, Y., Yang, C., & Chen, H. (2022). A 1200 V SiC Trench MOSFET with a Laterally Widened P-Shield Region to Enhance the Short-Circuit Ruggedness. Electronics, 11(7), 1077. https://doi.org/10.3390/electronics11071077