Soft Error Sensitivity Analysis Based on 40 nm SRAM-Based FPGA

Abstract

1. Introduction

2. Device under Test

2.1. Test Board

2.2. Test Chip

2.3. Test Module Analysis

3. SEE Test Methods

3.1. CRAM Test

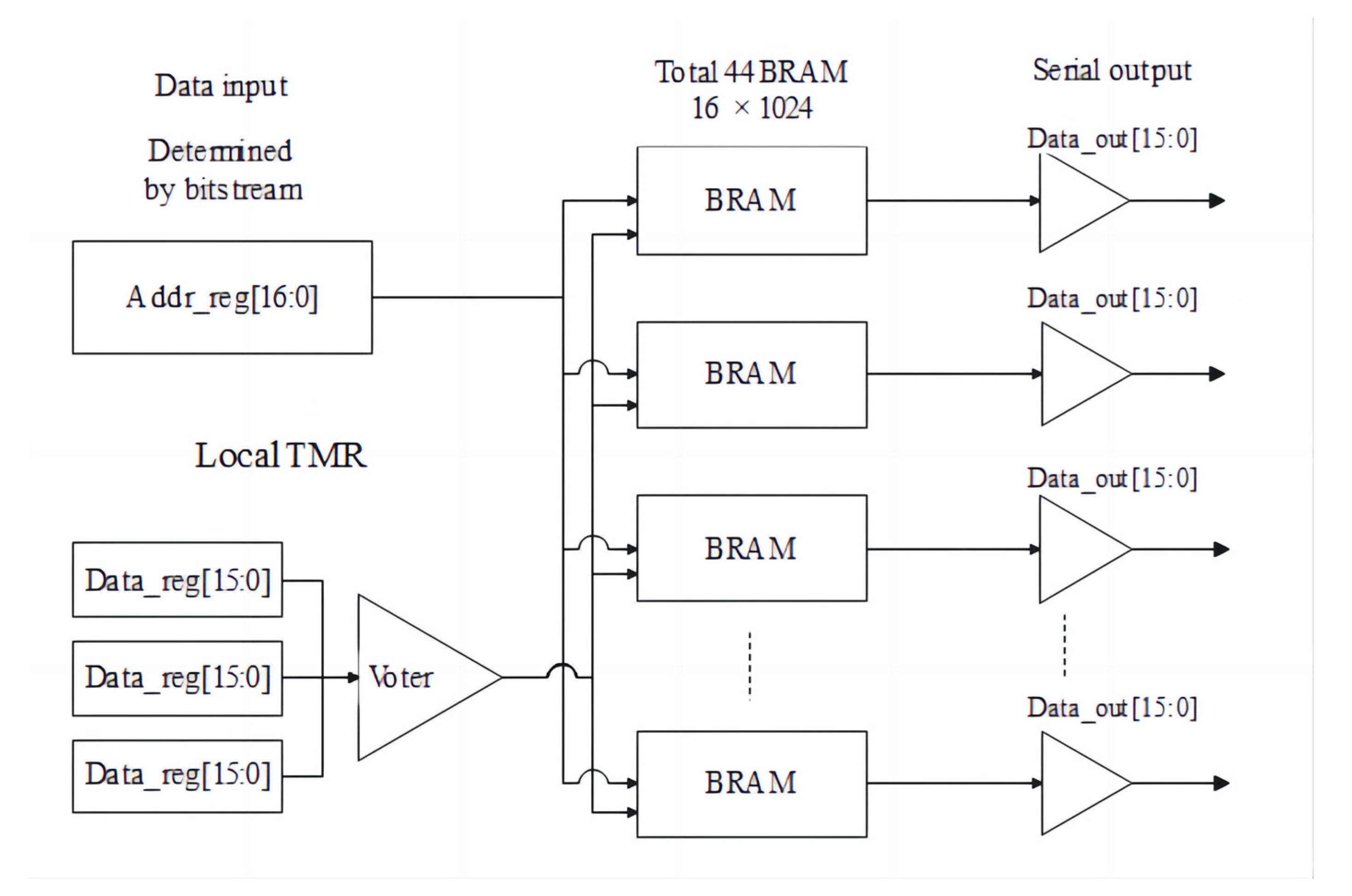

3.2. BRAM Test

3.3. CLM Test

4. SEE Experiments

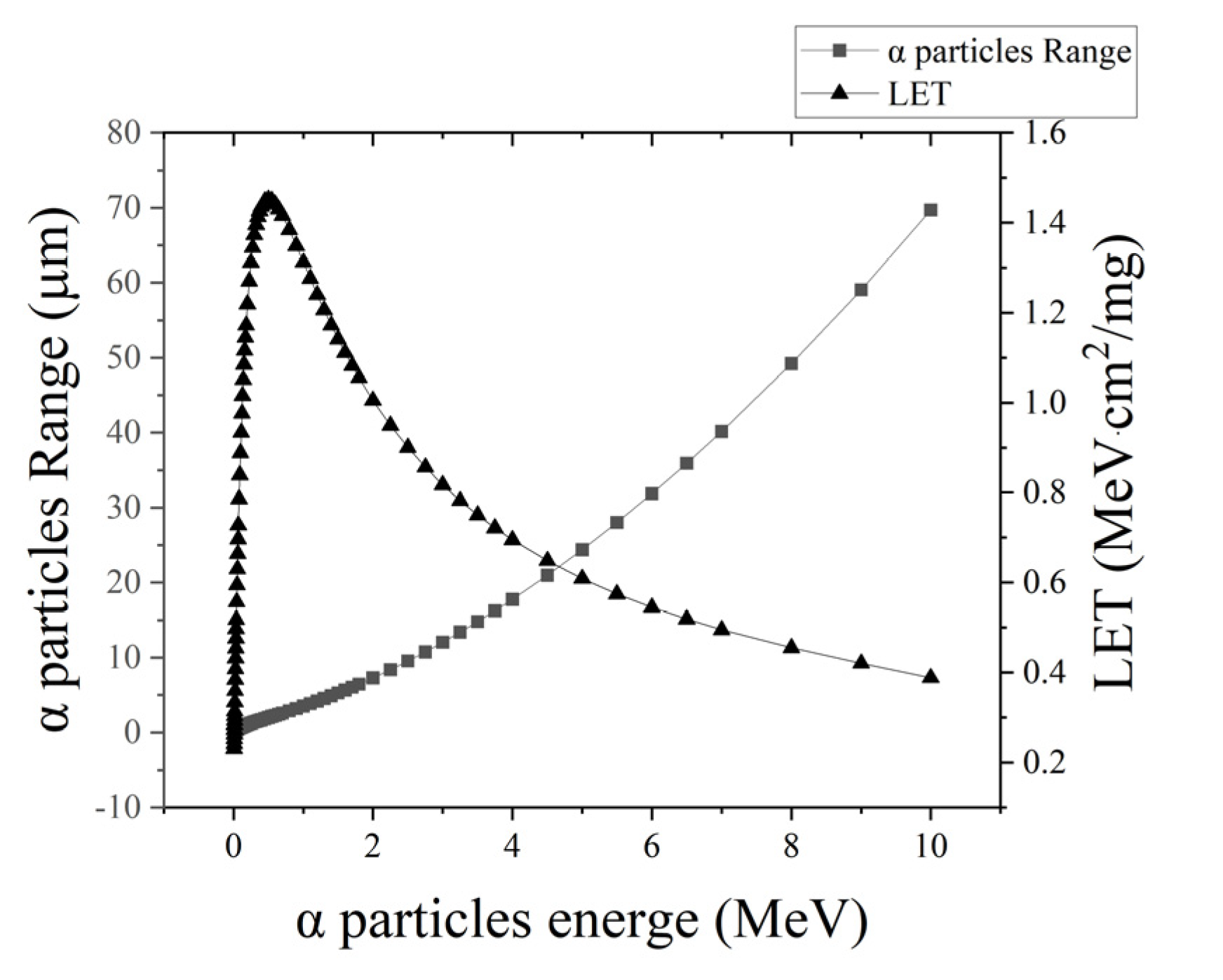

4.1. Radiation Source

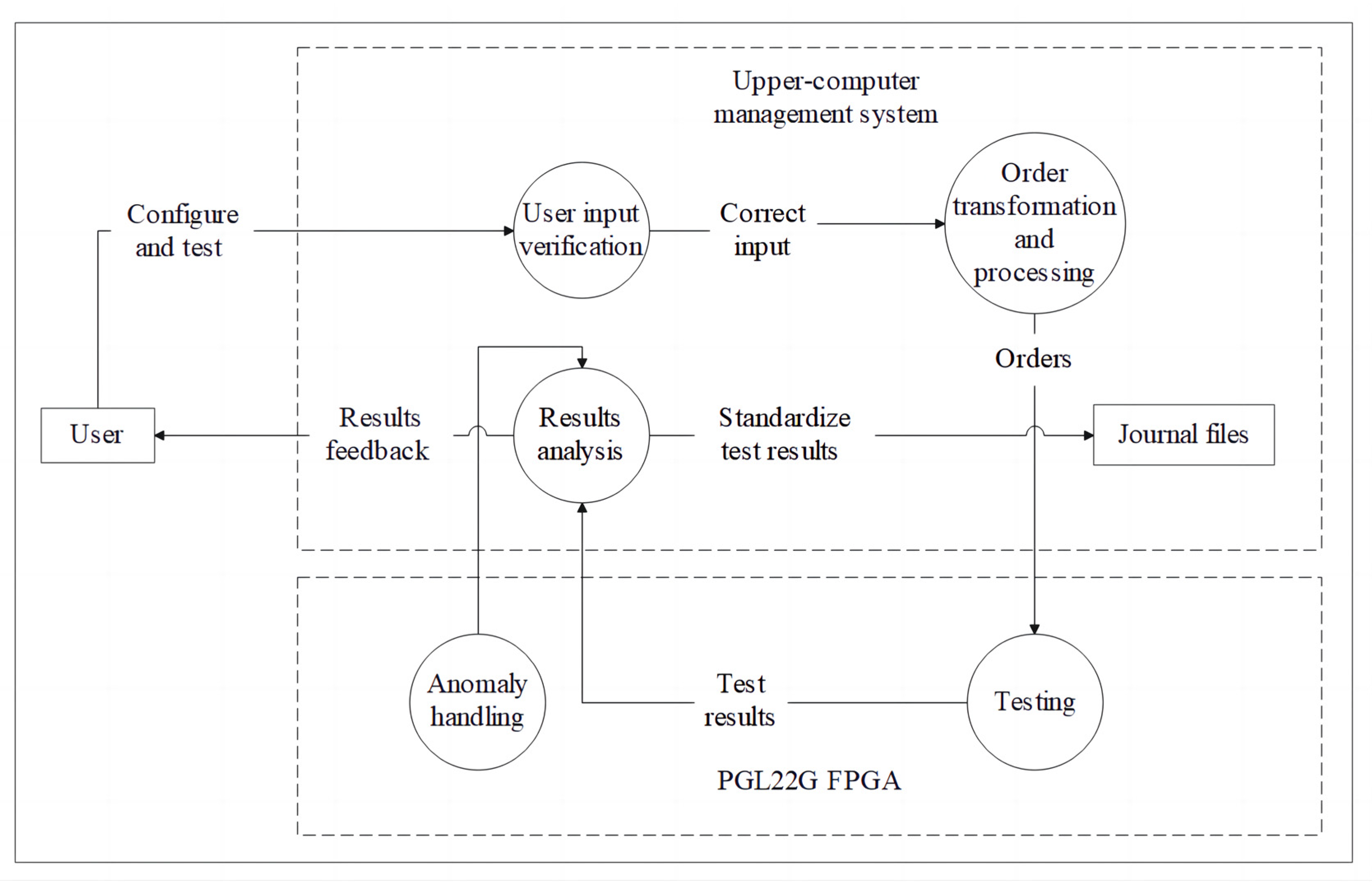

4.2. Test System

- User input and configuration, such as test circuits loading, configuration download, readback and other functions, were accepted by the host computer test management software;

- The host computer test management software sent test commands, such as bitstream file configuration, to the lower computer FPGA test board;

- The lower computer FPGA accepted the upper computer command to load the test program and executed the test according to the configuration;

- The FPGA test board fed back the test results to the upper test management software, which was used to record the test results;

- For the exceptions that occurred during the execution of the lower FPGA test board, information concerning the exception and its handling were fed back to the test management software of the upper computer.

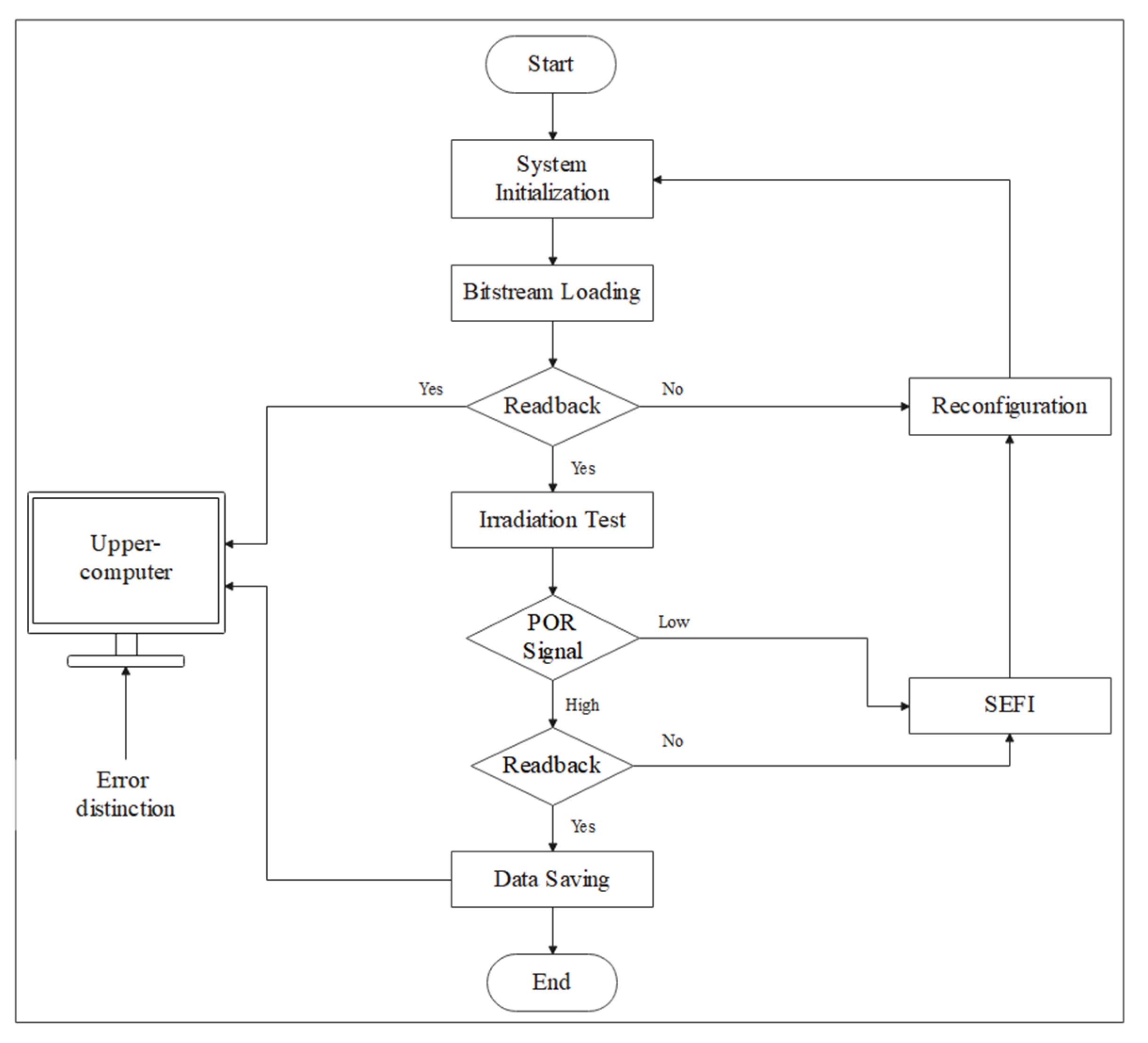

4.3. Test Procedures

- The system was powered up and at the same time the device was configured and the circuit program for the test, which was downloaded to the FPGA test board, was selected;

- The radiation source was placed horizontally on the surface of the chip under test and the upper computer for the test function was verified;

- Operation was continuous when the test board operated normally; otherwise, the abnormal data were counted and the FPGA test board was reconfigured;

- If the number of SEE events exceeded 100 or the alpha fluence exceeded , the irradiation test was stopped;

- The radiation source was removed and the alpha fluence and the number of SEEs were calculated.

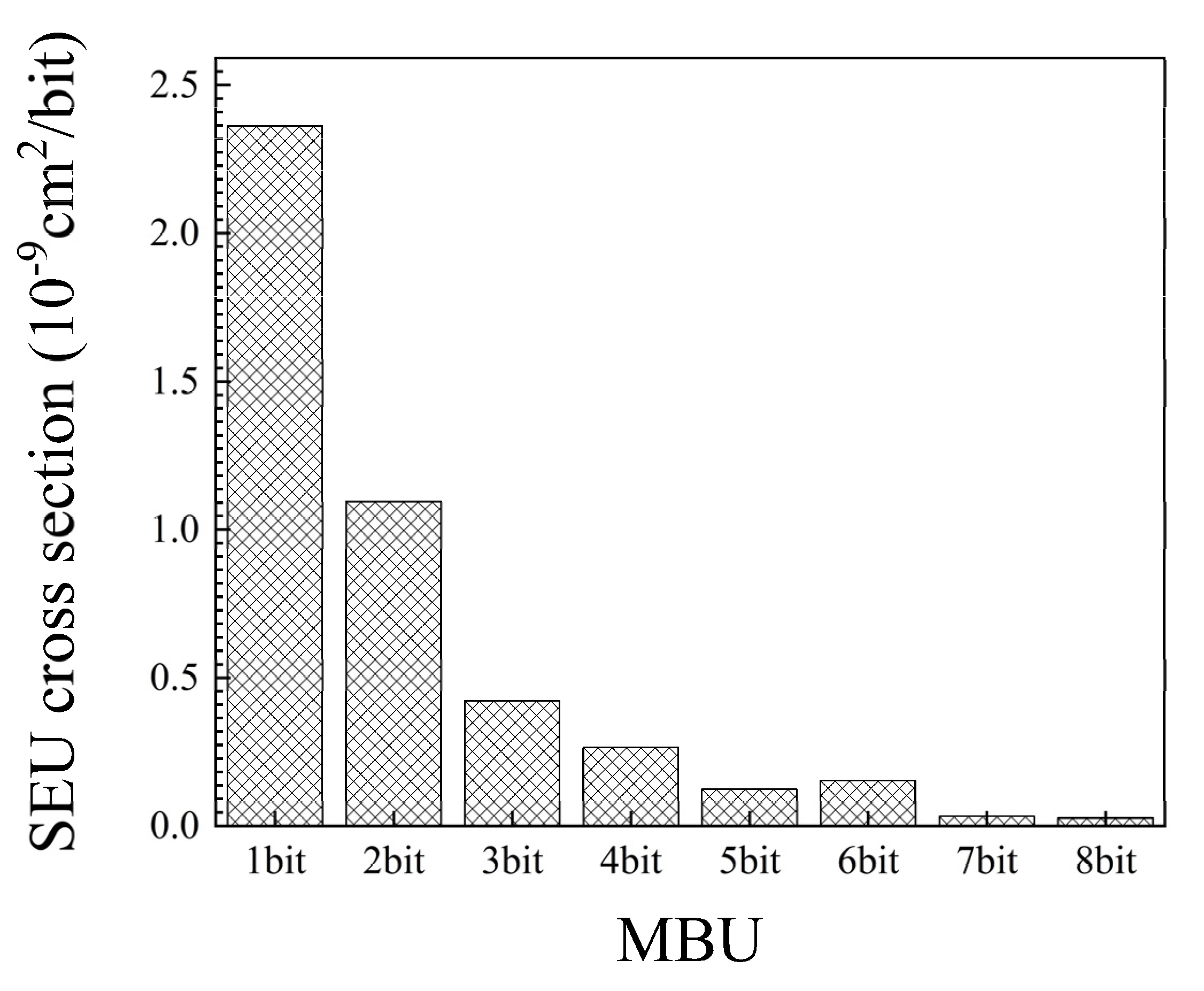

5. Experiments Results

- Upset Error: Data errors caused by SBUs and MBUs in the memory module or data register module. The LUT, register cell in the CLM module and the BRAM module were the main areas where SEUs occurred in this experiment.

- Program Interrupt: The test program was suddenly stopped but could be returned to the normal state through reloading the program in the power state. All program function interrupts in the dynamic test could be recovered by reconfiguration, and no DONE signal dropout was observed. Burst errors induced by the upset of the global registers can be one of the most important reasons for SEFIs in a functional test.

- Program Corrupt: An unrecognized or unknown output produced by the DUT which can be restored to a normal state by JTAG reconfiguration. Repetitive and unpredictable data upsets were often present in the output of this fault, which was generally considered to be the result of a clock-introduced error. This fault occurred very frequently in the BRAM and CLM testing, and thus should be considered when designing the radiation hardness techniques.

6. Discussion

6.1. Analysis of the Radiation Sensitivity

6.2. Influences and Strategies

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Wang, J.J.; Katz, R.B.; Sun, J.S. SRAM based re-programmable FPGA for space applications. IEEE Trans. Nucl. Sci. 1999, 46, 1728–1735. [Google Scholar] [CrossRef]

- Montealegre, N.; Merodio, D.; Fernandez, A.; Armbruster, P. In-flight reconfigurable FPGA-based space systems. In Proceedings of the 2015 NASA/ESA Conference on Adaptive Hardware & Systems, Montreal, QC, Canada, 15–18 June 2015; pp. 1–8. [Google Scholar]

- Leon, A.F. Field programmable gate arrays in space. IEEE Instrum. Meas. Mag. 2003, 6, 42–48. [Google Scholar] [CrossRef]

- Yan, L.; Wang, Q.; Fang, L.; Gu, H.; Li, N. Application of FPGA in space electronics device. J. Space Sci. 2009, 29, 54–58. [Google Scholar]

- Normand, E. Single-event effects in avionics. IEEE Trans. Nucl. Sci. 1996, 43, 461–474. [Google Scholar] [CrossRef]

- Normand, E.; Oberg, D.L.; Wert, J.L.; Ness, J.D.; Majewski, P.P.; Wender, S.; Gavron, A. Single event upset and charge collection measurements using high energy protons and neutrons. IEEE Trans. Nucl. Sci. 1994, 41, 2203–2209. [Google Scholar] [CrossRef]

- Koga, R. Single-event effect ground test issues. IEEE Trans. Nucl. Sci. 1996, 43, 661–670. [Google Scholar] [CrossRef]

- White, D. Considerations surrounding single event effects in FPGAs, ASICs, and processors. Xilinx White Pap, WP402 (v1.0.1) March 7. 2012. Available online: https://www.xilinx.com/content/dam/xilinx/support/documents/white_papers/wp402_SEE_Considerations.pdf. (accessed on 28 October 2022).

- Cabanas-Holmen, M.; Cannon, E.H.; Amort, T.; Ballast, J.; Brees, R.; Fischer, S.; Kleinosowski, A.J.; Meaker, B.; Swann, T.; Wert, J. Predicting the Single-event Error Rate of a Radiation Hardened by Design Microprocessor. IEEE Trans. Nucl. Sci. 2011, 58, 2726–2733. [Google Scholar] [CrossRef]

- Rezgui, S.; Louris, P.; Sharmin, R. SEE Characterization of the New RTAX-DSP (RTAX-D) Antifuse-based FPGA. IEEE Trans. Nucl. Sci. 2010, 57, 3537–3546. [Google Scholar] [CrossRef]

- George, J.; Koga, R.; Swift, G.; Allen, G.; Carmichael, C.; Tseng, C.W. Single Event Upsets in Xilinx Virtex-4 FPGA Devices. In Proceedings of the 2006 IEEE Radiation Effects Data Workshop, Ponte Vedra Beach, FL, USA, 17–21 July 2006; pp. 109–114. [Google Scholar]

- Quinn, H.; Morgan, K.; Graham, P.; Krone, J.; Caffrey, M. Static Proton and Heavy Ion Testing of the Xilinx Virtex-5 Device. In Proceedings of the 2007 IEEE Radiation Effects Data Workshop, Honolulu, HI, USA, 23–27 July 2007; pp. 177–184. [Google Scholar]

- Hiemstra, D.M.; Kirischian, V. Single Event Upset Characterization of the Virtex-6 Field Programmable Gate Array Using Proton Irradiation. In Proceedings of the 2012 IEEE Radiation Effects Data Workshop, Miami, FL, USA, 16–20 July 2012; pp. 1–4. [Google Scholar]

- Du, B.; Sterpone, L.; Azimi, S.; Codinachs, D.M.; Ferlet-Cavrois, V.; Polo, C.B.; Alía, R.G.; Kastriotou, M.; Fernandez-Martínez, P. Ultrahigh Energy Heavy Ion Test Beam on Xilinx Kintex-7 SRAM-Based FPGA. IEEE Trans. Nucl. Sci. 2019, 66, 1813–1819. [Google Scholar] [CrossRef]

- Lee, D.S.; Allen, G.R.; Swift, G.; Cannon, M.; Wirthlin, M.; George, J.S.; Koga, R.; Huey, K. Single-Event Characterization of the 20 nm Xilinx Kintex UltraScale Field-Programmable Gate Array under Heavy Ion Irradiation. In Proceedings of the 2015 IEEE Radiation Effects Data Workshop (REDW), Boston, MA, USA, 13–17 July 2015; pp. 1–6. [Google Scholar]

- Koga, R.; Davis, S.; George, J.; Zakrzewski, M.; Mabry, D. Heavy Ion and Proton Induced Single Event Effects on Xilinx Zynq UltraScale+ Field Programmable Gate Array (FPGA). In Proceedings of the 2018 IEEE Radiation Effects Data Workshop (REDW), Waikoloa, HI, USA, 16–20 July 2018; pp. 1–5. [Google Scholar]

- Autran, J.L.; Munteanu, D.; Roche, P.; Gasiot, G.; Martinie, S.; Uznanski, S.; Sauze, S.; Semikh, S.; Yakushev, E.; Rozov, S.; et al. Soft-errors induced by terrestrial neutrons and natural alpha-particle emitters in advanced memory circuits at ground level. Microelectron. Reliab. 2010, 50, 1822–1831. [Google Scholar] [CrossRef]

- Baumann, R.C. Radiation-induced soft errors in advanced semiconductor technologies. IEEE Trans. Device Mater. Reliab. 2005, 5, 305–316. [Google Scholar] [CrossRef]

- Logos Family FPGA Device Data Guide Sheet. Pangomicro: Shenzhen, China. (DS02001, Version2.2), 2020. Available online: https://www.pangomicro.com/upload/support/file. (accessed on 28 October 2022).

- Keller, A.M.; Whiting, T.A.; Sawyer, K.B.; Wirthlin, M.J. Dynamic SEU sensitivity of designs on two 28-nm SRAM-based FPGA architectures. IEEE Trans. Nucl. Sci. 2017, 65, 280–287. [Google Scholar] [CrossRef]

- Logos Series FPGA Dedicated RAM Modules (DRM) User Guides. Pangomicro: Shenzhen, China. (UG020002, Version1.1), 2018. Available online: https://www.pangomicro.com/upload/support/file (accessed on 28 October 2022).

- Zhang, Z.G.; Ye, B.; Ji, Q.G.; Guo, J.L.; Xi, K.; Lei, Z.F.; Huang, Y.; Peng, C.; He, Y.J.; Liu, J.; et al. Mechanisms of alpha particle induced soft errors in nanoscale static random access memories. Acta Phys. Sin. 2020, 69, 136103. [Google Scholar] [CrossRef]

- JESD89A Measurement and Reporting of Alpha Particle and Terrestrial Cosmic Ray-Induced Soft Errors in Semiconductor Devices JEDEC standard, JEDEC Solid State Technology Association: South Arlington, VA USA, 2006. Available online: https://www.jedec.org/ (accessed on 28 October 2022).

- Berg, M.; Kim, H.; Phan, A.; Seidleck, C.; Label, K.; Campola, M. Xilinx Kintex-UltraScale Field Programmable Gate Array Single Event Effects (SEE) Heavy-ion Test Report. NASA Electronic Parts and Packaging (NEPP): Washington, USA. 2018. Available online: https://nepp.nasa.gov/pages/pubs.cfm. (accessed on 28 October 2022).

- Cai, C.; Gao, S.; Zhao, P.; Yu, J.; Zhao, K.; Xu, L.; Li, D.; He, Z.; Yang, G.; Liu, T.; et al. SEE Sensitivity Evaluation for Commercial 16 nm SRAM-FPGA. Electronics 2019, 8, 1531. [Google Scholar] [CrossRef]

- Li, T.; Yang, H.; Cai, G.; Zhi, T.; Li, Y. A CMOS triple inter-locked latch for SEU insensitivity desige. IEEE Trans. Nucl. Sci. 2014, 61, 3265–3273. [Google Scholar] [CrossRef]

- Cai, C.; Fan, X.; Liu, J.; Li, D.; Liu, T.; Ke, L.; Zhao, P.; He, Z. Heavy-ion induced single event upsets in advanced 65 nm radiation hardened FPGAs. Electronics 2019, 8, 323. [Google Scholar] [CrossRef]

| Device | CLM | 18 Kb BRAM | APM | PLL | ADC | HMEMC | IO | ||

|---|---|---|---|---|---|---|---|---|---|

| LUT5 | FF | Distributed RAM | |||||||

| PGL22G | 17,536 | 26,304 | 71,040 | 48 | 30 | 6 | 1 | 2 | 240 |

| Parameter | Value |

|---|---|

| Radiation source | 241Am |

| Source number | 14AM4R2031 |

| Emissivity () | |

| Diameter (mm) | 35 |

| Thickness (mm) | 1.0 |

| Shape | Cylinder |

| DUT | Test Module | Test Capacity | Test Method | Test Duration |

|---|---|---|---|---|

| PGL22G | CRAM | 610,024 bit | Static test | 11 h 46 min |

| BRAM | 811,008 bit | Dynamic test | 10 h 6 min 19 s | |

| CLB | 5120 bit | Dynamic test | 10 h 10 min 7 s |

| Test Module | Event Type | Total Number of Events | Fluence | Cross Section |

|---|---|---|---|---|

| CRAM | Upset Error | 706,164 | ||

| BRAM | Program Interrupt | 95 | ||

| Program Corrupt | 89 | |||

| Upset Error | 20,668 | |||

| CLM | Program Interrupt | 144 | device | |

| Program Corrupt | 25 | device | ||

| Upset Error | 1011 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xiong, X.; Du, X.; Zheng, B.; Chen, Z.; Jiang, W.; He, S.; Zhu, Y. Soft Error Sensitivity Analysis Based on 40 nm SRAM-Based FPGA. Electronics 2022, 11, 3844. https://doi.org/10.3390/electronics11233844

Xiong X, Du X, Zheng B, Chen Z, Jiang W, He S, Zhu Y. Soft Error Sensitivity Analysis Based on 40 nm SRAM-Based FPGA. Electronics. 2022; 11(23):3844. https://doi.org/10.3390/electronics11233844

Chicago/Turabian StyleXiong, Xu, Xuecheng Du, Bo Zheng, Zhi Chen, Wei Jiang, Sanjun He, and Yixin Zhu. 2022. "Soft Error Sensitivity Analysis Based on 40 nm SRAM-Based FPGA" Electronics 11, no. 23: 3844. https://doi.org/10.3390/electronics11233844

APA StyleXiong, X., Du, X., Zheng, B., Chen, Z., Jiang, W., He, S., & Zhu, Y. (2022). Soft Error Sensitivity Analysis Based on 40 nm SRAM-Based FPGA. Electronics, 11(23), 3844. https://doi.org/10.3390/electronics11233844