A 0.0012 mm2 6-bit 700 MS/s 1 mW Calibration-Free Pseudo-Loop-Unrolled SAR ADC in 28 nm CMOS

Abstract

:1. Introduction

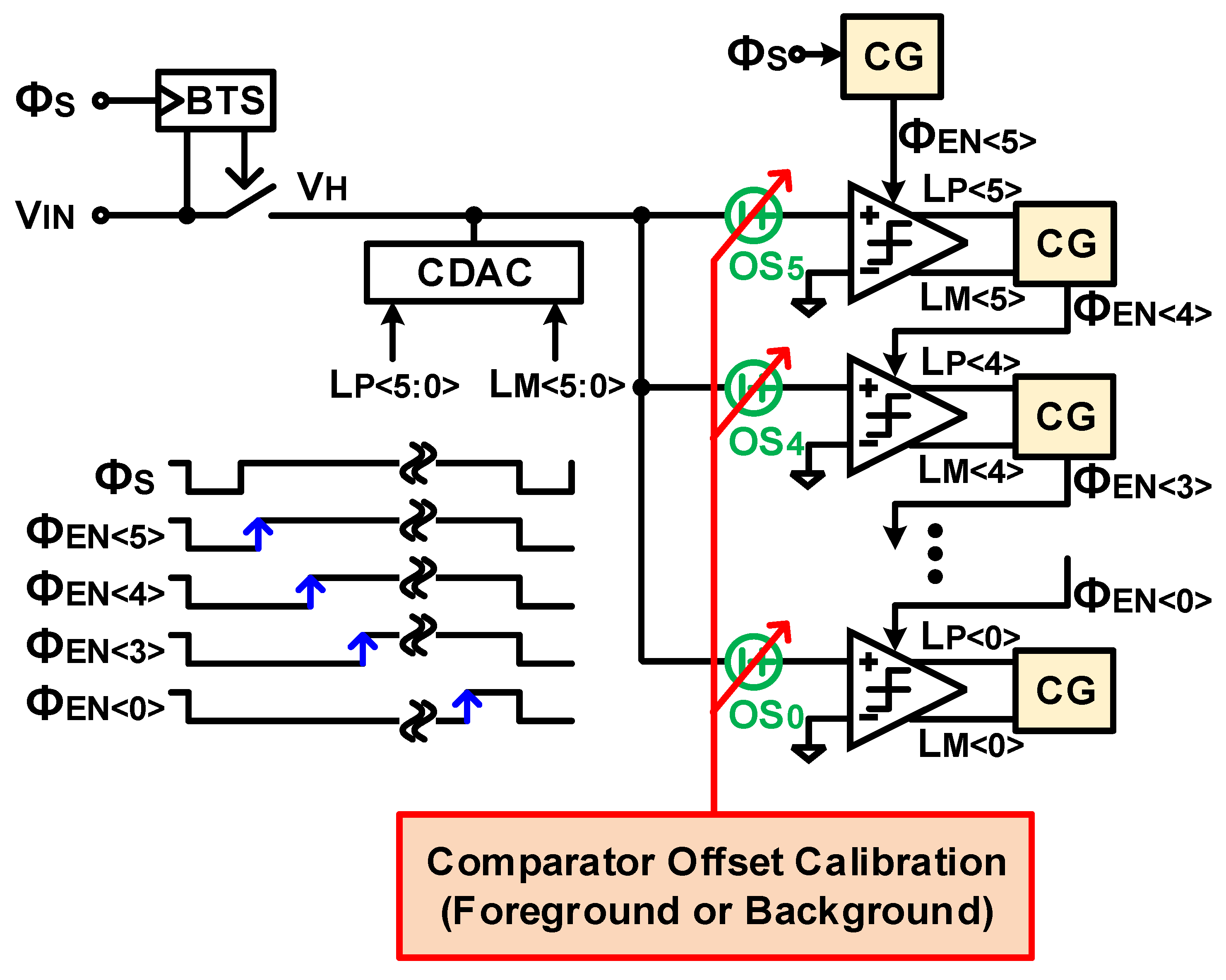

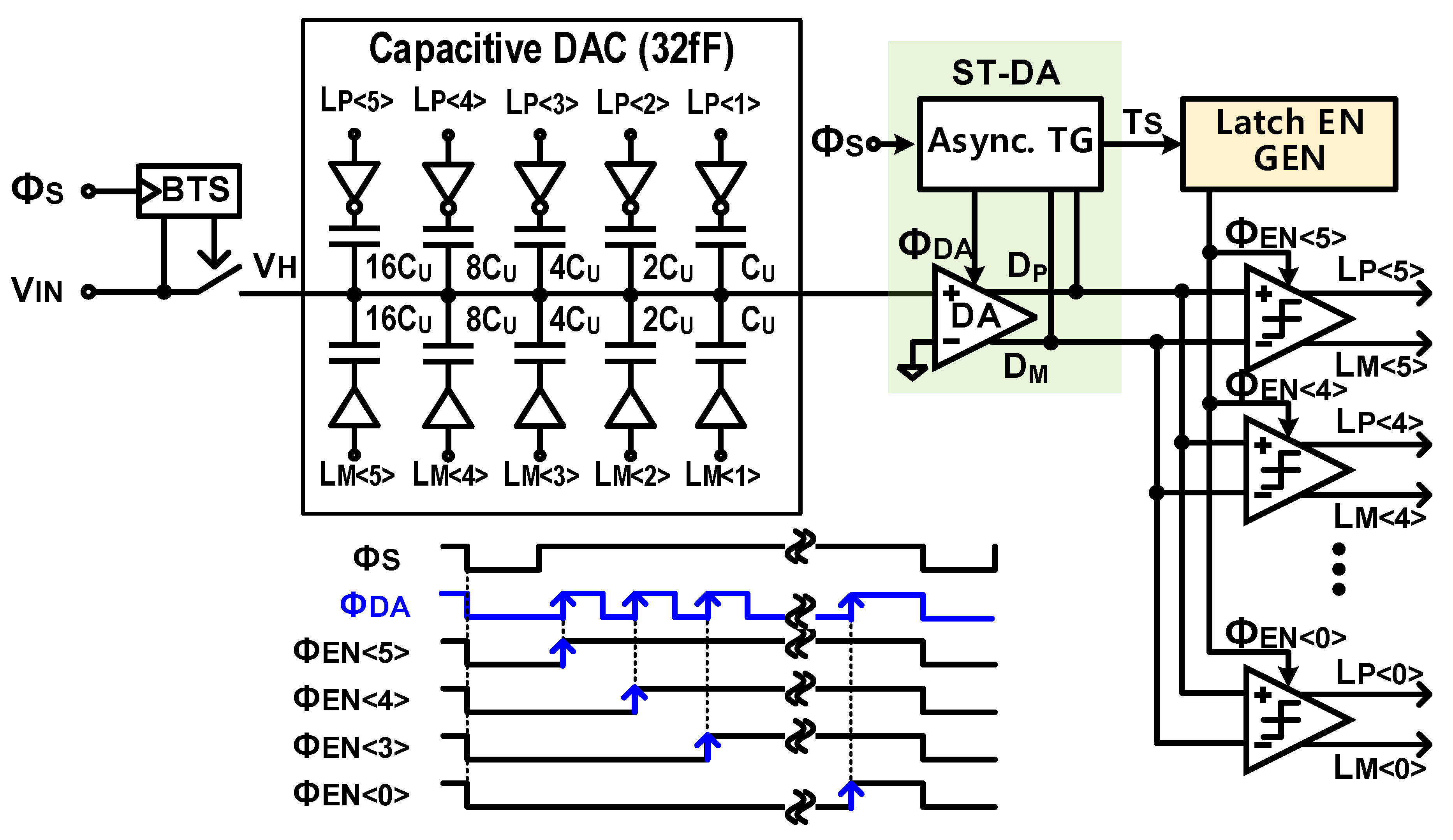

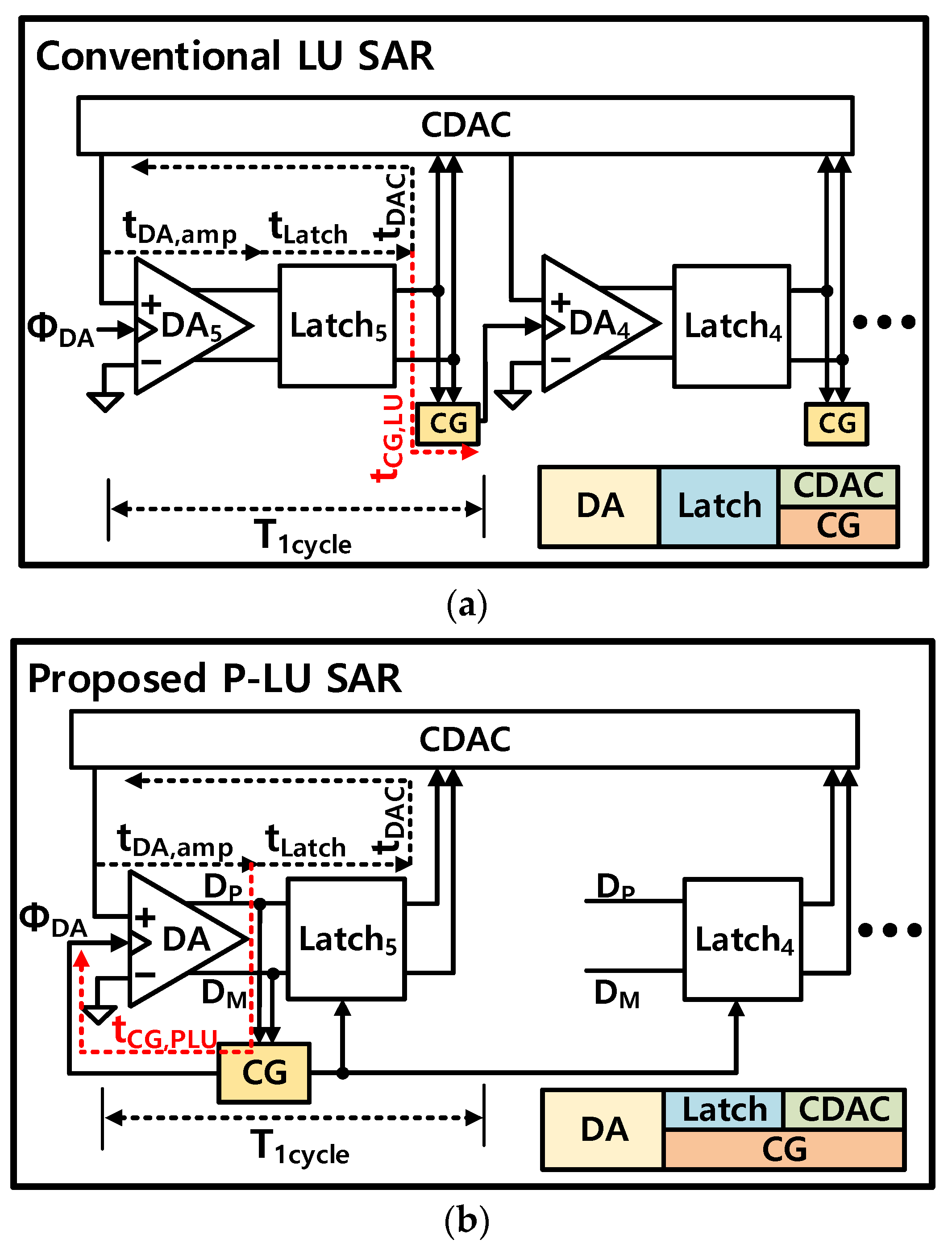

2. Review of LU SAR ADC Architecture

3. Proposed Pseudo-LU SAR ADC

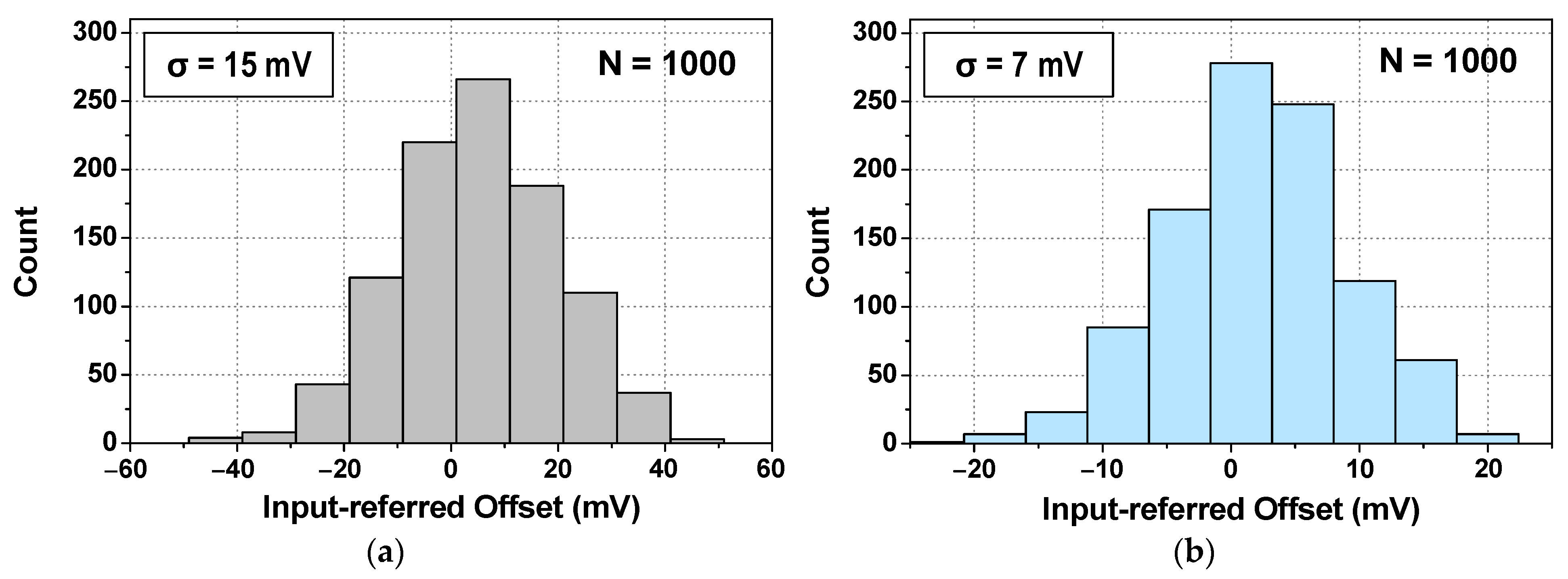

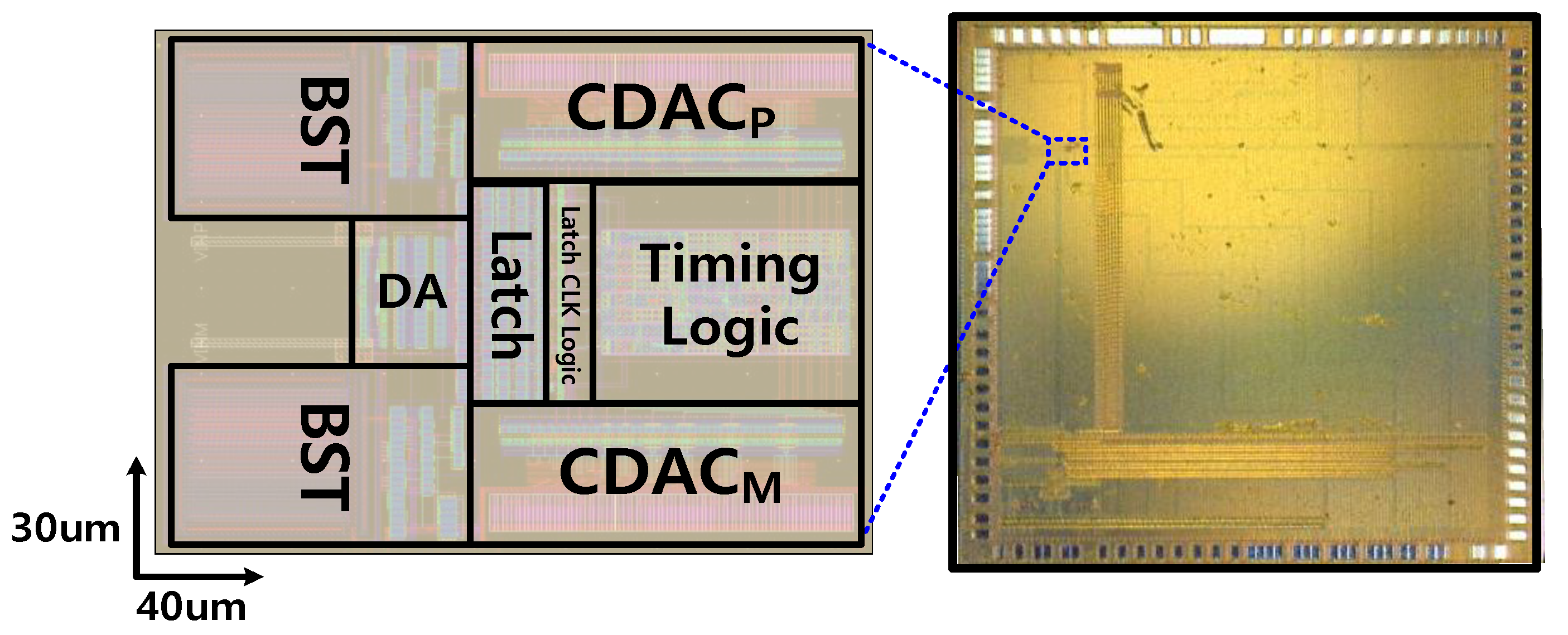

4. Circuit Implementation

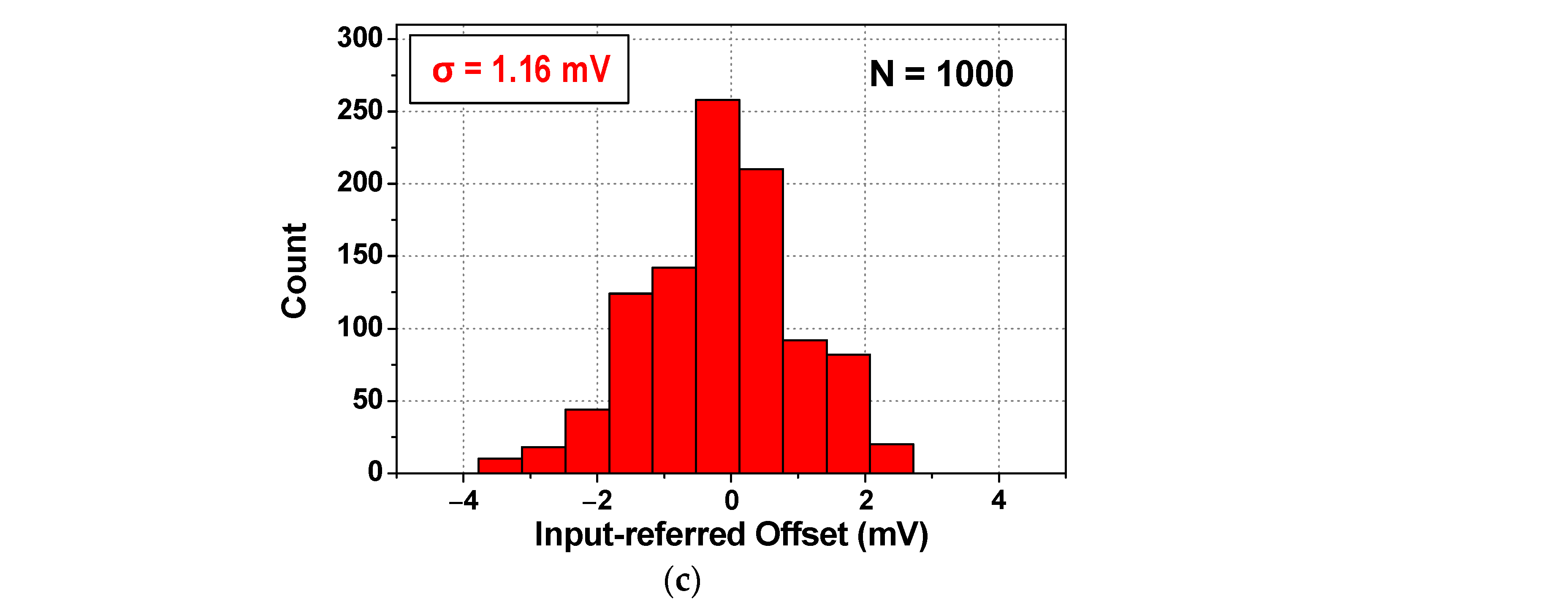

4.1. Inverter-Inserted Three-Stage Comparator

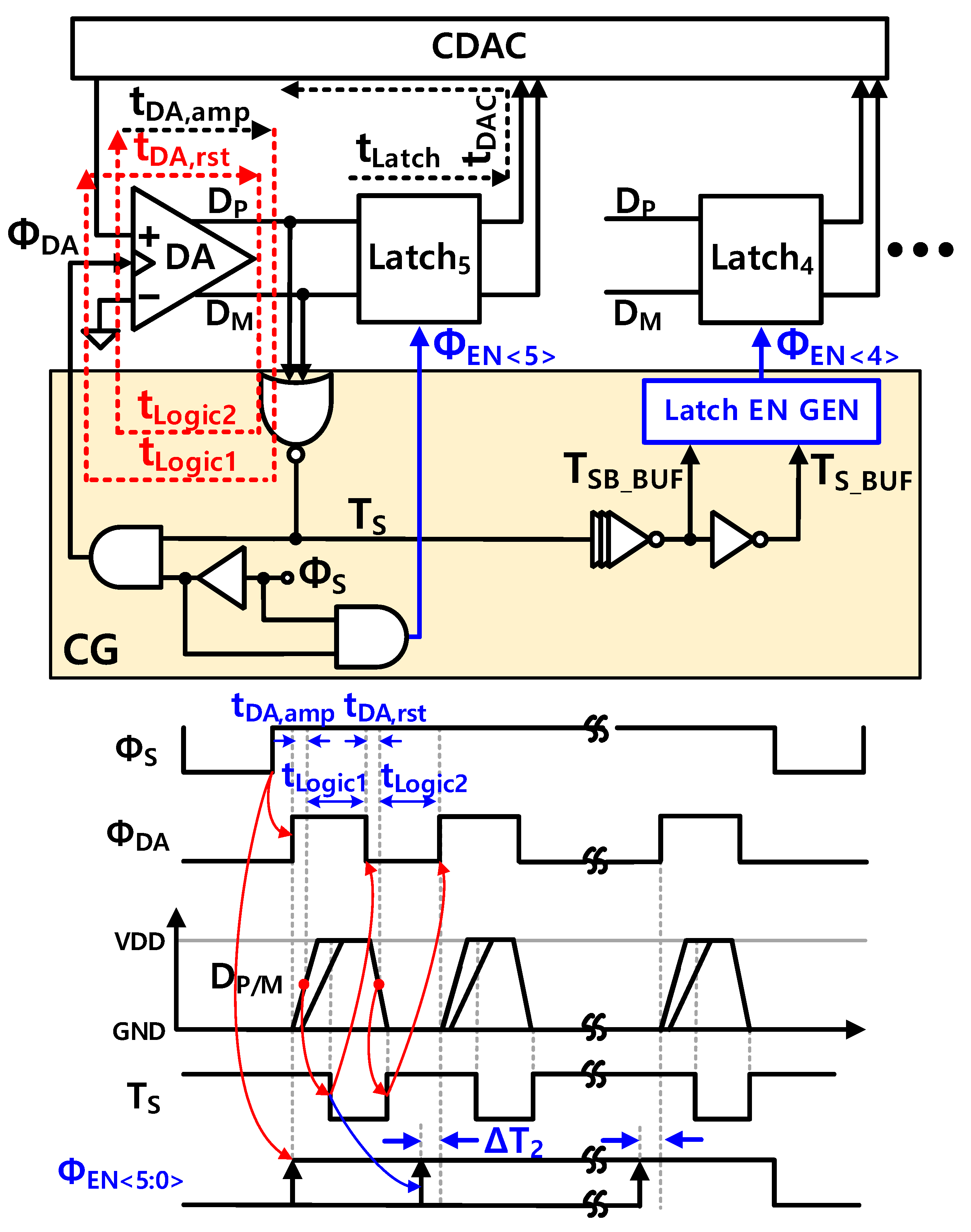

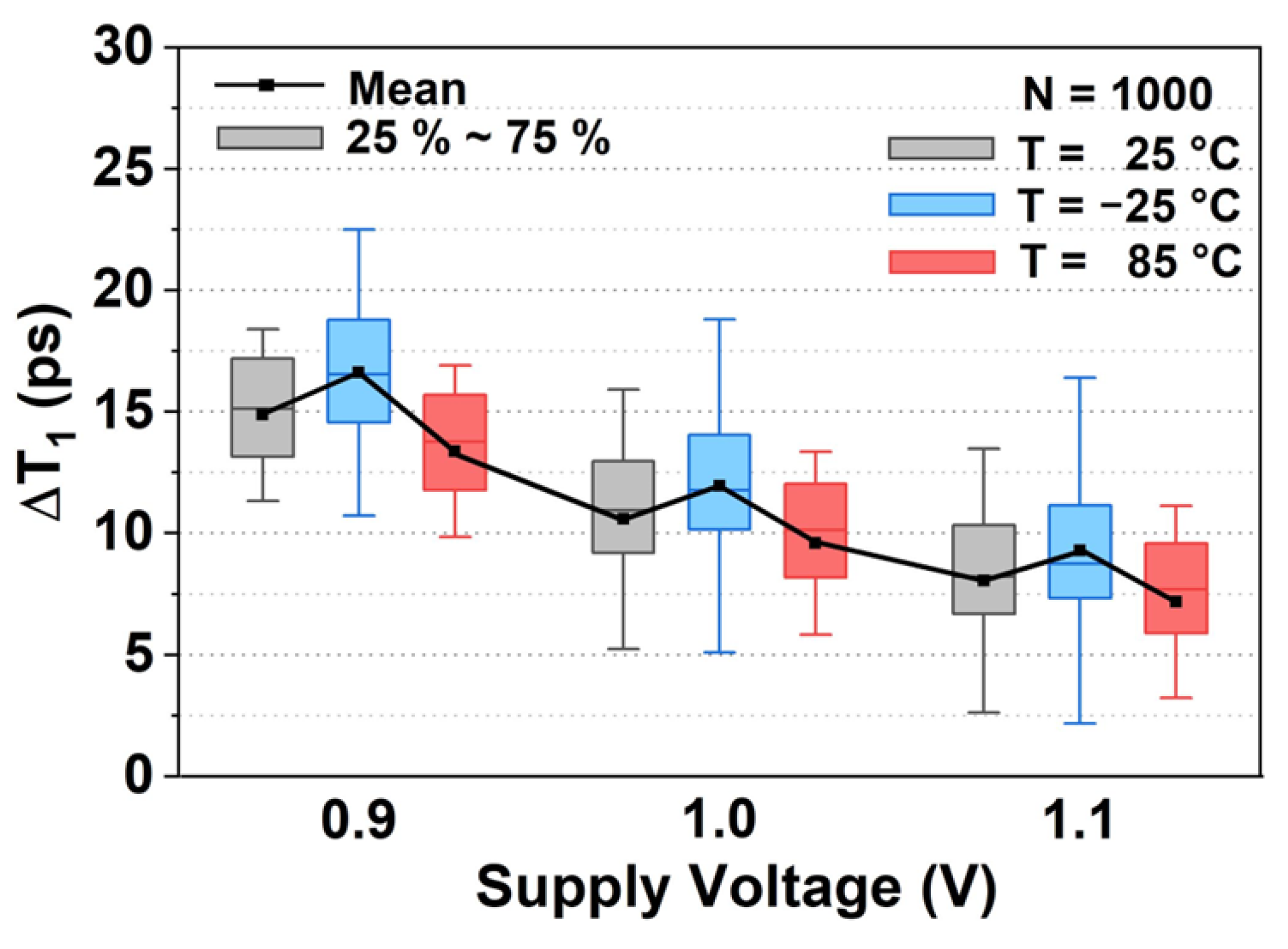

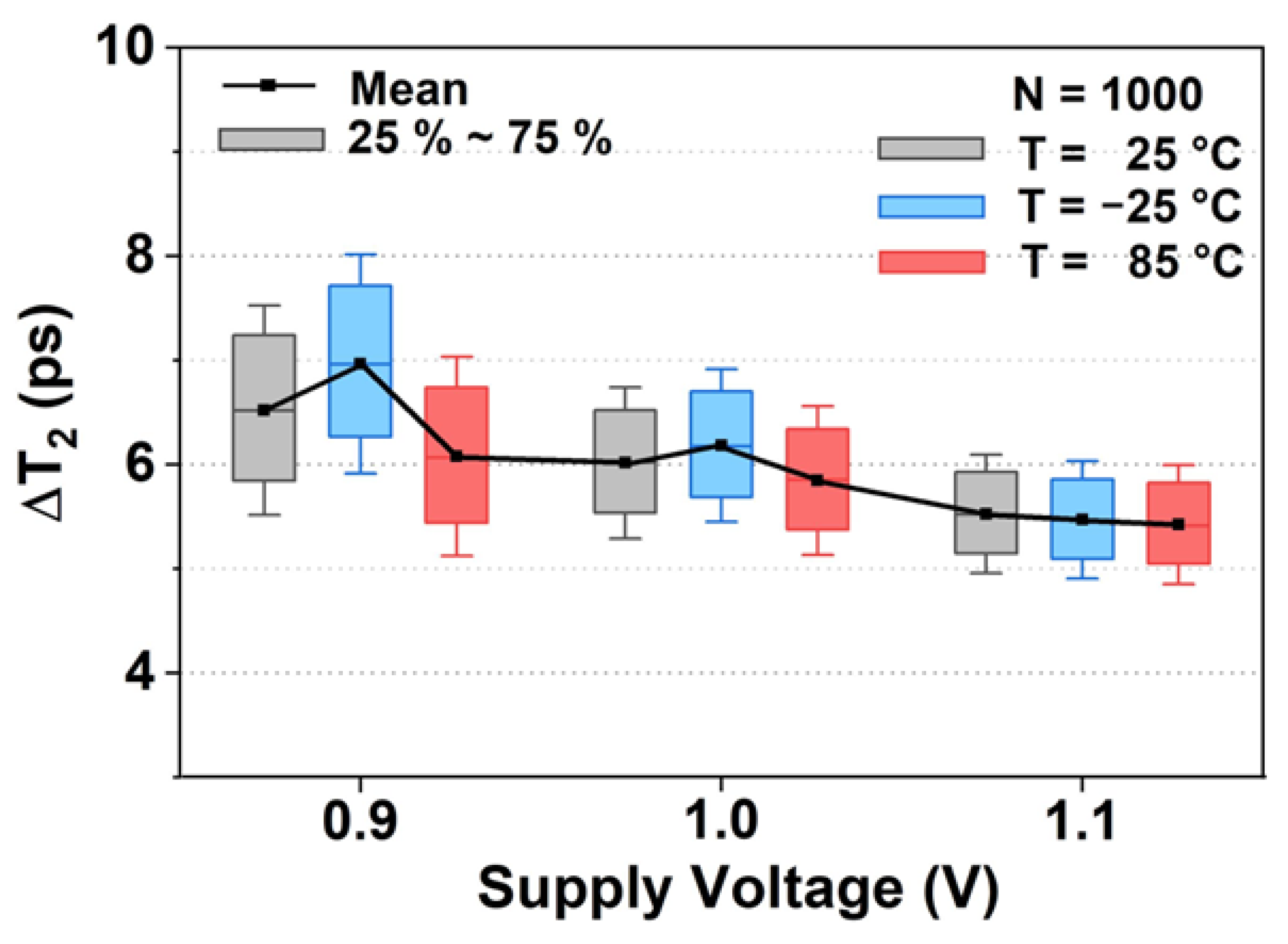

4.2. Clock Generator (CG)

4.3. High-Speed Logic for Latch Enable Generation

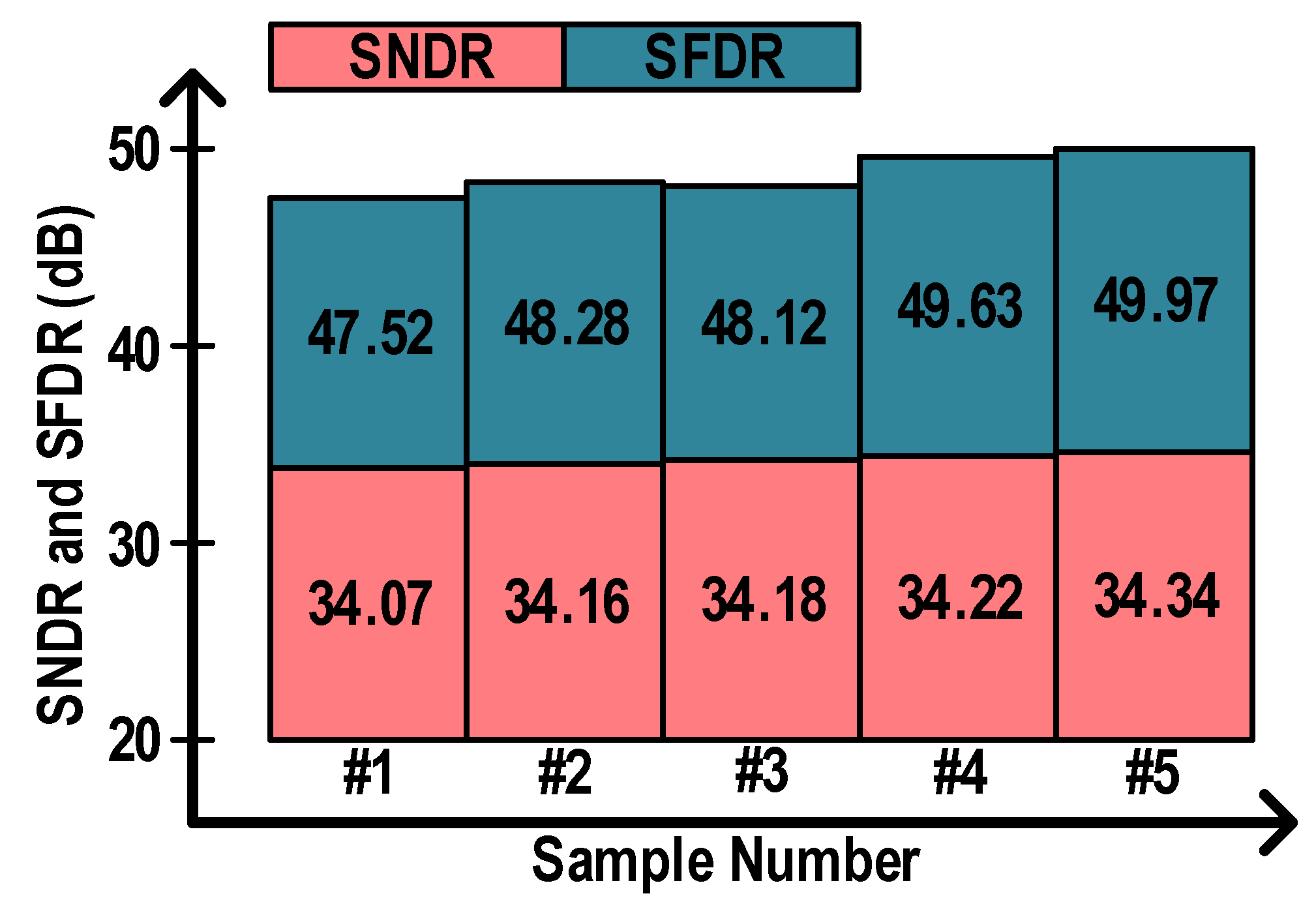

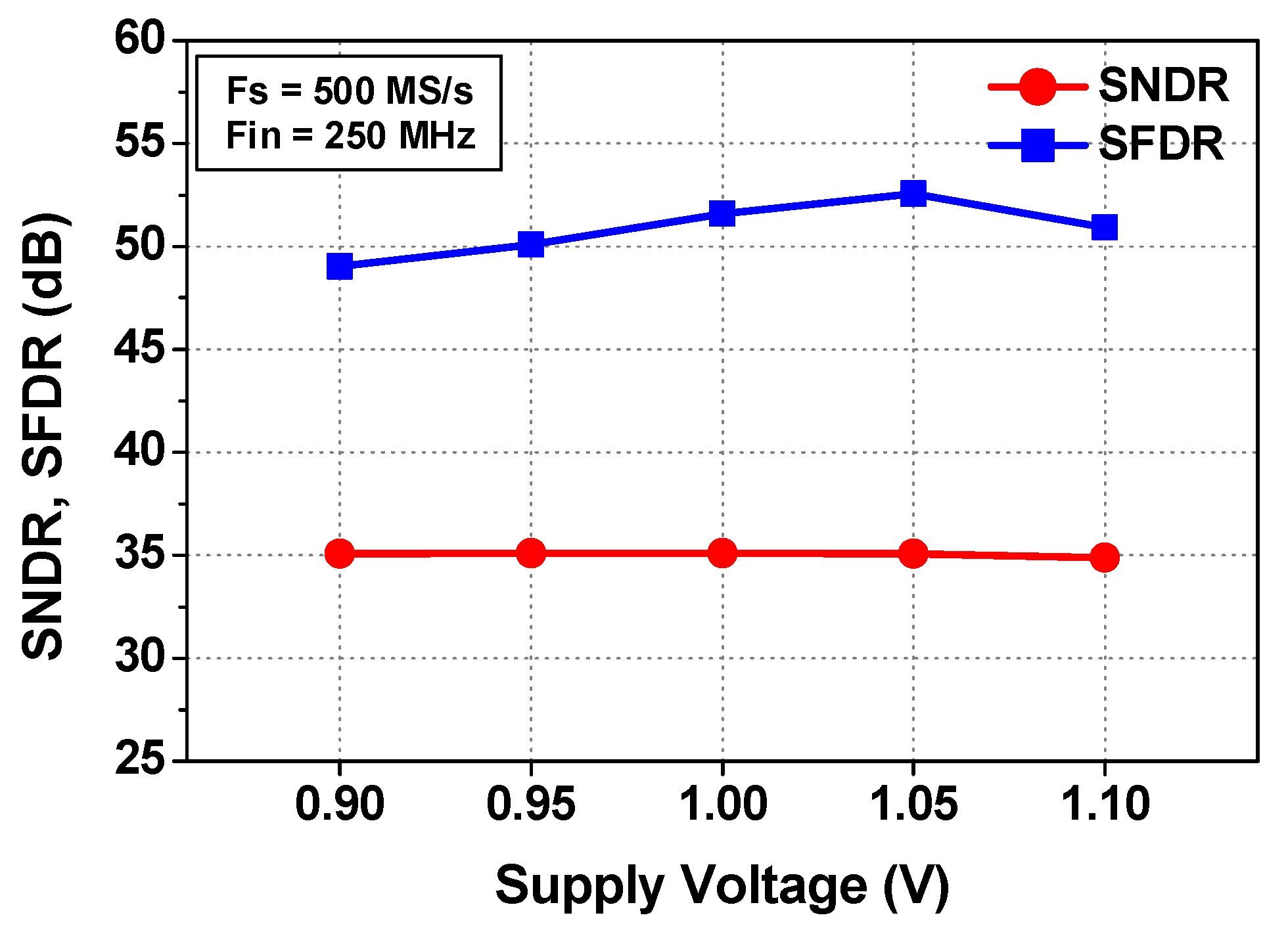

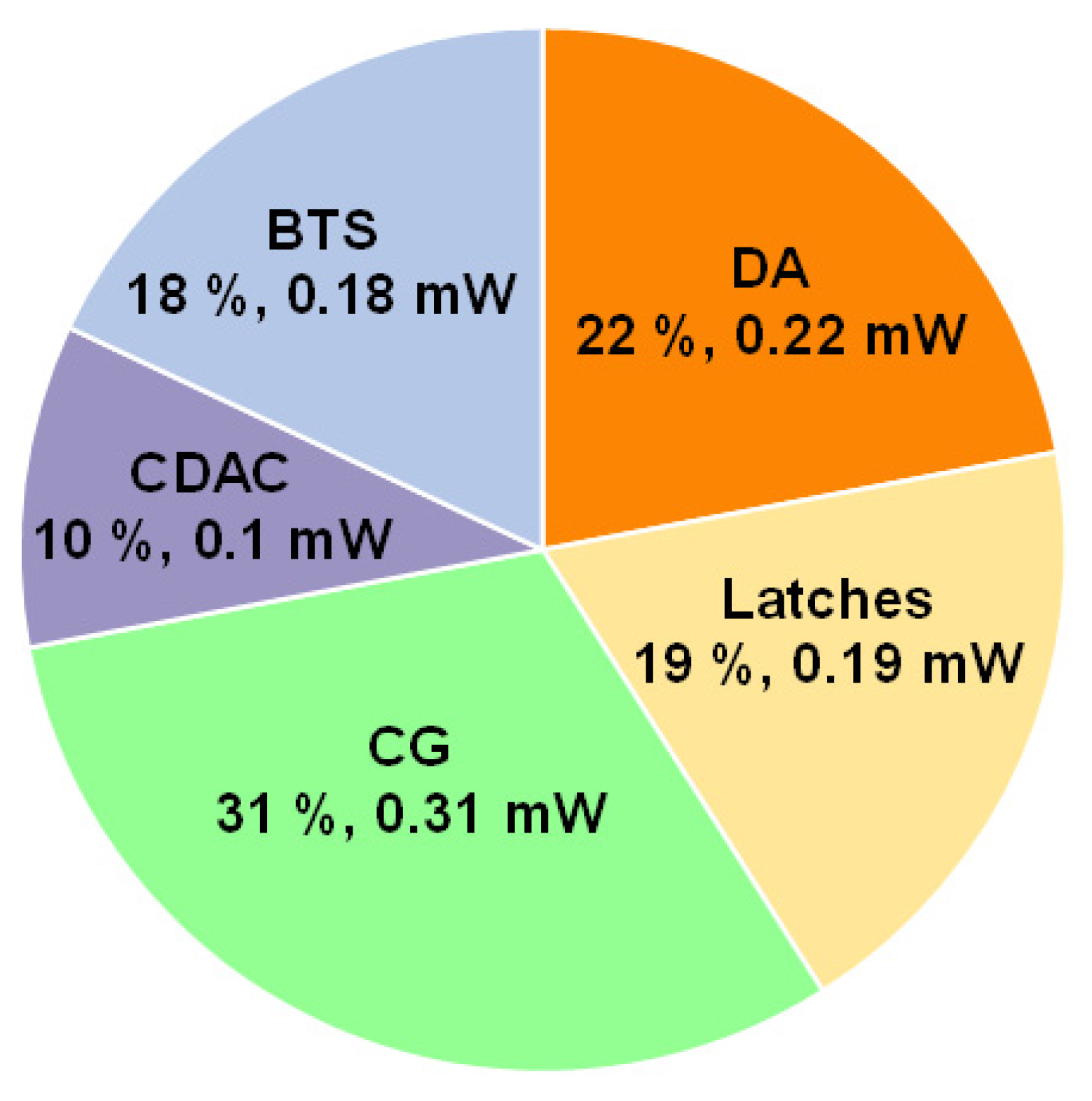

5. Measurement Results

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

Abbreviations

| SAR | Successive approximation register |

| ADC | Analog-to-digital converter |

| DA | Dynamic amplifier |

| ST-DA | Self-triggered DA |

| LU | Loop-unrolled |

| P-LU | Pseudo-loop-unrolled |

| CG | Clock generation |

| BTS | Bootstrapped |

| T/H | Track-and-hold |

| CDAC | Capacitive digital-to-analog converter |

| SNR | Signal-to-noise ratio |

| SNDR | Signal-to-noise distortion ratio |

| SFDR | Spurious-free dynamic range |

| ENOB | Effective number of bits |

| DNL | Differential non-linearity |

| INL | Integrated non-linearity |

| FoM | Figure-of-merit |

References

- Mishra, P.; Tan, A.; Helal, B.; Ho, C.R.; Loi, C.; Riani, J.; Sun, J.; Mistry, K.; Raviprakash, K.; Tse, L.; et al. A 112Gb/s ADC-DSP-Based PAM-4 Transceiver for Long-Reach Applications with >40 dB Channel Loss in 7 nm FinFET. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 13–22 February 2021. [Google Scholar]

- Bailey, J.; Shakiba, H.; Nir, E.; Marderfeld, G.; Krotnev, P.; LaCroix, M.A.; Cassan, D. A 112Gb/s PAM-4 Low-Power 9-Tap Sliding-Block DFE in a 7 nm FinFET Wireline Receiver. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 13–22 February 2021. [Google Scholar]

- Wang, D.; Wang, Z.; Xu, H.; Wang, J.; Zhao, Z.; Zhang, C.; Wang, Z.; Chen, H. A 56-Gbps PAM-4 Wireline Receiver with 4-Tap Direct DFE Employing Dynamic CML Comparators in 65 nm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 2022, 69, 1027–1040. [Google Scholar] [CrossRef]

- Jiang, W.; Zhu, Y.; Chan, C.H.; Murmann, B.; Martins, R.P. A 7-bit 2GS/s Time-Interleaved SAR ADC with Timing Skew Calibration Based on Current Integrating Sampler. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 557–568. [Google Scholar] [CrossRef]

- Ali, A.M.A.; Dinc, H.; Bhoraskar, P.; Bardsley, S.; Dillon, C.; Kumar, M.; McShea, M.; Bunch, R.; Prabhakar, J.; Puckett, S. A 12b 18GS/s RF Sampling ADC with an Integrated Wideband Track-and-Hold Amplifier and Background Calibration. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 16–20 February 2020. [Google Scholar]

- Seo, M.J. A Single-Amplifier Dual-Residue Pipelined-SAR ADC. Electronics 2021, 10, 421. [Google Scholar] [CrossRef]

- Hong, H.-K.; Kang, H.-W.; Sung, B.; Lee, C.-H.; Choi, M.; Park, H.-J.; Ryu, S.-T. An 8.6 ENOB 900 MS/s Time-Interleaved 2b/cycle SAR ADC with a 1b/cycle Reconfiguration for Resolution Enhancement. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013; pp. 470–471. [Google Scholar]

- Seo, M.-J.; Kim, Y.-D.; Chung, J.-H.; Ryu, S.-T. A 40 nm CMOS 12b 200 MS/s Single-amplifier Dual-residue Pipelined-SAR ADC. In Proceedings of the IEEE Symposium on VLSI Circuits Digest of Technical Papers, Kyoto, Japan, 9–14 June 2019. [Google Scholar]

- Nam, J.; Hassanpourghadi, M.; Zhang, A.; Chen, M.S.-W. A 12-Bit 1.6, 3.2, and 6.4 GS/s 4-b/Cycle Time-Interleaved SAR ADC with Dual Reference Shifting and Interpolation. IEEE J. Solid State Circuits 2018, 53, 1765–1779. [Google Scholar] [CrossRef]

- Seo, M.J.; Jin, D.H.; Kim, Y.D.; Kim, J.P.; Ryu, S.T. A Single-Supply CDAC-Based Buffer-Embedding SAR ADC with Skip-Reset Scheme Having Inherent Chopping Capability. IEEE J. Solid State Circuits 2020, 55, 2660–2669. [Google Scholar] [CrossRef]

- Luu, D.; Kull, L.; Toifl, T.; Menolfi, C.; Braendli, M.; Francese, P.A.; Morf, T.; Kossel, M.; Yueksel, H.; Cevrero, A.; et al. A 12-bit 300-MS/s SAR ADC with Inverter-Based Preamplifier and Common-Mode-Regulation DAC in 14-nm CMOS FinFET. IEEE J. Solid State Circuits 2018, 53, 3268–3279. [Google Scholar] [CrossRef]

- Wang, D.; Zhu, X.; Guo, X.; Luan, J.; Zhou, L.; Wu, D.; Liu, H.; Wu, J.; Liu, X. A 2.6 GS/s 8-Bit Time-Interleaved SAR ADC in 55 nm CMOS Technology. Electronics 2019, 8, 305. [Google Scholar] [CrossRef] [Green Version]

- Li, J.; Guo, X.; Luan, J.; Wu, D.; Zhou, L.; Wu, N.; Huang, Y.; Jia, H.; Zheng, X.; Wu, J.; et al. A 1 GS/s 12-Bit Pipelined/SAR Hybrid ADC in 40 nm CMOS Technology. Electronics 2020, 9, 375. [Google Scholar] [CrossRef] [Green Version]

- Chen, S.M.; Brodersen, R.W. A 6b 600 MS/s 5.3 mW Asynchronous ADC in 0.13 μm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 6–9 February 2006. [Google Scholar]

- Jiang, T.; Liu, W.; Zhong, F.Y.; Zhong, C.; Hu, K.; Chiang, P.Y. A Single-Channel, 1.25-GS/s, 6-bit, 6.08-mW Asynchronous Successive-Approximation ADC with Improved Feedback Delay in 40-nm CMOS. IEEE J. Solid-State Circuits 2012, 47, 2444–2453. [Google Scholar] [CrossRef]

- Chen, L.; Ragab, K.; Tang, X.; Song, J.; Sanyal, A.; Sun, N. A 0.95-mW 6-b 700-MS/s Single-Channel Loop-Unrolled SAR ADC in 40-nm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2017, 64, 244–248. [Google Scholar] [CrossRef]

- Chen, C.; Sun, J.; Wang, C.; Liu, W. A 10-b 500 MS/s Partially Loop-Unrolled SAR ADC with a Comparator Offset Calibration Technique. In Proceedings of the IEEE International Symposium on Circuits and Systems, Daegu, Korea, 22–28 May 2021. [Google Scholar]

- Akkaya, A.; Celik, F.; Leblebici, Y. An 8-Bit 800 MS/s Loop-Unrolled SAR ADC with Common-Mode Adaptive Background Offset Calibration in 28 nm FDSOI. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 2766–2774. [Google Scholar] [CrossRef]

- Ragap, K.; Sun, N. A 1.4 mW 8b 350 MS/s Loop-Unrolled SAR ADC with Background Offset Calibration in 40 nm CMOS. In Proceedings of the IEEE European Solid-State Circuits Conference, Lausanne, Switzerland, 12–15 September 2016. [Google Scholar]

- Kull, L.; Luu, D.; Menolfi, C.; Brändli, M.; Francese, P.A.; Morf, T.; Kossel, M.; Cevrero, A.; Ozkaya, I.; Toifl, T. A 24–72-GS/s 8-b Time-Interleaved SAR ADC with 2.0–3.3-pJ/Conversion and >30 dB SNDR at Nyquist in 14-nm CMOS FinFET. IEEE J. Solid-State Circuits 2018, 53, 3508–3516. [Google Scholar] [CrossRef]

- Chung, Y.-H.; Rih, W.-S.; Chang, C.-W. A 6-bit 1.3-GS/s Ping-Pong Domino-SAR ADC in 55-nm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 999–1003. [Google Scholar] [CrossRef]

- Oh, D.R.; Moon, K.J.; Lim, W.M.; Kim, Y.D.; An, E.J.; Ryu, S.T. An 8-Bit 1-GS/s Asynchronous Loop-Unrolled SAR-Flash ADC with Complementary Dynamic Amplifiers in 28-nm CMOS. IEEE J. Solid-State Circuits 2021, 56, 1216–1226. [Google Scholar] [CrossRef]

- Schinkel, D.; Mensink, E.; Klumperink, E.; Tuijl, E.V.; Nauta, B. A Double-Tail Latch-Type Voltage Sense Amplifier with 18 ps Setup-Hold Time. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 11–15 February 2007. [Google Scholar]

- Kim, W.; Hong, H.K.; Roh, Y.J.; Kang, H.W.; Hwang, S.I.; Jo, D.S.; Chang, D.J.; Seo, M.J.; Ryu, S.T. A 0.6 V 12b 10 MS/s Low-Noise Asynchronous SAR-Assisted Time-Interleaved SAR (SATI-SAR) ADC. IEEE J. Solid-State Circuits 2016, 51, 1826–1839. [Google Scholar] [CrossRef]

- Li, D.; Liu, J.; Zhuang, H.; Zhu, Z.; Yang, Y.; Sun, N. A 7b 2.6 mW 900 MS/s Nonbinary 2-Then-3b/cycle SAR ADC with Background Offset Calibration. In Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 14–17 April 2019. [Google Scholar]

- Chan, C.H.; Zhu, Y.; Sin, S.W.; Ben, S.P.U.; Martins, R.P. A 6b 5 GS/s 4 Interleaved 3b/Cycle SAR ADC. IEEE J. Solid-State Circuits 2016, 51, 365–377. [Google Scholar]

- Kiene, G.; Catania, A.; Overwater, R.; Bruschi, P.; Charbon, E.; Babaie, M.; Sebastiano, F. A 1 GS/s 6-to-8b 0.5 mW/Qubit Cryo-CMOS SAR ADC for Quantum Computing in 40 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 13–22 February 2021. [Google Scholar]

| N-bit | Async. SAR [14] | LU SAR [15,16,17] (Boreground cal.) | LU SAR [18,19,20] (Background cal.) | LU SAR + SAR [21] (Redundancy bit) | P-LU SAR (This Work) |

|---|---|---|---|---|---|

| # of comparators | 1 | N | N + 1 | N | One DA + N |

| # of input gates | 1 | N | N + 1 | N | 1 |

| Conversion cycle | N | N | N + 1 | N + 1 | N |

| Offset calibration | Not needed | Needed | Needed | Not needed | Not needed |

| Comparator reset | Needed | Not needed | Not needed | Partially Needed | Hidden |

| DAC switching logic | Needed | Not needed | Not needed | Not needed | Not needed |

| This Work | ESSCIRC16 Ragab [19] | TCAS17 Chen [16] | TCAS18 Chung [21] | TCAS21 Akkaya [18] | CICC19 Li [25] | JSSC21 Oh [22] | JSSC16 Chan [26] | ISSCC21 Kiene [27] | |

|---|---|---|---|---|---|---|---|---|---|

| Architecture | P-LU SAR | LU SAR | LU SAR | LU SAR + SAR | LU SAR | 2–3b/cycle | SAR-Flash | TI 3b/cycle | TI LU SAR |

| # of channels | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 4 | 2 |

| Technology (nm) | 28 | 40 | 40 | 55 | 28(FDSOI) | 40 | 28 | 65 | 40 |

| Resolution (bit) | 6 | 8 | 6 | 6 | 8 | 7 | 8 | 6 | 6 |

| FS (GS/s) | 0.7 | 0.35 | 0.7 | 1.3 | 0.8 | 0.9 | 1 | 5 | 0.9 |

| Area (mm2) | 0.0012 | 0.024 1 | 0.004 | 0.03 | 0.0037 | 0.014 | 0.0056 | 0.09 | 0.045 |

| Supply (V) | 1.0 | 1.1 | 1.2 | 1.2 | 1.0 | 1.1 | 1.1 | 1.0 | 1.1 |

| DNLMAX (LSB) | 0.33 | 0.9 | 0.9 | 0.78 | 0.74 | 0.5 | 0.59 | 1.4 | 0.5 1 |

| INLMAX (LSB) | 0.27 | 0.9 | 0.6 | 0.85 | 0.65 | 0.8 | 0.82 | 0.95 | 0.5 1 |

| CIN (fF) | 32 | 249 | 30.4 | 32 | 64 | 25.2 | 64 | 31 | 63.5 |

| SNDR@Nyq. (dB) | 34.0 | 43.7 | 34.8 | 30.5 | 42.5 | 39.7 | 45.5 | 30.7 | 33.4 |

| SFDR@Nyq. (dB) | 47.5 | 59.5 | 47.8 | 36.3 | 50.7 | 54.8 | 59.4 | 43.1 | 48.4 |

| Power (mW) | 1.0 | 1.37 | 0.95 | 3.5 | 2 | 2.6 | 2.55 | 5.5 | 0.7 |

| Walden FOM 2 (fJ/conv.-step) | 34.6 | 31.3 | 30.0 | 99 | 22.8 | 36.6 | 16.6 | 39 | 20 |

| Offset Calibration | Not needed | Background | Foreground | Not needed | Background | Background | Foreground | Foreground | Foreground |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

An, E.-J.; Oh, D.-R. A 0.0012 mm2 6-bit 700 MS/s 1 mW Calibration-Free Pseudo-Loop-Unrolled SAR ADC in 28 nm CMOS. Electronics 2022, 11, 1707. https://doi.org/10.3390/electronics11111707

An E-J, Oh D-R. A 0.0012 mm2 6-bit 700 MS/s 1 mW Calibration-Free Pseudo-Loop-Unrolled SAR ADC in 28 nm CMOS. Electronics. 2022; 11(11):1707. https://doi.org/10.3390/electronics11111707

Chicago/Turabian StyleAn, Eun-Ji, and Dong-Ryeol Oh. 2022. "A 0.0012 mm2 6-bit 700 MS/s 1 mW Calibration-Free Pseudo-Loop-Unrolled SAR ADC in 28 nm CMOS" Electronics 11, no. 11: 1707. https://doi.org/10.3390/electronics11111707

APA StyleAn, E.-J., & Oh, D.-R. (2022). A 0.0012 mm2 6-bit 700 MS/s 1 mW Calibration-Free Pseudo-Loop-Unrolled SAR ADC in 28 nm CMOS. Electronics, 11(11), 1707. https://doi.org/10.3390/electronics11111707