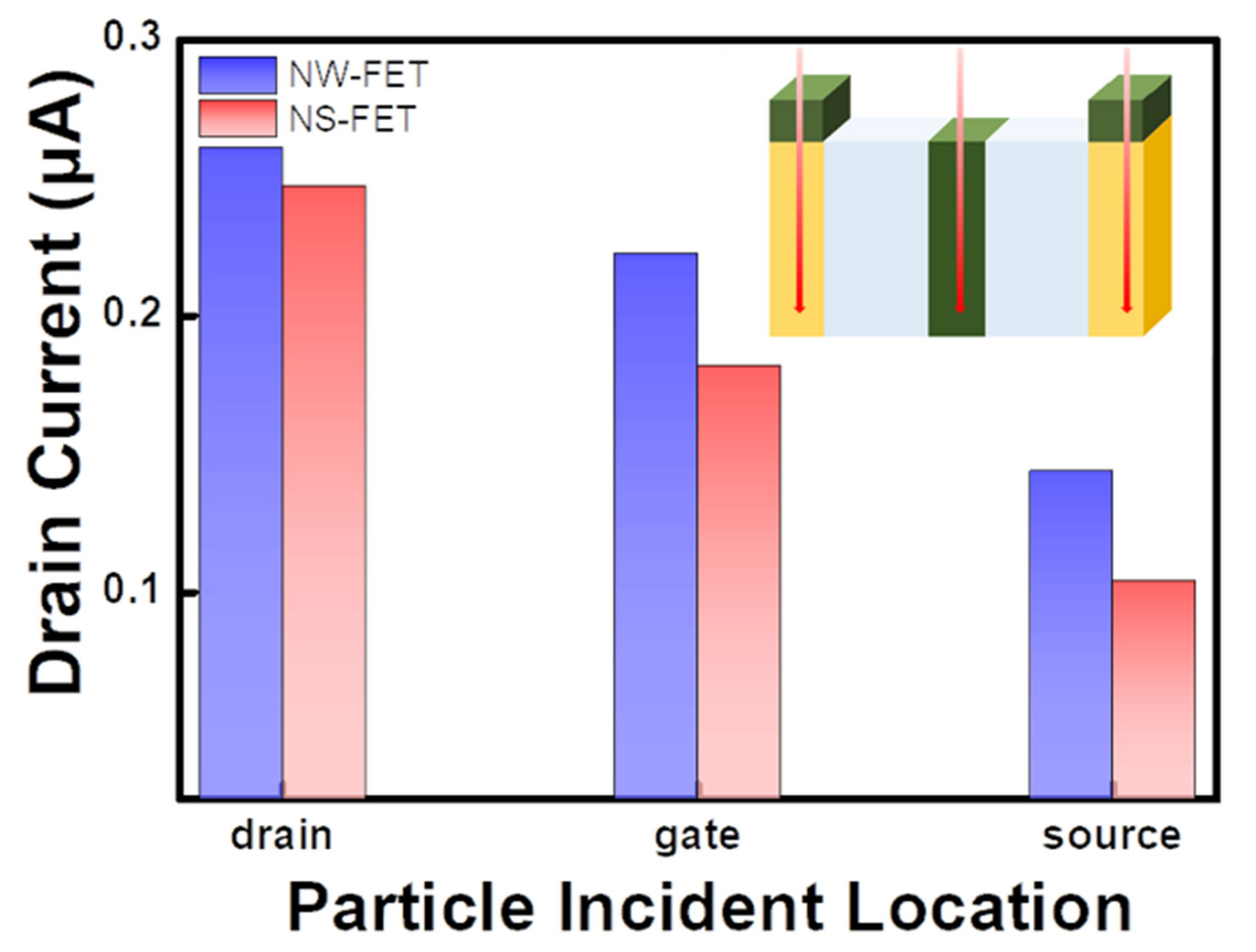

The Analysis of SEU in Nanowire FETs and Nanosheet FETs

Abstract

:1. Introduction

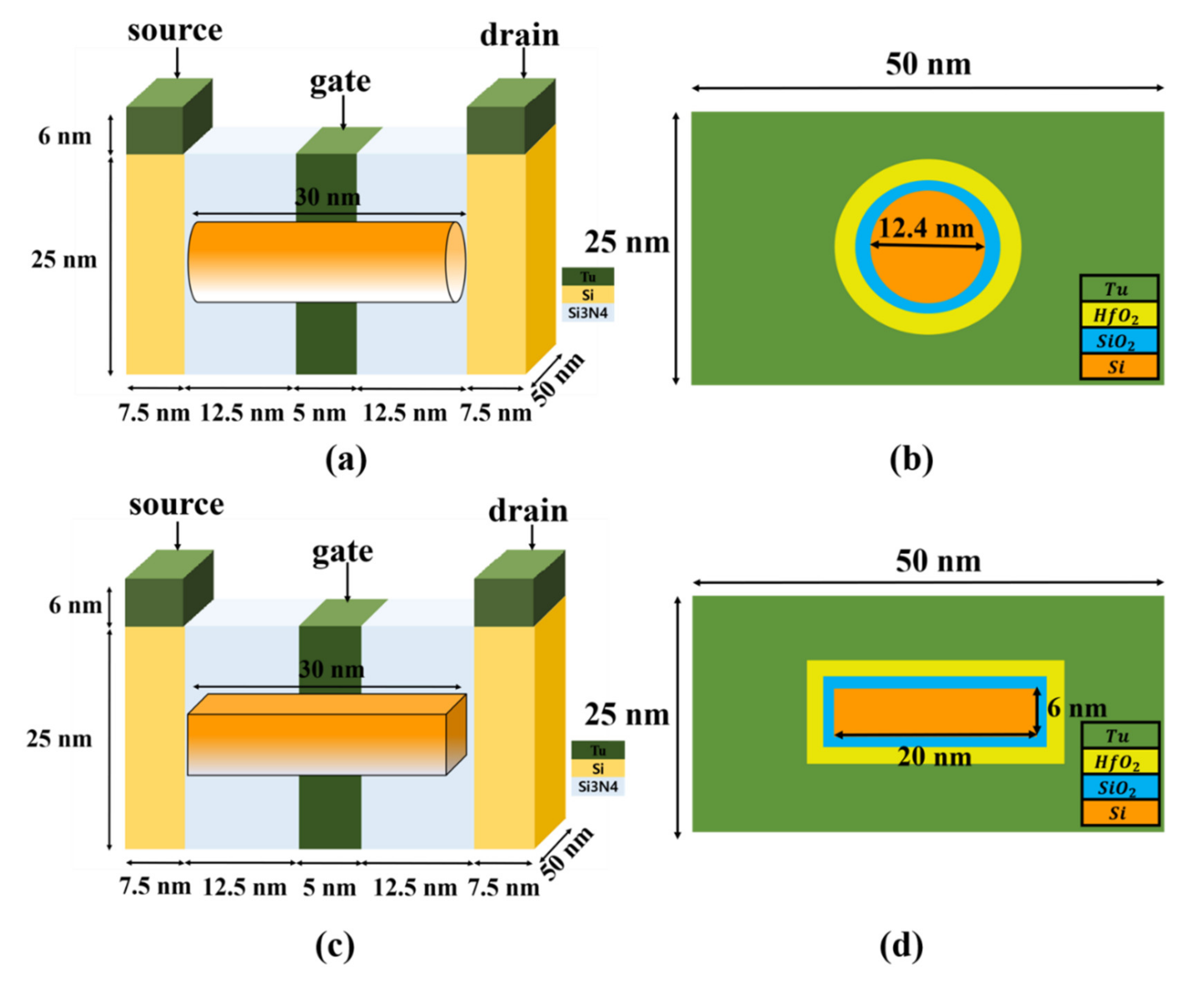

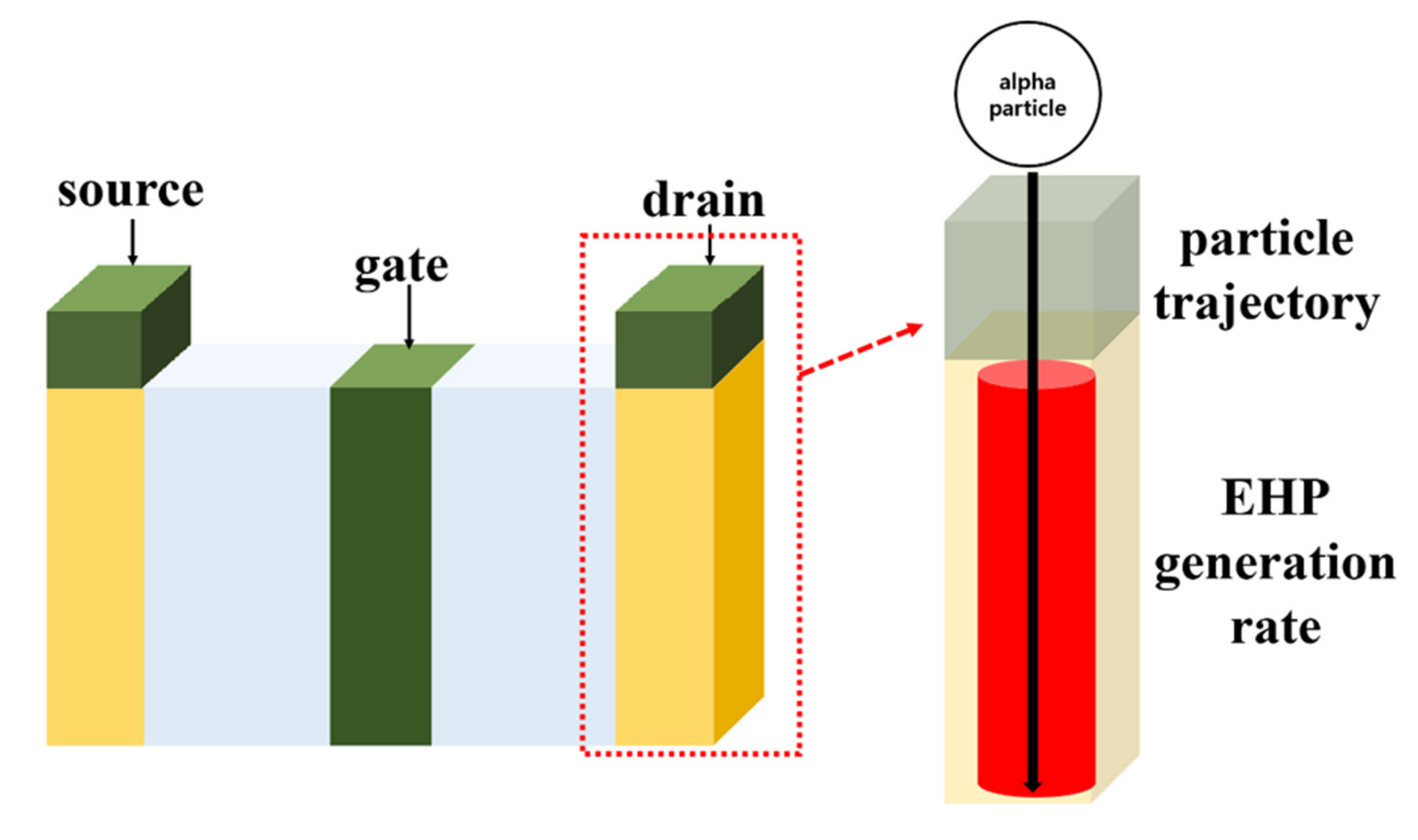

2. Proposed Structure and Operation

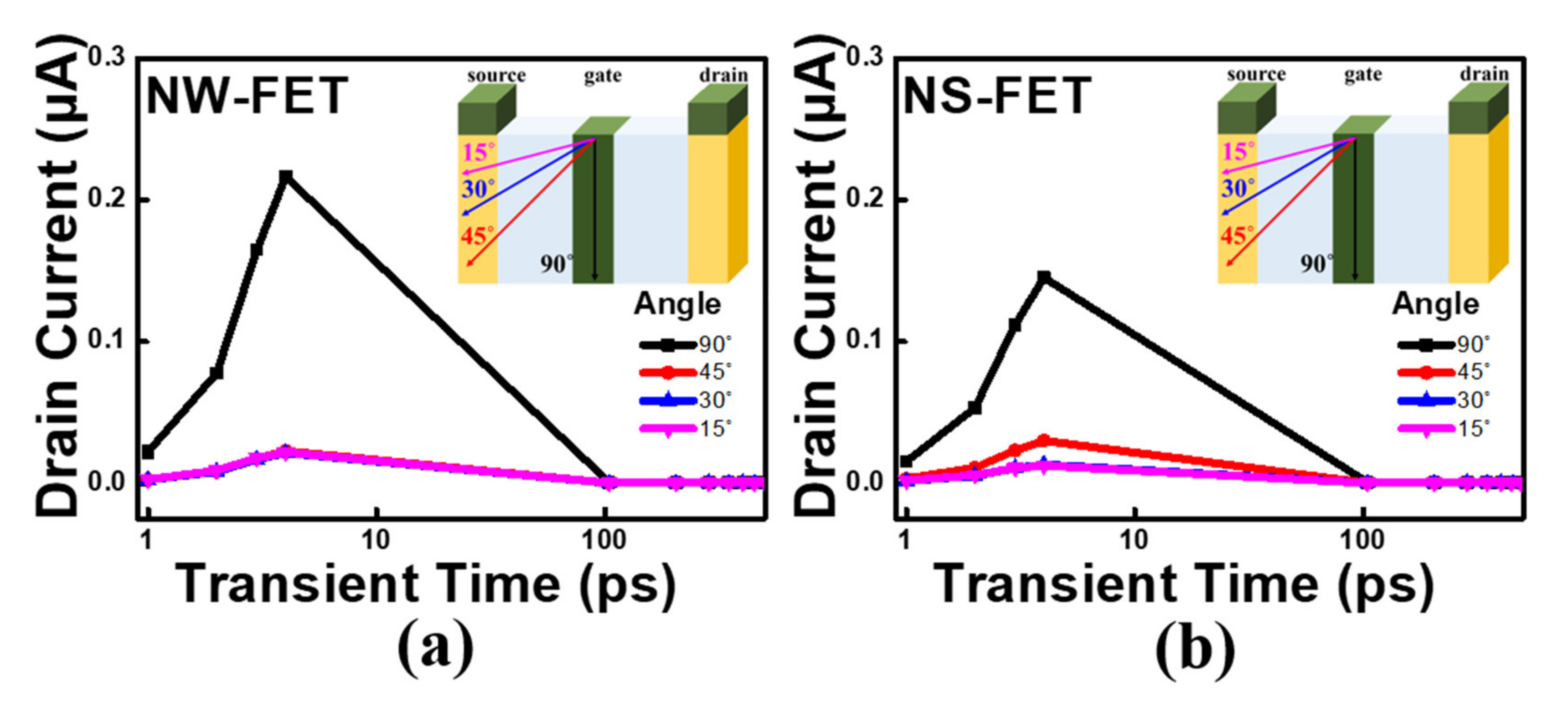

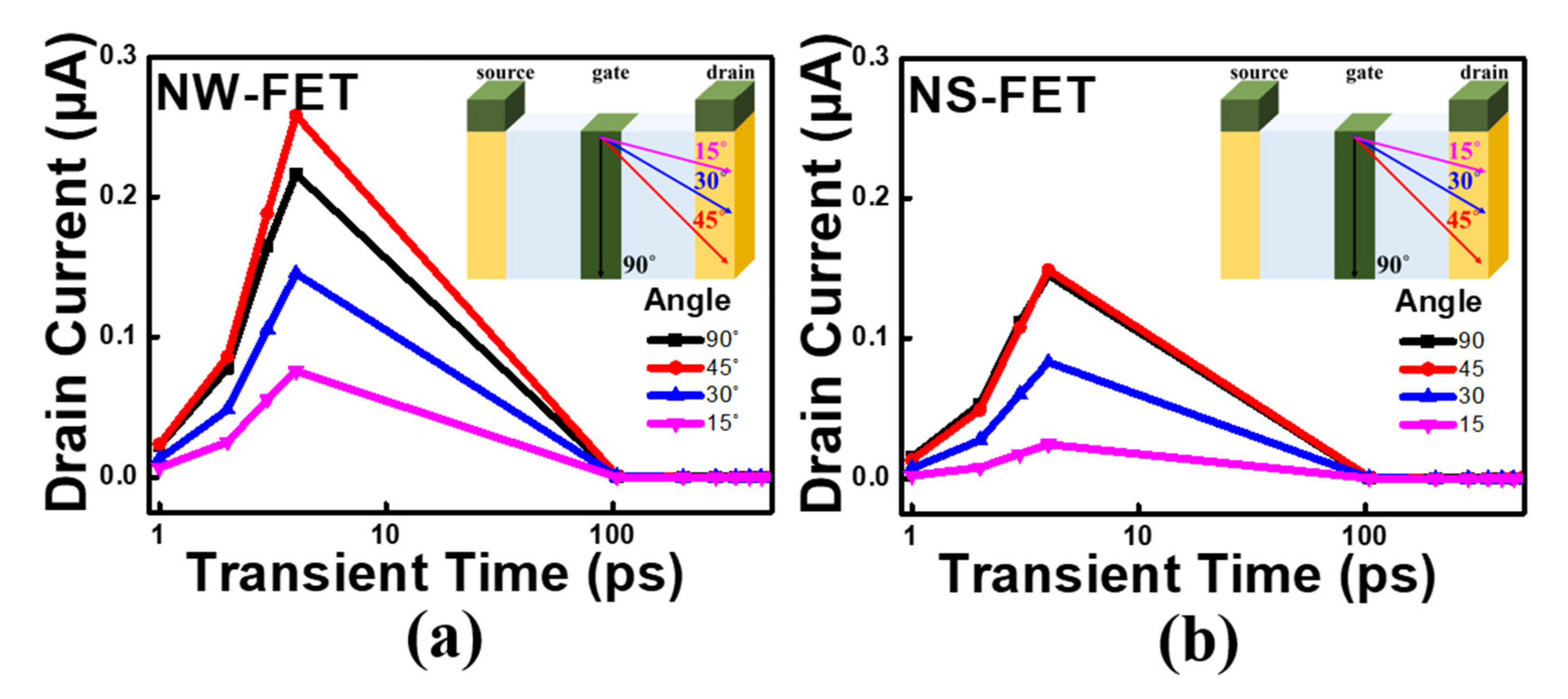

3. Results

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Gaillard, R. Single Event effects: Mechanisms and classification. In Soft Errors in Modern Electronic Systems, 1st ed.; Nicolaidis, M., Ed.; Springer: Boston, MA, USA, 2010; pp. 27–54. [Google Scholar]

- Baumann, R.C. Radiation-induced soft errors in advanced semiconductor technologies. IEEE Trans. Device Mater. Reliab. 2005, 5, 305–316. [Google Scholar] [CrossRef]

- Takeda, E.; Hisamoto, D. A new soft-error phenomenon in VLSIs: The alpha particle-induced source/drain penetration (ALPEN) effect. In Proceedings of the 26th Annual Proceedings Reliability Physics Symposium 1988, Monterey, CA, USA, 12–14 April 1988; Volume 26, pp. 109–112. [Google Scholar]

- Dodd, P.; Shaneyfelt, M.; Felix, J.; Schwank, J. Production and propagation of single-event transients in high-speed digital logic ICs. IEEE Trans. Nucl. Sci. 2004, 51, 3278–3284. [Google Scholar] [CrossRef]

- Nsengiyumva, P.; Ball, D.R.; Kauppila, J.S.; Tam, N.; McCurdy, M.; Holman, W.T.; Alles, M.L.; Bhuva, B.L.; Massengill, L.W. A Comparison of the SEU Response of Planar and FinFET D Flip-Flops at Advanced Technology Nodes. IEEE Trans. Nucl. Sci. 2016, 63, 266–272. [Google Scholar] [CrossRef]

- Hazucha, P.; Svensson, C. Impact of CMOS technology scaling on the atmospheric neutron soft error rate. IEEE Trans. Nucl. Sci. 2000, 47, 2586–2594. [Google Scholar] [CrossRef]

- Uemura, T.; Tosaka, Y.; Satoh, S. Neutron-Induced Soft-Error Simulation Technology for Logic Circuits. Jpn. J. Appl. Phys. 2006, 45, 3256–3259. [Google Scholar] [CrossRef]

- Dodd, P.; Massengill, L. Basic mechanisms and modeling of single-event upset in digital microelectronics. IEEE Trans. Nucl. Sci. 2003, 50, 583–602. [Google Scholar] [CrossRef]

- Haddad, N.F.; Kelly, A.T.; Lawrence, R.K.; Li, B.; Rodgers, J.C.; Ross, J.F.; Warren, K.M.; Weller, R.A.; Mendenhall, M.H.; Reed, R.A. Incremental Enhancement of SEU Hardened 90 nm CMOS Memory Cell. IEEE Trans. Nucl. Sci. 2011, 58, 975–980. [Google Scholar] [CrossRef]

- Munteanu, D.; Autran, J.-L. Modeling and Simulation of Single-Event Effects in Digital Devices and ICs. IEEE Trans. Nucl. Sci. 2008, 55, 1854–1878. [Google Scholar] [CrossRef]

- Atkinson, M.; Ahlbin, J. Effect of transistor density and charge sharing on single-event transients in 90-nm bulk CMOS. IEEE Trans. Nucl. Sci. 2011, 58, 2578–2584. [Google Scholar] [CrossRef]

- Dodd, P. Device simulation of charge collection and single-event upset. IEEE Trans. Nucl. Sci. 1996, 43, 561–575. [Google Scholar] [CrossRef]

- Qin, J.; Chen, S.; Chen, J. 3-D TCAD simulation study of the single event effect on 25 nm raised source-drain FinFET. Sci. China Ser. E Technol. Sci. 2012, 55, 1576–1580. [Google Scholar] [CrossRef]

- Zhang, H.; Assis, T.R.; Ball, D.R.; Narasimham, B.; Anvar, A.; Massengill, L.W.; Bhuva, B.L.; Jiang, H. Angular Effects of Heavy-Ion Strikes on Single-Event Upset Response of Flip-Flop Designs in 16-nm Bulk FinFET Technology. IEEE Trans. Nucl. Sci. 2016, 64, 491–496. [Google Scholar] [CrossRef]

- Kim, S.-D.; Guillorn, M.; Lauer, I.; Oldiges, P.; Hook, T.; Na, M.-H. Performance Trade-Offs in FinFET and Gate-All-Around Device Architectures for 7 nm-Node and Beyond; Institute of Electrical and Electronics Engineers (IEEE): Piscataway, NJ, USA, 2015; pp. 1–3. [Google Scholar]

- Loubet, N.; Hook, T.; Montanini, P.; Yeung, C.-W.; Kanakasabapathy, S.; Guillom, M.; Yamashita, T.; Zhang, J.; Miao, X.; Wang, J.; et al. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017. [Google Scholar] [CrossRef]

- Kim, J.; Lee, J.-S.; Han, J.-W.; Meyyappan, M. Single-Event Transient in FinFETs and Nanosheet FETs. IEEE Electron Device Lett. 2018, 39, 1840–1843. [Google Scholar] [CrossRef]

- Nsengiyumva, P.; Massengill, L.W.; Kauppila, J.S.; Maharrey, J.A.; Harrington, R.C.; Haeffner, T.D.; Ball, D.R.; Alles, M.L.; Bhuva, B.L.; Holman, W.T.; et al. Angular Effects on Single-Event Mechanisms in Bulk FinFET Technologies. IEEE Trans. Nucl. Sci. 2018, 65, 223–230. [Google Scholar] [CrossRef]

| NW-FET | NS-FET | |

|---|---|---|

| Channel width (nm) | 12.4 (diameter) | 20 |

| Channel height (nm) | 12.4 (diameter) | 6 |

| Channel area (nm2) Channel length (nm) SiO2 area (nm2) HfO2 area (nm2) EOT (nm) Channel doping (cm2) Source/drain doping (cm3) | 120.7 5 20.25 96.7 8.33 1 × 1 × | 119.14 5 27 128 8.33 1 × 1 × |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, Y.; Kang, M. The Analysis of SEU in Nanowire FETs and Nanosheet FETs. Electronics 2021, 10, 863. https://doi.org/10.3390/electronics10070863

Kim Y, Kang M. The Analysis of SEU in Nanowire FETs and Nanosheet FETs. Electronics. 2021; 10(7):863. https://doi.org/10.3390/electronics10070863

Chicago/Turabian StyleKim, Yunjae, and Myounggon Kang. 2021. "The Analysis of SEU in Nanowire FETs and Nanosheet FETs" Electronics 10, no. 7: 863. https://doi.org/10.3390/electronics10070863

APA StyleKim, Y., & Kang, M. (2021). The Analysis of SEU in Nanowire FETs and Nanosheet FETs. Electronics, 10(7), 863. https://doi.org/10.3390/electronics10070863