A Cascaded DC-AC-AC Grid-Tied Converter for PV Plants with AC-Link

Abstract

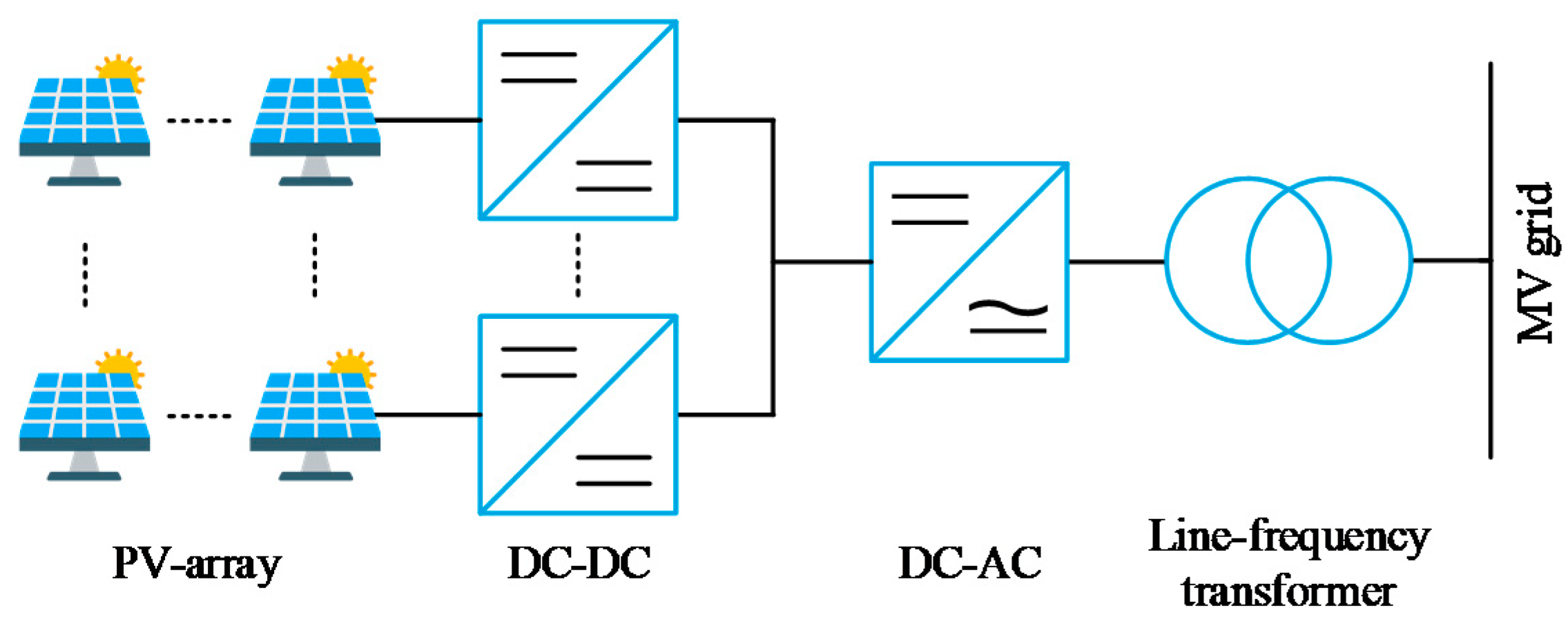

1. Introduction

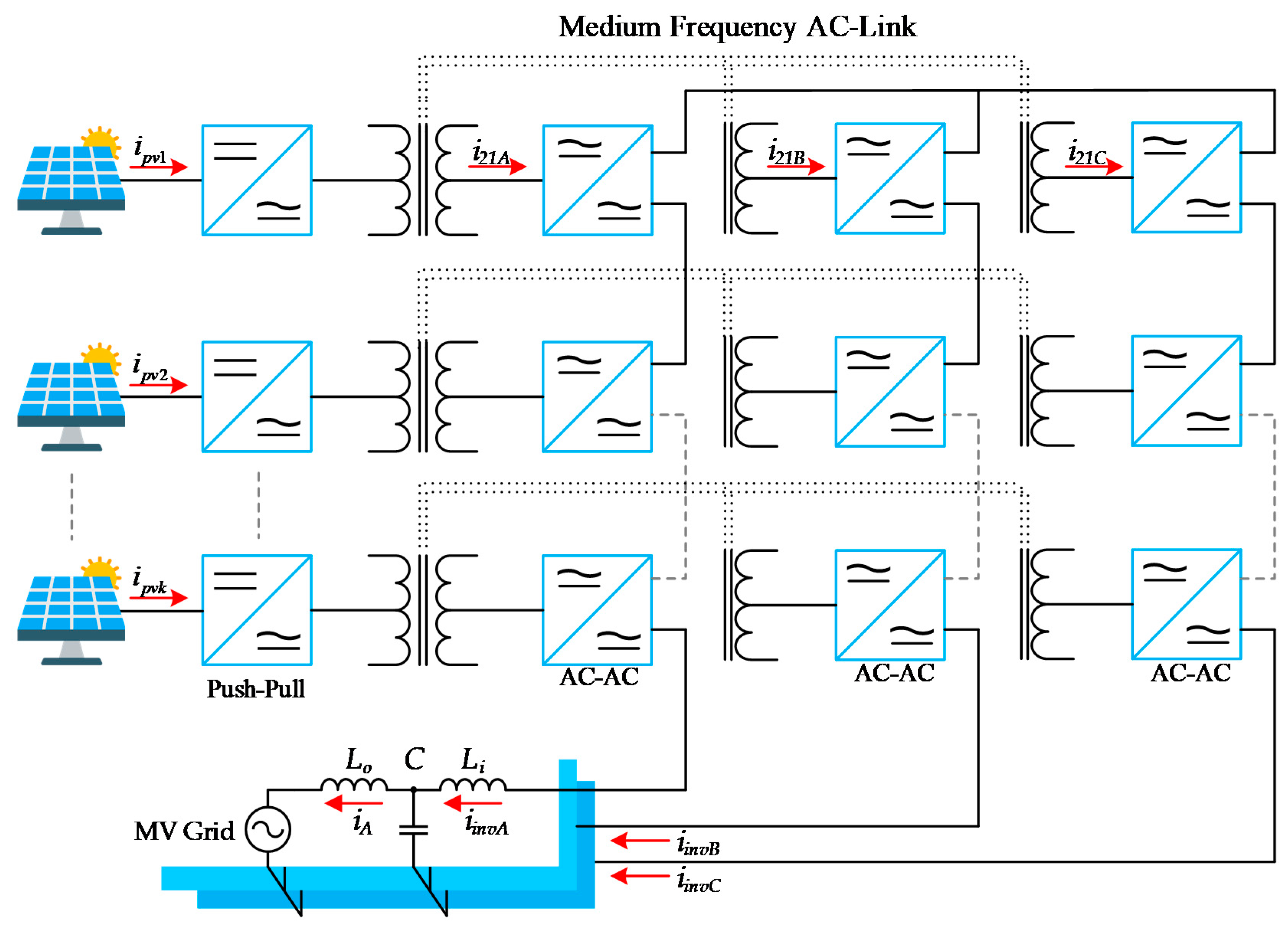

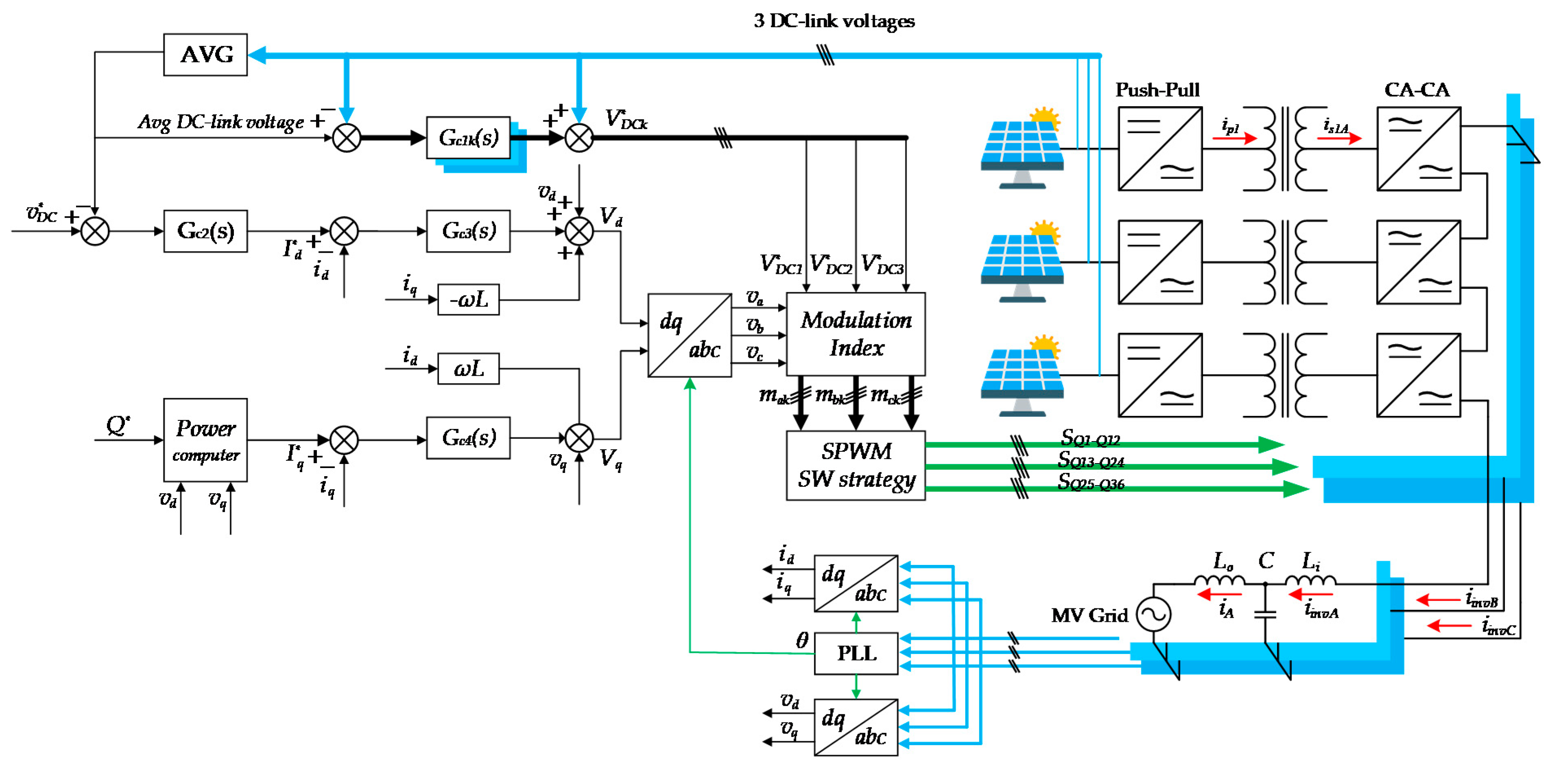

2. Grid-Tied Converter with AC Link

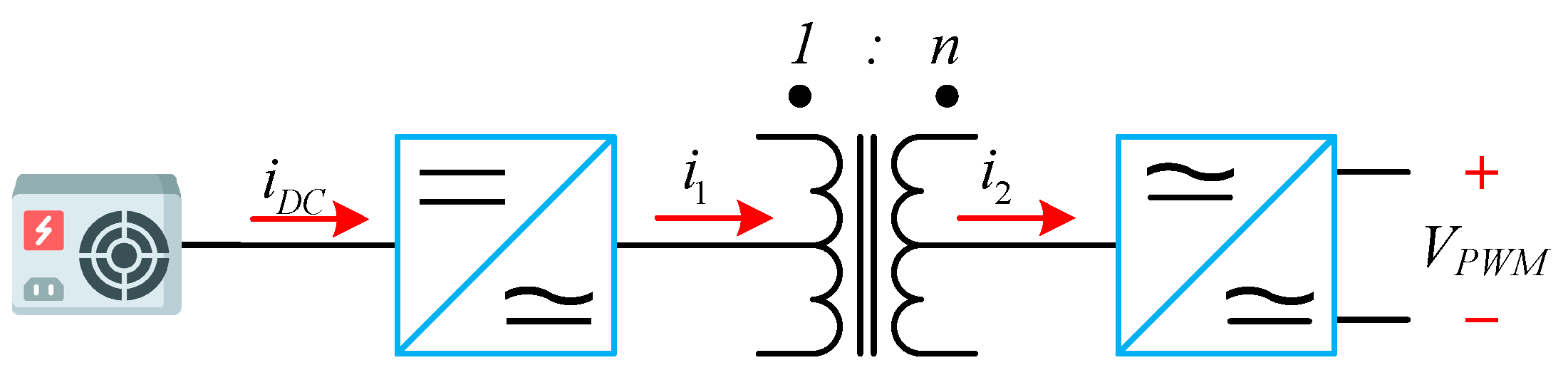

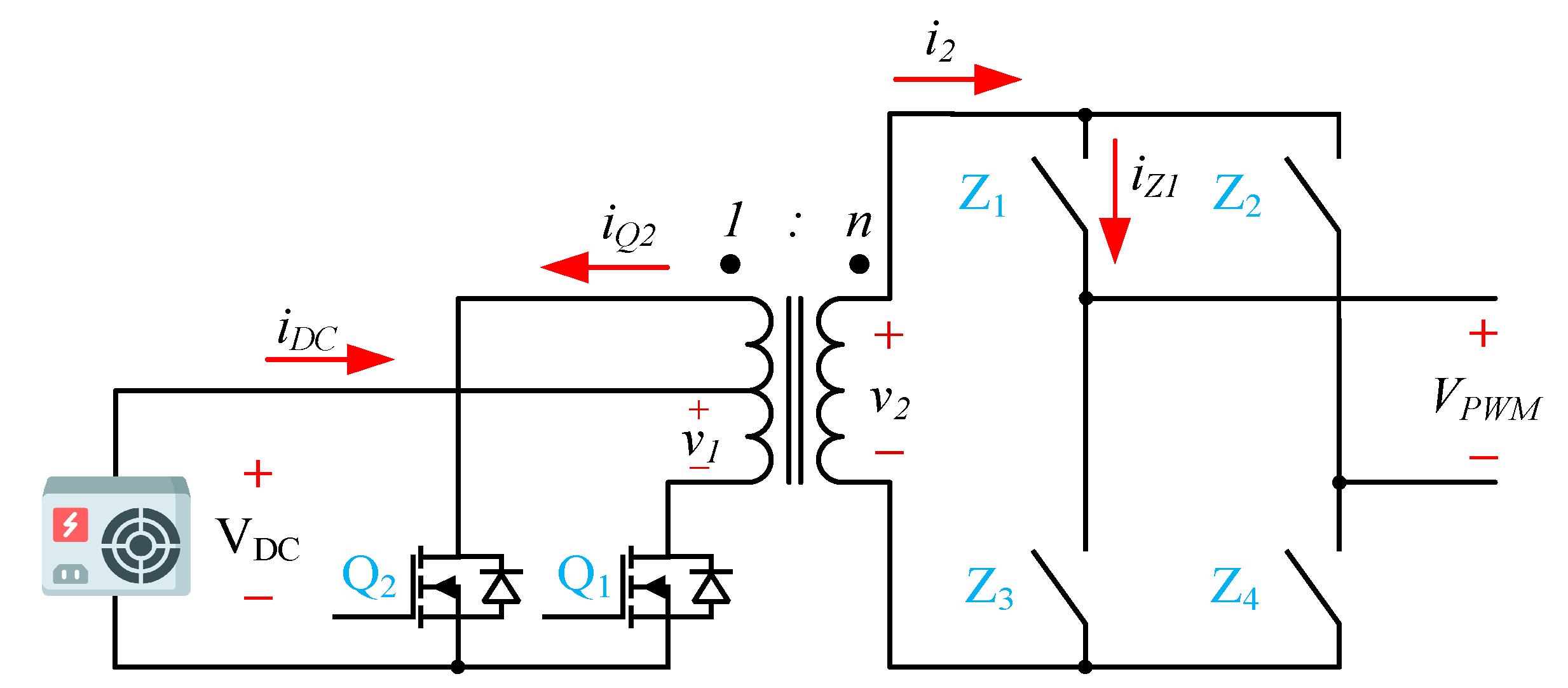

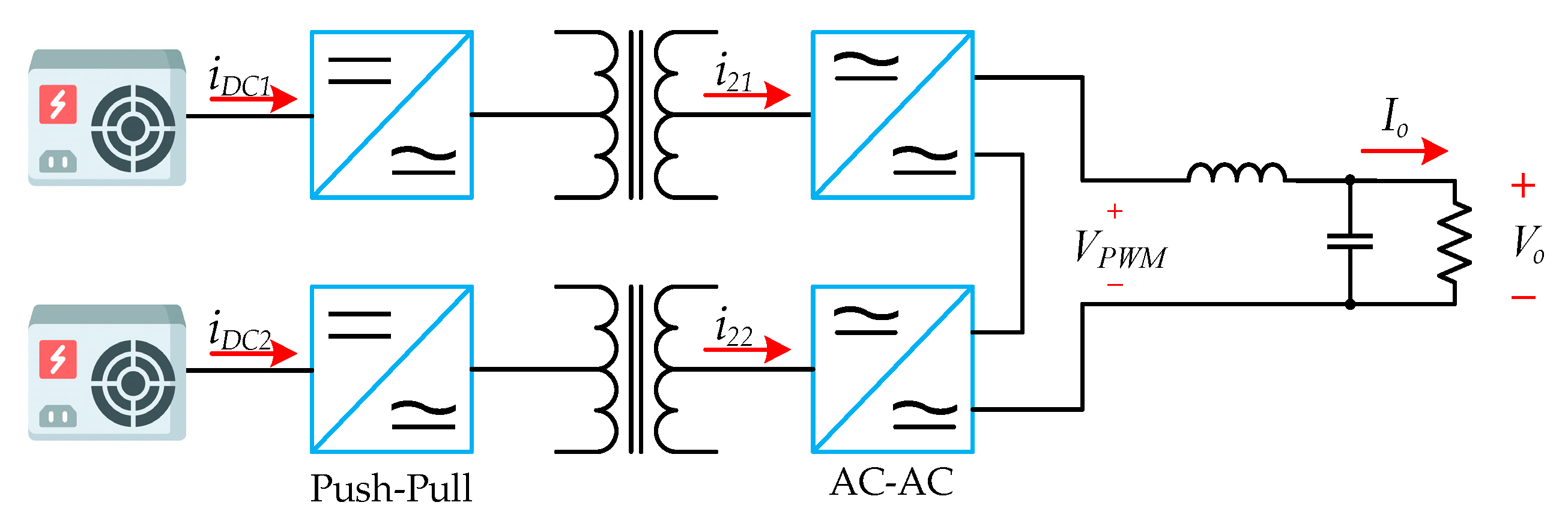

2.1. The Single-Phase DC-AC-AC Converter

- The PV modules are the first stage; they are interconnected in serial parallel arrays to satisfy the design and regulations’ power levels. For the purposes of this explanation, the PV modules are replaced by ideal DC power supplies.

- The second stage converts the DC voltage from the PV modules to a medium-frequency square AC voltage. Many converters can do this work half-bridge, full-bridge, push-pull, flyback, dual-active-bridge, and others.

- The third stage consists of a ferrite-based medium-frequency transformer, which isolates and steps up the voltage. The primary winding is plugged into stage two, and the secondary winding feeds stage four.

- The fourth stage has the task to convert a MF-AC voltage to a low-frequency AC voltage. There are two methods to accomplish that task: a two-step (involves a MF rectifier and an inverter) and a direct approach. The direct method could eliminate the MF-rectifier, get bidirectional power flow, and improve efficiency.

2.2. Modulation Strategy for a Single-Phase DC-AC-AC Converter

2.3. Design of Seven-Levels 3PH DC-AC-AC Converter

3. Control Strategy

4. Simulations

4.1. Open-Loop Off-Grid Mode Simulations

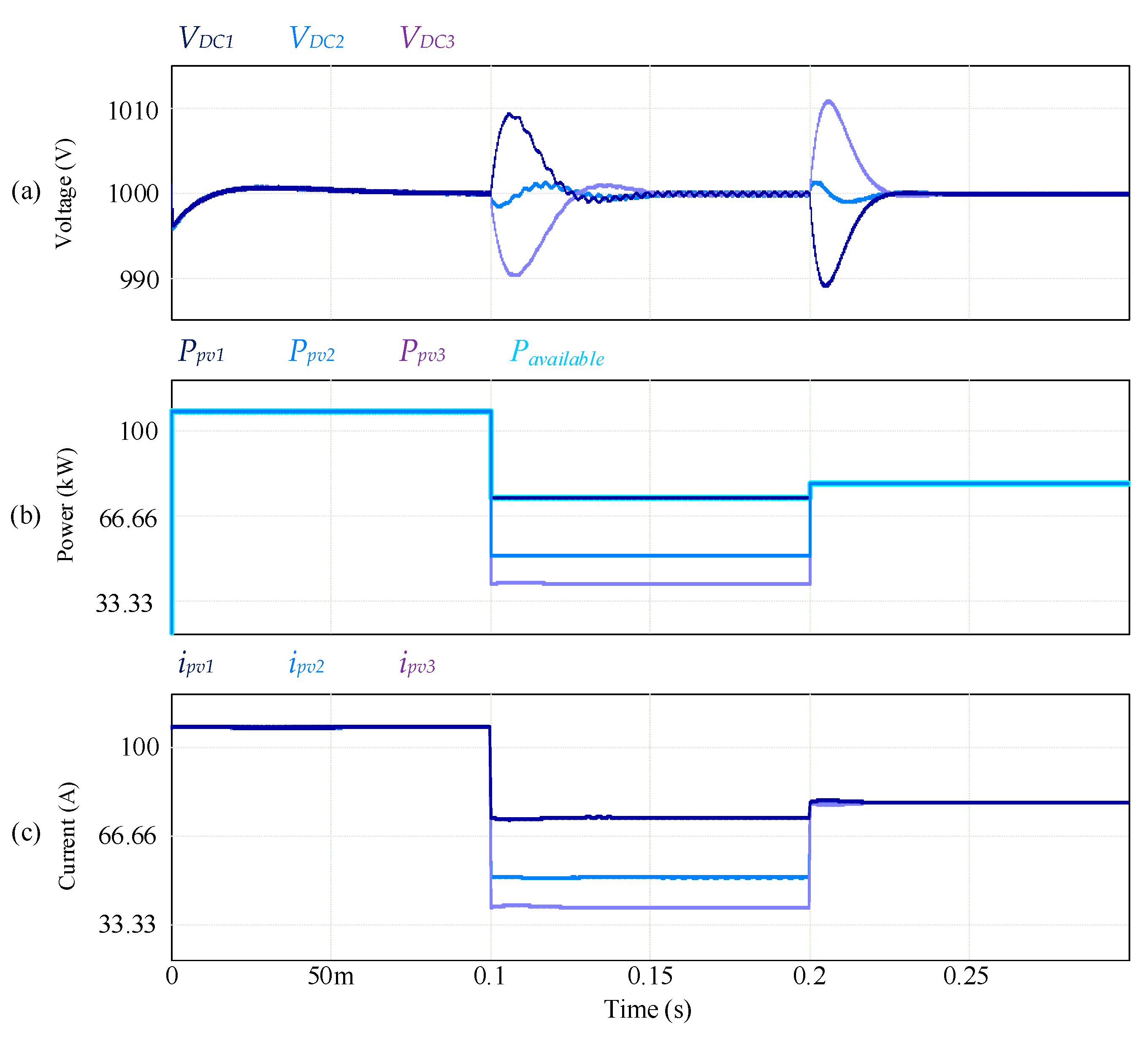

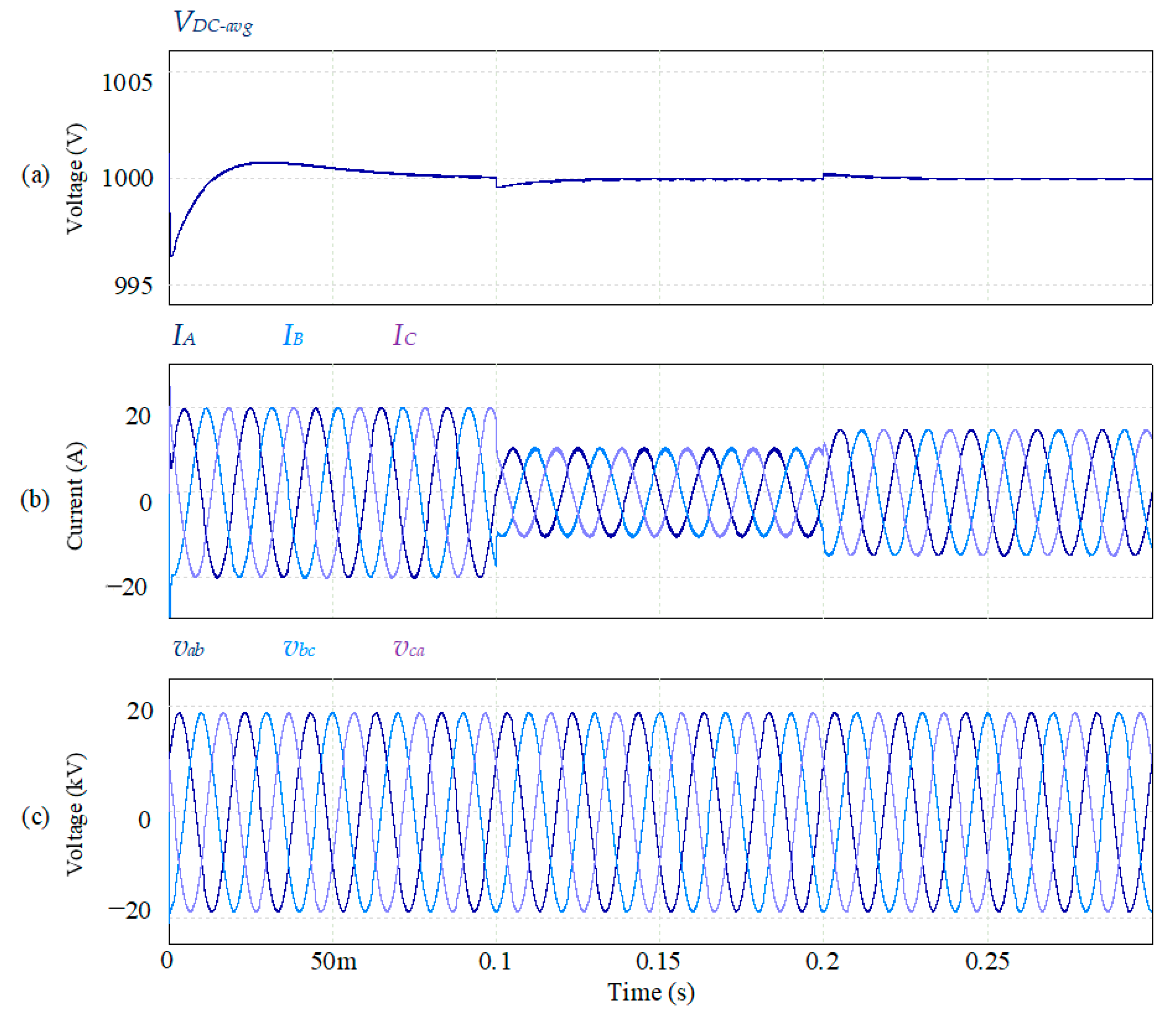

4.2. Closed-Loop On-Grid Mode Simulations

5. Experimental Results

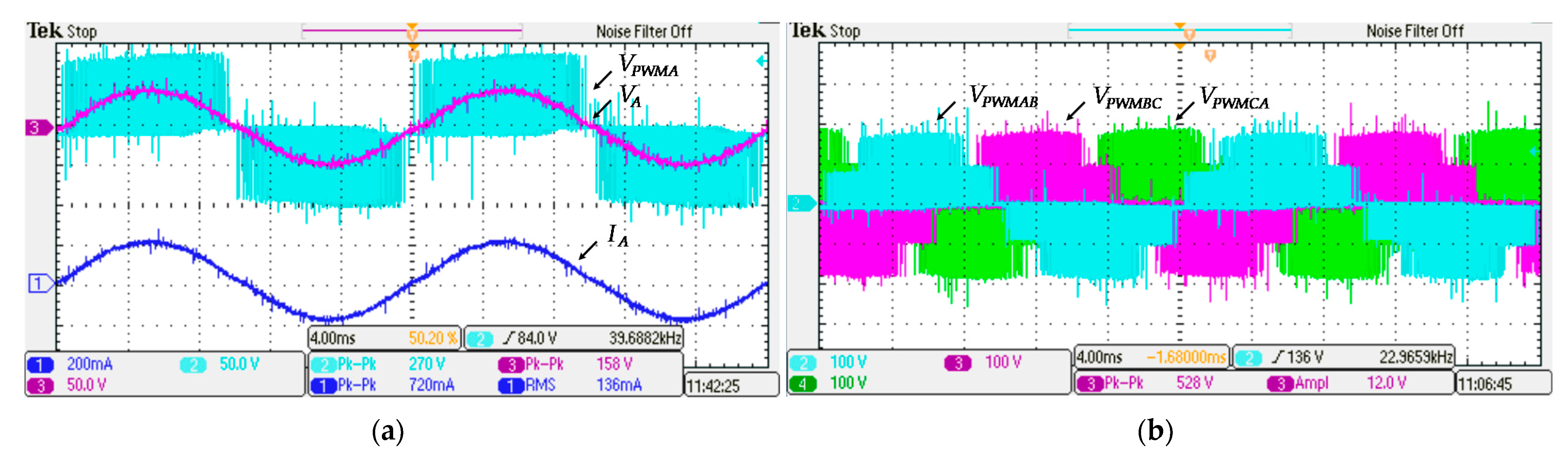

5.1. Single-Phase Multilevel DC-AC-AC Converter

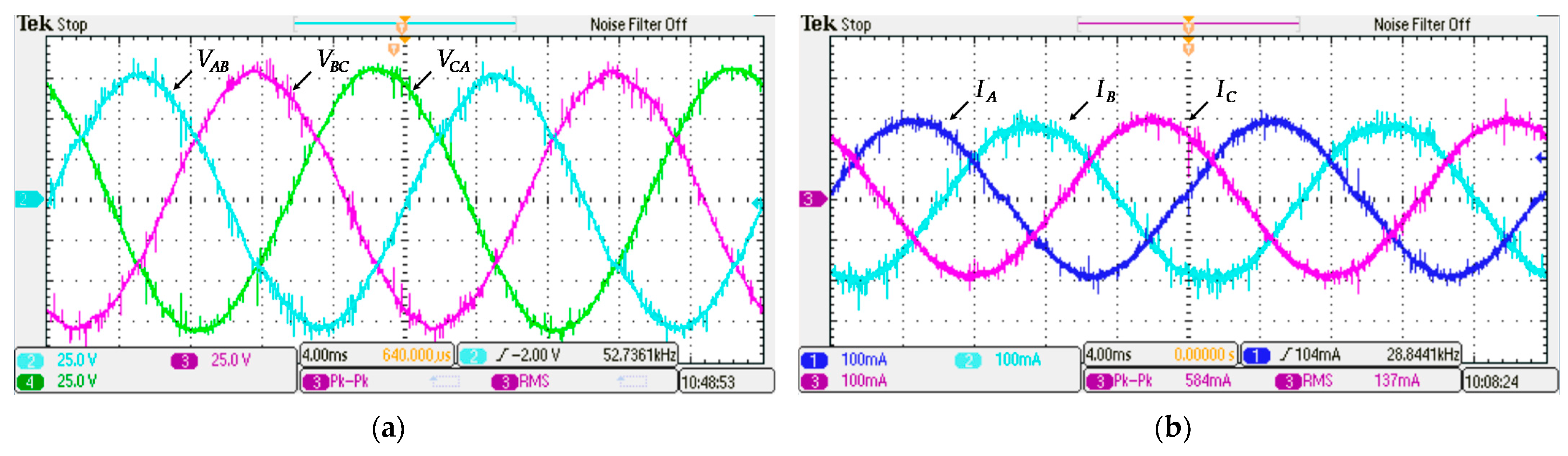

5.2. Three-Phase DC-AC-AC Converter

6. Discussion

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- International Renewable Energy Agency. Renewable Energy Statistics 2020 Statistiques D’énergie Renouvelable 2020 Estadísticas de Energía Renovable 2020 about Irena; IRENA: Abu Dhabi, United Arab Emirates, 2020; ISBN 978-92-9260-246-8. [Google Scholar]

- International Renewable Energy Agency. Renewable Power Generation Costs in 2018; IRENA: Abu Dhabi, United Arab Emirates, 2018; ISBN 978-92-9260-040-2. [Google Scholar]

- FusionSolar Utility & Commercial. Available online: https://solar.huawei.com/mea/Products/FusionSolar (accessed on 18 September 2020).

- PVS980-CS (From 2.0 to 4.6 MW). Available online: https://www.fimer.com/central-inverter-solutions/pvs980-cs-20-46-mw (accessed on 18 September 2020).

- Solar Energy Solutions. Available online: https://www.ge.com/renewableenergy/hybrid/solar-solutions (accessed on 18 September 2020).

- Huawei Smart PV Solution Contributes to Successful Grid Connection of World’s Largest PV Plant. Available online: https://solar.huawei.com/mea/news/mea/Huawei-Smart-PV-Solution-Contributes-to-Successful-Grid-Connection-of-World-Largest-PV-Plant (accessed on 1 November 2020).

- Kerekes, T.; Koutroulis, E.; Séra, D.; Teodorescu, R.; Katsanevakis, M. An Optimization Method for Designing Large PV Plants. IEEE J. Photovolt. 2013, 3, 814–822. [Google Scholar] [CrossRef]

- Islam, R.; Guo, Y.; Zhu, J. A Multilevel Medium-Voltage Inverter for Step-Up-Transformer-Less Grid Connection of Photovoltaic Power Plants. IEEE J. Photovolt. 2014, 4, 881–889. [Google Scholar] [CrossRef]

- Choi, H.; Ciobotaru, M.; Jang, M.; Agelidis, V.G. Performance of Medium-Voltage DC-Bus PV System Architecture Utilizing High-Gain DC–DC Converter. IEEE Trans. Sustain. Energy 2015, 6, 464–473. [Google Scholar] [CrossRef]

- Islam, R.; Mahfuz-Ur-Rahman, A.M.; Muttaqi, K.M.; Sutanto, D. State-of-the-Art of the Medium-Voltage Power Converter Technologies for Grid Integration of Solar Photovoltaic Power Plants. IEEE Trans. Energy Convers. 2019, 34, 372–384. [Google Scholar] [CrossRef]

- Zeb, K.; Islam, S.U.; Uddin, W.; Khan, I.; Khan, M.; Ali, S.; Busarello, T.; Kim, H.J. An Overview of Transformerless Inverters for Grid Connected Photovoltaic System. In Proceedings of the 2018 International Conference on Computing, Electronic and Electrical Engineering (ICE Cube), Quetta, Pakistan, 12–13 November 2018; pp. 1–6. [Google Scholar] [CrossRef]

- Brando, G.; Dannier, A.; Del Pizzo, A.; Rizzo, R. A high performance control technique of power electronic transformers in medium voltage grid-connected PV plants. In Proceedings of the the XIX International Conference on Electrical Machines—ICEM 2010, Rome, Italy, 6–8 September 2010; pp. 1–6. [Google Scholar] [CrossRef]

- GEAFOL Cast-Resin Transformers 100 to 16,000 kVA. Available online: https://www.simosynergy.com/download/Catalog_TV1_GEAFOL_Cast-resin_Transformers.pdf (accessed on 6 October 2020).

- Mainali, K.; Tripathi, A.; Madhusoodhanan, S.; Kadavelugu, A.; Patel, D.; Hazra, S.; Hatua, K.; Bhattacharya, S. A Transformerless Intelligent Power Substation: A three-phase SST enabled by a 15-kV SiC IGBT. IEEE Power Electron. Mag. 2015, 2, 31–43. [Google Scholar] [CrossRef]

- Salem, A.; Van Khang, H.; Robbersmyr, K.G.; Gae, M.N.; Rodriguez, J. Voltage Source Multilevel Inverters With Reduced Device Count: Topological Review and Novel Comparative Factors. IEEE Trans. Power Electron. 2021, 36, 2720–2747. [Google Scholar] [CrossRef]

- Xiao, H. Overview of Transformerless Photovoltaic Grid-Connected Inverters. IEEE Trans. Power Electron. 2020, 36, 533–548. [Google Scholar] [CrossRef]

- Khan, N.H.; Forouzesh, M.; Siwakoti, Y.P.; Li, L.; Kerekes, T.; Blaabjerg, F. Transformerless Inverter Topologies for Single-Phase Photovoltaic Systems: A Comparative Review. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 805–835. [Google Scholar] [CrossRef]

- Pilgaard, M.; Sundvall, J. Three-Level Inverter for Medium Level Voltage Using Series Connected IGBTs. Master’s Thesis, Aalborg University, Aalborg, Denmark, 2008. [Google Scholar]

- Villanueva, E.; Correa, P.; Rodriguez, J.; Pacas, M. Control of a Single-Phase Cascaded H-Bridge Multilevel Inverter for Grid-Connected Photovoltaic Systems. IEEE Trans. Ind. Electron. 2009, 56, 4399–4406. [Google Scholar] [CrossRef]

- Gultekin, B.; Ermis, M. Cascaded Multilevel Converter-Based Transmission STATCOM: System Design Methodology and Development of a 12 kV ± 12 MVAr Power Stage. IEEE Trans. Power Electron. 2013, 28, 4930–4950. [Google Scholar] [CrossRef]

- Islam, R.; Guo, Y.; Zhu, J. A High-Frequency Link Multilevel Cascaded Medium-Voltage Converter for Direct Grid Integration of Renewable Energy Systems. IEEE Trans. Power Electron. 2014, 29, 4167–4182. [Google Scholar] [CrossRef]

- Calais, M.; Agelidis, V.G.; Borle, L.J.; Dymond, M.S. A transformerless five level cascaded inverter based single phase photovoltaic system. In Proceedings of the 2000 IEEE 31st Annual Power Electronics Specialists Conference. Conference Proceedings (Cat. No.00CH37018), Galway, Ireland, 23 June 2000; Volume 3, pp. 1173–1178. [Google Scholar] [CrossRef]

- Farivar, G.; Hredzak, B.; Agelidis, V.G. A DC-Side Sensorless Cascaded H-Bridge Multilevel Converter-Based Photovoltaic System. IEEE Trans. Ind. Electron. 2016, 63, 4233–4241. [Google Scholar] [CrossRef]

- Rath, I.C.; Shukla, A. Review of Three Phase Transformer-less PV Converters. In Proceedings of the 2019 IEEE International Conference on Sustainable Energy Technologies (ICSET), Bhubaneswar, India, 26 February–1 March 2019; Volume 1, pp. 063–068. [Google Scholar] [CrossRef]

- Islam, M.R.; Guo, Y.; Zhu, J. Multilevel Converters for Step-Up-Transformer-Less Direct Integration of Renewable Generation Units with Medium Voltage Smart Microgrids. In Large Scale Renewable Power Generation Advances in Technologies for Generation, Transmission and Storage; Jahangir Hossain, A.M., Ed.; Springer: Berlin, Germany, 2014; pp. 127–149. ISBN 9789814585293. [Google Scholar] [CrossRef]

- Ruderman, A. About Voltage Total Harmonic Distortion for Single- and Three-Phase Multilevel Inverters. IEEE Trans. Ind. Electron. 2015, 62, 1548–1551. [Google Scholar] [CrossRef]

- Daher, S.; Schmid, J.; Antunes, F.L.M. Multilevel Inverter Topologies for Stand-Alone PV Systems. IEEE Trans. Ind. Electron. 2008, 55, 2703–2712. [Google Scholar] [CrossRef]

- Krug, D.; Bernet, S.; Fazel, S.S.; Jalili, K.; Malinowski, M. Comparison of 2.3-kV Medium-Voltage Multilevel Converters for Industrial Medium-Voltage Drives. IEEE Trans. Ind. Electron. 2007, 54, 2979–2992. [Google Scholar] [CrossRef]

- Kouro, S.; Malinowski, M.; Gopakumar, K.; Pou, J.; Franquelo, L.G.; Wu, B.; Rodriguez, J.; Perez, M.A.; Leon, J.I. Recent Advances and Industrial Applications of Multilevel Converters. IEEE Trans. Ind. Electron. 2010, 57, 2553–2580. [Google Scholar] [CrossRef]

- Lai, J.-S.; Peng, F.Z. Multilevel converters-a new breed of power converters. IEEE Trans. Ind. Appl. 1996, 32, 509–517. [Google Scholar] [CrossRef]

- Meynard, T.A.; Foch, H. Multi-Level Choppers for High Voltage Applications. EPE J. 1992, 2, 45–50. [Google Scholar] [CrossRef]

- Escalante, M.F.; Vannier, J.; Arzande, A. Flying capacitor multilevel inverters and DTC motor drive applications. IEEE Trans. Ind. Electron. 2002, 49, 809–815. [Google Scholar] [CrossRef]

- Rodriguez, J.; Lai, J.-S.; Peng, F.Z. Multilevel inverters: A survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef]

- Rodriguez, J.; Franquelo, L.G.; Kouro, S.; Leon, J.I.; Portillo, R.C.; Prats, M.; Ángeles, M.; Perez, M.A. Multilevel Converters: An Enabling Technology for High-Power Applications. Proc. IEEE 2009, 97, 1786–1817. [Google Scholar] [CrossRef]

- Lesnicar, A.; Marquardt, R. An innovative modular multilevel converter topology suitable for a wide power range. In Proceedings of the 2003 IEEE Bologna Power Tech Conference Proceedings, Bologna, Italy, 23–26 June 2003; Volume 3, p. 6. [Google Scholar] [CrossRef]

- Allebrod, S.; Hamerski, R.; Marquardt, R. New transformerless, scalable Modular Multilevel Converters for HVDC-transmission. In Proceedings of the 2008 IEEE Power Electronics Specialists Conference, Rhodes, Greece, 15–19 June 2008; pp. 174–179. [Google Scholar]

- Otero-De-Leon, R.; Mohan, N. Full-bridge Modular Multilevel Converter with High Frequency Link for Photovoltaic applications. In Proceedings of the 2015 IEEE 24th International Symposium on Industrial Electronics (ISIE), Buzios, Brazil, 3–5 June 2015; pp. 294–299. [Google Scholar] [CrossRef]

- Abu-Siada, A.; Abu-Siada, A.; Islam, S.M.; Dahidah, M. A New Cascaded Multilevel Inverter Topology with Galvanic Isolation. IEEE Trans. Ind. Appl. 2018, 54, 3463–3472. [Google Scholar] [CrossRef]

- Iyer, K.; Baranwal, R.; Mohan, N. A High-Frequency AC-Link Single-Stage Asymmetrical Multilevel Converter for Grid Integration of Renewable Energy Systems. IEEE Trans. Power Electron. 2016, 32, 5087–5108. [Google Scholar] [CrossRef]

- Elsayad, N.; Mohammed, O.A. A cascaded high frequency AC link system for large-scale PV-assisted EV fast charging stations. In Proceedings of the 2017 IEEE Transportation Electrification Conference and Expo (ITEC), Chicago, IL, USA, 22–24 June 2017; pp. 90–94. [Google Scholar] [CrossRef]

- Sayed, M.A.; Suzuki, K.; Takeshita, T.; Kitagawa, W. PWM Switching Technique for Three-Phase Bidirectional Grid-Tie DC–AC–AC Converter With High-Frequency Isolation. IEEE Trans. Power Electron. 2018, 33, 845–858. [Google Scholar] [CrossRef]

- Wang, M.; Huang, Q.; Yu, W.; Huang, A.Q. An isolated bi-directional high-frequency-AC link DC-AC converter using hybrid SiC switches with carrier-based unipolar modulation technique. In Proceedings of the 2015 IEEE 2nd International Future Energy Electronics Conference (IFEEC), Taipei, Taiwan, 1–4 November 2015; pp. 1–8. [Google Scholar] [CrossRef]

- Krishnamoorthy, H.S.; Essakiappan, S.; Enjeti, P.N.; Balog, R.S.; Ahmed, S. A new multilevel converter for Megawatt scale solar photovoltaic utility integration. In Proceedings of the 2012 Twenty-Seventh Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Orlando, FL, USA, 5–9 February 2012; pp. 1431–1438. [Google Scholar] [CrossRef]

- Essakiappan, S.; Krishnamoorthy, H.S.; Enjeti, P.; Balog, R.S.; Ahmed, S. Multilevel Medium-Frequency Link Inverter for Utility Scale Photovoltaic Integration. IEEE Trans. Power Electron. 2015, 30, 3674–3684. [Google Scholar] [CrossRef]

- Barrios, M.A.; Cárdenas, V.; Sandoval, J.M.; Gonzalez, M.; Miranda, H. DC-AC-AC Converter for PV Plant in Medium Voltage Grid-Connected Systems. In Proceedings of the 2018 14th International Conference on Power Electronics (CIEP), Cholula, Mexico, 24–26 October 2018; pp. 146–154. [Google Scholar]

- Burany, N. Nándor Burány Safe Control of Four-Quadrant Switches. In Proceedings of the Conference Record of the IEEE Industry Applications Society Annual Meeting, San Diego, CA, USA, 1–5 October 1989; pp. 1190–1194. [Google Scholar]

- Enjeti, P.; Choi, S. An approach to realize higher power PWM AC controller. In Proceedings of the Eighth Annual Applied Power Electronics Conference and Exposition, San Diego, CA, USA, 7–11 March 1993; pp. 323–327. [Google Scholar]

- Wheeler, P.; Clare, J.C.; Empringham, L. Enhancement of Matrix Converter Output Waveform Quality Using Minimized Commutation Times. IEEE Trans. Ind. Electron. 2004, 51, 240–244. [Google Scholar] [CrossRef]

- Beristain, J.; Bordonau, J.; Gilabert, A.; Velasco, G. Synthesis and modulation of a single phase DC/AC converter with high-frequency isolation in photovoltaic energy applications. In Proceedings of the IEEE 34th Annual Conference on Power Electronics Specialist, PESC ’03, Acapulco, Mexico, 15–19 June 2003; Volume 3, pp. 1191–1196. [Google Scholar] [CrossRef]

- Mohan, N.; Undeland, T.M.; Robbins, W.P. Power Electronics Converters, Applications, and Design; John Wiley & Sons, Inc.: Chichester, UK, 2007; Volume 4, ISBN 0136865933. [Google Scholar] [CrossRef]

- Palanivel, P.; Dash, S. Analysis of THD and output voltage performance for cascaded multilevel inverter using carrier pulse width modulation techniques. IET Power Electron. 2011, 4, 951. [Google Scholar] [CrossRef]

- McLyman, C.W.T. Transformer and Inductor Design Handbook, 4th ed.; CRC Press: Boca Raton, FL, USA, 2011; ISBN 9781439836873. [Google Scholar]

- Kouro, S.; Wu, B.; Moya, A.; Villanueva, E.; Correa, P.; Rodriguez, J. Control of a cascaded H-bridge multilevel converter for grid connection of photovoltaic systems. In Proceedings of the 2009 35th Annual Conference of IEEE Industrial Electronics, Porto, Portugal, 3–5 November 2009; pp. 3976–3982. [Google Scholar]

- Akagi, H.; Kanazawa, Y.; Nabae, A. Instantaneous Reactive Power Compensators Comprising Switching Devices without Energy Storage Components. IEEE Trans. Ind. Appl. 1984, 625–630. [Google Scholar] [CrossRef]

- Rivera, S.; Kouro, S.; Wu, B.; Leon, J.I.; Rodríguez, J.; Franquelo, L.G. Cascaded H-bridge multilevel converter multistring topology for large scale photovoltaic systems. In Proceedings of the 2011 IEEE International Symposium on Industrial Electronics, Gdansk, Poland, 27–30 June 2011; pp. 1837–1844. [Google Scholar] [CrossRef]

- 6.5 kV IGBT Modules in IHV Housing. Available online: https://www.infineon.com/cms/en/product/power/igbt/igbt-modules/ihv-6500v/ (accessed on 28 September 2020).

| Parameter | Acronym | Value |

|---|---|---|

| Rated Power | Po | 324.16 kW |

| Output voltage | VLL | 13.20 kV |

| DC-link voltage | VDC | 1 kV |

| Switching frequency | fsw | 9.96 kHz |

| Output levels | m | 7 |

| Inductor | Li | 60 mF |

| Capacitor | C | 100 nF |

| Line-frequency | f | 60 Hz |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Barrios, M.A.; Cárdenas, V.; Sandoval, J.M.; Guerrero, J.M.; Vasquez, J.C. A Cascaded DC-AC-AC Grid-Tied Converter for PV Plants with AC-Link. Electronics 2021, 10, 409. https://doi.org/10.3390/electronics10040409

Barrios MA, Cárdenas V, Sandoval JM, Guerrero JM, Vasquez JC. A Cascaded DC-AC-AC Grid-Tied Converter for PV Plants with AC-Link. Electronics. 2021; 10(4):409. https://doi.org/10.3390/electronics10040409

Chicago/Turabian StyleBarrios, Manuel A., Víctor Cárdenas, Jose M. Sandoval, Josep M. Guerrero, and Juan C. Vasquez. 2021. "A Cascaded DC-AC-AC Grid-Tied Converter for PV Plants with AC-Link" Electronics 10, no. 4: 409. https://doi.org/10.3390/electronics10040409

APA StyleBarrios, M. A., Cárdenas, V., Sandoval, J. M., Guerrero, J. M., & Vasquez, J. C. (2021). A Cascaded DC-AC-AC Grid-Tied Converter for PV Plants with AC-Link. Electronics, 10(4), 409. https://doi.org/10.3390/electronics10040409