Generalized Circuit Averaging Technique for Two-Switch PWM DC-DC Converters in CCM

Abstract

1. Introduction

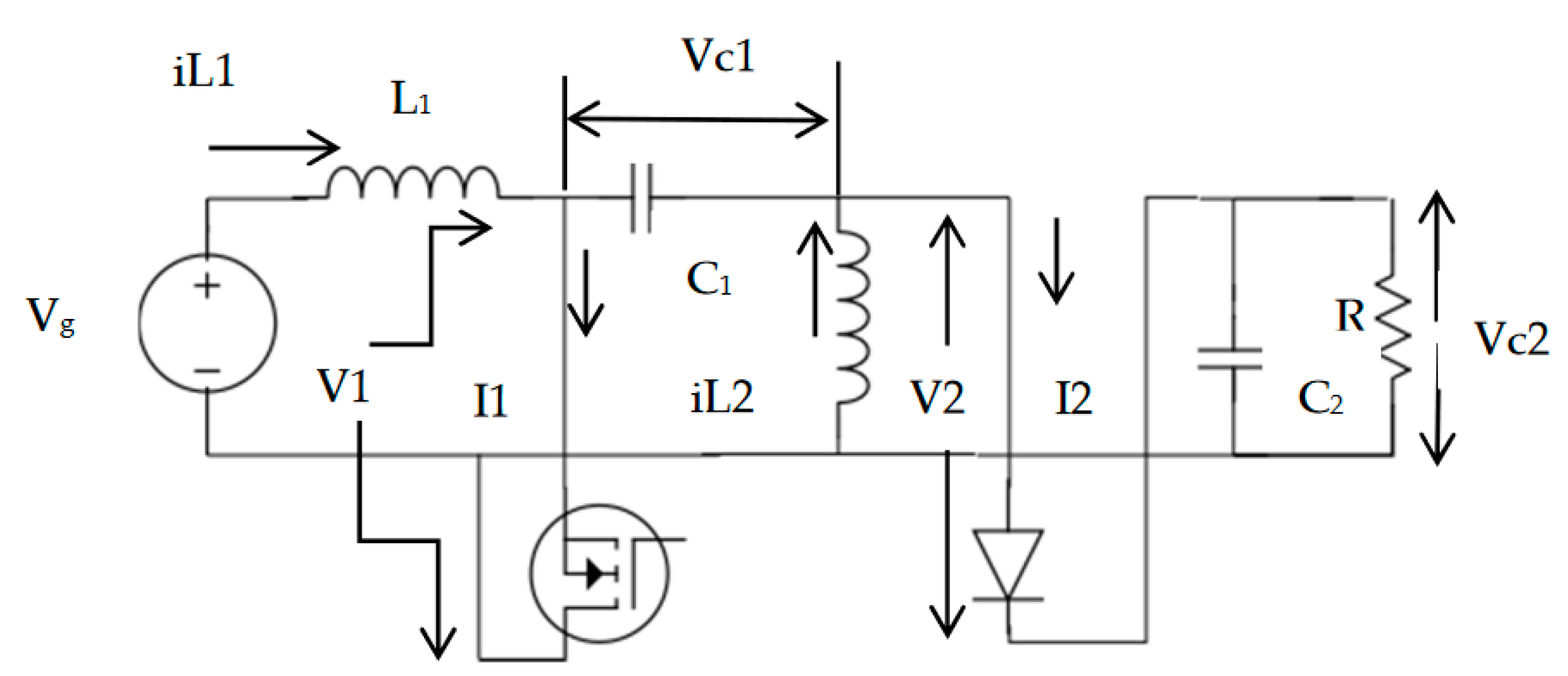

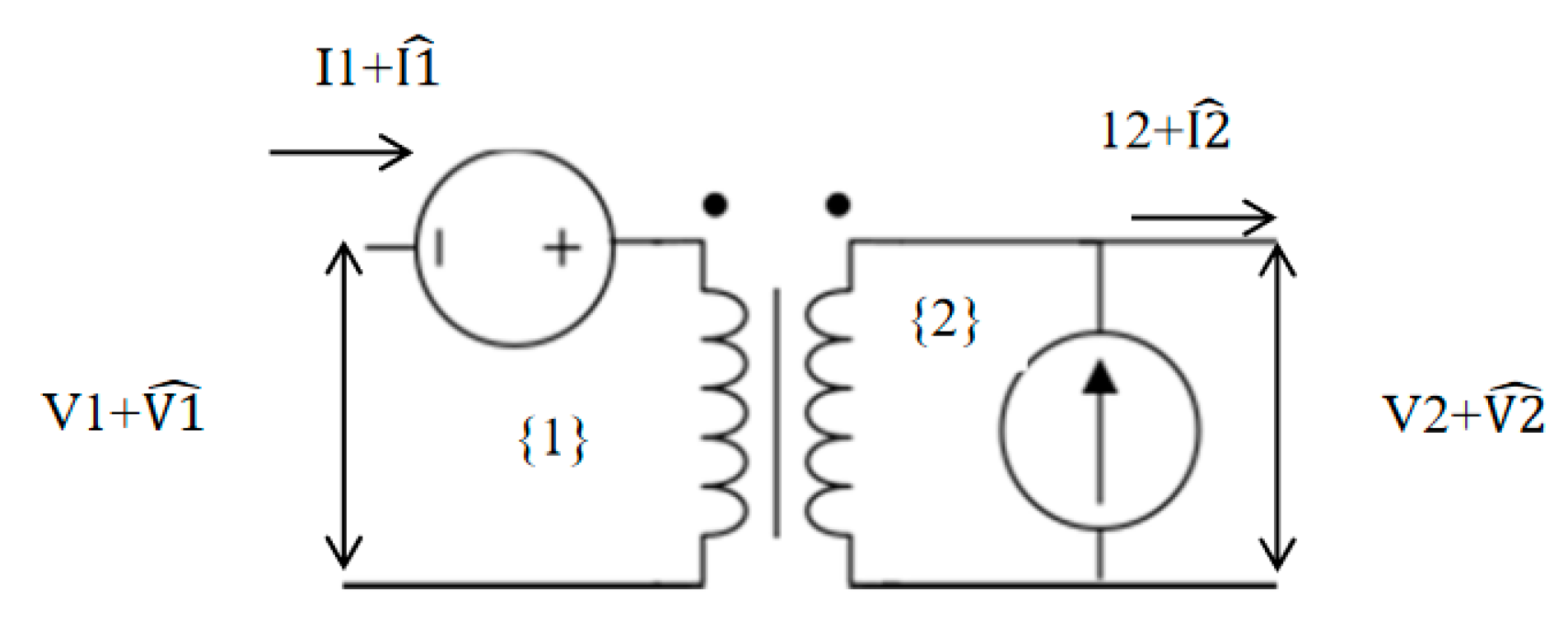

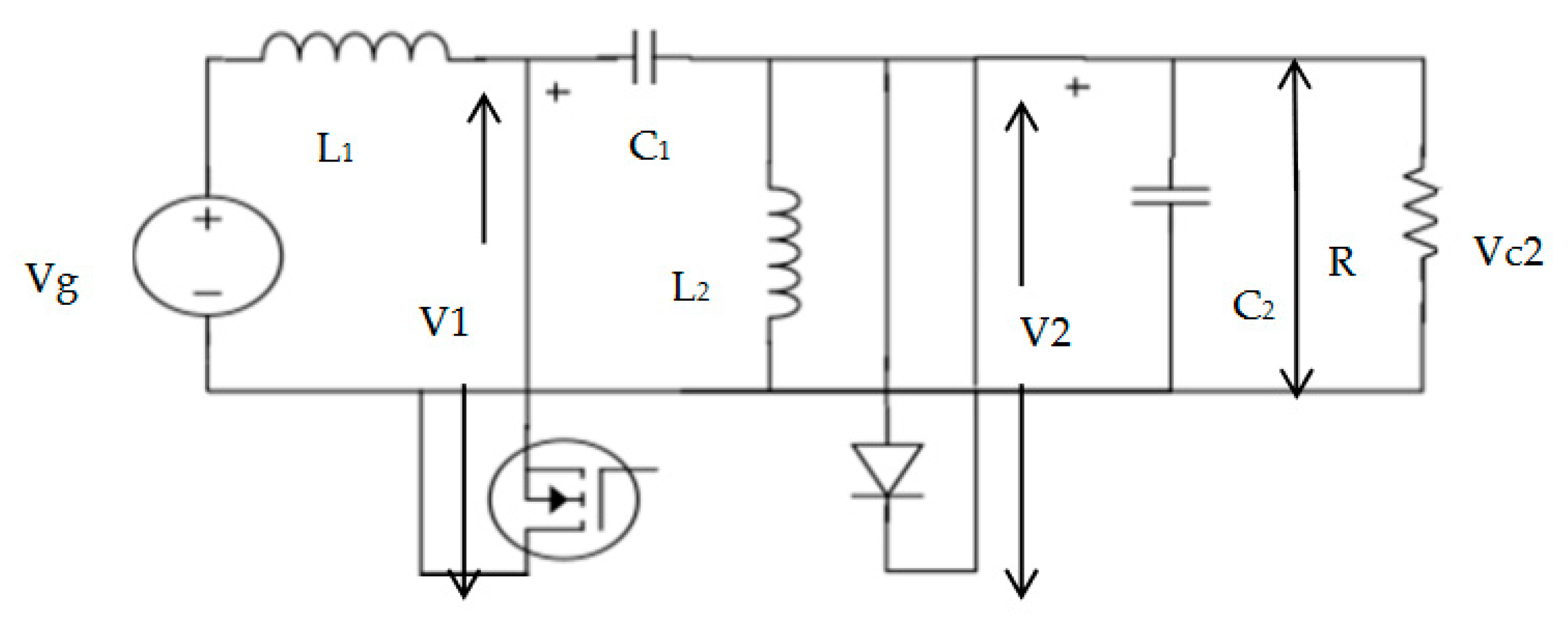

2. Circuit Averaging for an Ideal SEPIC

- Separate the switch network from the converter and define the ports.

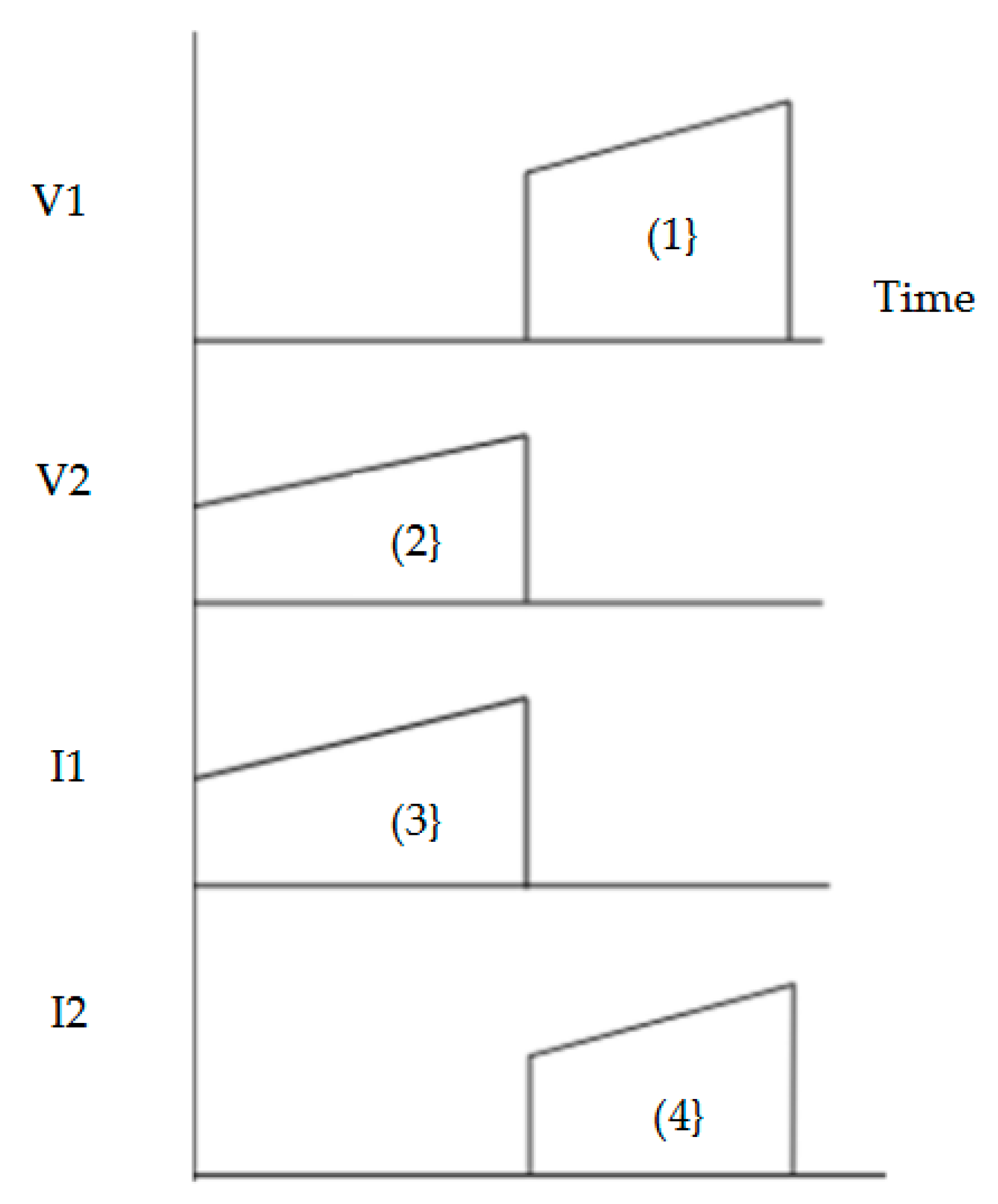

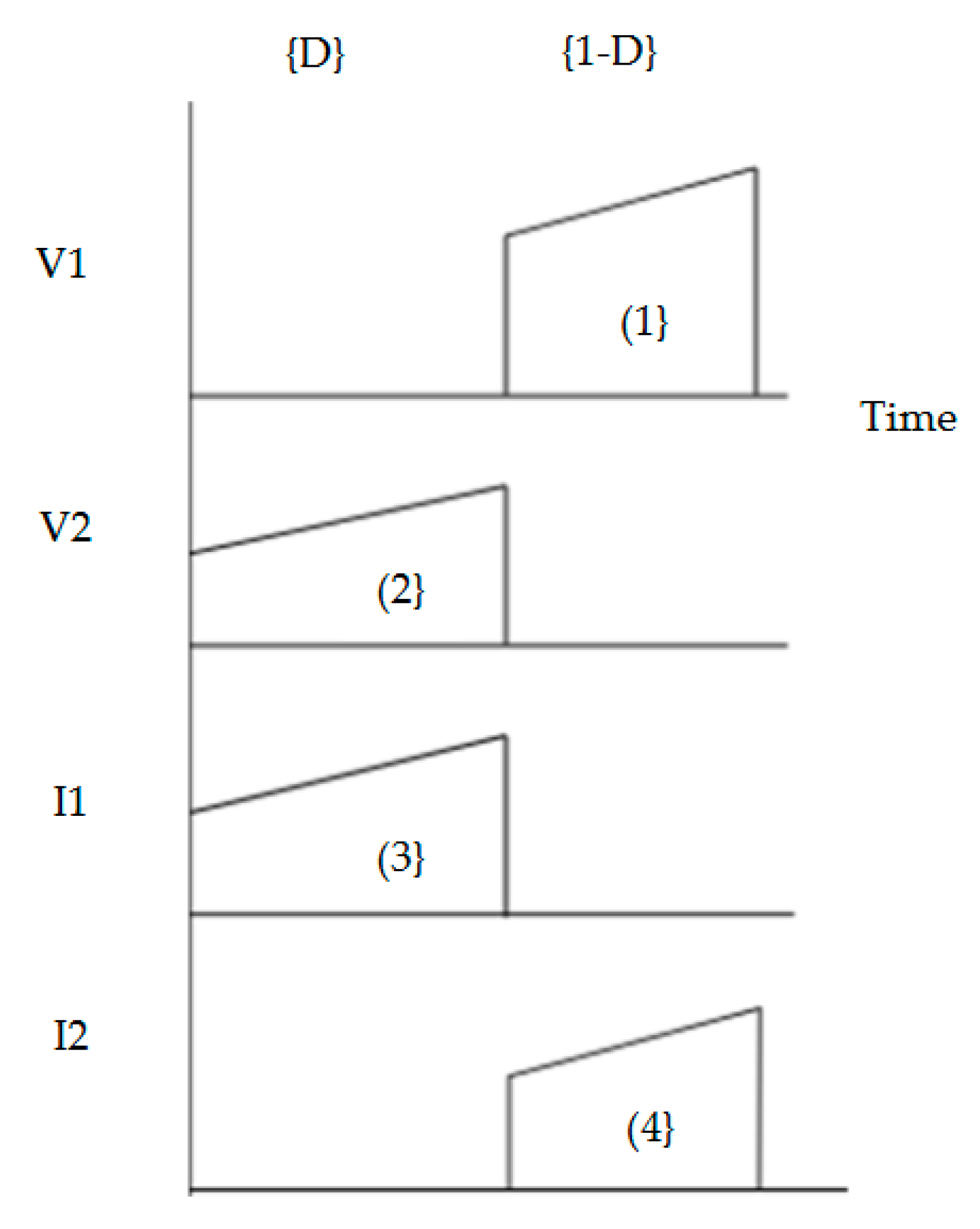

- Sketch the waveform of the switch current and voltage waveforms and average it.

- Simplify the equations and draw the equivalent switch network.

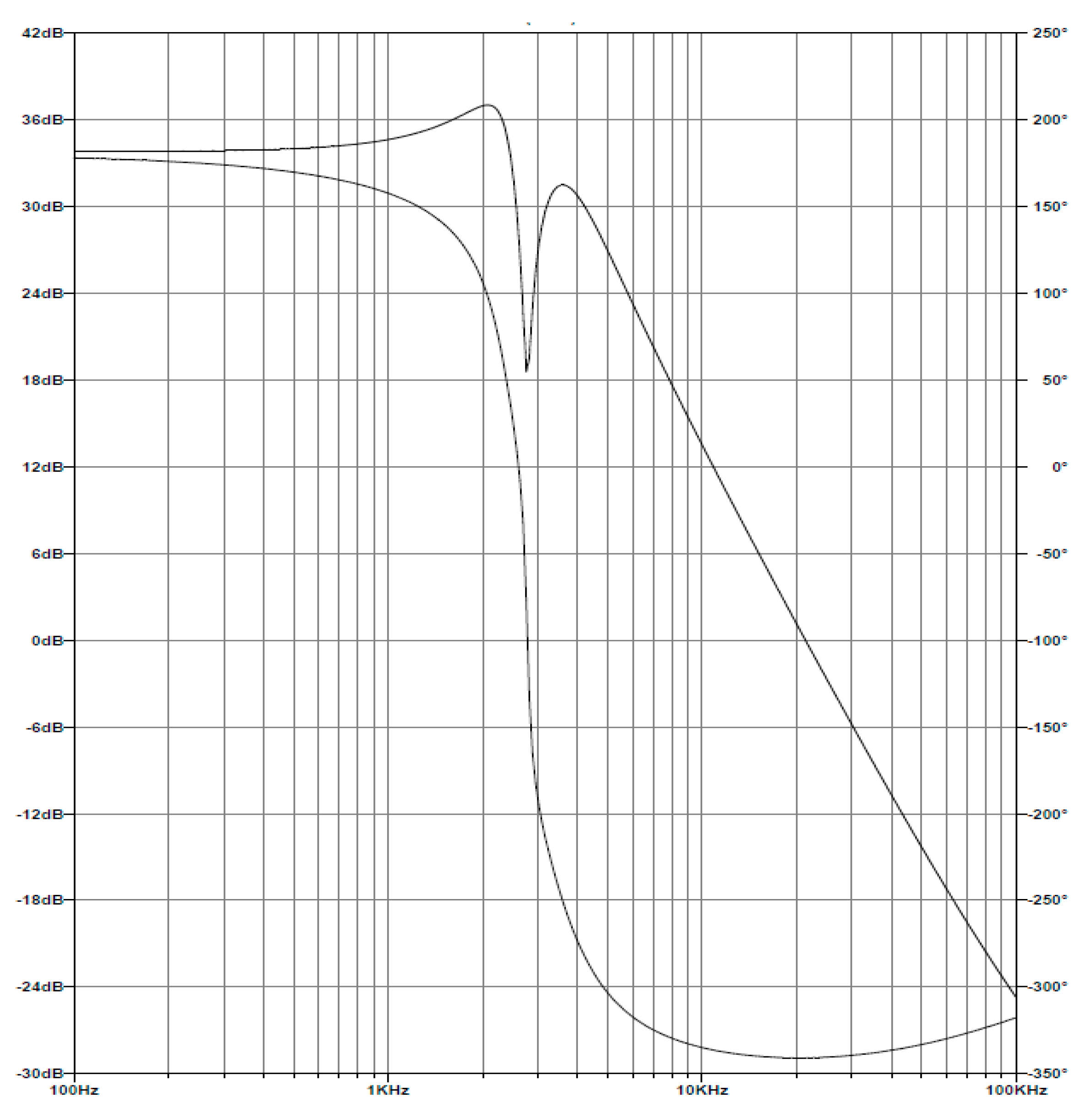

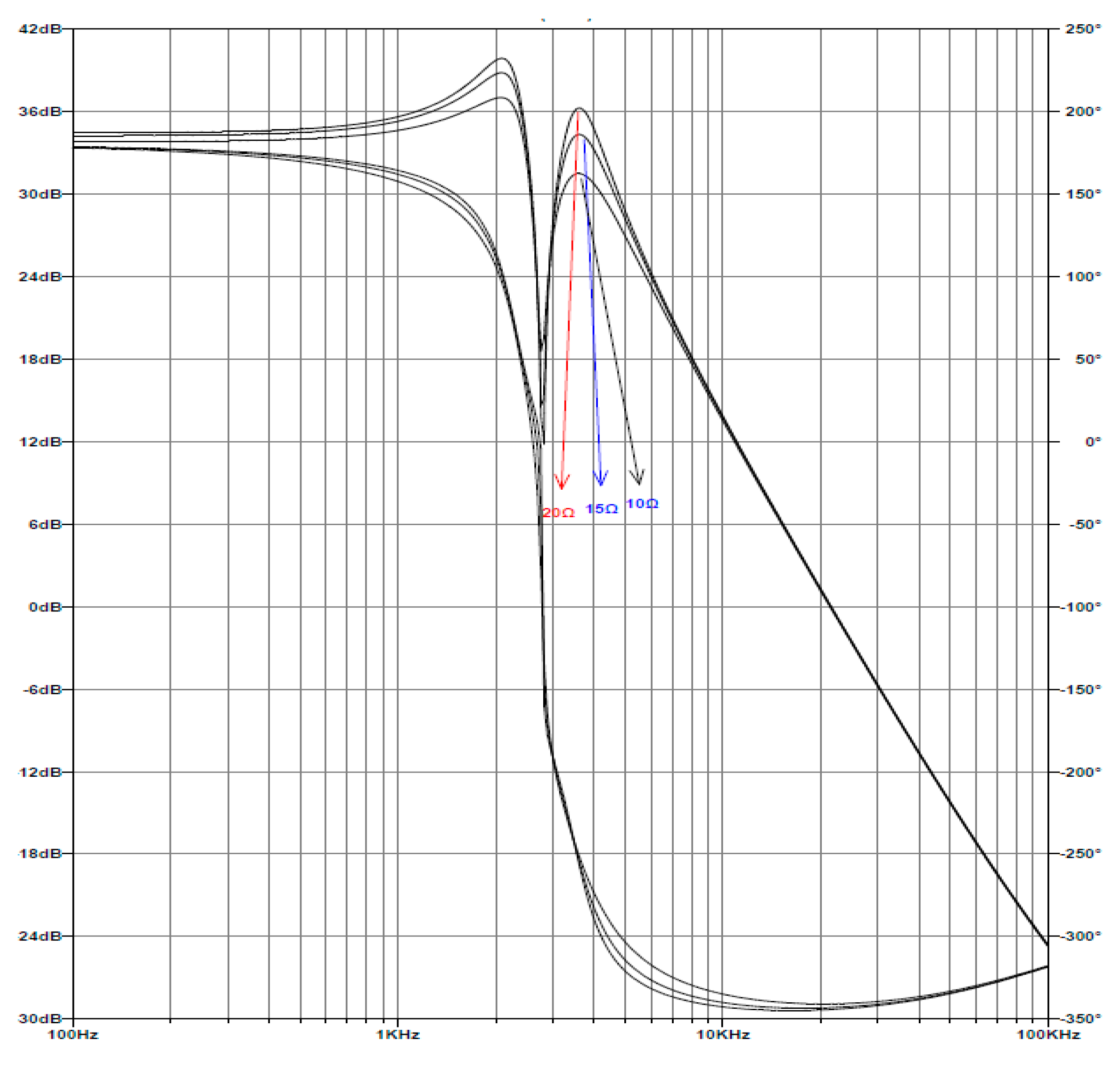

3. Small Signal Model

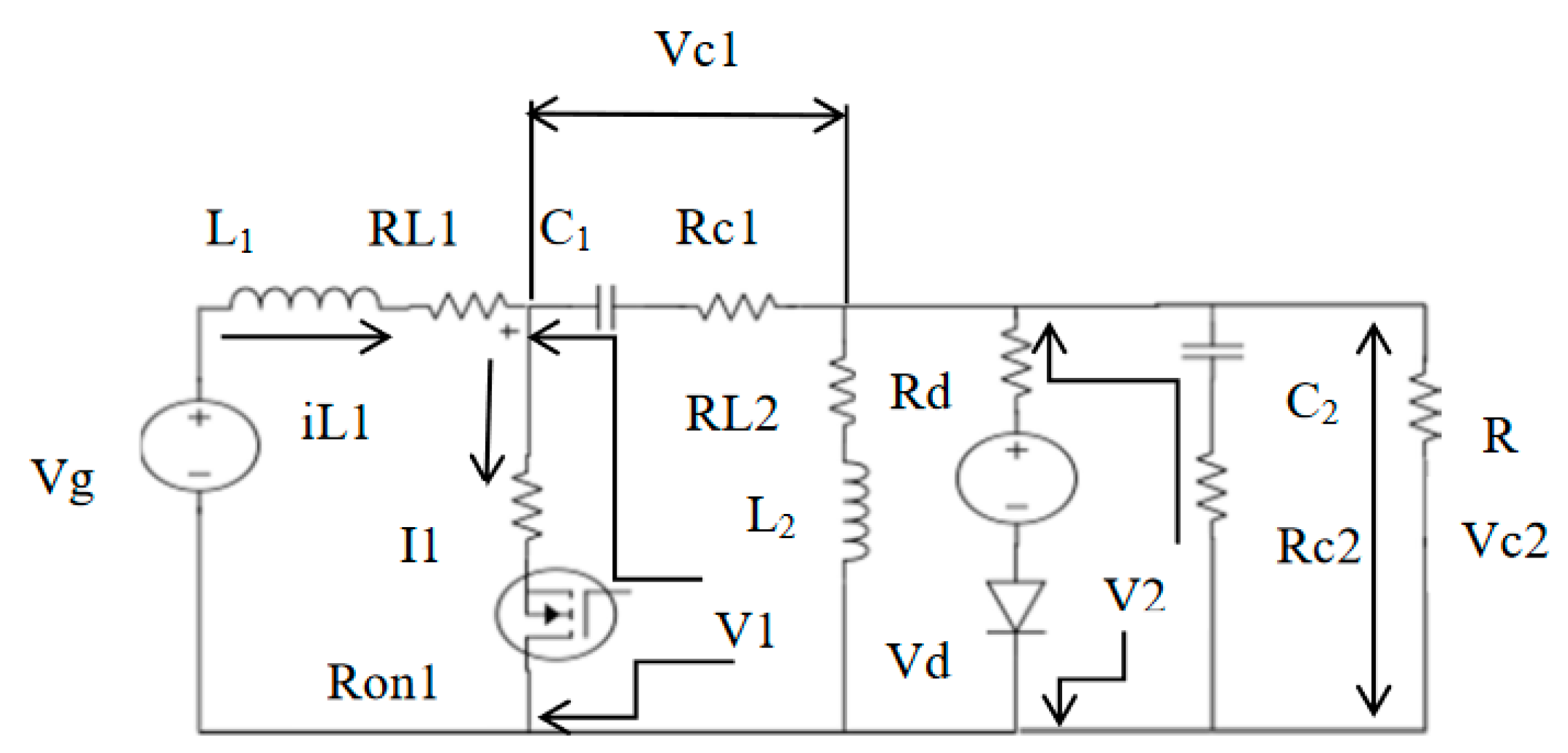

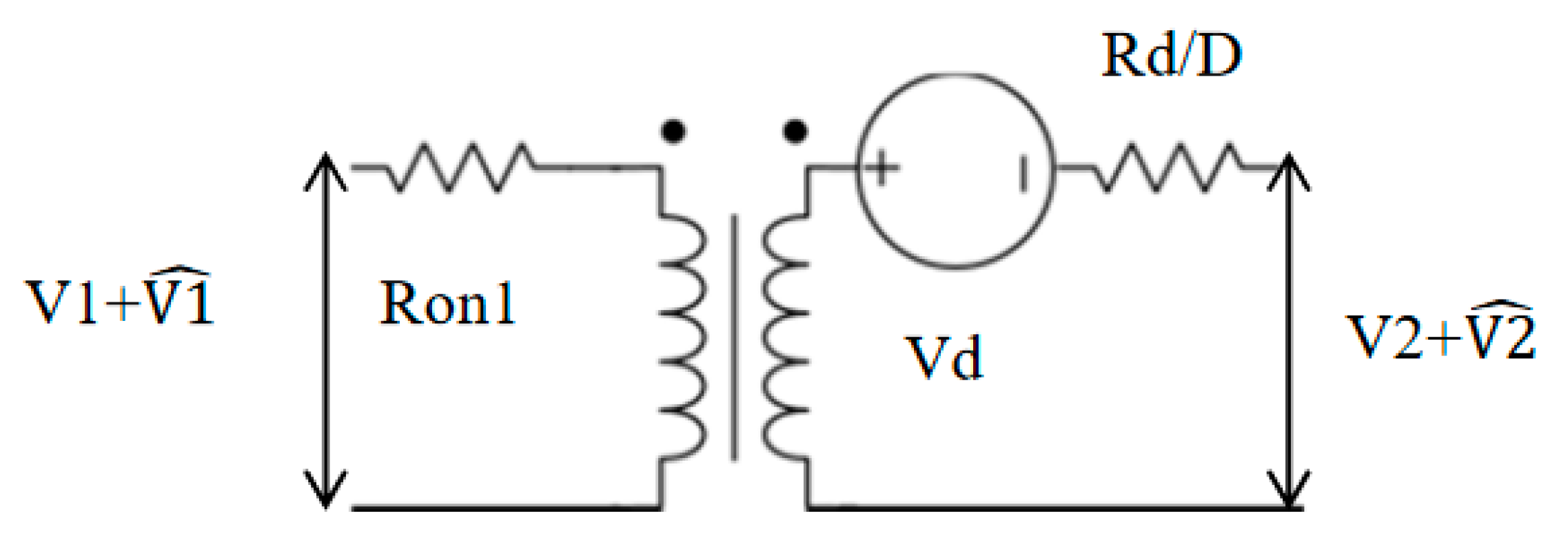

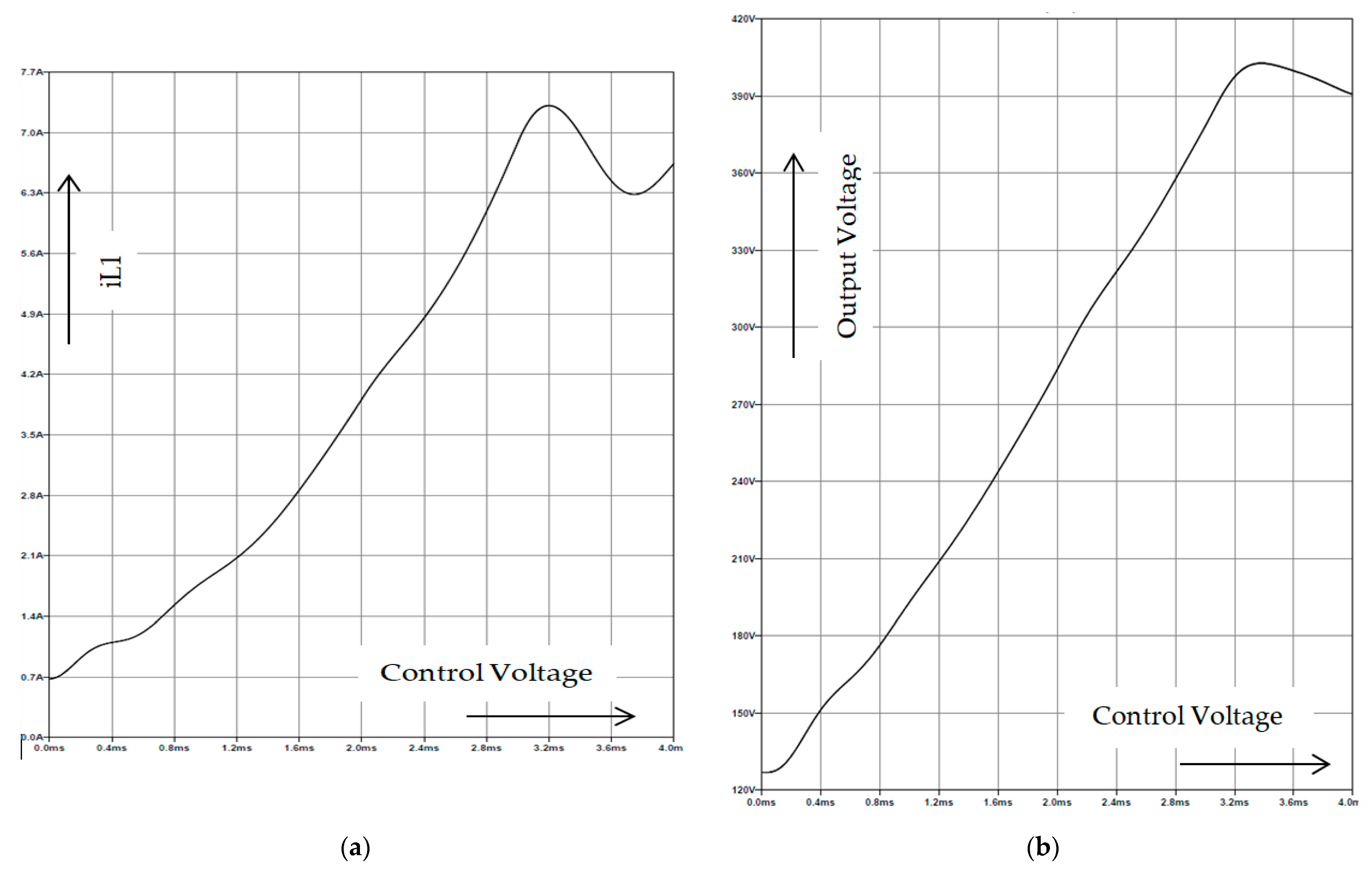

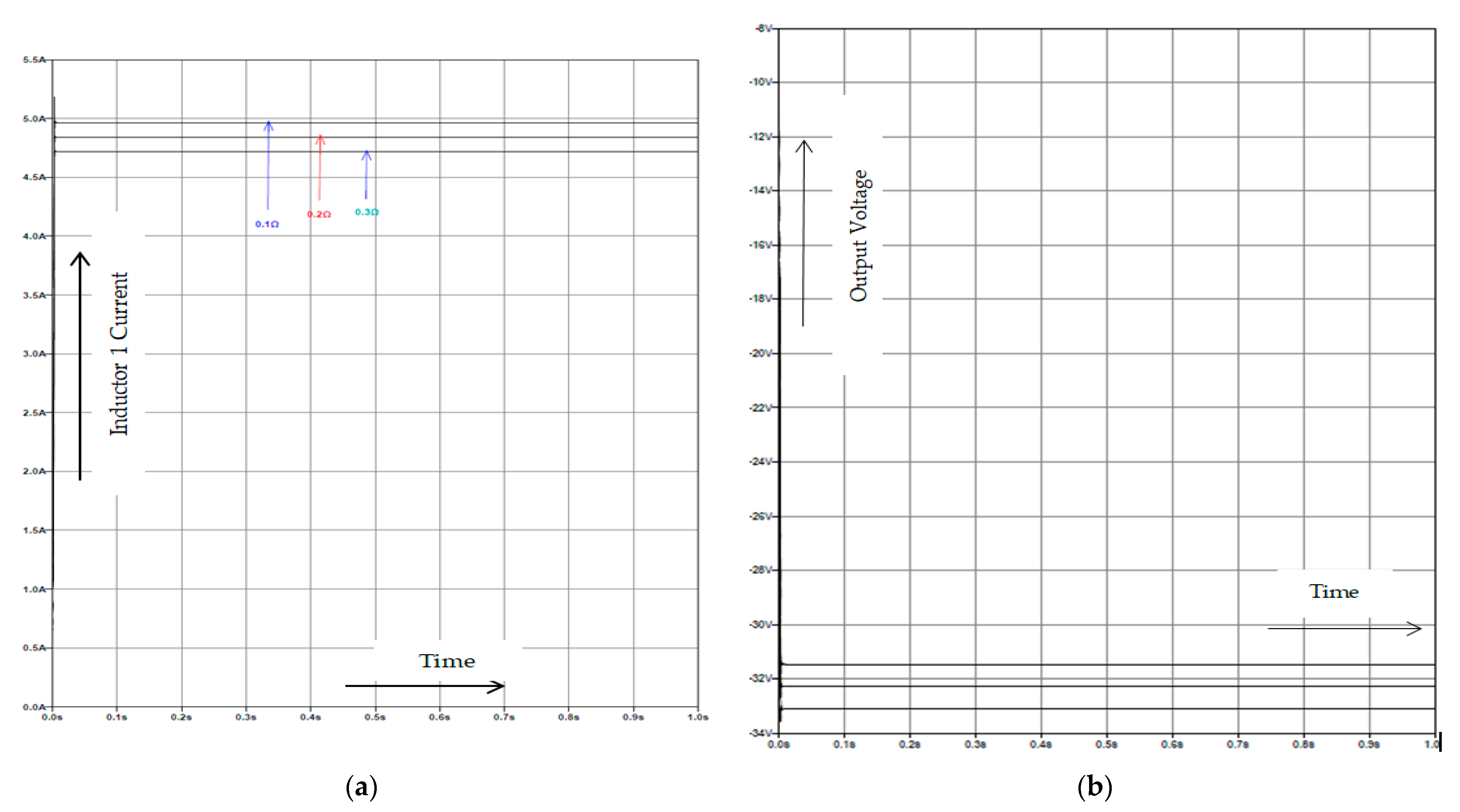

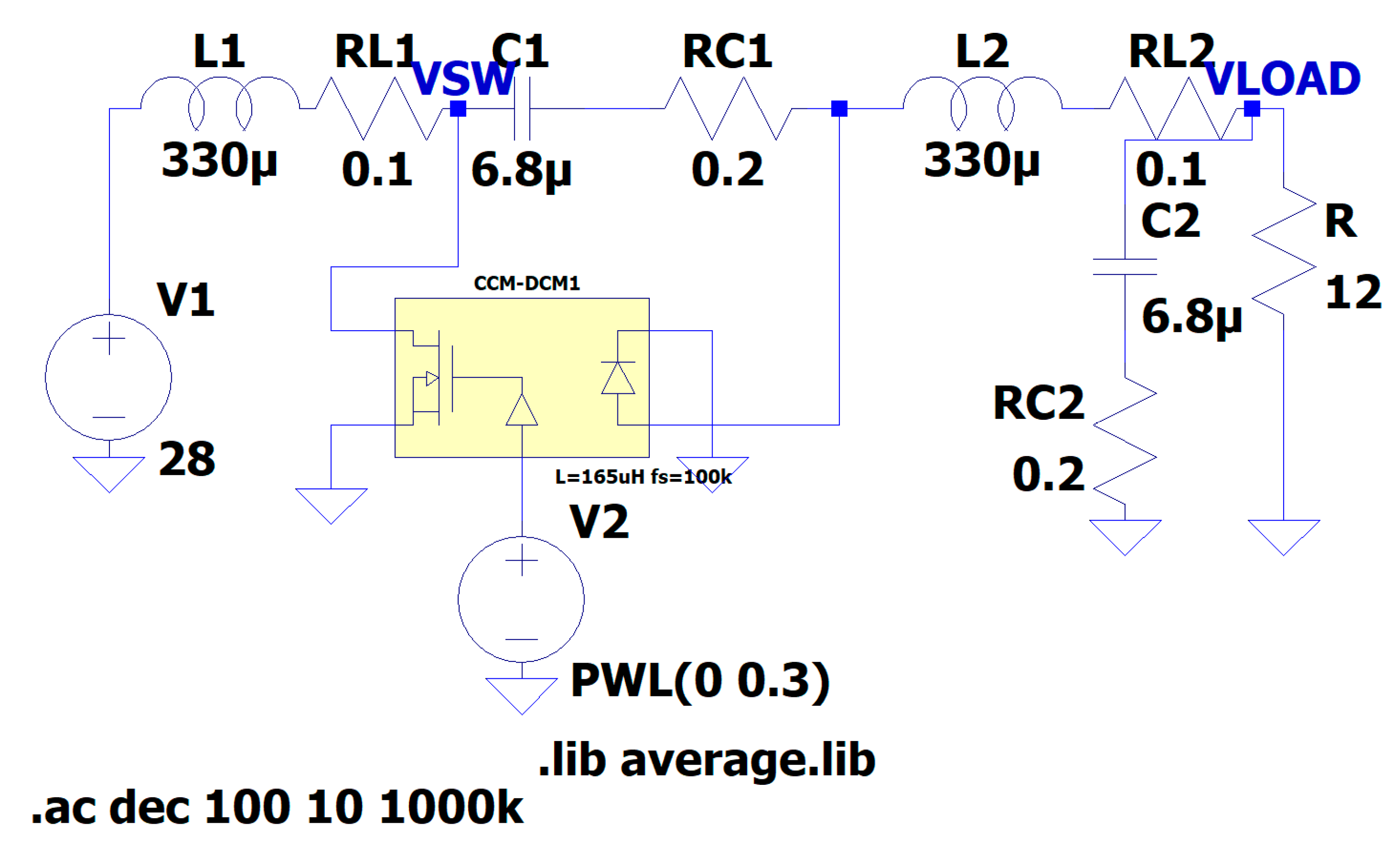

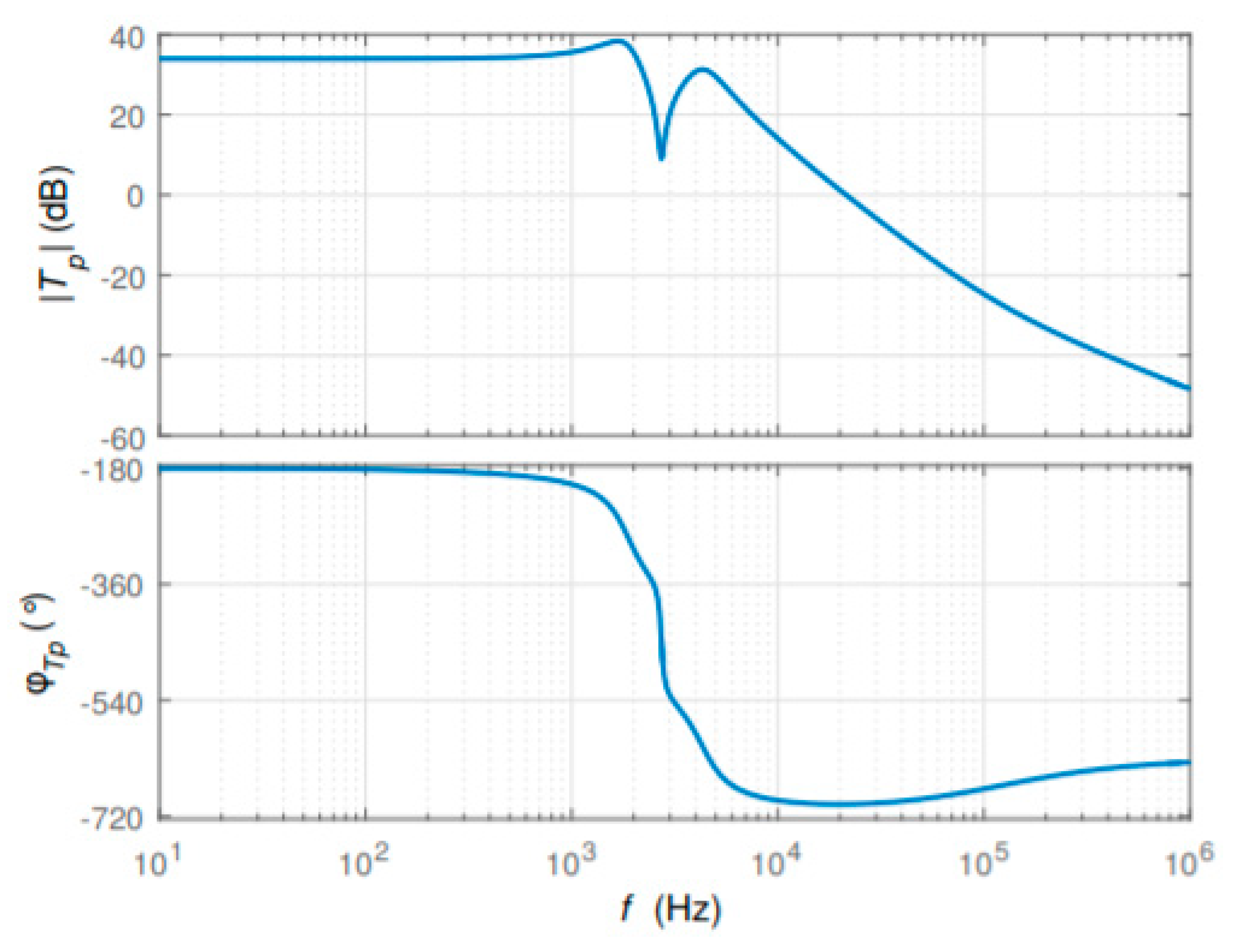

4. Circuit Averaging for a Non-Ideal SEPIC

5. Circuit Averaging for a Non-Ideal Cuk

6. Circuit Averaging for Non-Ideal Cuk Converter

7. Converter Specifications

8. Results

9. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Erickson, W.R.; Maksimovic, D. Fundamentals of Power Electronics; Springer Science & Business Media: Berlin/Heidelberg, Germany, 2007. [Google Scholar]

- Surya, S.; Patil, V. Cuk Converter as an Efficient Driver for LED. In Proceedings of the 2019 4th International Conference on Electrical, Electronics, Communication, Computer Technologies and Optimization Techniques (ICEECCOT), Mysuru, India, 13–14 December 2019. [Google Scholar]

- Surya, S.; Arjun, M.N. Effect of fast discharge of a battery on its core temperature. In Proceedings of the 2020 International Conference on Futuristic Technologies in Control Systems & Renewable Energy (ICFCR), Malappuram, India, 23–24 September 2020. [Google Scholar]

- Kathi, L.; Ayachit, A.; Saini, D.K.; Chadha, A.; Kazimierczuk, M.K. Open-loop small-signal modeling of Cuk DC-DC converter in CCM by circuit-averaging technique. In Proceedings of the 2018 IEEE Texas Power and Energy Conference (TPEC), College Station, TX, USA, 8–9 February 2018. [Google Scholar]

- Lee, C.M.; Lai, Y.S. Averaged switch modeling of dc/dc converters using new switch network. In Proceedings of the 2007 7th International Conference on Power Electronics and Drive Systems, Bangkok, Thailand, 27–30 November 2007. [Google Scholar]

- Middlebrook, R.D.; Cuk, S. A General Unified Approach to Modeling Switching Converter Stages. In Proceedings of the 1976 IEEE Power Electronics Specialists Conference, Cleveland, OH, USA, 8–10 June 1976; pp. 18–34. [Google Scholar]

- Niculescu, E.; Iancu, E.P. Modeling and analysis of the DC/DC fourth-order PWM converters. In Proceedings of the COMPEL 2000, 7th Workshop on Computers in Power Electronics, Proceedings (Cat. No. 00TH8535), Blacksburg, VA, USA, 16–18 July 2000. [Google Scholar]

- Van Dijk, E.; Spruijt, J.N.; O’sullivan, D.M.; Klaassens, J.B. PWM-switch modeling of DC-DC converters. IEEE Trans. Power Electron. 1995, 10, 659–665. [Google Scholar] [CrossRef]

- Sumukh, S.; Channegowda, J.; Naraharisetti, K. Generalized Circuit Averaging Technique for Two Switch DC-DC Converters. arXiv 2020, arXiv:2012.12724. [Google Scholar]

- Ayachit, A.; Kazimierczuk, M.K. Averaged small-signal model of PWM DC-DC converters in CCM including switching power loss. IEEE Trans. Circuits Syst. II Express Briefs 2018, 66, 262–266. [Google Scholar] [CrossRef]

- Bertoldi, B.; Junior, M.M.B.; Dall’Asta, M.S.; Mocellini, M.P.; Roig, G.M.D.; Kirsten, A.L.; Heldwein, M.L. A Non-Ideal SEPIC DCM Modeling for LED Lighting Applications. In Proceedings of the 2018 IEEE 4th Southern Power Electronics Conference (SPEC), Singapore, 10–13 December 2018. [Google Scholar]

- Simonetti, D.S.L.; Sebastian, J.; Uceda, J. The discontinuous conduction mode Sepic and Cuk power factor preregulators: Analysis and design. IEEE Trans. Ind. Electron. 1997, 44, 630–637. [Google Scholar] [CrossRef]

- Singer, S.; Erickson, R.W. Canonical modeling of power processing circuits based on the POPI concept. IEEE Trans. Power Electron. 1992, 7, 37–43. [Google Scholar] [CrossRef]

| SL.NO | Specifications | Value |

|---|---|---|

| 1 | Input Voltage, Vg | 28 V |

| 2 | Output Voltage, V0 | 10 V |

| 3 | Output Current, I0 | 1 A |

| 4 | Inductors, L1 and L2 | 330 µH |

| 5 | Inductor ESR, RL1 and RL2 | 0.1 Ω |

| 6 | MOSFET Resistance, Ron1 | 31 mΩ |

| 7 | Duty Cycle, D | 0.3 |

| 8 | Capacitors, C1 and C2 | 6.8 µH |

| 9 | Capacitor ESR, Resr | 0.2 Ω |

| 10 | Switching Frequency, fs | 100 kHz |

| 11 | Diode Drop, Vd | 0.8 V |

| 12 | Diode Forward Resistance | 0.8 Ω |

| SL.NO | Specifications | Value |

|---|---|---|

| 1 | Input Voltage, Vg | 300 V |

| 2 | Output Voltage, V0 | 400 V |

| 3 | Output Current, I0 | 5 A |

| 4 | Inductors, L1 and L2 | 2.57 mH & 1.71 mH |

| 5 | Inductor ESR, RL1 and RL2 | 130 mΩ & 110 mΩ |

| 6 | MOSFET Resistance, Ron1 | 321 mΩ |

| 7 | Duty Cycle, D | 0.571 |

| 8 | Capacitors, C1 and C2 | 4.7 µF & 3.57 µF |

| 9 | Capacitor ESR, Resr | 270 mΩ & 350 mΩ |

| 10 | Switching Frequency, fs | 100 kHz |

| 11 | Diode Drop, Vd | 0.62 V |

| 12 | Diode Forward Resistance | 80 mΩ |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Surya, S.; Williamson, S. Generalized Circuit Averaging Technique for Two-Switch PWM DC-DC Converters in CCM. Electronics 2021, 10, 392. https://doi.org/10.3390/electronics10040392

Surya S, Williamson S. Generalized Circuit Averaging Technique for Two-Switch PWM DC-DC Converters in CCM. Electronics. 2021; 10(4):392. https://doi.org/10.3390/electronics10040392

Chicago/Turabian StyleSurya, Sumukh, and Sheldon Williamson. 2021. "Generalized Circuit Averaging Technique for Two-Switch PWM DC-DC Converters in CCM" Electronics 10, no. 4: 392. https://doi.org/10.3390/electronics10040392

APA StyleSurya, S., & Williamson, S. (2021). Generalized Circuit Averaging Technique for Two-Switch PWM DC-DC Converters in CCM. Electronics, 10(4), 392. https://doi.org/10.3390/electronics10040392