Linear Characterization and Modeling of GaN-on-Si HEMT Technologies with 100 nm and 60 nm Gate Lengths

Abstract

1. Introduction

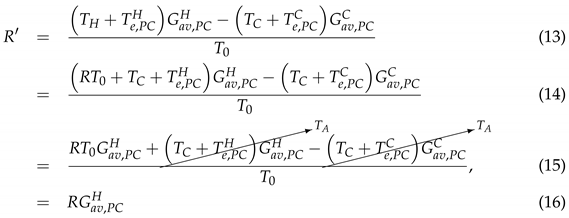

2. Technology

3. Results

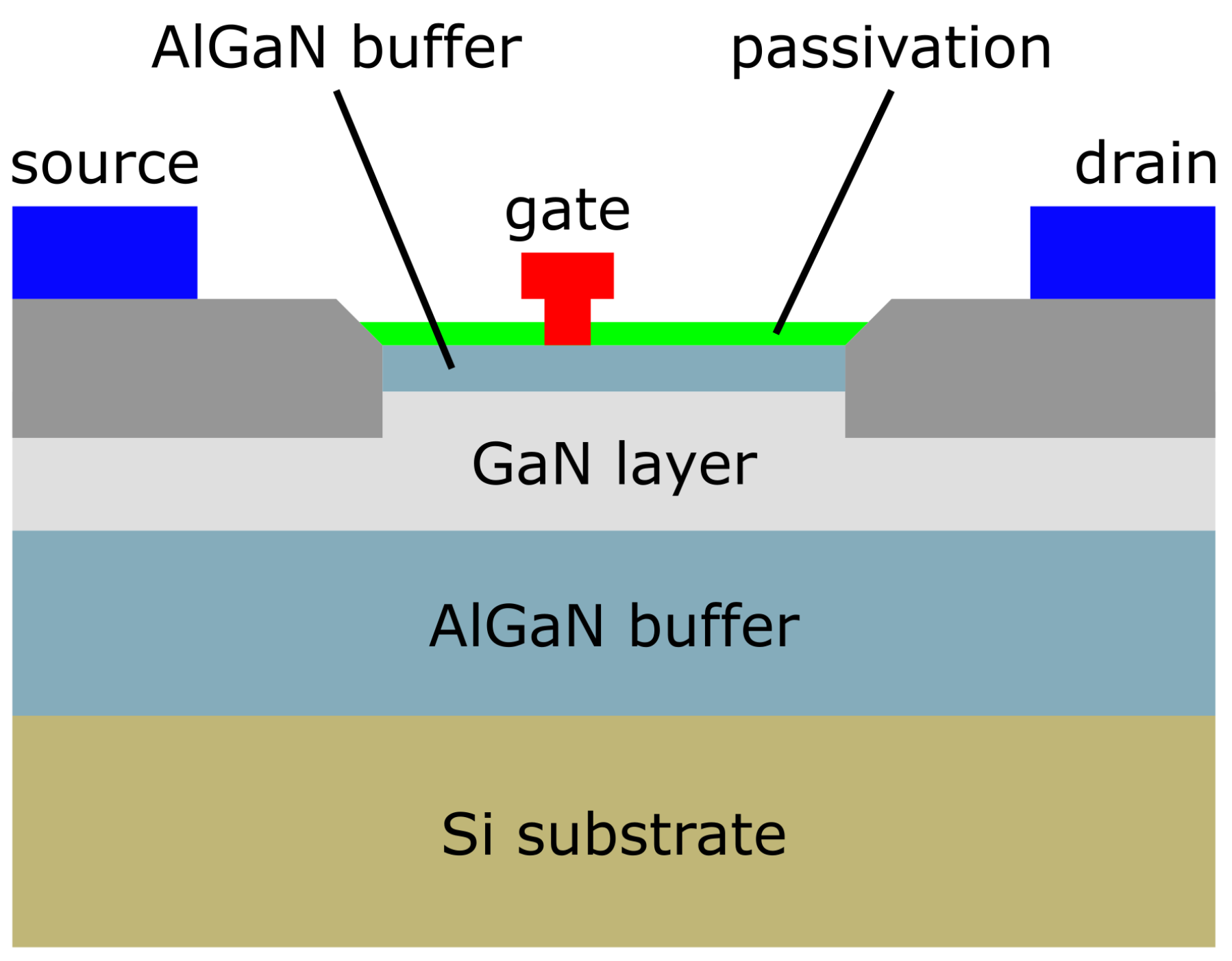

3.1. Device Screening

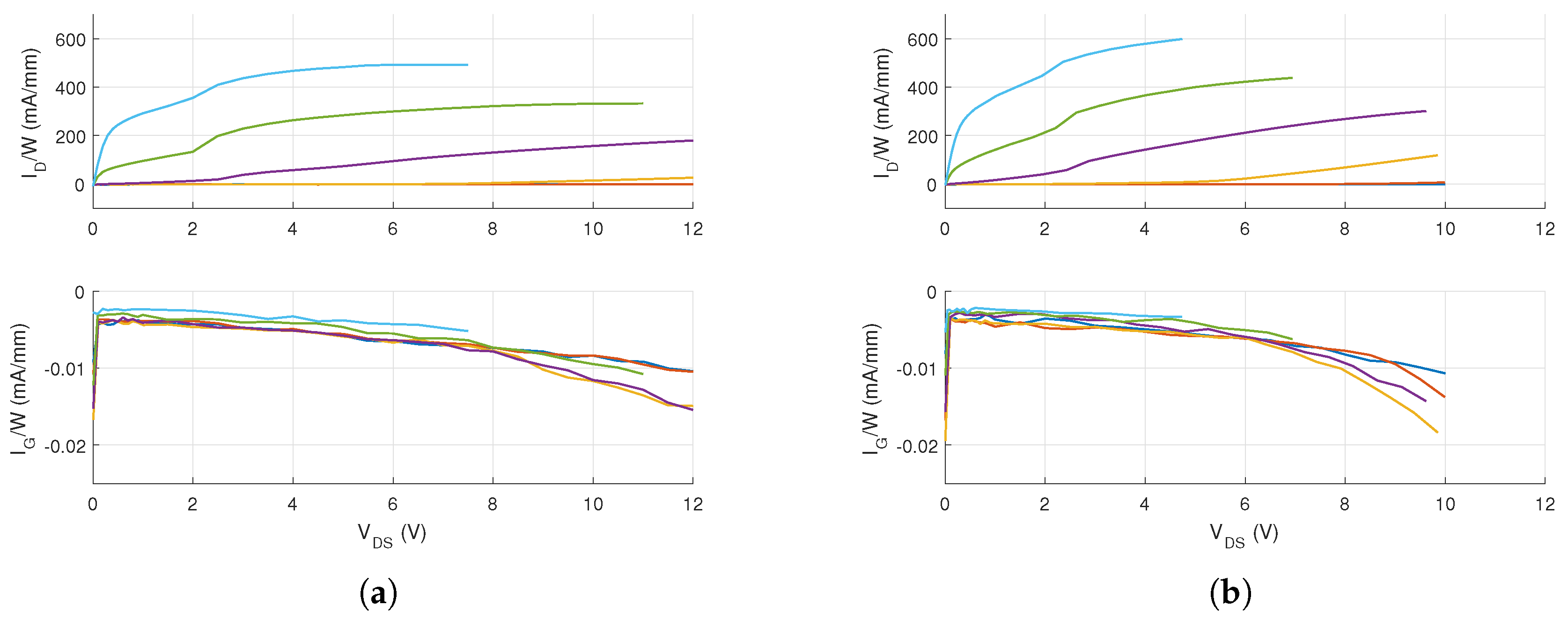

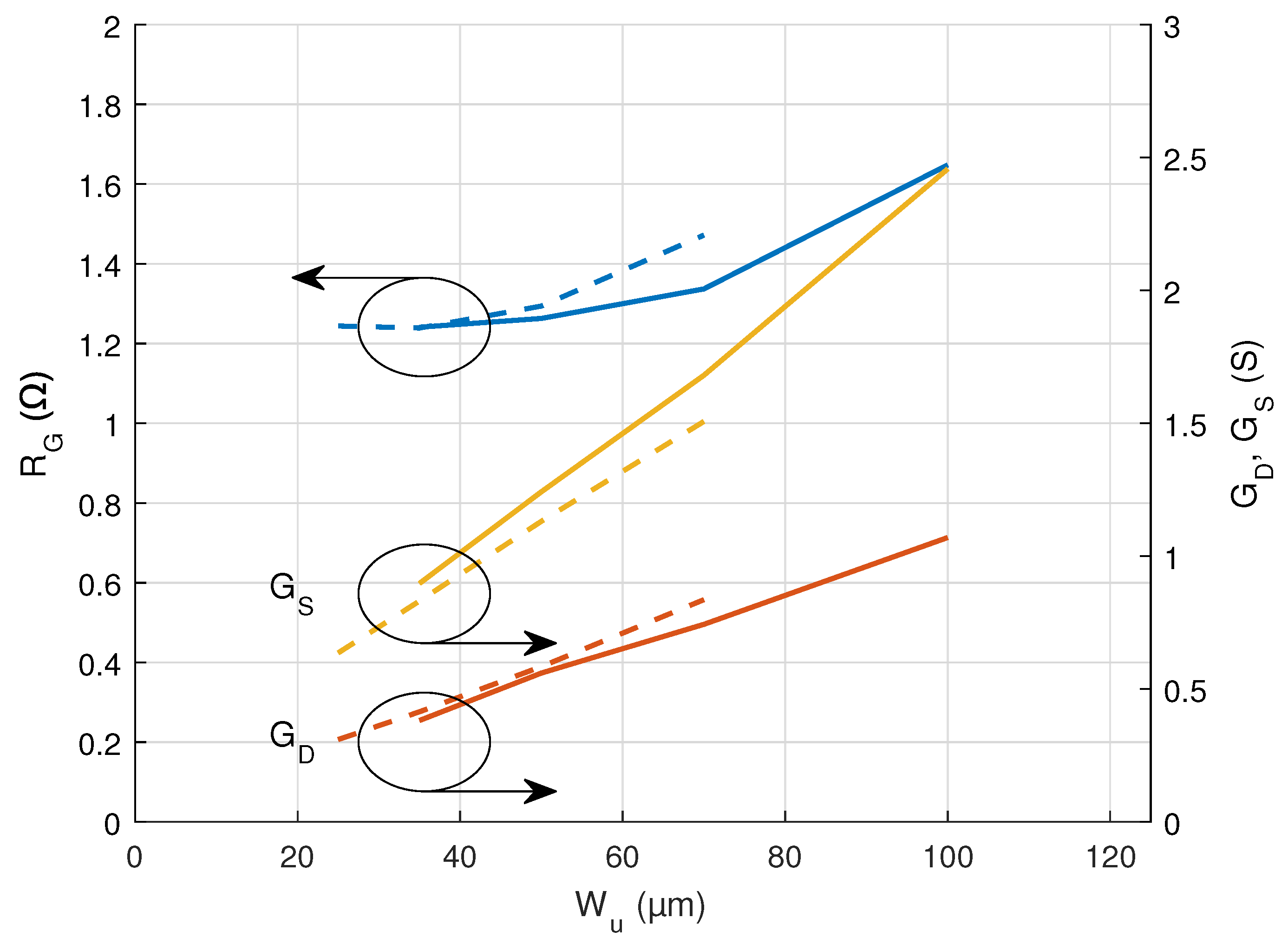

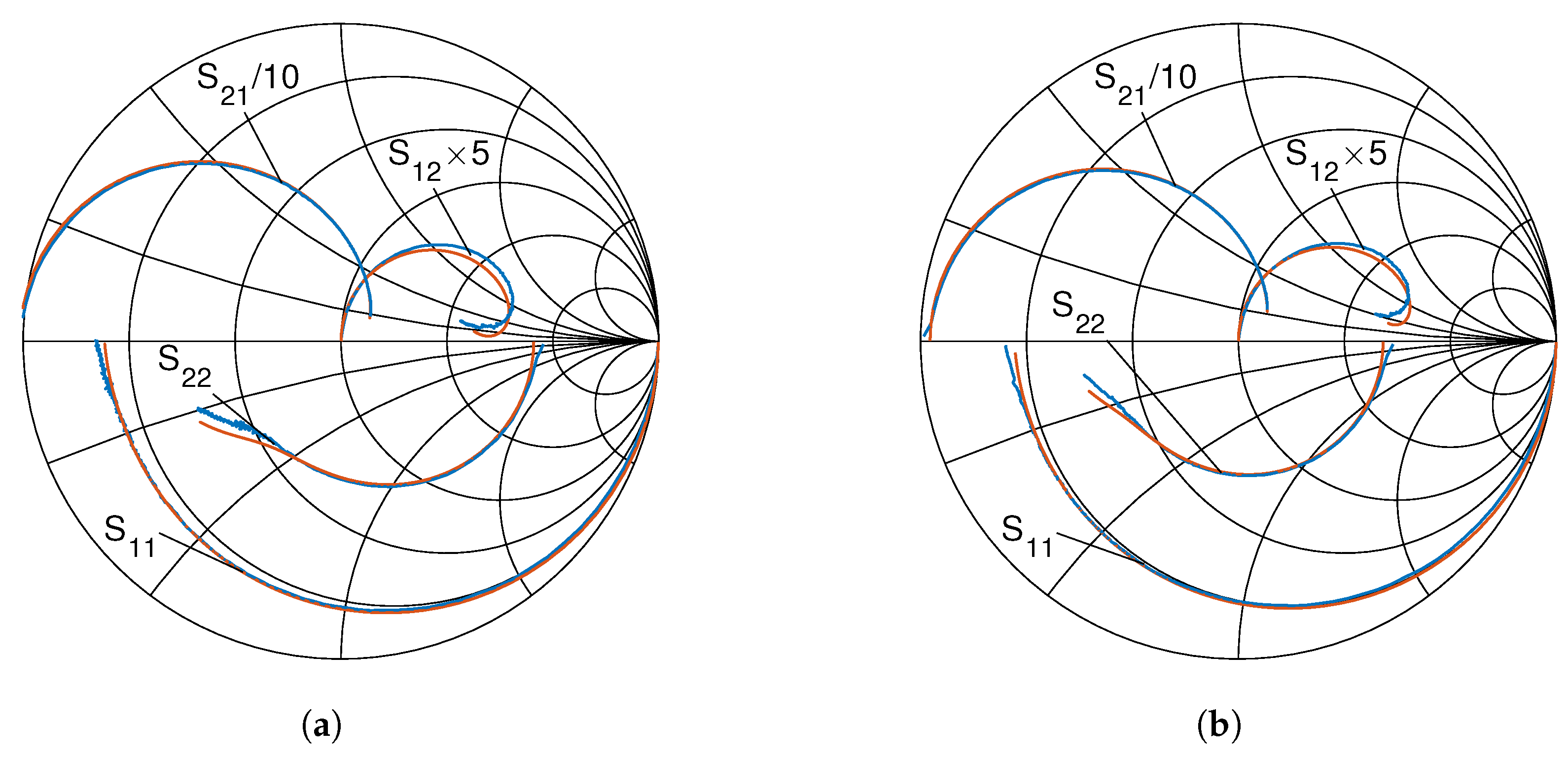

3.2. Small-Signal Characterization and Modeling

- cold-FET measurements: V, swept from below threshold to mild direct current;

- hot-FET measurements over the – plane (same for multiple geometries);

- hot-FET measurements over the – plane.

- convert calibrated S-matrix to Y-matrix and subtract , and ;

- convert resulting Y-matrix to Z-matrix and subtract , , , , and ;

- convert resulting Z-matrix to Y-matrix and identify the intrinsic elements.

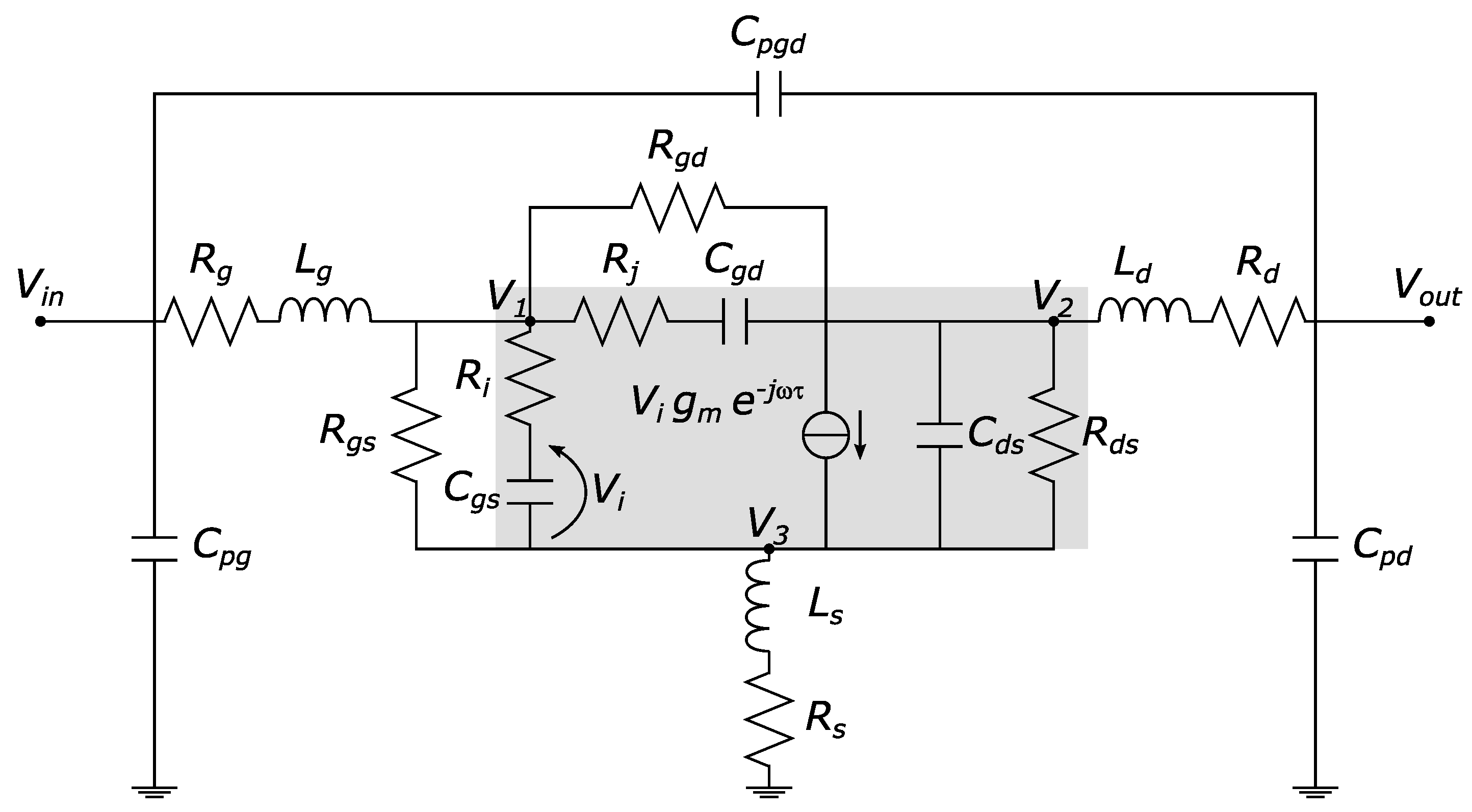

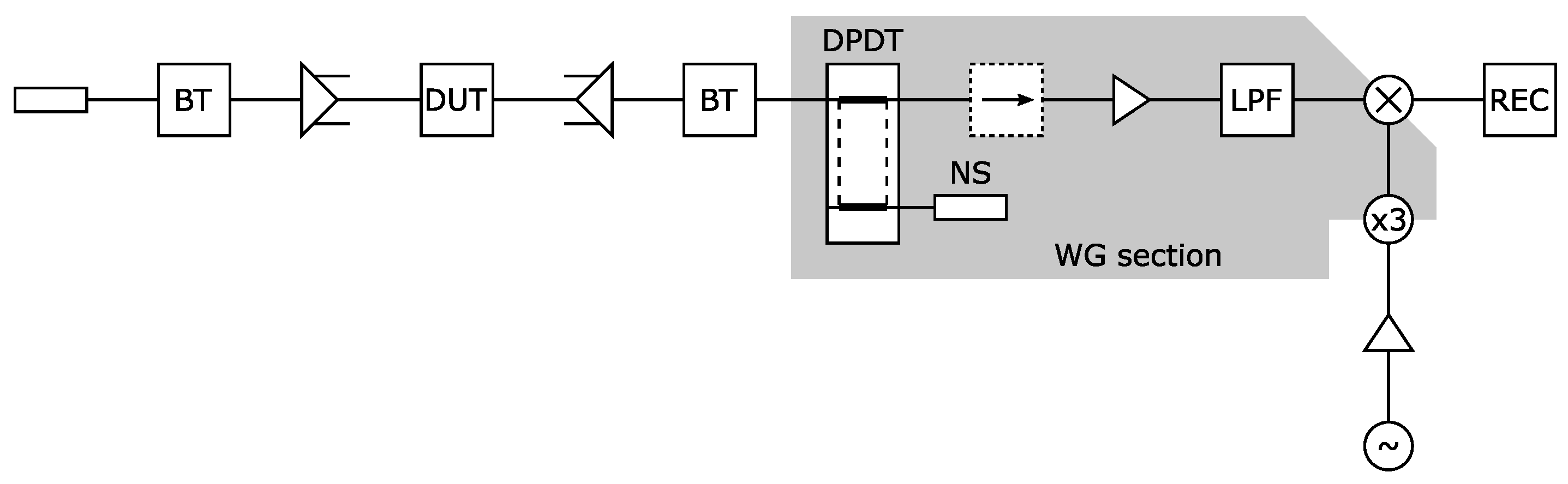

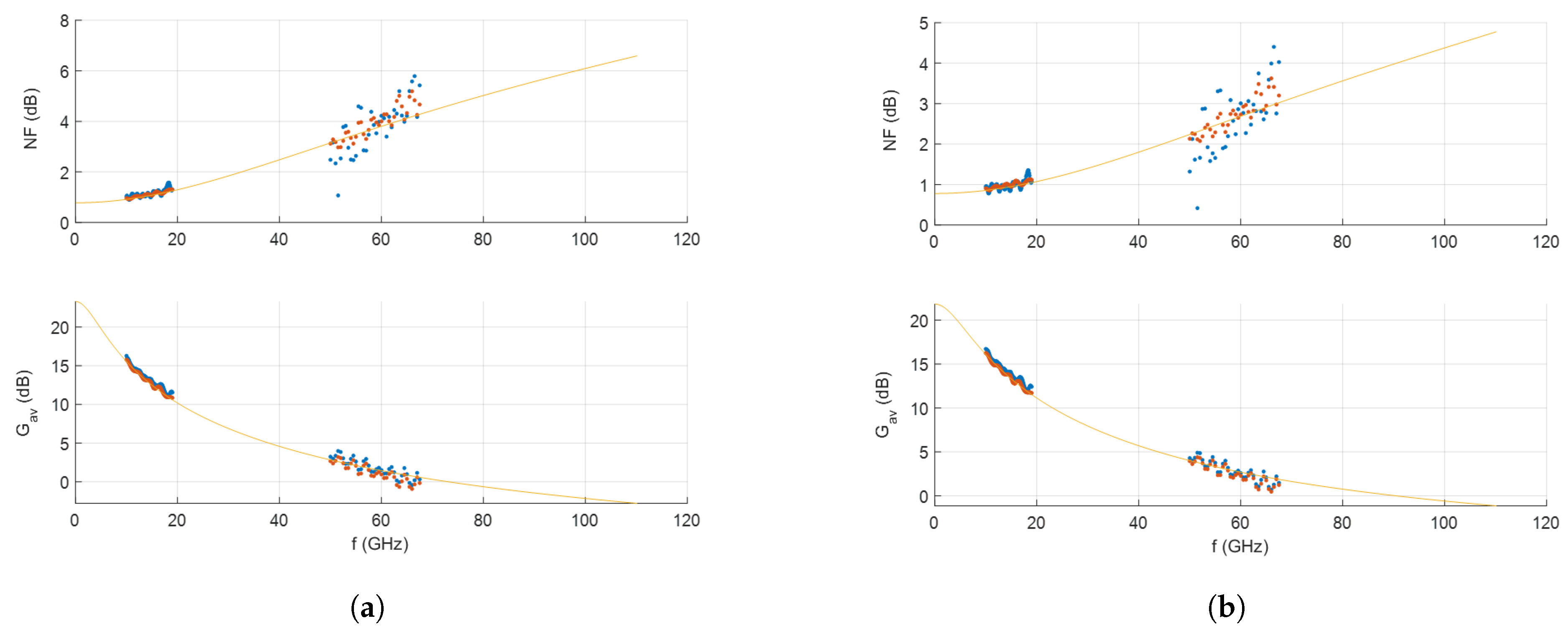

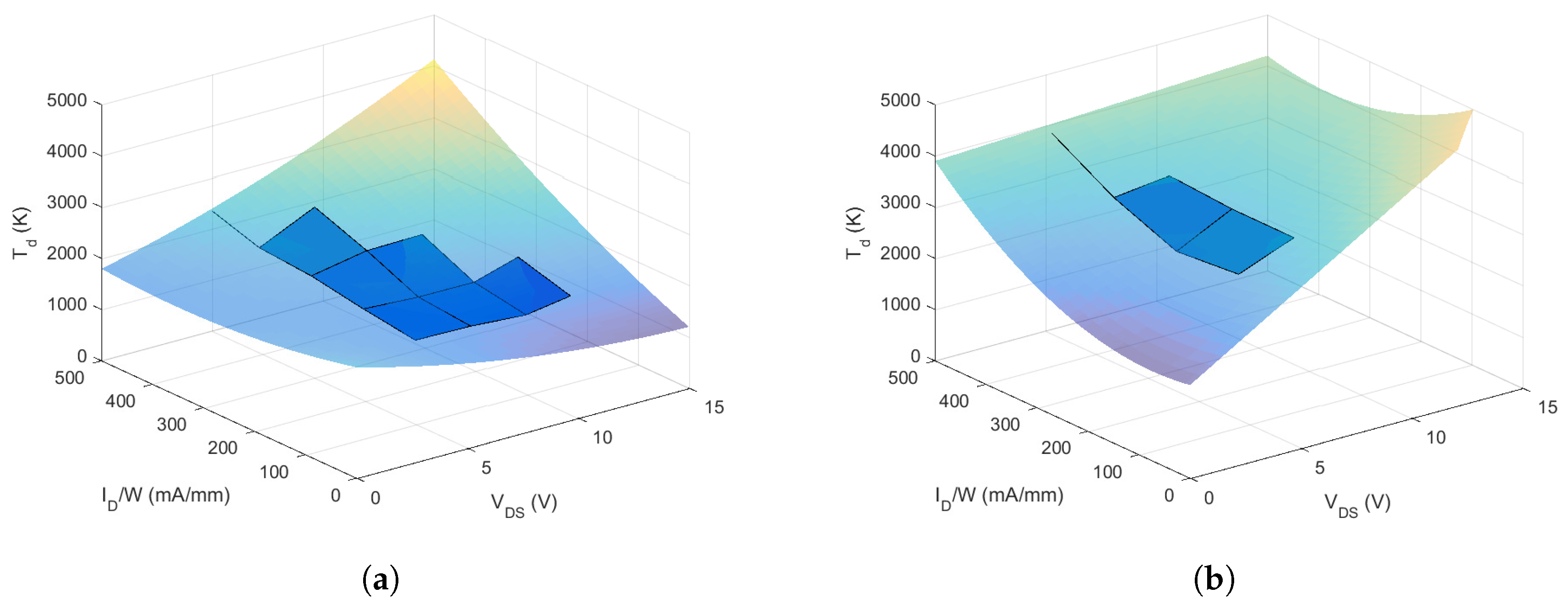

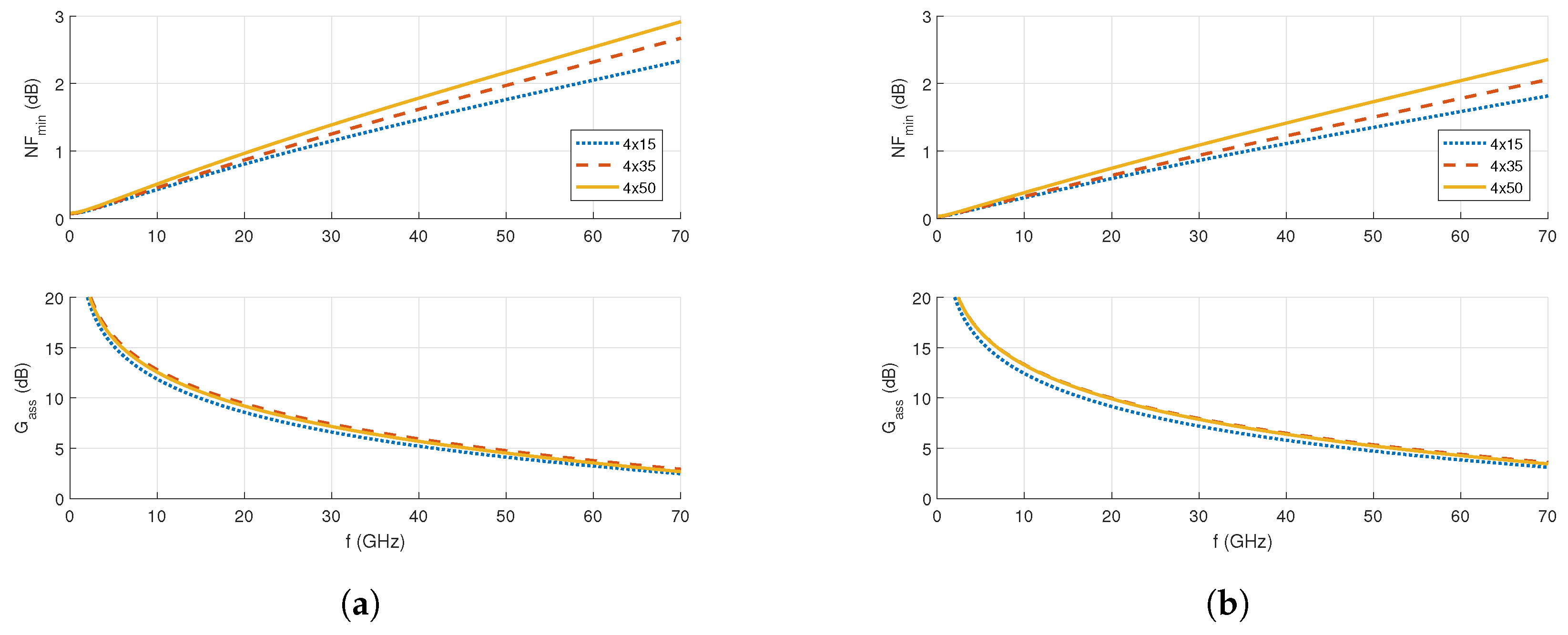

3.3. Noise Characterization and Modeling

- an ELVA-1 ISSN-15 V-band noise source;

- a SAGE Millimeter SFB-15-E2 V-band balanced mixer with external bias;

- a SAGE Millimeter SWF-75379340-15-L1 V-band waveguide low-pass filter;

- a SAGE Millimeter SWJ-15-TS V-band motorized waveguide switch;

- a Low Noise Factory LNF-LNR45_77WA LNA;

- a VDI WR15x3 frequency tripler.

- it allows a frequent calibration of the receiver while requiring only one solid-state noise source;

- it simplifies the characterization of the input chain, which has to be known merely as a termination;

- prospectively, it allows a simpler implementation of the source-pull technique.

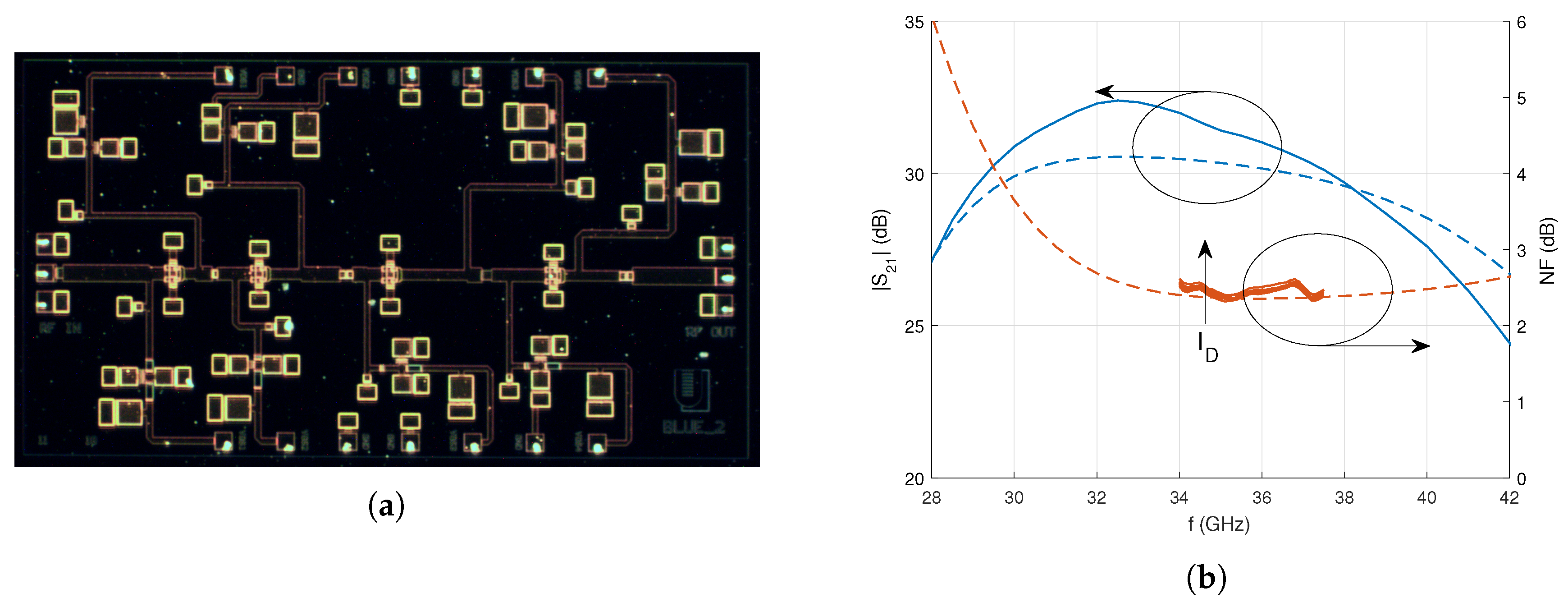

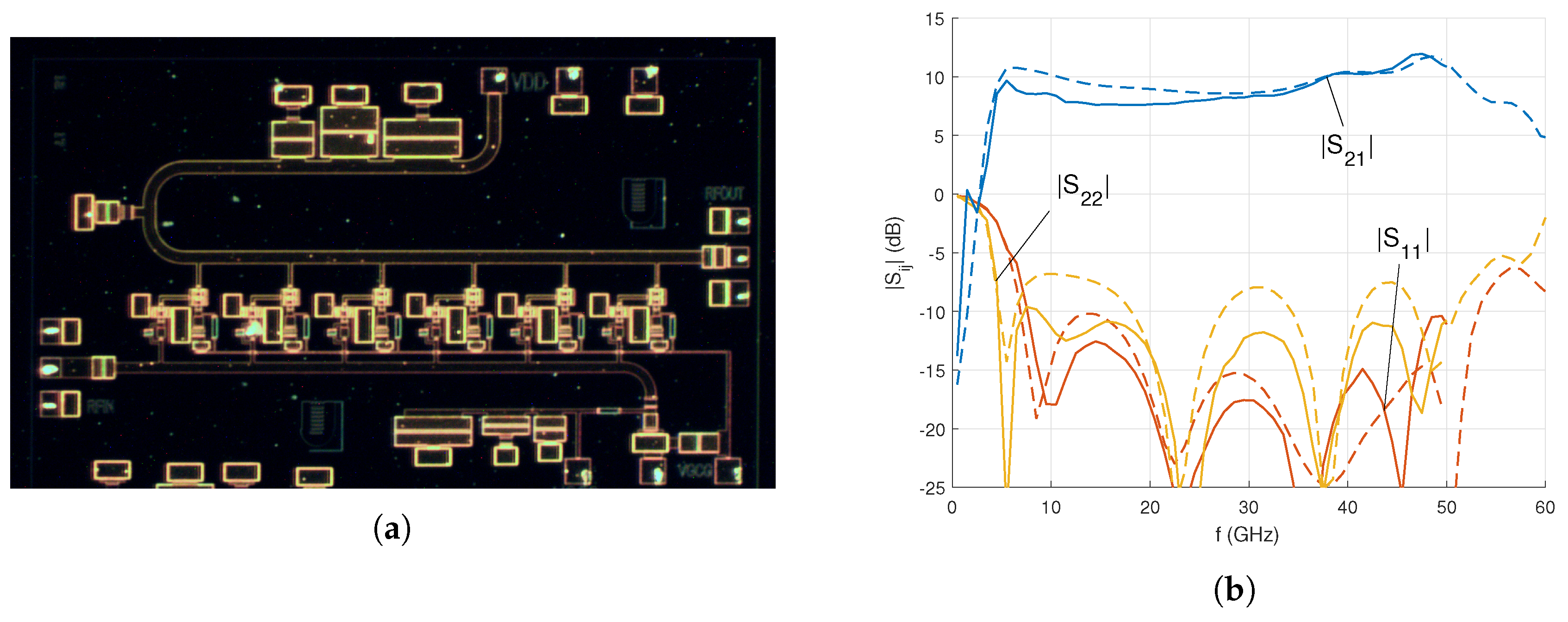

4. Test Vehicles

5. Discussion and Future Research

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| AlGaN | Aluminium Gallium Nitride |

| GaN | Gallium Nitride |

| GaAs | Gallium Arsenide |

| Si | Silicon |

| SiC | Silicon Carbide |

| SiN | Silicon Nitride |

| SiO2 | Silicon Dioxide |

| NiCr | Nickel Chromium |

| FET | Field-Effect Transistor |

| HEMT | High Electron Mobility Transistor |

| DUT | Device Under Test |

| LNA | Low-Noise Amplifier |

| SCFE | Single-Chip Front End |

| MMIC | Monolithic Microwave Integrated Circuit |

| DPDT | Double-Pole Double-Throw |

| SPDT | Single-Pole Double-Throw |

| Tx | Transmit (mode) |

| Rx | Receive (mode) |

| SSEC | Small-Signal Equivalent Circuit |

| MIM | Metal-Insulator-Metal |

| DC | Direct Current |

| RF | Radio Frequency |

| VNA | Vector Network Analyzer |

| TRL | Thru Reflect Line |

| LRRM | Line Reflect Reflect Match |

| EM | Electromagnetic |

| ENR | Excess Noise Ratio |

References

- Joshi, B.C.; Dhanavantri, C.; Kumar, D. Sapphire, SiC, AlN, Si and diamond-substrate material for GaN HEMT and LED. J. Optoelectron. Adv. Mater. 2009, 11, 1111–1116. [Google Scholar]

- Masuda, S.; Yamada, M.; Ohki, T.; Makiyama, K.; Okamoto, N.; Nakasha, Y.; Imanishi, K.; Kikkawa, T.; Shigematsu, H. C-Ku band GaN MMIC T/R frontend module using multilayer ceramics technology. In Proceedings of the IEEE MTT-S International Microwave Symposium, Baltimore, MD, USA, 5–10 June 2011; pp. 1–4. [Google Scholar] [CrossRef]

- Schuh, P.; Reber, R. Robust X-band low noise limiting amplifiers. In Proceedings of the IEEE MTT-S International Microwave Symposium Digest (MTT), Seattle, WA, USA, 2–7 June 2013; pp. 1–4. [Google Scholar] [CrossRef]

- Suijker, E.M.; Rodenburg, M.; Hoogland, J.A.; van Heijningen, M.; Seelmann-Eggebert, M.; Quay, R.; Bruckner, P.; van Vliet, F.E. Robust AlGaN/GaN Low Noise Amplifier MMICs for C-, Ku- and Ka-Band Space Applications. In Proceedings of the Annual IEEE Compound Semiconductor Integrated Circuit Symposium, Greensboro, NC, USA, 11–14 October 2009; pp. 1–4. [Google Scholar] [CrossRef]

- Rudolph, M. GaN HEMTs for low-noise amplification—Status and challenges. In Proceedings of the Integrated Nonlinear Microwave and Millimetre-wave Circuits Workshop (INMMiC), Graz, Austria, 20–21 April 2017; pp. 1–4. [Google Scholar] [CrossRef]

- Ciccognani, W.; Colangeli, S.; Serino, A.; Pace, L.; Fenu, S.; Longhi, P.E.; Poulain, J.; Leblanc, R. Comparative noise investigation of high-performance GaAs and GaN millimeter-wave monolithic technologies. In Proceedings of the European Microwave Integrated Circuits Conference (EuMIC), Paris, France, 30 September–1 October 2019; pp. 192–195. [Google Scholar]

- Giofrè, R.; Costanzo, F.; Ciccognani, W.; Colangeli, S.; Limiti, E. A GaN Single-Chip Front End With Improved Efficiency and Power by Using Class F Approach. IEEE Microw. Wirel. Compon. Lett. 2019, 29, 140–142. [Google Scholar] [CrossRef]

- Ciccognani, W.; Colangeli, S.; Costanzo, F.; Giofrè, R.; Polli, G.; Salvucci, A.; Vittori, M.; Limiti, E.; Sotgia, M.; Cirillo, M. A GaN Single-Chip Front-End for Active Electronically Scanned Arrays. In Proceedings of the IEEE/MTT-S International Microwave Symposium (IMS), Philadelphia, PA, USA, 10–15 June 2018; pp. 613–615. [Google Scholar] [CrossRef]

- Giofrè, R.; Colangeli, S.; Ciccognani, W.; Costanzo, F.; Polli, G.; Salvucci, A.; Vittori, M.; Sotgia, M.; Cirillo, M.; Limiti, E. S-Band GaN Single-Chip Front End for Active Electronically Scanned Array With 40-W Output Power and 1.75-dB Noise Figure. IEEE Trans. Microw. Theory Tech. 2018, 66, 5696–5707. [Google Scholar] [CrossRef]

- Giofrè, R.; Ciccognani, W.; Colangeli, S.; Feudale, M.; Lanzieri, C.; Polli, G.; Salvucci, A.; Suriani, A.; Vittori, M.; Limiti, E. A C-Band GaN Single Chip Front-End for SAR Applications. In Proceedings of the IEEE Radio and Wireless Symposium (RWS), San Antonio, TX, USA, 26–29 January 2020; pp. 162–164. [Google Scholar] [CrossRef]

- Salvucci, A.; Polli, G.; Vittori, M.; Giofrè, R.; Colangeli, S.; Ciccognani, W.; Limiti, E.; Carosi, D.; Feudale, M.; Lanzieri, C.; et al. A GaN single chip front-end for C-band synthetic aperture radars. In Proceedings of the International Microwave and Radar Conference (MIKON), Poznan, Poland, 14–17 May 2018; pp. 504–507. [Google Scholar] [CrossRef]

- van Heijningen, M.; de Hek, P.; Dourlens, C.; Fellon, P.; Adamiuk, G.; Ayllon, N.; van Vliet, F. C-Band Single-Chip Radar Front-End in AlGaN/GaN Technology. IEEE Trans. Microw. Theory Tech. 2017, 65, 4428–4437. [Google Scholar] [CrossRef]

- Limiti, E.; Colangeli, S.; Bentini, A.; Nanni, A. Characterization and modeling of low-cost, high-performance GaN-Si technology. In Proceedings of the International Conference on Microwaves, Radar and Wireless Communications (MIKON), Warsaw, Poland, 21–23 May 2012; Volume 2. [Google Scholar]

- Kazior, T.E.; LaRoche, J.R.; Ip, K.; Kennedy, T.; Knickerbocker, J.; Tsang, C.; Soirez, L. More Than Moore—Wafer Scale Integration of Dissimilar Materials on a Si Platform. In Proceedings of the IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), New Orleans, LA, USA, 11–14 October 2015; p. 1. [Google Scholar] [CrossRef]

- Kazior, T.E.; LaRoche, J.R.; Hoke, W.E. More Than Moore: GaN HEMTs and Si CMOS Get It Together. In Proceedings of the IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), Monterey, CA, USA, 13–16 October 2013; pp. 1–4. [Google Scholar] [CrossRef]

- Boles, T. GaN-on-silicon present challenges and future opportunities. In Proceedings of the European Microwave Integrated Circuits Conference (EuMIC), Nuremberg, Germany, 8–10 October 2017; pp. 21–24. [Google Scholar] [CrossRef]

- Hsu, S.S.H.; Tsou, C.; Lian, Y.; Lin, Y. GaN-on-silicon devices and technologies for RF and microwave applications. In Proceedings of the IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), Taipei, Taiwan, 24–26 August 2016; pp. 1–3. [Google Scholar] [CrossRef]

- Buchta, M.; Beilenhoff, K.; Blanck, H.; Thorpe, J.; Behtash, R.; Heckmann, S.; Jung, H.; Ouarch, Z.; Camiade, M. GaN technologies and developments: Status and trends. In Proceedings of the International Conference on Microwave and Millimeter Wave Technology, Chengdu, China, 8–11 May 2010; pp. 488–491. [Google Scholar] [CrossRef]

- Reveyrand, T.; Ciccognani, W.; Ghione, G.; Jardel, O.; Limiti, E.; Serino, A.; Camarchia, V.; Cappelluti, F.; Quéré, R. GaN Transistor Characterisation and Modelling Activities Performed within the Frame of the KorriGaN Project. Int. J. Microw. Wirel. Technol. 2010, 2, 51–61. [Google Scholar] [CrossRef]

- CORDIS’ Website on the MiGaNSOS Project. Available online: https://cordis.europa.eu/project/id/776322/ (accessed on 6 January 2021).

- Pace, L.; Costanzo, F.; Longhi, P.; Ciccognani, W.; Colangeli, S.; Suriani, A.; Leblanc, R.; Limiti, E. Design of a Ka-band single-chip front-end based on a 100 nm GaN-on-Si technology. In Proceedings of the Integrated Nonlinear Microwave and Millimetre-Wave Circuits Workshop (INMMiC), Cardiff, UK, 16–17 July 2020. [Google Scholar] [CrossRef]

- Pace, L.; Colangeli, S.; Ciccognani, W.; Longhi, P.E.; Limiti, E.; Leblanc, R.; Feudale, M.; Vitobello, F. Design and validation of 100 nm GaN-on-Si Ka-Band LNA based on custom noise and small signal models. Electronics 2020, 9, 150. [Google Scholar] [CrossRef]

- Pace, L.; Ciccognani, W.; Colangeli, S.; Longhi, P.E.; Limiti, E.; Pace, L.; Ciccognani, W.; Colangeli, S.; Longhi, P.E.; Limiti, E.; et al. A Ka-band low-noise amplifier for space applications in a 100 nm GaN on Si technology. In Proceedings of the Conference on Ph.D Research in Microelectronics and Electronics (PRIME), Lausanne, Switzerland, 15–18 July 2019; pp. 161–164. [Google Scholar] [CrossRef]

- Longhi, P.; Colangeli, S.; Ciccognani, W.; Pace, L.; Leblanc, R.; Limiti, E. C to V-band cascode distributed amplifier design leveraging a double gate length Gallium Nitride on Silicon process. In Proceedings of the IEEE MTT-S International Microwave Symposium Digest, Los Angeles, CA, USA, 4–6 August 2020; pp. 409–412. [Google Scholar] [CrossRef]

- OMMIC’s Website. Available online: https://www.ommic.com/iii-v-processes/ (accessed on 6 January 2021).

- Engen, G.F.; Hoer, C.A. Thru-Reflect-Line: An Improved Technique for Calibrating the Dual Six-Port Automatic Network Analyzer. IEEE Trans. Microw. Theory Tech. 1979, 27, 987–993. [Google Scholar] [CrossRef]

- Williams, D.F.; Marks, R.B. Transmission line capacitance measurement. IEEE Microw. Guid. Wave Lett. 1991, 1, 243–245. [Google Scholar] [CrossRef]

- Williams, D.F.; Arz, U.; Grabinski, H. Characteristic-impedance measurement error on lossy substrates. IEEE Microw. Wirel. Compon. Lett. 2001, 11, 299–301. [Google Scholar] [CrossRef]

- Pulido-Gaytán, M.A.; de Landa, A.Z. Determination of the Line Characteristic Impedance Using Calibration Comparison. In Proceedings of the ARFTG Microwave Measurement Conference, Philadelphia, PA, USA, 15 June 2018; pp. 1–3. [Google Scholar] [CrossRef]

- Williams, D.F.; Marks, R.B.; Davidson, A. Comparison of On-Wafer Calibrations. In Proceedings of the ARFTG Conference Digest, San Diego, CA, USA, 5–6 December 1991; Volume 20, pp. 68–81. [Google Scholar] [CrossRef]

- Davidson, A.; Jones, K.; Strid, E. LRM and LRRM Calibrations with Automatic Determination of Load Inductance. In Proceedings of the ARFTG Conference Digest, Monterey, CA, USA, 29–30 November 1990; Volume 18, pp. 57–63. [Google Scholar] [CrossRef]

- Colangeli, S.; Ciccognani, W.; Serino, A.; Longhi, P.E.; Pace, L.; Poulain, J.; Leblanc, R.; Limiti, E. Nondestructive, Self-Contained Extraction Method of Parasitic Resistances in HEMT Devices. IEEE Trans. Microw. Theory Tech. 2020, 68, 2571–2578. [Google Scholar] [CrossRef]

- Colangeli, S.; Ciccognani, W.; Cleriti, R.; Palomba, M.; Limiti, E. Optimization-based approach for scalable small-signal and noise model extraction of GaN-on-SiC HEMTs. Int. J. Numer. Model. Electron. Netw. Devices Fields 2017, 30, e2135. [Google Scholar] [CrossRef]

- Dambrine, G.; Cappy, A.; Heliodore, F.; Playez, E. A new method for determining the FET small-signal equivalent circuit. IEEE Trans. Microw. Theory Tech. 1988, 36, 1151–1159. [Google Scholar] [CrossRef]

- Berroth, M.; Bosch, R. Broad-band determination of the FET small-signal equivalent circuit. IEEE Trans. Microw. Theory Tech. 1990, 38, 891–895. [Google Scholar] [CrossRef]

- Tiemeijer, L.F.; Havens, R.J.; de Kort, R.; Scholten, A.J. Improved Y-factor method for wide-band on-wafer noise-parameter measurements. IEEE Trans. Microw. Theory Tech. 2005, 53, 2917–2925. [Google Scholar] [CrossRef]

- Pospieszalski, M.W. Modeling of noise parameters of MESFETs and MODFETs and their frequency and temperature dependence. IEEE Trans. Microw. Theory Tech. 1989, 37, 1340–1350. [Google Scholar] [CrossRef]

- Mokari, M.E.; Patience, W. A new method of noise parameter calculation using direct matrix analysis. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 1992, 39, 767–771. [Google Scholar] [CrossRef]

Samples are to be requested to the foundry. |

| Parameter | D01GH | D006GH |

|---|---|---|

| Gate length | 100 nm | 60 nm |

| Cutoff frequency | 110 GHz | 150 GHz |

| Maximum oscillation frequency | 180 GHz | 190 GHz |

| Gate-drain breakdown voltage (1) | 36 V | 36 V |

| Maximum drain current density | 1200 mA/mm | 1200 mA/mm |

| Maximum extrinsic transconductance | 800 mS/mm | 950 mS/mm |

| Minimum noise figure at 40 GHz | 1.5 dB | 1.1 dB |

| RF power density | 4 W/mm (2) | 3.3 W/mm |

| Parameter | Unit | D01GH ( mA) | D006GH ( mA) |

|---|---|---|---|

| F | 9.2306 × | 9.7087 × | |

| F | 7.5285 × | 5.1388 × | |

| F | 8.2609 × | 8.5547 × | |

| s | 2.2607 × | 3.7819 × | |

| H | 2.4735 × | 2.5441 × | |

| H | 2.5520 × | 2.5763 × | |

| H | 1.5125 × | 1.8542 × | |

| Ω | 1.2537 | 1.2931 | |

| Ω | 1.8400 | 1.6700 | |

| Ω | 0.8000 | 0.8600 | |

| F | 2.1598 × | 1.7146 × | |

| F | 8.3262 × | 7.8070 × | |

| F | 3.2511 × | 3.4192 × | |

| Ω | 3.0755 | 0.4741 | |

| Ω | 14.4632 | 15.9634 | |

| S | 5.6334 × | 0 | |

| S | 0.0059 | 0.0084 | |

| S | 8.6424 × | 5.3925 × | |

| S | 0.1322 | 0.1479 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Colangeli, S.; Ciccognani, W.; Longhi, P.E.; Pace, L.; Poulain, J.; Leblanc, R.; Limiti, E. Linear Characterization and Modeling of GaN-on-Si HEMT Technologies with 100 nm and 60 nm Gate Lengths. Electronics 2021, 10, 134. https://doi.org/10.3390/electronics10020134

Colangeli S, Ciccognani W, Longhi PE, Pace L, Poulain J, Leblanc R, Limiti E. Linear Characterization and Modeling of GaN-on-Si HEMT Technologies with 100 nm and 60 nm Gate Lengths. Electronics. 2021; 10(2):134. https://doi.org/10.3390/electronics10020134

Chicago/Turabian StyleColangeli, Sergio, Walter Ciccognani, Patrick Ettore Longhi, Lorenzo Pace, Julien Poulain, Rémy Leblanc, and Ernesto Limiti. 2021. "Linear Characterization and Modeling of GaN-on-Si HEMT Technologies with 100 nm and 60 nm Gate Lengths" Electronics 10, no. 2: 134. https://doi.org/10.3390/electronics10020134

APA StyleColangeli, S., Ciccognani, W., Longhi, P. E., Pace, L., Poulain, J., Leblanc, R., & Limiti, E. (2021). Linear Characterization and Modeling of GaN-on-Si HEMT Technologies with 100 nm and 60 nm Gate Lengths. Electronics, 10(2), 134. https://doi.org/10.3390/electronics10020134