1. Introduction

With the advent of IoT, the need for portable, and self-powered devices has been dramatically increasing. Batteries are still the most common way of powering embedded applications. Yet, due to their size, weight, impractical replacement, limited lifetime, and above all environmental impact, batteries tend to become unwelcomed in ultra-compact ultra-low power applications.

Harvesting energy from ambient background (solar, eolian, thermal, kinetic, etc.), has been a hot research topic over the last years. The goal is to do without batteries by implementing highly efficient dynamic power generators. In particular, the literature reports many implementations of kinetic harvesters involving piezoelectric devices Çiftci et al. [

1], Chen et al. [

2], Du and Seshia [

3], Sanchez et al. [

4], inductive devices Rahimi et al. [

5], and electrostatic (capacitive) devices Tao et al. [

6], Stanzione et al. [

7].

Piezoelectric energy harvesters (PEH) are among the most investigated and popular kinetic energy harvesting systems, first because of the wide availability of ambient vibration sources, and second because they can achieve relatively high power density, i.e., from tens to several hundreds of microwatts per cubic centimeter, compared to the capacitive or inductive conversion principles. Moreover, they are easy to combine with conventional integrated circuit technologies Stanzione et al. [

7].

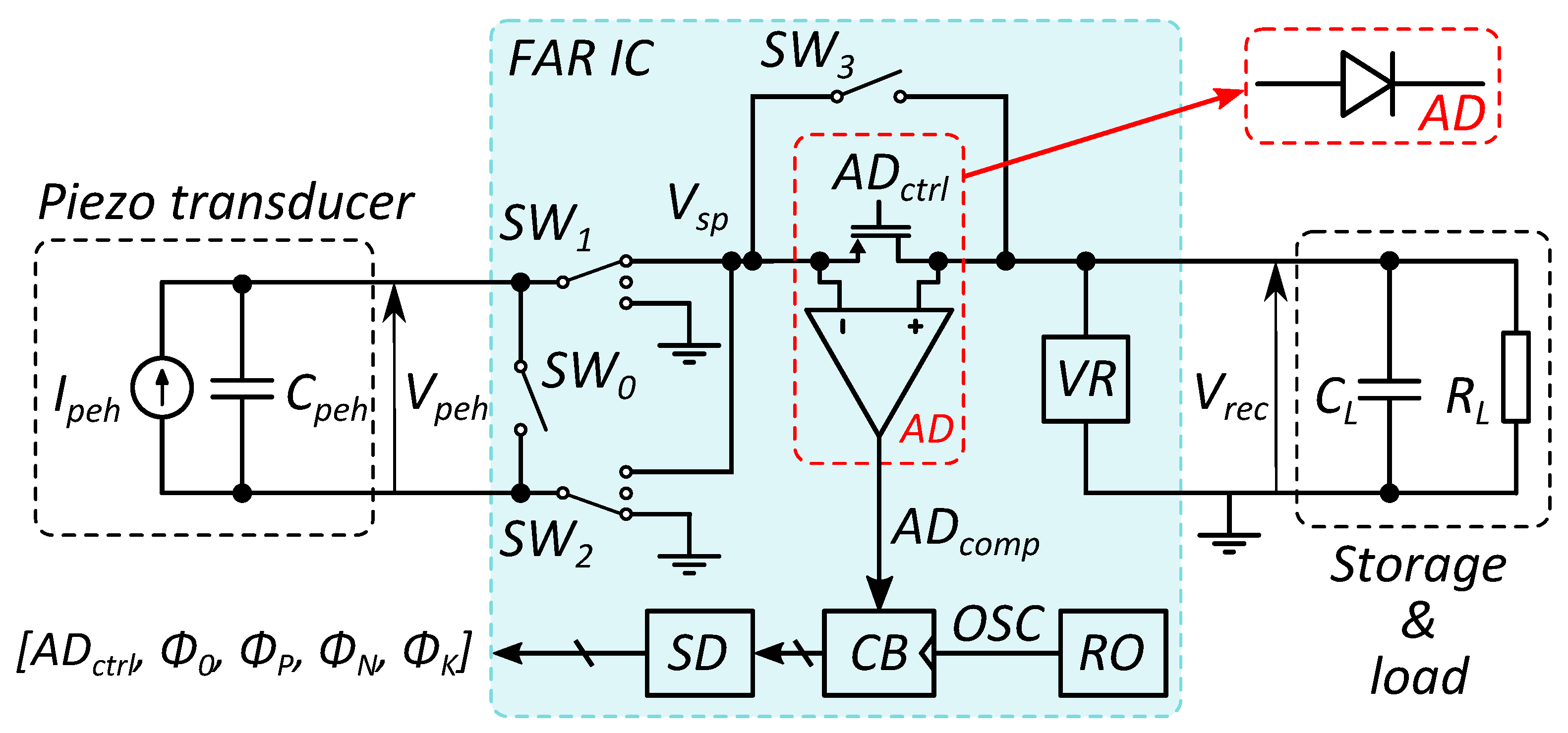

Figure 1 shows the basic topology of a PEH system. It breaks down into three core parts: (1) A piezoelectric transducer (PT). (2) An interface and control circuit (IC). (3) Storage and load elements.

Thanks to the piezoelectric properties of its material, the PT turns the mechanical energy into electrical energy. The equivalent electrical model of the PT consists in the parallel combination of an AC current source, which provides the current proportional to mechanical excitation, with an inherent piezoelectric capacitor . The storage element can be a supercapacitor , and the load is usually modelled as a resistor . Note that may change dynamically according to the power requirements of loads such as sensors or wireless modules for instance. The main role of the interface circuit is to rectify the AC voltage of the PT, , and provide the system with stable voltage supply. Ideally, the voltage supply should be independent of the load but in practice, a change in the value of can strongly affect the power efficiency of the harvester.

The most common interface circuit for rectifying

is a Full-Bridge Rectifier (FBR). Yet, the voltage drop across the rectifying diodes makes the FBR unsuitable for low-voltage PT (i.e.,

in the 1 V range or below). In order to circumvent the diodes’ threshold issue, Herbawi et al. [

8] proposed the principle of active rectification that uses a negative voltage converter (NVC) combined to a series-connected active diode (AD) instead of the FBR Peters et al. [

9]. The NVC acts like an FBR but uses transistors instead of diodes, thus yielding lower voltage drop across the rectifier. The AD prevents

-to-PT current backflow.

Furthermore, the combination of the inherent capacitor

in parallel with

causes

and

to be normally in phase quadrature. This contributes to further dramatically hamper FBR efficiency because

needs to discharge and recharge at each zero-crossing moment of

. Numerous interface topologies and architectures have been proposed to improve power efficiency by applying nonlinear synchronous switching Richard et al. [

10]. All these architectures use external devices, i.e.inductor and/or capacitor, to handle the charge of

. Synchronous Electric Charge Extraction (SECE) consists in extracting the energy accumulated in

by transferring it into an inductor, which in turn transfers it into the storage device Hehn et al. [

11], Dini et al. [

12], Shi et al. [

13], Morel et al. [

14,

15]. SECE alleviates the load dependency of the system but requires a bulky inductor and tends to have degraded performance for periodic excitation of PT. Synchronized Switch Harvesting architectures reuse the own charge of

to invert the polarity of

upon

zero-crossing. They employ either an inductor (SSHI) (Sanchez et al. [

4], Du et al. [

16], Ramadass and Chandrakasan [

17], Wu et al. [

18], Chamanian et al. [

19,

20]) or a set of capacitors (SSHC) (Chen et al. [

2], Du and Seshia [

3], Chen et al. [

21], Hong et al. [

22]) to store the charge of

temporarily before sending it back once the electrodes of the PT have been swapped. Architectures combining both an inductor and a capacitor have also been reported in Çiftci et al. [

23] and Çiftci et al. [

1]. Synchronized-switch-based architectures globally achieve better power efficiency than SECE for both shock and periodic excitation. According to Ramadass and Chandrakasan [

17], full voltage flip of

could theoretically allow very high (i.e., infinite) efficiency. Yet, in practice the characteristics of the components strongly limit the voltage flip efficiency, and

still needs to provide

with complementary charge prior to transferring energy from the PT to

and

. Moreover, SSHC and SSHI architectures have load-dependent performance, which means that the power efficiency strongly depends on changes in

and/or the excitation’s amplitude. Çiftci et al. [

1] proposed a circuit that reduces the load-dependency of the power efficiency. But such systems require more complex control.

Therefore, there is a genuine interest in proposing an easy-to-implement synchronized switch architecture that both achieves high-efficiency voltage flip and is able to maintain fair power efficiency during transient changes of the load . Enhancing the voltage flip minimizes the charge needed by and thus allows to extract energy from the PT shortly after the voltage flip. This point is particularly critical in low-voltage systems, i.e., V, that harvest power in the tens of microwatts range.

In this paper, we demonstrate the benefit of a synchronized-switch-based architecture, referred to as full active rectifier (FAR) and first proposed in Wassouf et al. [

24], to alleviate the load influence of the piezoelectric energy harvester. The FAR is based on the SSHC concept that consists in flipping

by means of a capacitor, but has much simpler control and needs no additional capacitors. In terms of power performance, the FAR is similar to the Switch-only principle Ramadass [

25], and thus performs worse than state-of-the-art SSHI or SSHC. But it is important to note that, discussing raw absolute performance is not the point of this paper. The key result we propose here is the theoretical and experimental proof that thanks to the voltage flip enhancement, the FAR achieves better power efficiency under load constraint than Switch-only. It is yet also important to note that the proposed technique may be applied in addition to state-of-the-art voltage flip architectures that reuse the charge of

(i.e., SSHI and SSHC), and hence contribute to enhance their performance.

The paper is organized as follows:

Section 2 presents the enhanced voltage flip concept, the FAR IC topology, its operation principle, and provides a thorough analysis of charge loss and power performance compared to Switch-only.

Section 3 provides experimental results. Finally,

Section 4 concludes this paper.

2. Enhanced Voltage Flip

The voltage flip enhancement technique that we propose consists in recharging

with

. At first glance, the concept of reusing the stored charge may appear as counter intuitive but in this section, we demonstrate that it contributes to enhance the power efficiency of the harvester. At each zero-crossing instant of

, the piezo capacitor

is first shorted, and then immediately recharged with a fraction of the charge from the storage capacitor

Wassouf et al. [

24]. In the following sections, the proposed concept will be referred to as the FAR.

The concept is based on the use of a large storage capacitance

, which should be at least one order of magnitude greater than

. This can easily be admitted because storage capacitances have usually large values. As discussed in

Section 2.3, the concept also imperatively needs the rectified voltage

to be regulated, in order to ensure optimal power extraction of the proposed harvester.

For comparison purpose, because the FAR and the conventional Switch-only principle have a priori the same energy balance, we designed the FAR integrated circuit architecture presented below. This circuit allows to implement both FAR and Switch-only modes.

2.1. FAR IC Topology

Figure 2 presents the topology of the FAR IC. A set of switches (

to

) consisting of transmission gates (TG) is connected to an active diode (AD) to form the rectifying part of the system. The logic control block (CB) of

Figure 3 performs the switching sequence described below. The circuit also features a voltage regulator (VR) Du and Seshia [

3], a ring oscillator (RO) Ferreira and Galup-Montoro [

26], and switch drivers (SD). The later include a charge pump Tsuji et al. [

27] and level shifters Du and Seshia [

3], Matsuzuka et al. [

28] that are needed to control the switches properly. Note that blocks VR, RO and SD are standard functions, which are largely documented in the state-of-the-art literature. Therefore, they are not further detailed in this paper.

The AD is used for both preventing the current from flowing back from

and detecting the zero-crossing moment of

. It comprises a PMOS switch and an ultra-low power comparator proposed in Du and Seshia [

3]. When the voltage at node

drops below the rectified output voltage

(

Figure 2), the PMOS switch of AD is turned off, and the voltage flip operation is triggered as explained below.

2.2. FAR Operation Principle

The zero-crossing of causes the AD’s comparator output signal to go high. triggers the signal sequence generated by CB. The CB signals control in turn the AD and the switches to .

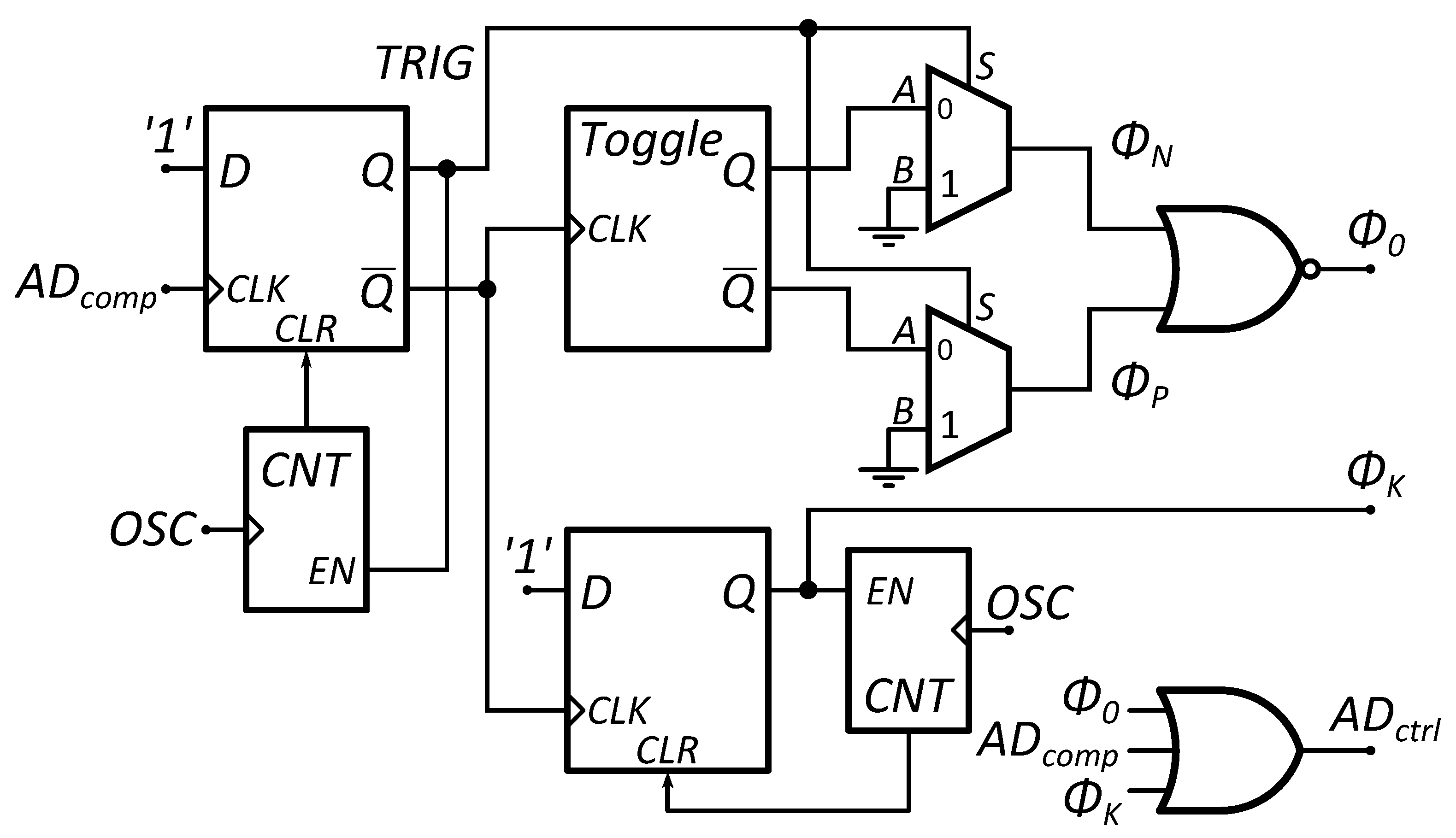

Figure 3 shows the architecture of CB. Signal

controls the PMOS switch of AD, signal

controls

, signals

and

both control switches

and

, and signal

controls

.

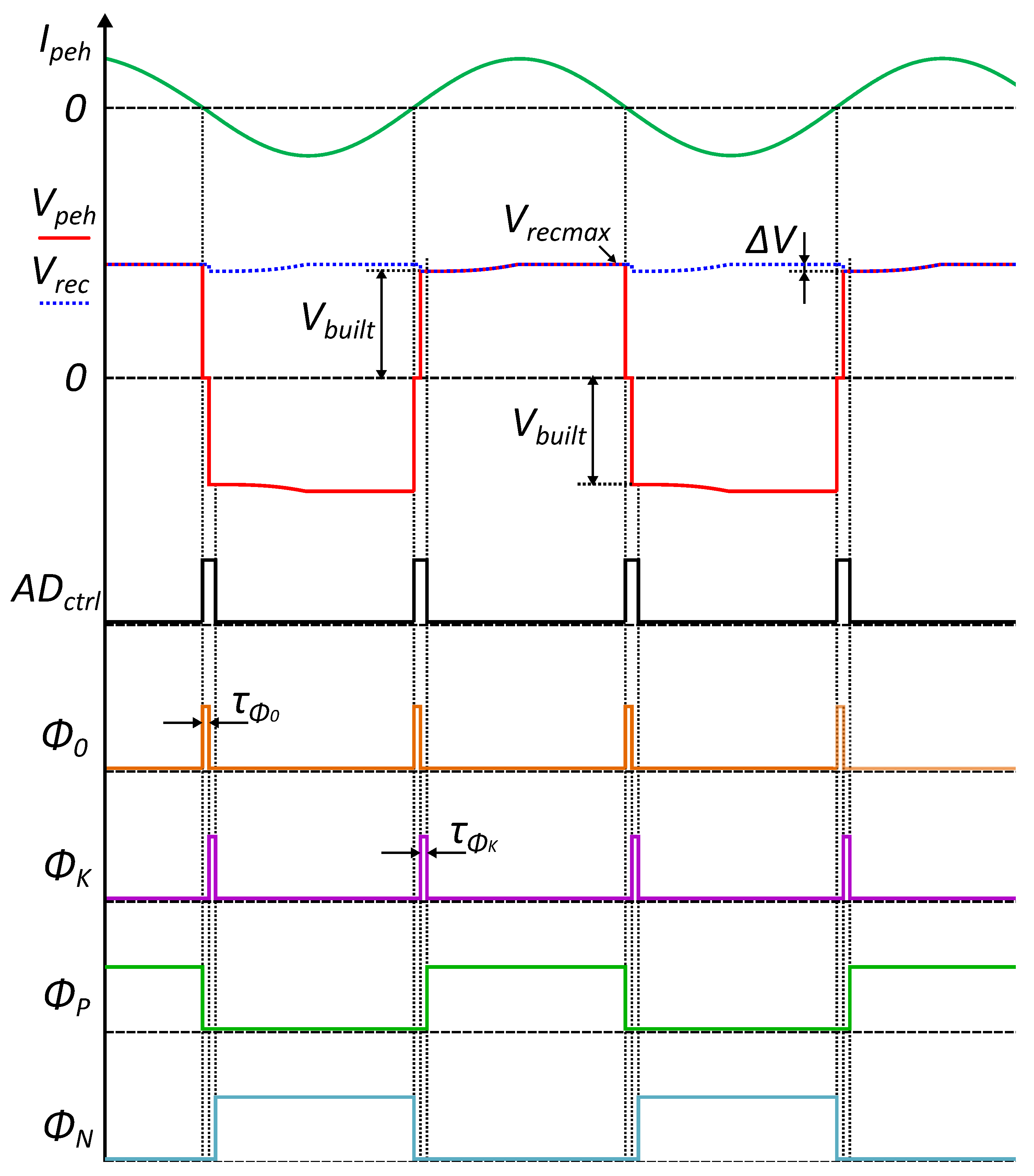

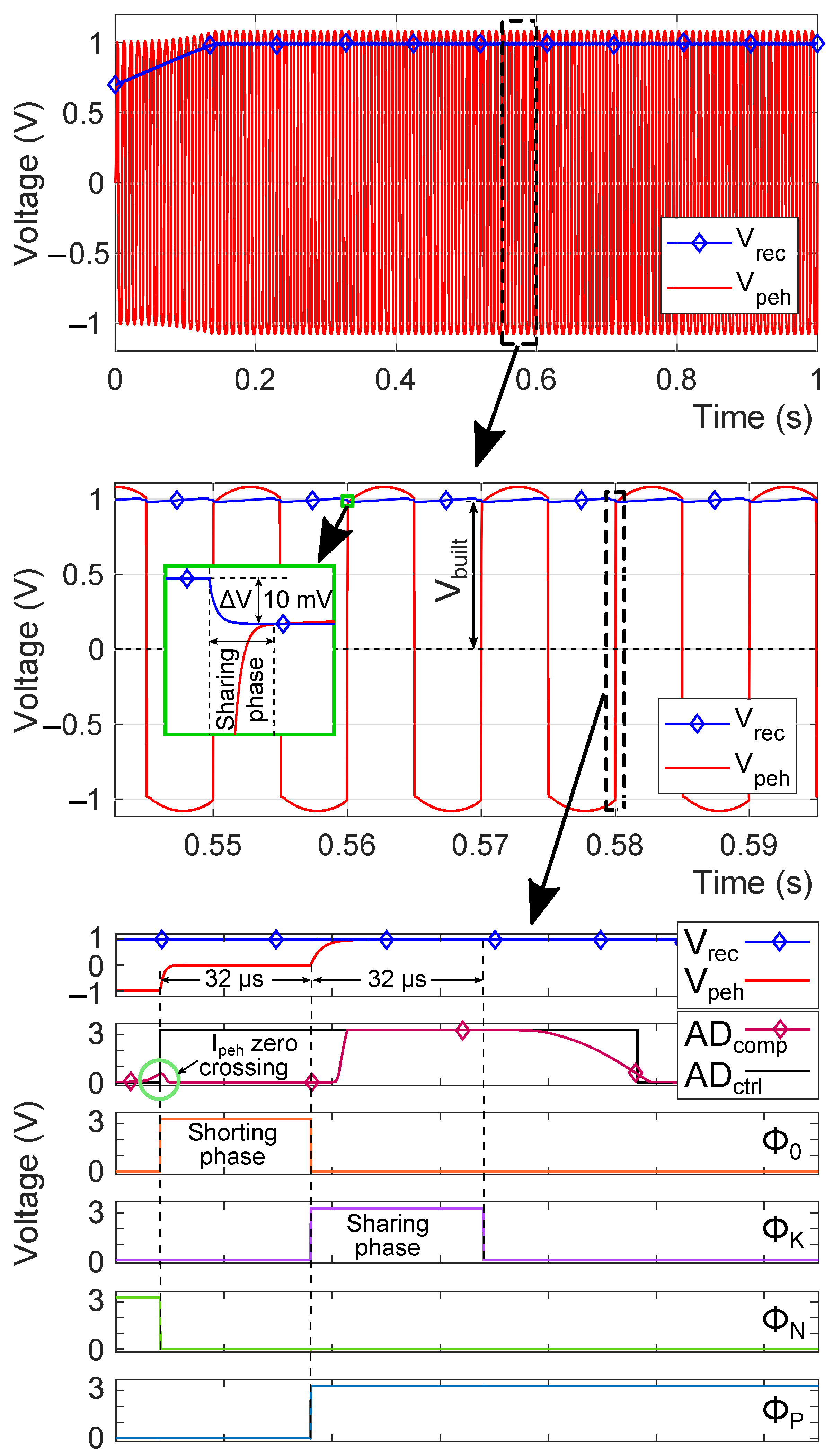

Figure 4 shows the sequence and its effect on the PEH’s voltages, while

Table 1 shows the operating scheme of the switches according to the control signals. It is worth noticing that the voltage flip operation is triggered by signal

and thus the control block auto-adapts according to the zero-crossing moment of

regardless of the PT’s excitation frequency

.

The operation of the FAR breaks down into 3 phases.

2.2.1. Shorting Phase

Signal

acts as the clock signal of a D flip-flop whose data input is set to a constant logic “high” state (

Figure 3). When

goes high, a trigger signal

turns on signals

and

simultaneously, which puts switches

and

in high impedance, i.e., off (

Table 1). In the meantime, signal

turns on

(

Figure 4), which shorts

. Signal

remains high until

is discharged. The duration of the shorting phase

depends on the value of

and the resistance of

. The TGs used to implement the switches have very low ON-resistance, typically around

. Assuming

nF, based on the off-the-shelf transducer characteristics (S118-J12S-1808YB,

Piezo.com, accessed on 1 September 2021) used in the experiments (

Section 3), the corresponding

time constant is thus

µs. The duration

is controlled by means of a counter (CNT in

Figure 3) clocked by the RO signal

. This signal is initially used to clock the charge pump used in the switch drivers, and has a frequency of 125 kHz. Therefore,

allows controlling

with 8 µs accuracy. In the proposed system, we used a modulo 4 counter, which thus yields

µs. This duration is largely sufficient to ensure complete discharging of

.

2.2.2. Sharing Phase

Once

is reset, i.e.,

goes high, a toggle sets either

or

to high depending on whether

is positive or negative, respectively. When

is high,

is connected to node

and

is connected to ground, and inversely when

is high (

Table 1). In the meantime,

goes high, which closes

and causes

to share its charge with

. During this sharing phase,

is in series with either

or

. Since all switches are implemented with the same TGs, the RC time constant is thus 3 µs. Therefore, we also used a modulo 4 counter (

Figure 3) to set the duration of the sharing phase

µs, which is also sufficient to complete the charge transfer.

At the end of the sharing phase, the value of

across

is

:

only depends on the charge

stored in

, the charge of

being

after the shorting phase. If

, then

, which is the value of

right before the voltage flip operation is triggered (see

Figure 4). Note that,

continuously increases as

charges.

2.2.3. Power Extraction Phase

Once

is recharged,

turns off while either

or

remains on, depending on whether

is negative (

high) or positive (

high), respectively (

Figure 4). Since the terminals of the PT are swapped by

and

at each phase inversion of

, this procudes the rectifying of

(i.e.,

). In this phase, the AD’s PMOS switch turns on as soon as

, which in turn connects the PT to

. As a result, most of the charges transfer directly from PT to

and

.

Note that the PMOS switch turns on very shortly after the sharing phase, since the voltage at node

is

as mentioned in

Section 2.2.2. This has significant consequence on the power efficiency as discussed in

Section 2.3.

2.3. Power Performance Analysis

If we suppose that

is a sine current source such as

where

represents the amplitude and

is the vibration frequency, then the expression of the open-circuit voltage

across the PT is given by:

with

the open-circuit amplitude. When

shifts from

to

, the total amount of charge generated by the PT in half a period is thus (Du and Seshia [

3], Ramadass [

25]):

where

.

2.3.1. With Infinite

The total charge loss breaks down into two main contributions: , lost by during the recharging of (sharing phase) and , the charge that goes to during the power extraction phase, i.e., when is in parallel with .

In steady state, when

reaches its maximum value

(

Figure 4) imposed by VR, the expressions for

and

are

where

represents the ripple of

caused by the recharging of

. The total charge loss is then

From (

1) and (

5), we may consider

provided that

. Therefore, we can consider that

fully recharges

, making

the principal charge loss (i.e.,

). We can thus express the total charge stored on

in half a period as

and then the total charge on a full period is then

.

Thus, the output power is given by

From (

9), we can deduce that the maximum power extraction is achieved when

, which corresponds to a maximum power

This result shows that the power efficiency is inherently load-dependent because applying a finite value load

affects

, as it would for any synchronized switch harvesting system ( Çiftci et al. [

1], Chen et al. [

21], Du et al. [

29]) and suggests VR should regulate

to

(Ramadass and Chandrakasan [

17]). Moreover, it is identical to Switch-only, the architecture and signals of which are presented in

Figure 5.

When

is infinite and

is regulated to

, the amount of charge needed to recharge either

(FAR) or

(Switch-only) is

. Yet, energy harvesting systems are meant to supply a finite value load with charges delivered by

and PT. As demonstrated in the next section and in

Section 3.2, the proposed FAR architecture has an impact on the power performance when

has finite value. Furthermore, since FAR and Switch-only have the same power performance a priori, we compared both architectures.

2.3.2. With Finite

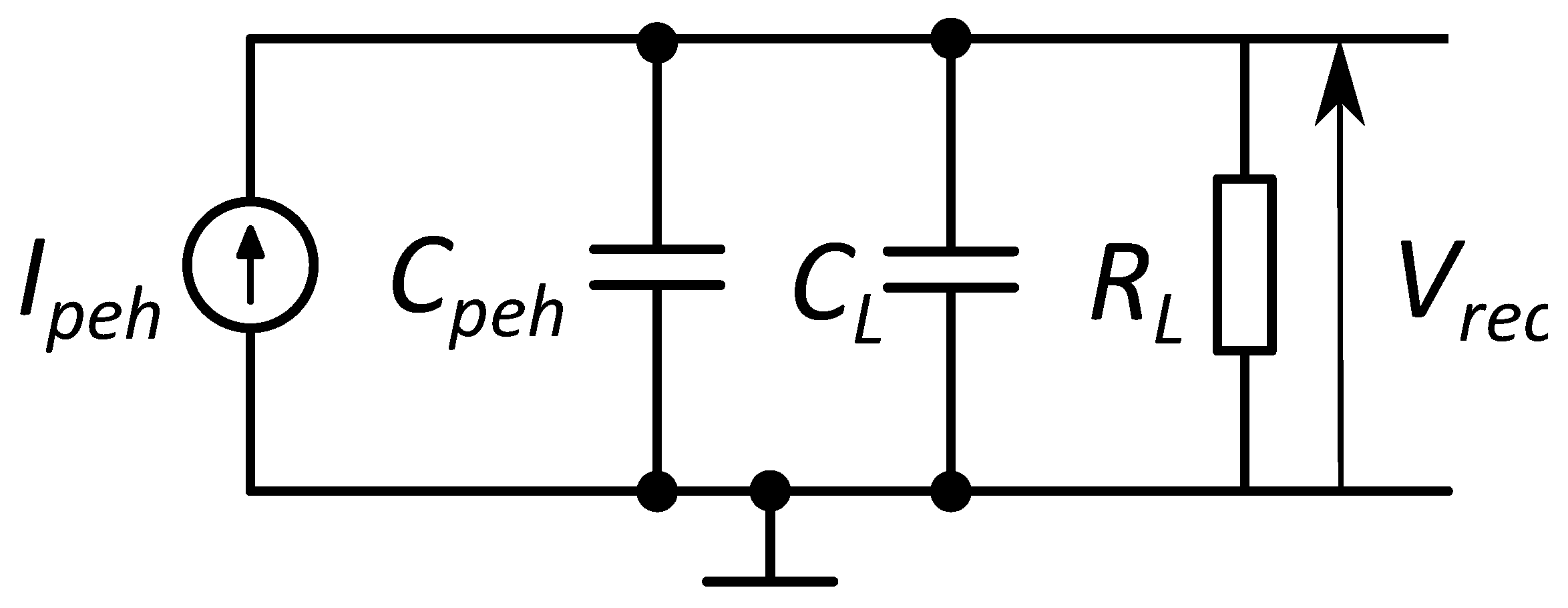

Figure 6 shows the equivalent electrical model of the PEH during the power extraction phase (i.e., AD is “ON”), when

has a finite value. Note that this model assumes the series resistances of the switches and ADs are negligible, which is realistic considering

is around several tens of kilo-ohms as discussed below. The expression of

is given by:

where

and

K is the initial condition constant such as

, considering

s corresponds to the zero-crossing moment of

. Equation (

11) applies for

lower than

. When

reaches

, it is regulated to this value by VR.

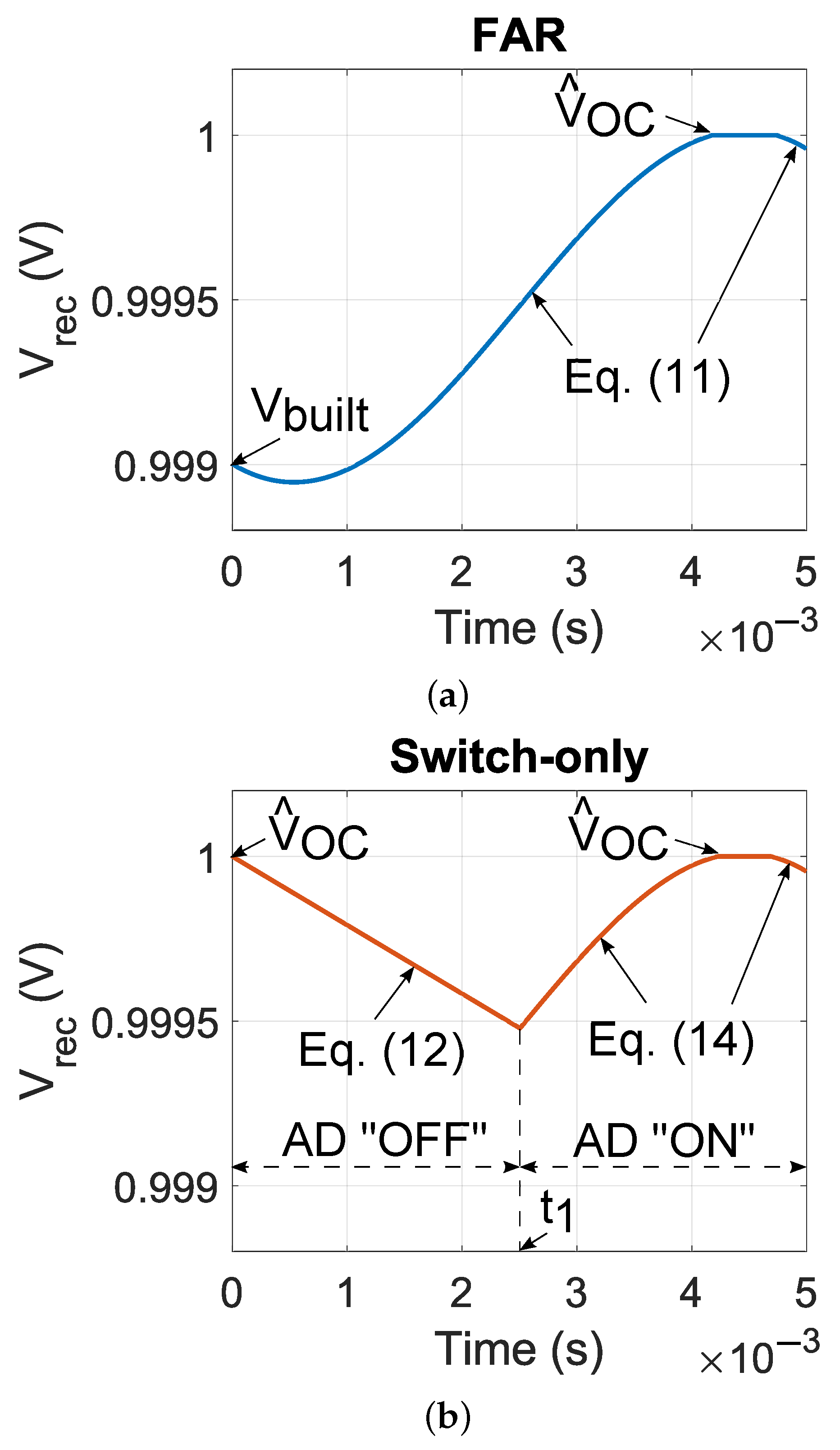

Figure 7a shows

for the FAR architecture (

) simulated on half a period of

when applying a finite load

at

s. The parameters of PT are:

nF and

A, and the excitation frequency is

Hz. This corresponds to

V. The load is

k

, and

K is set so that

, which is the value of

when

at the zero-crossing moment of

(See

Section 2.2.2).

In the Switch-only architecture, the evolution of

breaks down into two phases. First, its AD is “OFF” and

recharges, while in the meantime,

discharges into

. Therefore, in this phase,

and

evolve separately. On the one hand, the expression of

is

where

is the initial value of

at the zero-crossing moment of

. On the other hand, the expression of

is

The second phase of

for the Switch-only starts when AD is “ON” (i.e.,

). In this phase, the equivalent schematic of the Switch-only architecture is exactly the same as for the FAR (cf.

Figure 6). Therefore, the expression of

is deduced from (

11) but with an offset

:

This offset

is induced by the decay of

during the first phase of Switch-only. Furthermore, just as for the FAR architecture, when

reaches

, it is regulated by VR.

Figure 7b shows

for the Switch-only architecture (

) simulated with the same parameters as for the FAR simulation presented in

Figure 7a. Note that, for Switch-only

V.

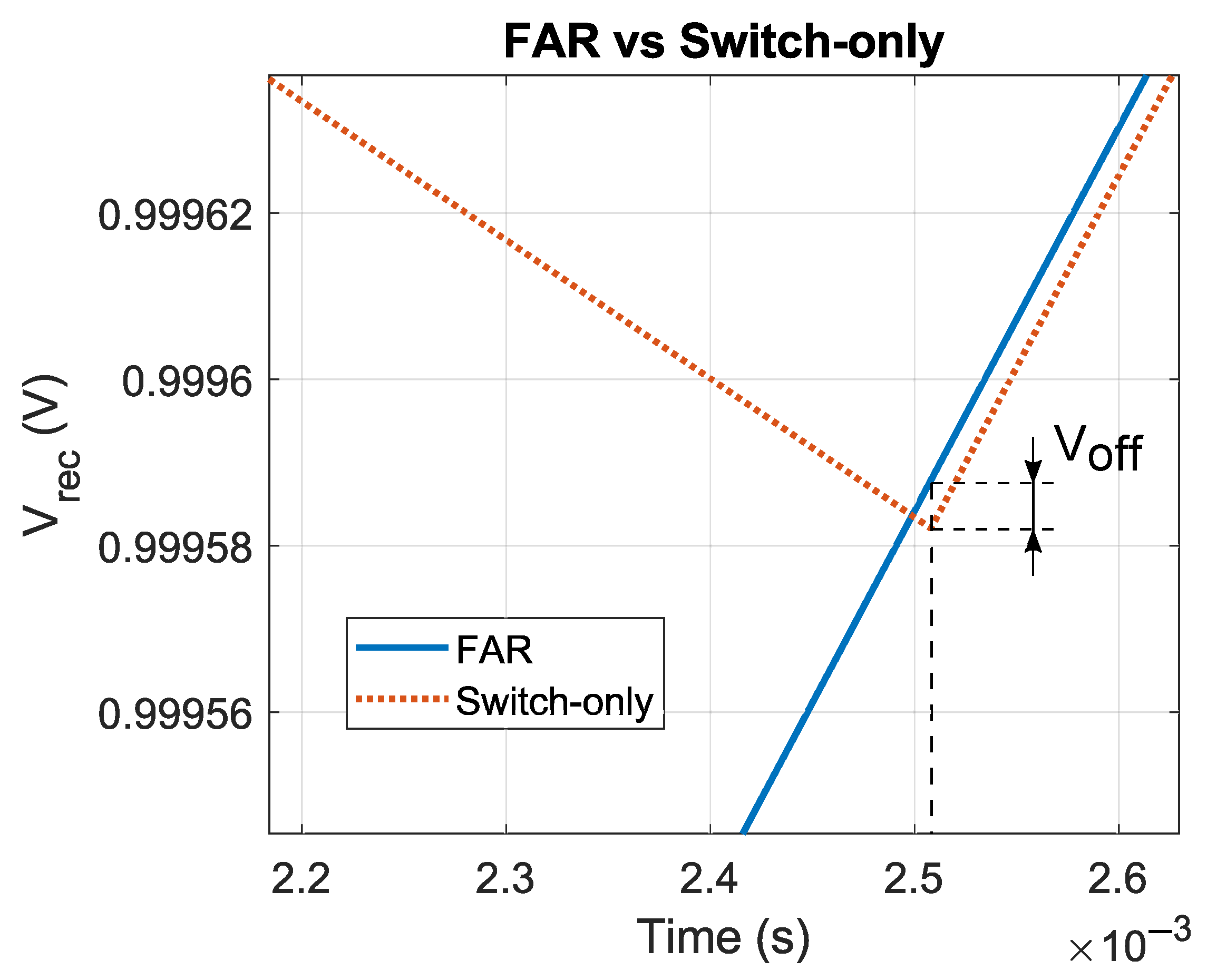

To establish whether

is positive or negative, i.e., which one yields the greater value (

11 or

14, FAR or Switch-only), we first needed to find the moment

when

of Switch-only caught up with

, which corresponds to the moment when AD turns “ON”:

Note: there is no analytic expression to solve (

15). Therefore, to evaluate

we need to apply a numerical method, such as Newton–Raphson ( Conejo and Baringo [

30]). The value

is then injected into (

14) to determine

so that Equations (

12)–(

14) yield the same value. Numerical simulations (

Figure 8) reveal that, whatever the values of the parameters in (

11) and (

14),

, which means that for

,

.

This result has significant consequences for the power efficiency of the systems as

evolves. More specifically, from (

11) we found the limit value

of

for which

reached

at

. Applying

in (

14) yielded

. Since the value of

set the initial conditions of

for the next half period of

, we verified that for

, the average value of

decreased to compensate for the presence of

while the average value of

remained constant. More generally, when

,

decreased in both architectures,

decreased faster and, more importantly, stabilized to a lower value than

. Note that, for either architecture,

adjusted to a steady-state average value that depended on the amount of energy the harvester transfered from the PT to

. This amount was lower in Switch-only because the power extraction phase was shorter than in FAR. Furthermore, the value of

only affected the evolution speed of

when

changed. The faster decreasing speed of

cames from the smaller time constant

when the ADwas “OFF” (see

12). The same reason explains why

stabilized at a lower value than

.

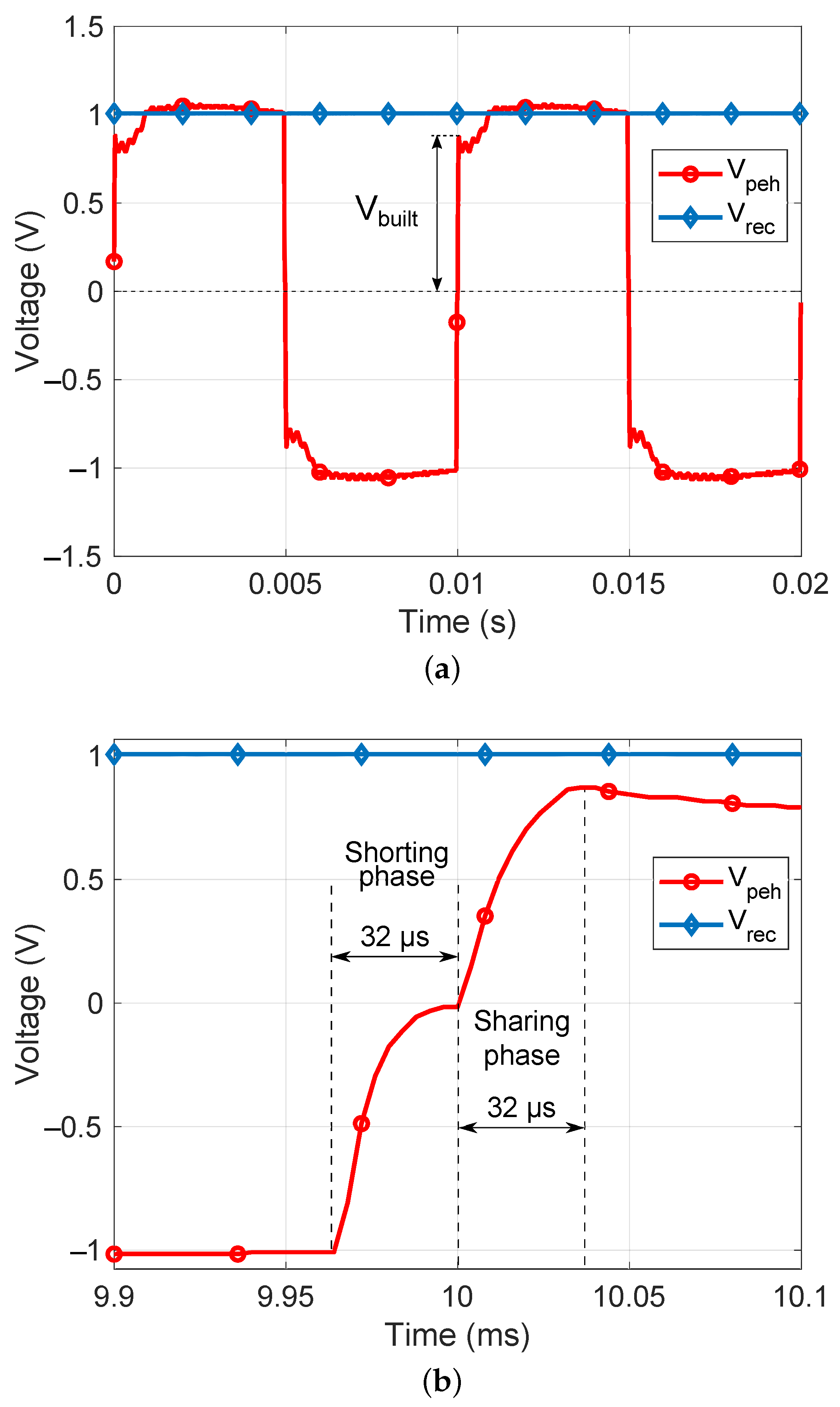

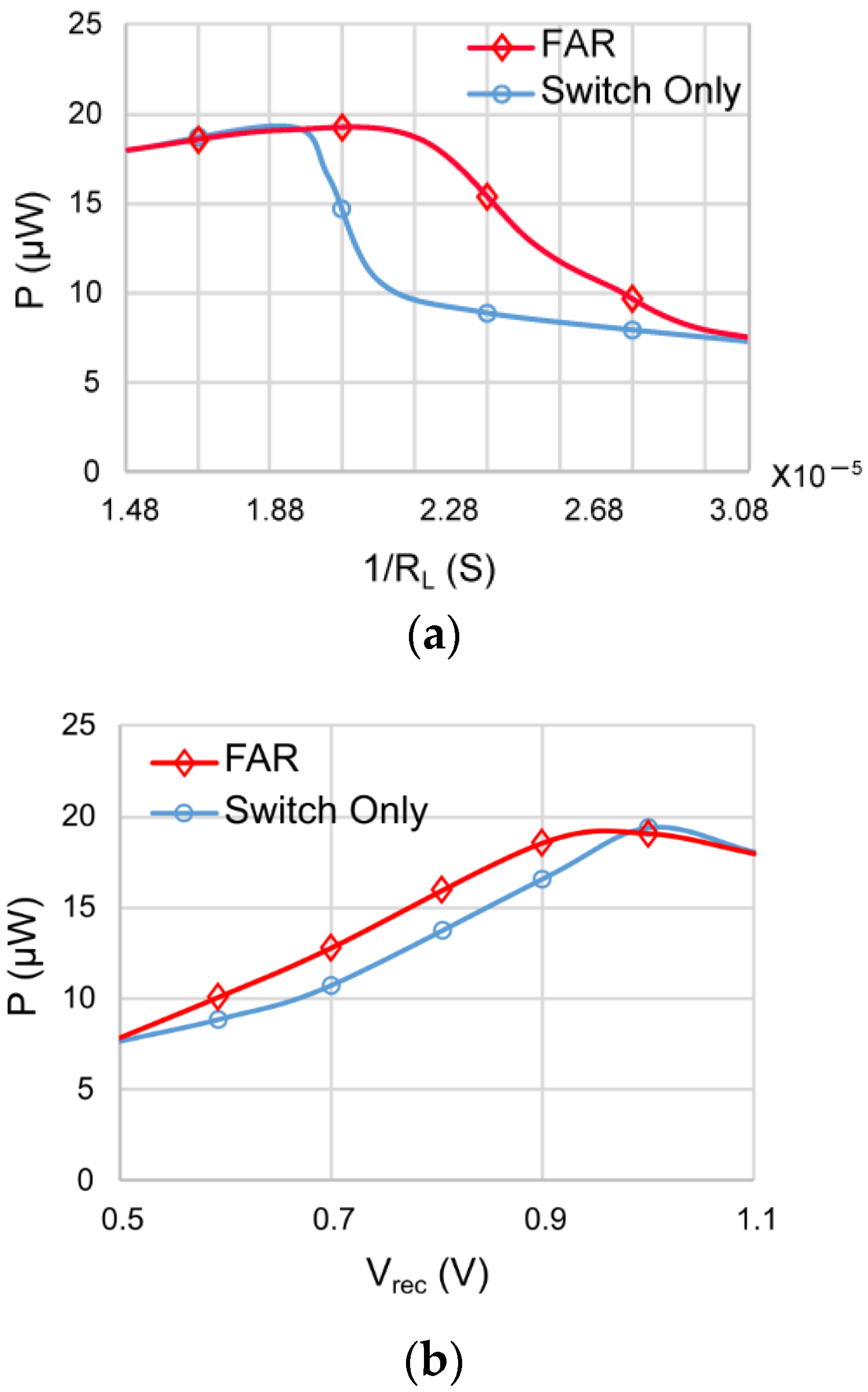

Figure 9 shows the numerical simulations of both architectures with

k

and the same initial conditions as above. We noticed that

stabilized around 3 mV below

.

For power, FAR was also more efficient than Switch-only once

had been stabilized.

Figure 10 shows the average power difference

between FAR and Switch-only. It is worth noticing that at

s, i.e., before and shortly after applying

, Switch-only achieved slightly better power performance than FAR (

). This was due to the fact that without

, the FAR principle yielded lower average values of

. However, energy harvesting systems are not just meant to charge a storage device; they are intrinsically designed to supply energy to a load. Therefore, as shown here in the FAR implementation, there was a benefit in using voltage flip enhancement to improve power performance.

Furthermore, we believe that combining the voltage flip enhancement principle to SSHI or SSHC might contribute to further improve the power performance under load constraint. But for the time being, this statement is based on theoretical assumptions and needs to be further investigated.