A Pipelined Noise-Shaping SAR ADC Using Ring Amplifier

Abstract

1. Introduction

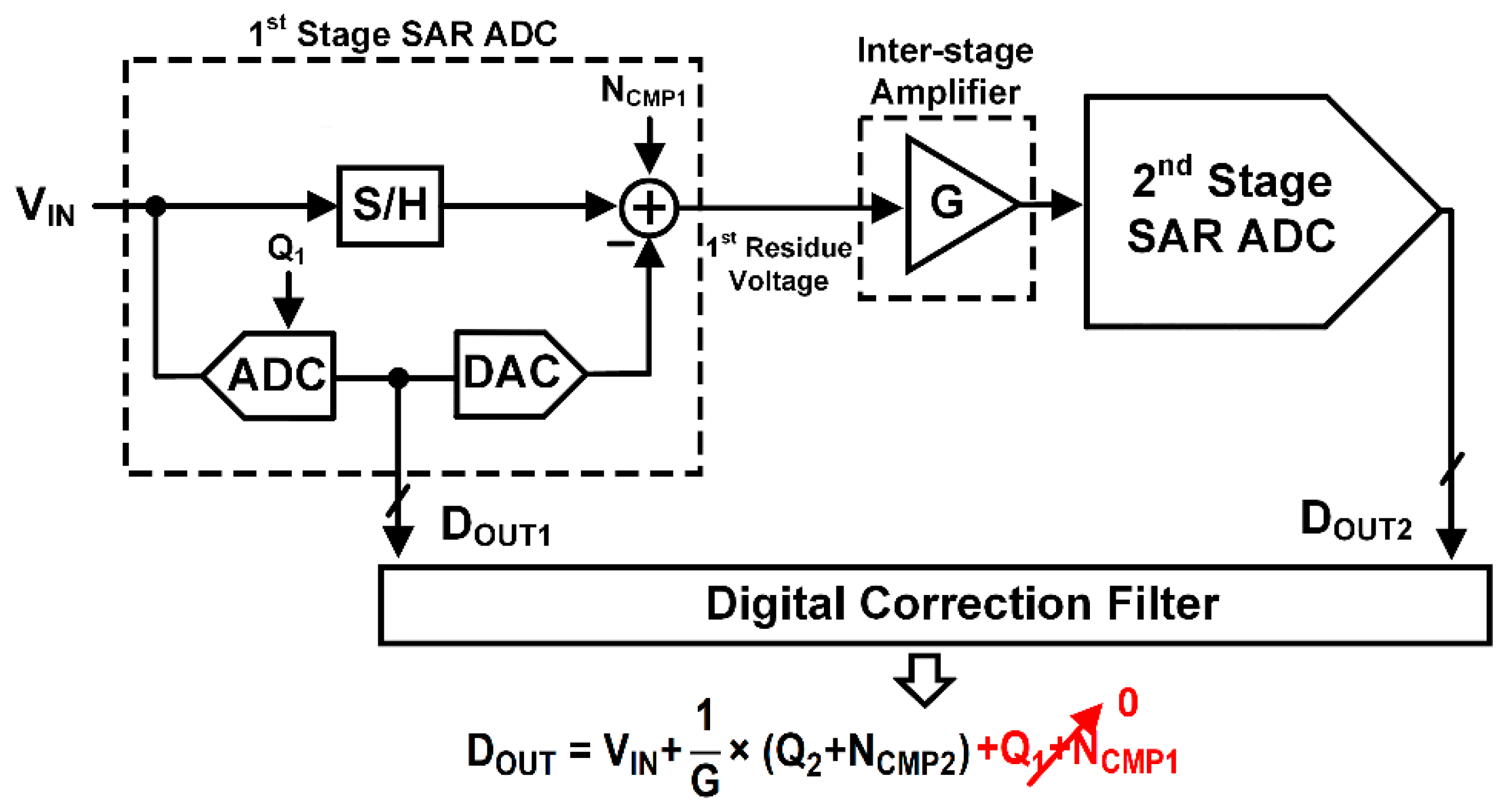

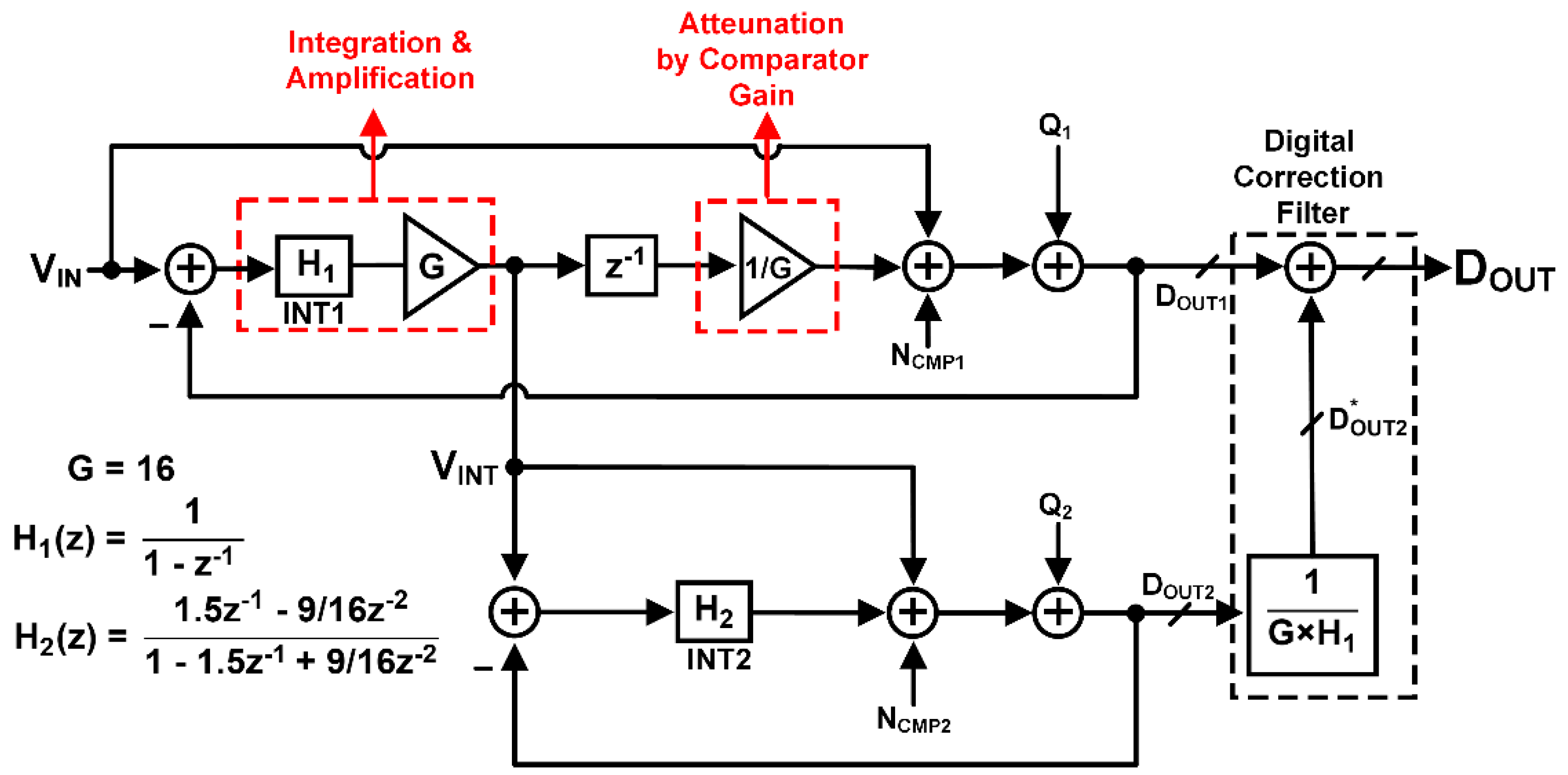

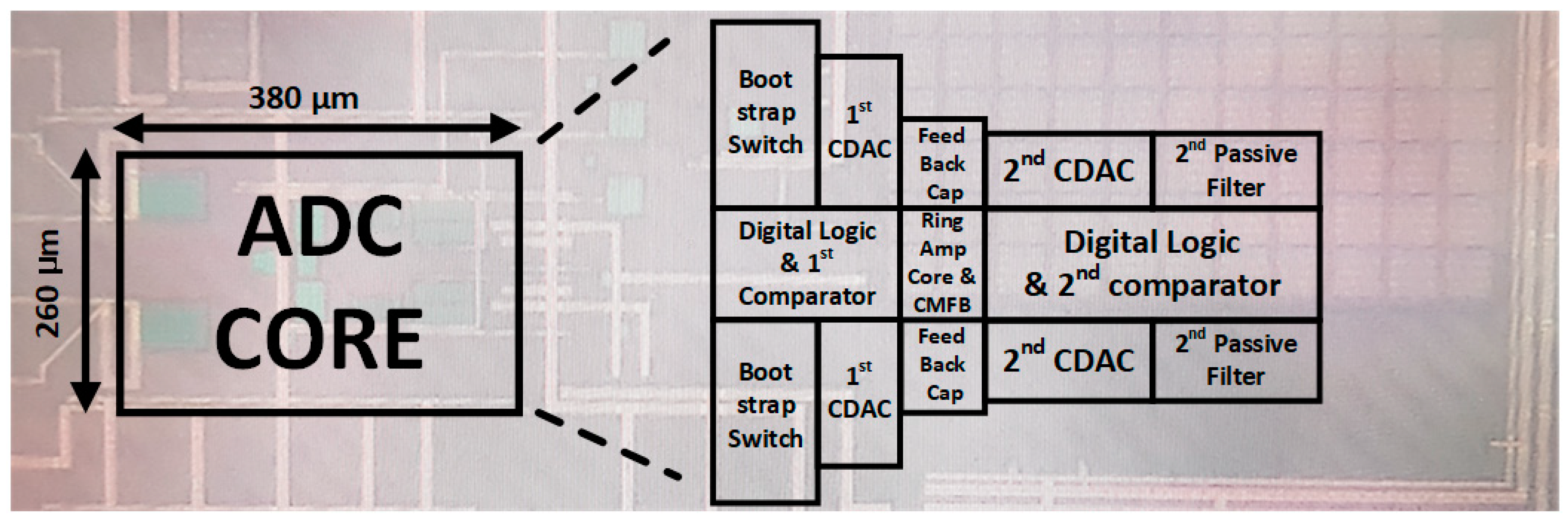

2. Architecture

2.1. Pipelined Noise-Shaping SAR ADC

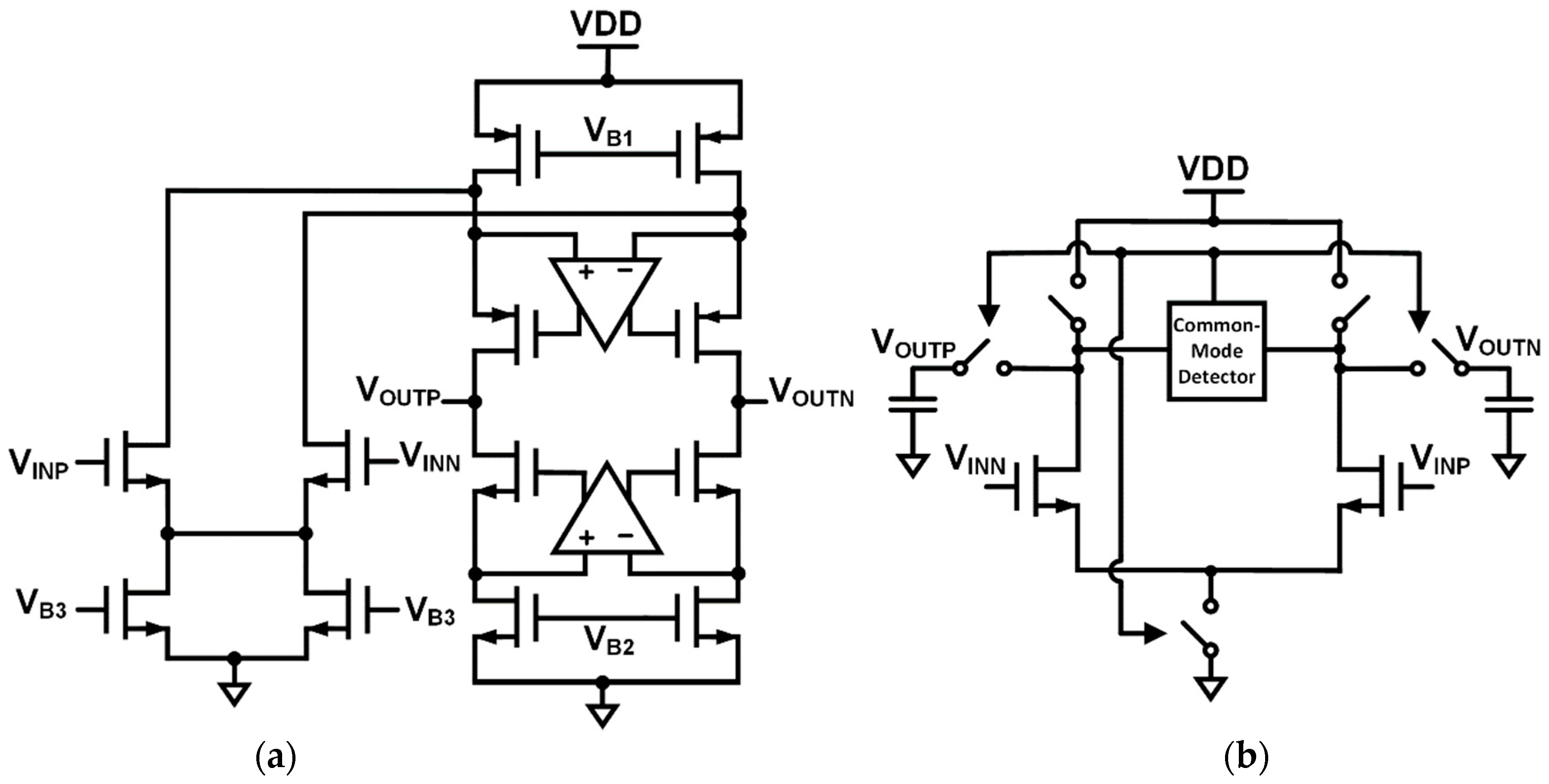

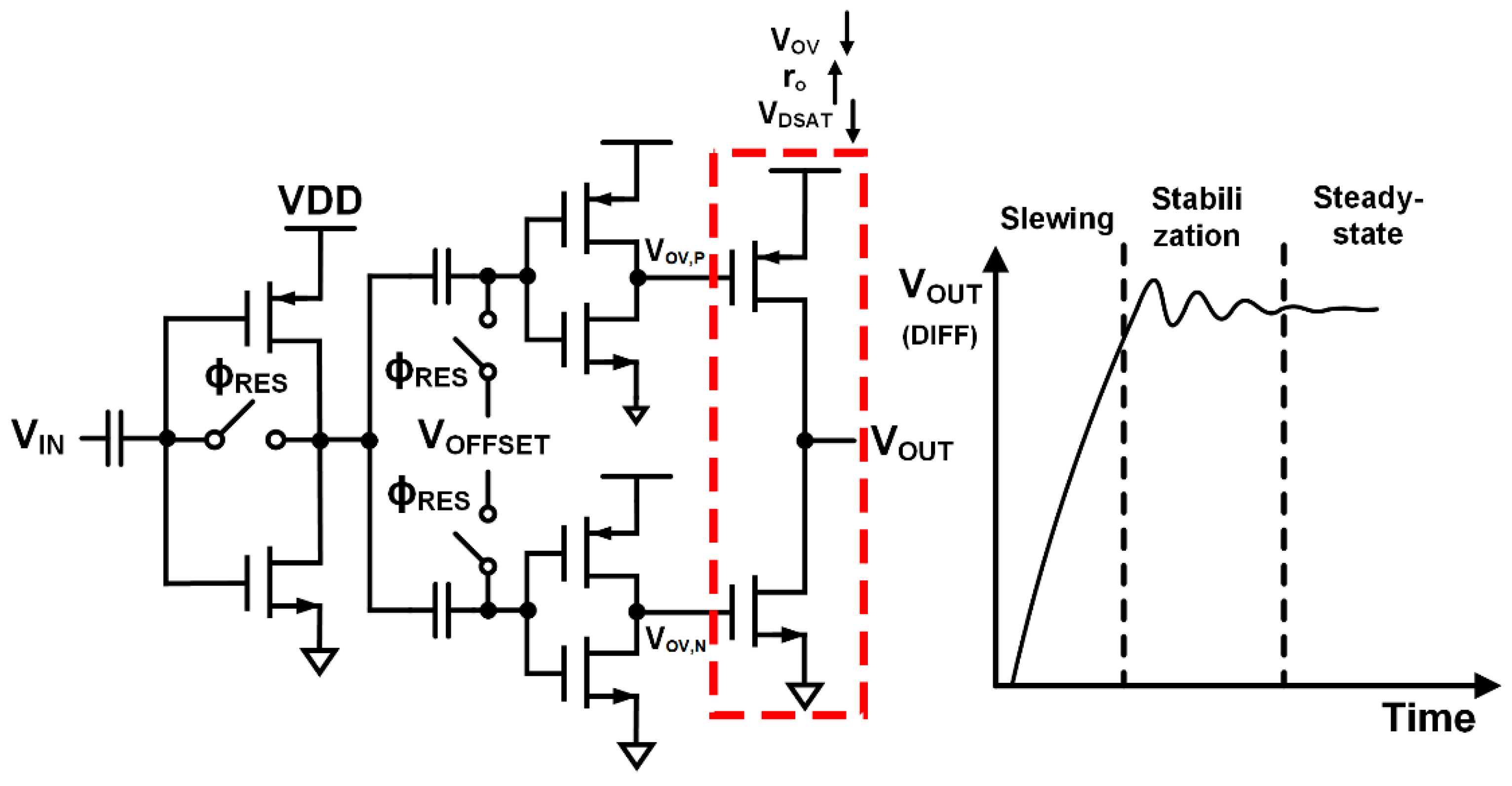

2.2. Ring Amplifier

3. Circuit Implementation

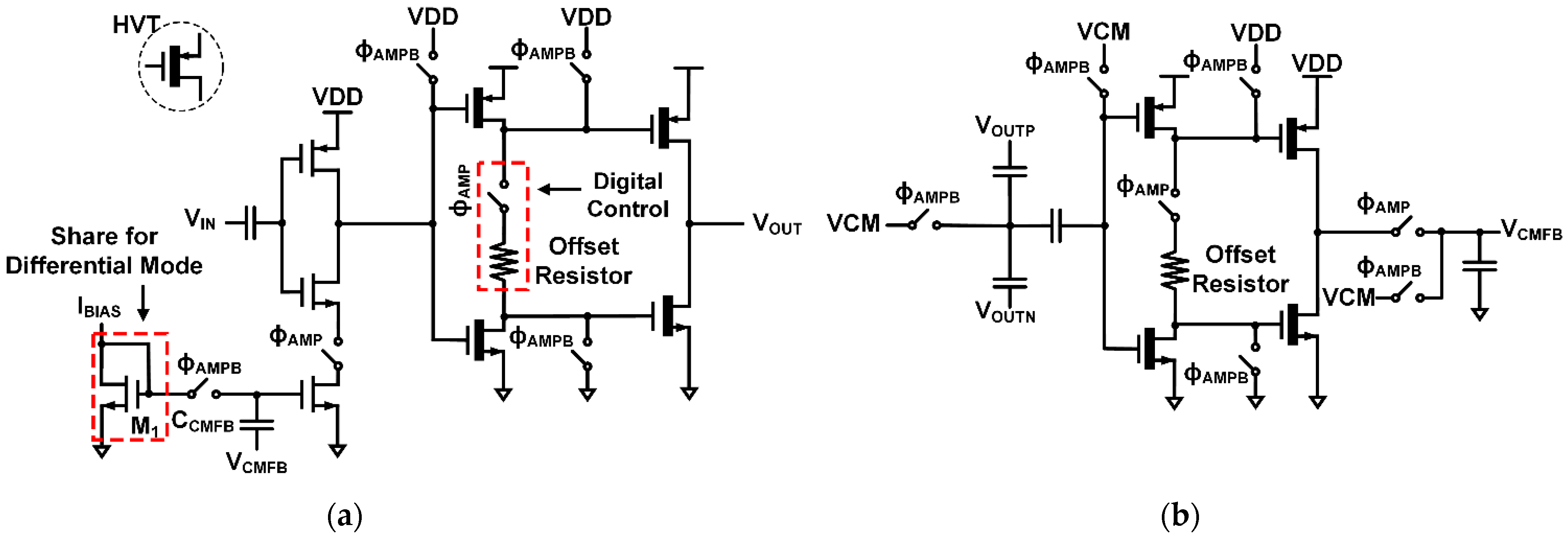

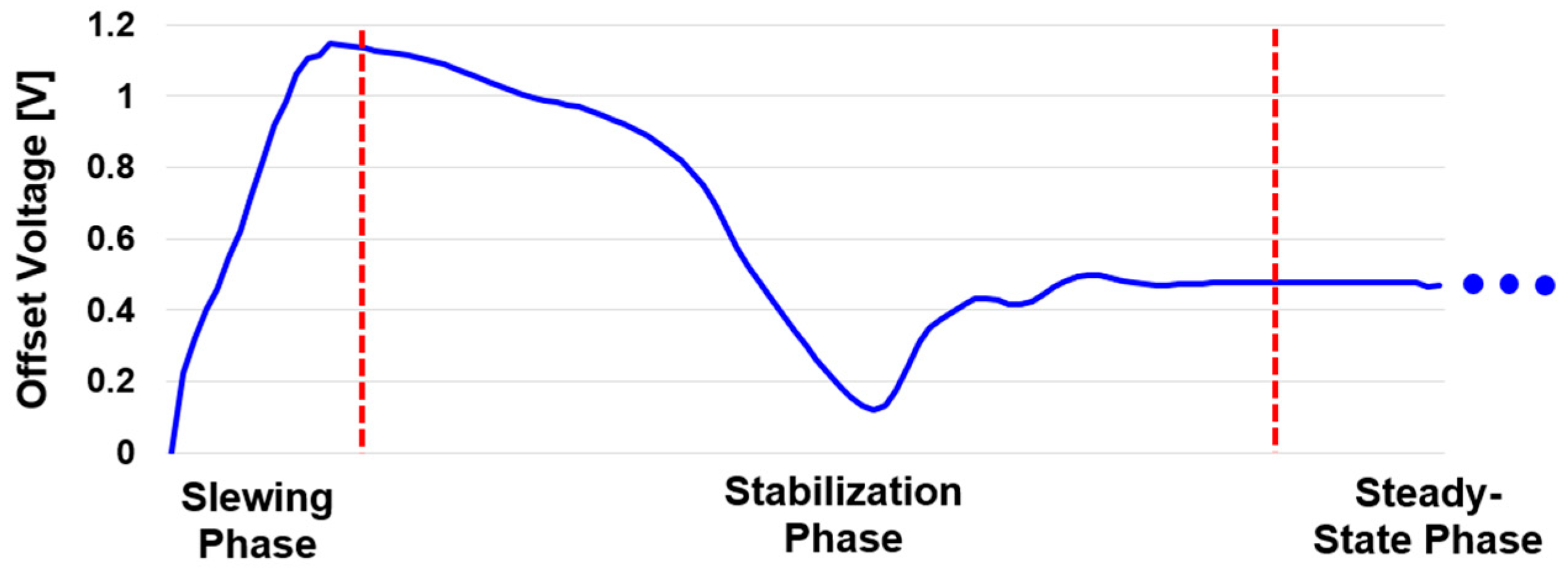

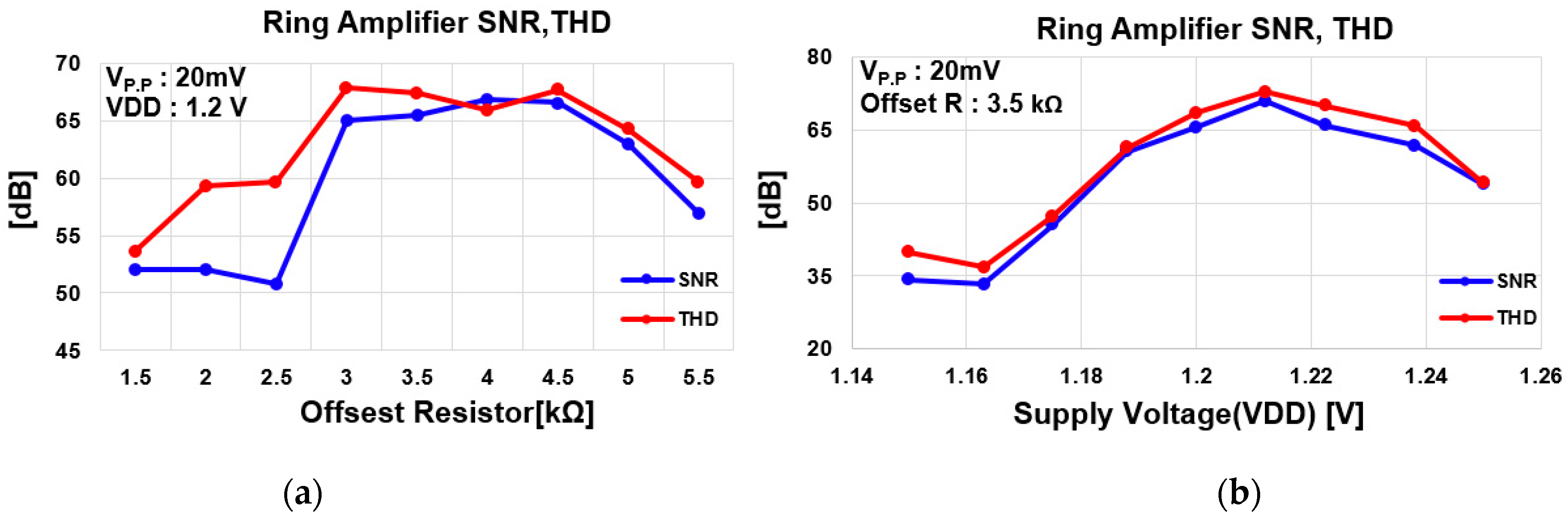

3.1. Ring Amplifier-Based Loop Filter

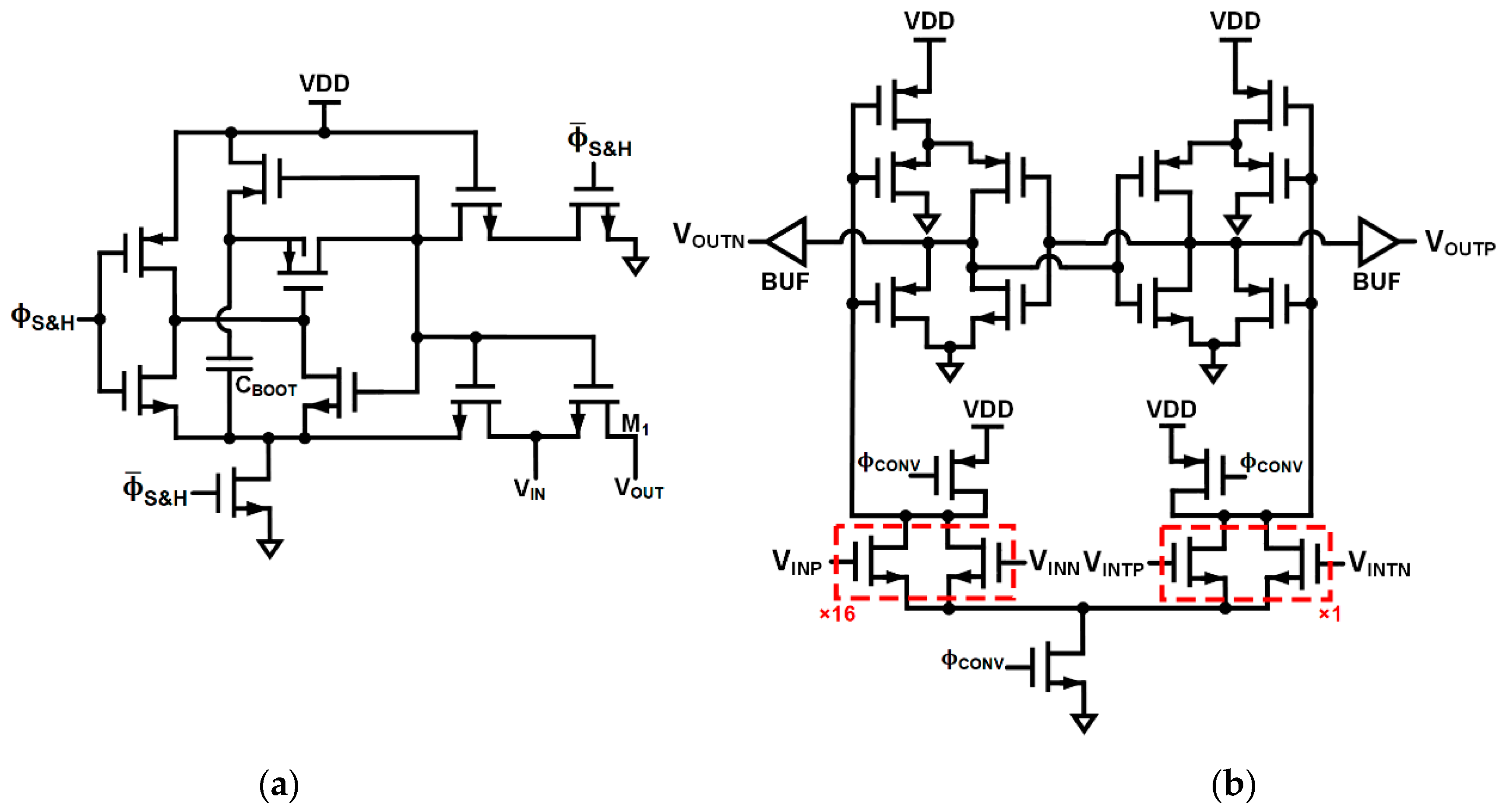

3.2. Ring Amplifier-Based Pipelined Noise-Shaping SAR ADC

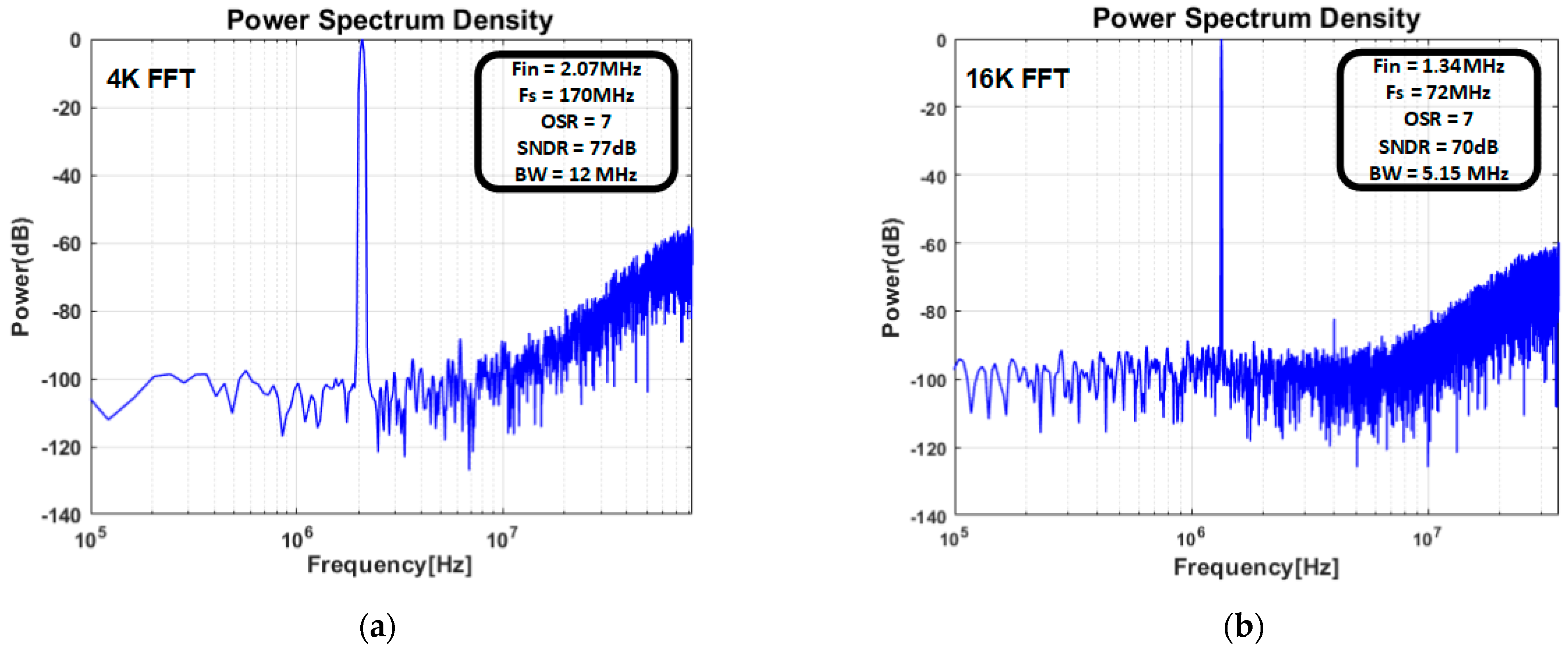

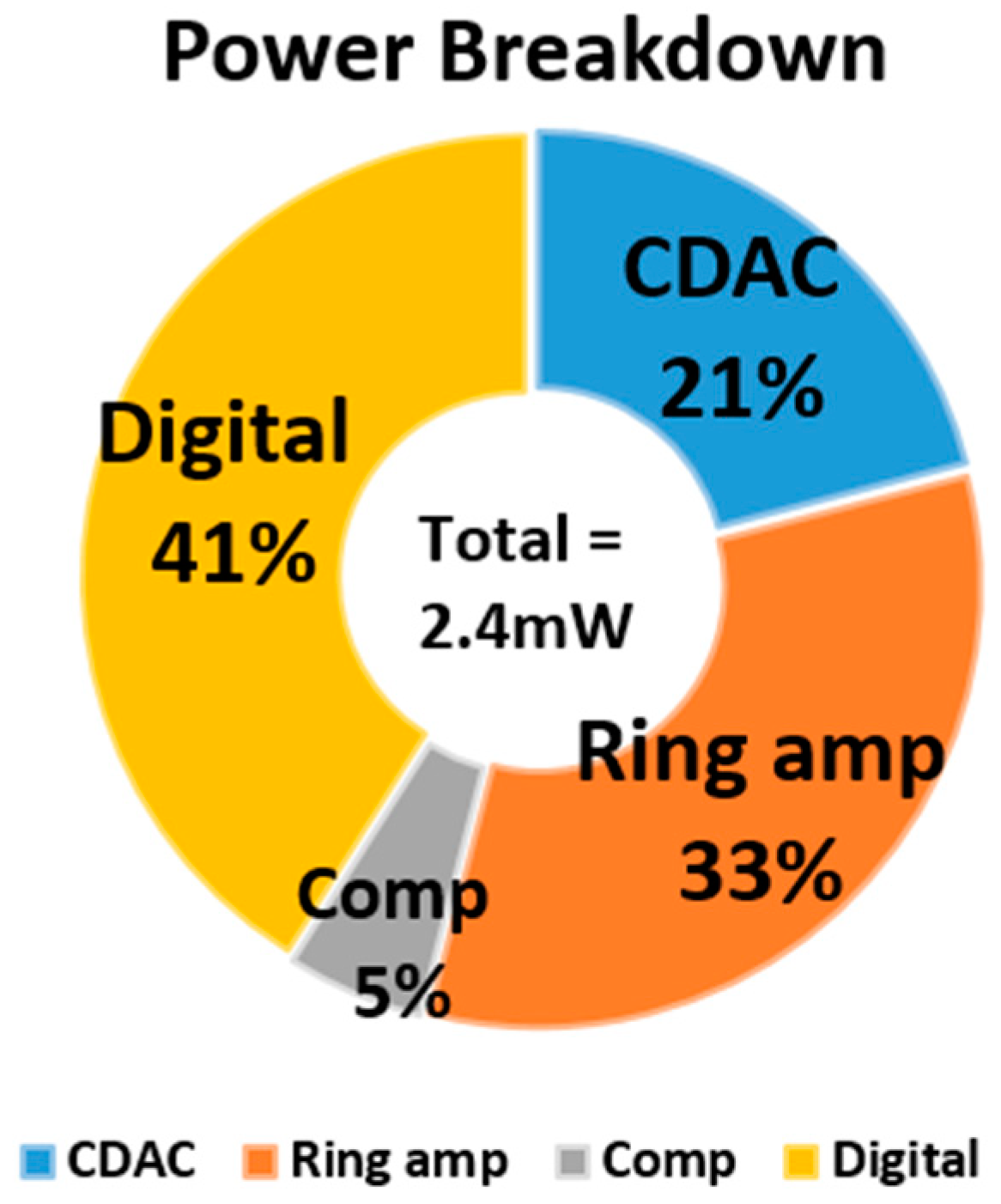

4. Results

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Ron, K.; Shen, J.; Decker, S.; Li, H.; Ibaragi, E.; Zhu, H. A 14 b 80 MS/s SAR ADC with 73.6 DB SNDR in 65 nm CMOS. IEEE J. Solid State Circuits 2013, 48, 3059–3066. [Google Scholar]

- Lee, K.; Miller, R.M.; Temes, C.G. An 8.1 mW, 82 dB delta-sigma ADC with 1.9 MHz BW and −98 dB THD. IEEE J. Solid State Circuits 2009, 44, 2202–2211. [Google Scholar] [CrossRef]

- Chandrakasan, P.A.; Verma, N. An ultra low energy 12-bit rate-resolution scalable SAR ADC for wireless sensor nodes. IEEE J. Solid State Circuits 2009, 42, 1196–1205. [Google Scholar]

- Maddox, M.; Chen, B.; Coln, M.; Kapusta, R.; Shen, J.; Fernando, L. A 16 bit linear passive-charge-sharing SAR ADC in 55 nm CMOS. In Proceedings of the IEEE Asian Solid-State Circuits Conference, Toyama, Japan, 7–9 November 2016. [Google Scholar]

- Flynn, P.M.; Lee, C. A SAR-assisted two-stage pipeline ADC. IEEE J. Solid State Circuits 2011, 46, 859–869. [Google Scholar]

- Liu, Q.; Shu, W.; Chang, J. A 1-GS/s 11-Bit SAR-assisted pipeline ADC with 59-dB SNDR in 65-nm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 1164–1168. [Google Scholar] [CrossRef]

- Yang, C.; Li, F.; Li, W.; Wang, X.; Wang, Z. An 85 mW 14-bit 150 MS/s pipelined ADC with 71.3 dB peak SNDR in 130nm CMOS. In Proceedings of the IEEE Asian Solid-State Circuits Conference, Singapore, 11–13 November 2013. [Google Scholar]

- Verbruggen, B.; Iriguchi, M.; Craninckx, J. A 1.7 mW 11 b 250 MS/s 2× interleaved fully dynamic pipelined SAR ADC in 40nm digital CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2012. [Google Scholar]

- Lee, C.; Venkatachala, P.; ElSHater, A.; Xiao, B.; Hu, H.; Moon, U. Cascoded ring amplifiers for high speed and high accuracy settling. In Proceedings of the IEEE International Symposium on Circuits and Systems, Sapporo, Japan, 26–29 May 2019. [Google Scholar]

- Verbriggen, B.; Deguchi, K.; Malki, B.; Craninckx, J. A 70 dB SNDR 200 MS/s 2.3 mW dynamic pipelined SAR ADC in 28nm digital CMOS. In Proceedings of the Symposium on VLSI Circuits Digest of Technical Papers, Honolulu, HI, USA, 10–13 June 2014. [Google Scholar]

- Tripathi, V.; Murmann, B. A 160 MS/s, 11.1 mW, single-channel pipelined SAR ADC with 68.3 dB SNDR. In Proceedings of the IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 15–17 September 2014. [Google Scholar]

- Liu, H.; Liu, M.; Zhu, Z. A 12-bit 200MS/s Pipelined-SAR ADC in 65-nm CMOS with 61.9 dB SNDR. In Proceedings of the IEEE International Conference on Electron Devices and Solid-State Circuits, Xi’an, China, 12–14 June 2019. [Google Scholar]

- Chen, Y.; Wang, J.; Hu, H.; Ye, F.; Ren, J. A 200 MS/s, 11 bit SAR-assisted pipeline ADC with bias-enhanced ring amplifier. In Proceedings of the IEEE International Symposium on Circuits and Systems, Baltimore, MD, USA, 28–31 May 2017. [Google Scholar]

- Frendenburg, J.; Flynn, M. A 90-MS/s 11-MHz-bandwidth 62-dB SNDR noise-shaping SAR ADC. IEEE J. Solid State Circuits 2012, 47, 2898–2904. [Google Scholar] [CrossRef]

- Liu, C.; Huang, M. 28.1 A 0.46 mW 5 MHz-BW 79.7 dB-SNDR noise-shaping SAR ADC with dynamic-amplifier-based FIR-IIR filter. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 5–9 February 2017. [Google Scholar]

- Oh, S.; Oh, Y.; Lee, J.; Kim, K.; Lee, S.; Kim, J.; Chae, H. A 80 dB DR 6 MHz bandwidth pipelined noise-shaping SAR ADC with 1–2 MASH structure. In Proceedings of the IEEE Custom Integrted Circuits Conference, Boston, MA, USA, 22–25 March 2020. [Google Scholar]

- Oh, S.; Oh, Y.; Lee, J.; Kim, K.; Lee, S.; Kim, J.; Chae, H. A 85 dB DR 4 MHz BW pipelined noise-shaping SAR ADC with 1-2 MASH structure. IEEE J. Solid State Circuits 2021, 1. [Google Scholar] [CrossRef]

- Gao, B.; Li, X.; Yan, C.; Wu, J. Active noise shaping SAR ADC based on ISDM with the 5MHz bandwidth. In Proceedings of the IEEE International Symposium on Circuits and Systems, Seville, Spain, 12–14 October 2020. [Google Scholar]

- Chen, Z.; Miyahara, M.; Matsuzawa, A. A 2nd order fully-passive noise-shaping SAR ADC with embedded passive gain. In Proceedings of the IEEE Asian Solid-State Circuits Conference, Toyama, Japan, 7–9 November 2016. [Google Scholar]

- Chen, Z.; Miyahara, M.; Matsuzawa, A. A 9.35-ENOB, 14.8 fJ/conv.-step fully-passive noise-shaping SAR ADC. In Proceedings of the IEEE Symposium on VLSI Circuits, Kyoto, Japan, 17–19 June 2015. [Google Scholar]

- Maghami, H.; Payandehnia, P.; Mirzaie, H.; Mayaram, K.; Zanbaghi, R.; Fiez, T. A highly linear OTA-free VCO-based 1-1 MASH ΔΣ ADC. In Proceedings of the IEEE International Symposium on Circuits and Systems, Baltimore, MD, USA, 28–31 May 2017. [Google Scholar]

- Zhang, S.; Zhu, Z.; Zhang, H.; Xiong, Z.; Li, Q. A 90-dB DC gain high-speed nested gain-boosted folded-cascode opamp. In Proceedings of the 11th Conference on Ph.D. Research in Microelectronics and Electronics, Glasgow, UK, 29 June–2 July 2015. [Google Scholar]

- Rahim, S.; Azmi, I. A CMOS single stage fully differential folded cascode amplifier employing gain boosting technique. In Proceedings of the International Symposium on Integrated Circuits, Singapore, 12–14 December 2011. [Google Scholar]

- Park, Y.; Song, J.; Choi, Y.; Lim, C.; Ahn, S.; Kim, C. An 11-b 100-MS/s fully dynamic pipelined ADC using a high-linearity dynamic amplifier. IEEE J. Solid State Circuits 2020, 55, 2468–2477. [Google Scholar] [CrossRef]

- Malki, B.; Verbruggen, B.; Wambacq, P.; Deguchi, K.; Iriguchi, M.; Craninckx, J. A complementary dynamic residue amplifier for a 67 dB SNDR 1.36 mW 170 MS/s pipelined SAR ADC. In Proceedings of the 40th European Solid State Circuits Conference, Venice Lido, Italy, 22–26 September 2014. [Google Scholar]

- Sehgal, R.; Goes, F.; Bult, K. A 13-mW 64-dB SNDR 280-MS/s pipelined ADC using linearized integrating amplifiers. IEEE J. Solid State Circuits 2018, 53, 1878–1888. [Google Scholar] [CrossRef]

- Hershberg, B.; Weaver, S.; Sobue, K.; Takeuchi, S.; Hamashita, K.; Moon, U. Ring amplifiers for switched-capacitor circuits. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2012. [Google Scholar]

- Lim, Y.; Flynn, M. 11.5 A 100 MS/s 10.5 b 2.46 mW comparator-less pipeline ADC using self-biased ring amplifiers. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Paper, San Francisco, CA, USA, 9–13 February 2014. [Google Scholar]

- Lagos, J.; Hershberg, B.; Martens, E.; Wambacq, P.; Craninckx, J. A single-channel, 600 Msps, 12 bit, ringamp-based pipelined ADC in 28 nm CMOS. In Proceedings of the Symposium on VLSI Circuits, Kyoto, Japan, 5–8 June 2017. [Google Scholar]

- Hershberg, B.; Dermit, D.; Liempd, B.; Martens, E.; Markulic, N.; Lagos, J.; Craninckx, J. A 3.2 GS/s 10 ENOB 61mW ringamp ADC in 16 nm with background monitoring of distortion. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 17–21 February 2019. [Google Scholar]

- Liu, C.; Chang, S.; Huang, G.; Lin, Y. A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J. Solid State Circuits 2010, 45, 731–740. [Google Scholar] [CrossRef]

- Aksin, D.; Al-Shyoukh, M.; Maloberti, F. Switch bootstrapping for precise sampling beyond supply voltage. IEEE J. Solid State Circuits 2006, 41, 1938–1943. [Google Scholar] [CrossRef][Green Version]

- Chiu, P.; Zimmer, B.; Nikolić, B. A double-tail sense amplifier for low-voltage SRAM in 28 nm technology. In Proceedings of the IEEE Asian Solid-Stage Circuits Conference, Toyama, Japan, 7–9 November 2016. [Google Scholar]

- Miyahara, M.; Asada, Y.; Paik, D.; Matsuzawa, A. A low-noise self-calibrating dynamic comparator for high-speed ADCs. In Proceedings of the IEEE Asian Solid-Stage Circuits Conference, Fukuoka, Japan, 3–5 November 2008. [Google Scholar]

- Babayan-M, S.; Lotfi, R. Analysis and design of a low-voltage low-power double-tail comparator. IEEE Trans. Very Large Scale Integr. Syst. 2014, 22, 343–352. [Google Scholar] [CrossRef]

- Liu, J.; Li, S.; Guo, W.; Wen, G.; Sun, N. A 0.0029 mm2 17 fJ/conversion-step third-order CT ΔΣ ADC with a single OTA and second-order noise-shaping SAR quantizer. IEEE J. Solid State Circuits 2019, 54, 428–440. [Google Scholar] [CrossRef]

| Reference | VLSI’14 [10] | CICC’14 [11] | EDSSC’19 [12] | ISCAS’17 [13] |

|---|---|---|---|---|

| Technology | 28 nm CMOS | 65 nm CMOS | 65 nm CMOS | 40 nm CMOS |

| ADC Type | Pipeline-SAR | Pipeline-SAR | Pipeline-SAR | Pipelined |

| Signal to Noise and Distortion Ratio (SNDR) [dB] | 70 | 68.3 | 61.9 | 58 |

| Sampling Rate (Fs) [Ms/s] | 200 | 160 | 200 | 200 |

| Power [mW] | 2.3 | 11.1 | 7.3 | 2.28 |

| Amplifier Calibration | Yes | No | No | No |

| Amplifier Type | Dynamic | Open-loop 2-stage | Cascade | Ring |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, J.; Lee, S.; Kim, K.; Chae, H. A Pipelined Noise-Shaping SAR ADC Using Ring Amplifier. Electronics 2021, 10, 1968. https://doi.org/10.3390/electronics10161968

Lee J, Lee S, Kim K, Chae H. A Pipelined Noise-Shaping SAR ADC Using Ring Amplifier. Electronics. 2021; 10(16):1968. https://doi.org/10.3390/electronics10161968

Chicago/Turabian StyleLee, Juyong, Seungjun Lee, Kihyun Kim, and Hyungil Chae. 2021. "A Pipelined Noise-Shaping SAR ADC Using Ring Amplifier" Electronics 10, no. 16: 1968. https://doi.org/10.3390/electronics10161968

APA StyleLee, J., Lee, S., Kim, K., & Chae, H. (2021). A Pipelined Noise-Shaping SAR ADC Using Ring Amplifier. Electronics, 10(16), 1968. https://doi.org/10.3390/electronics10161968