A Single-Amplifier Dual-Residue Pipelined-SAR ADC

Abstract

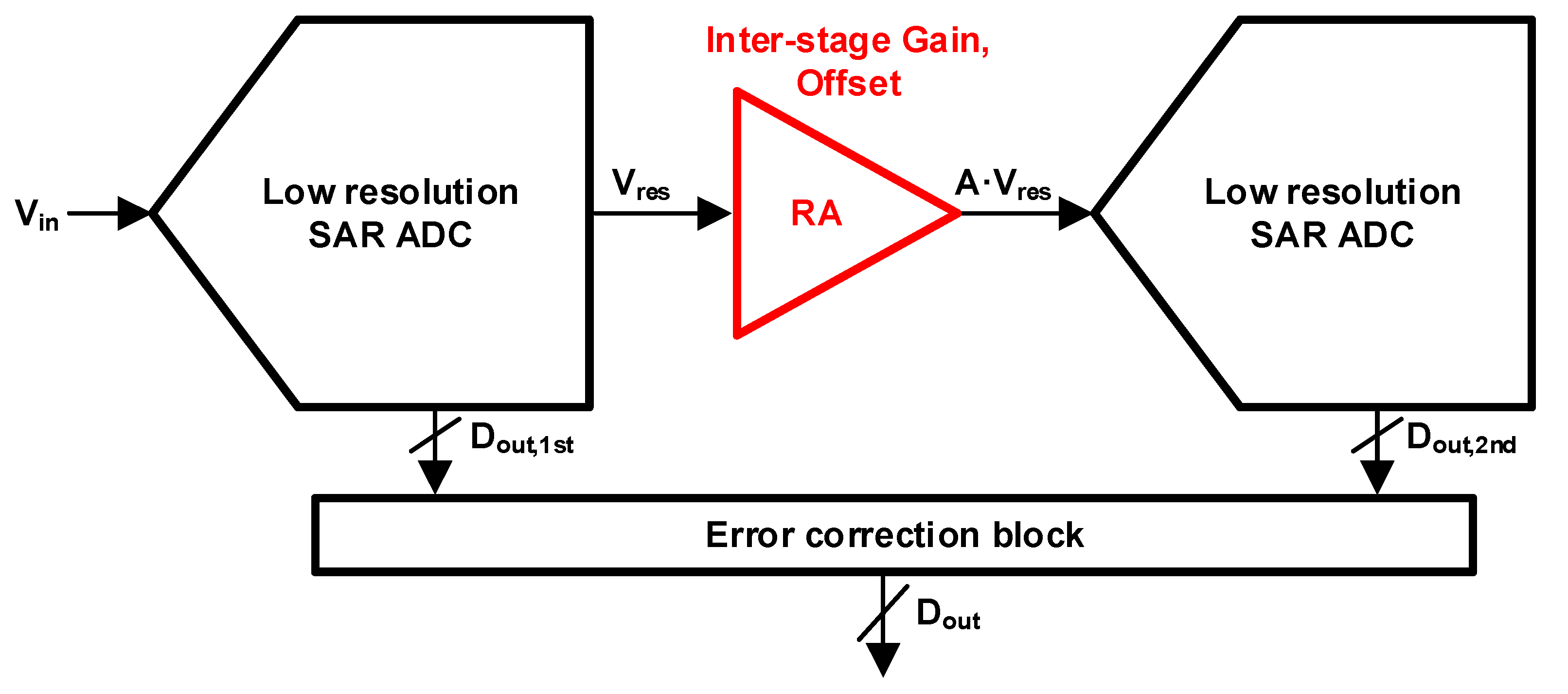

1. Introduction

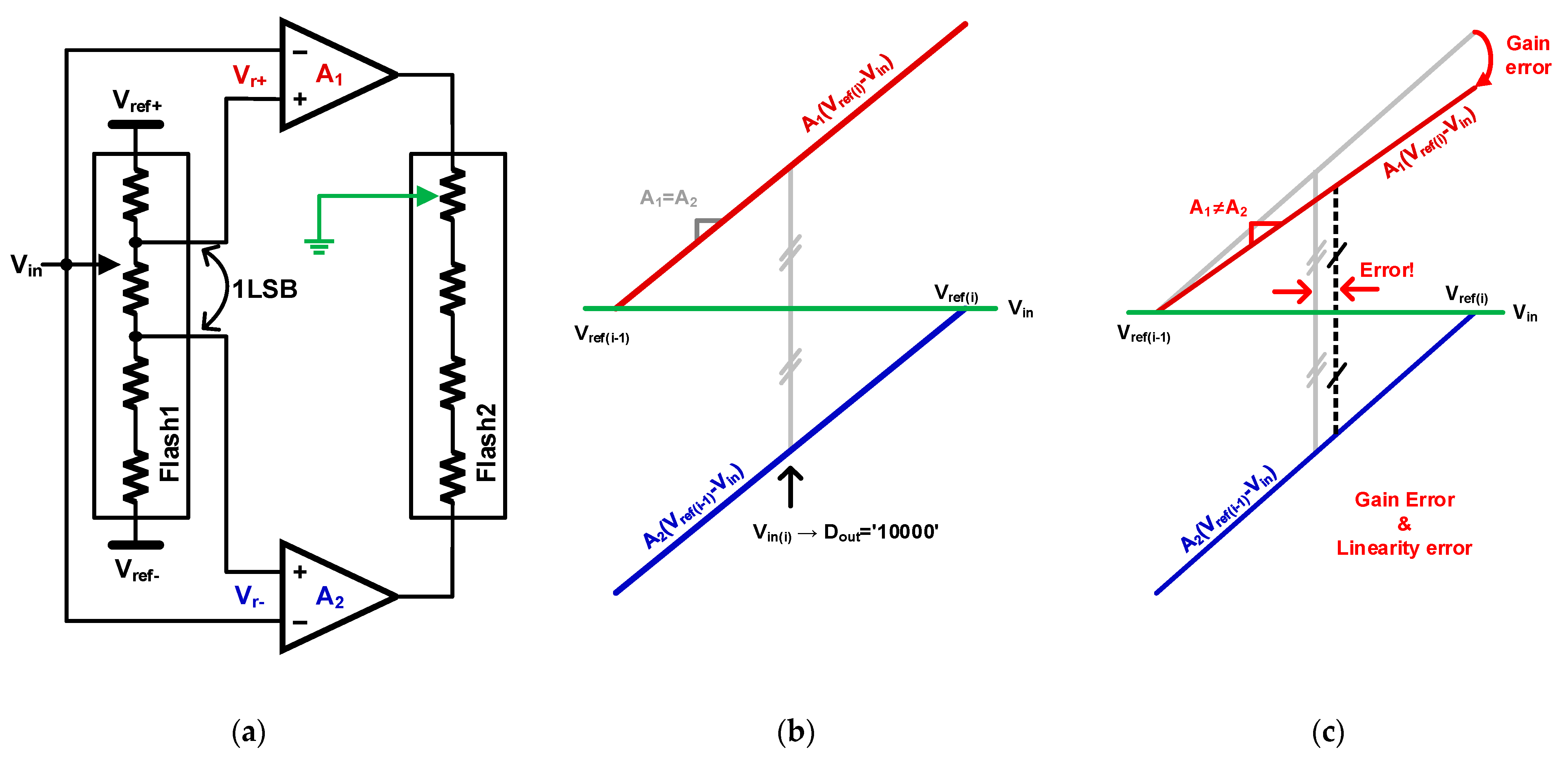

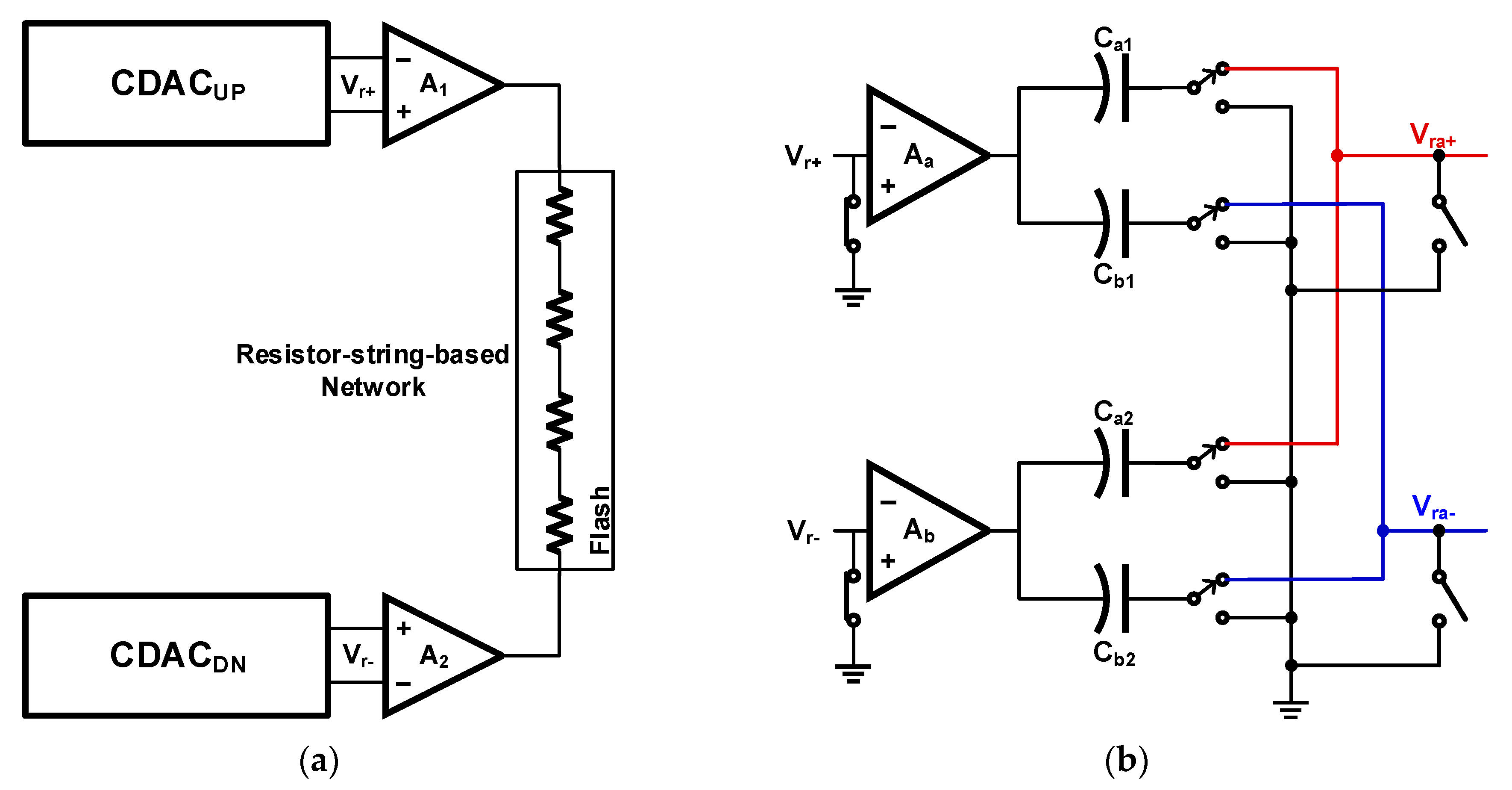

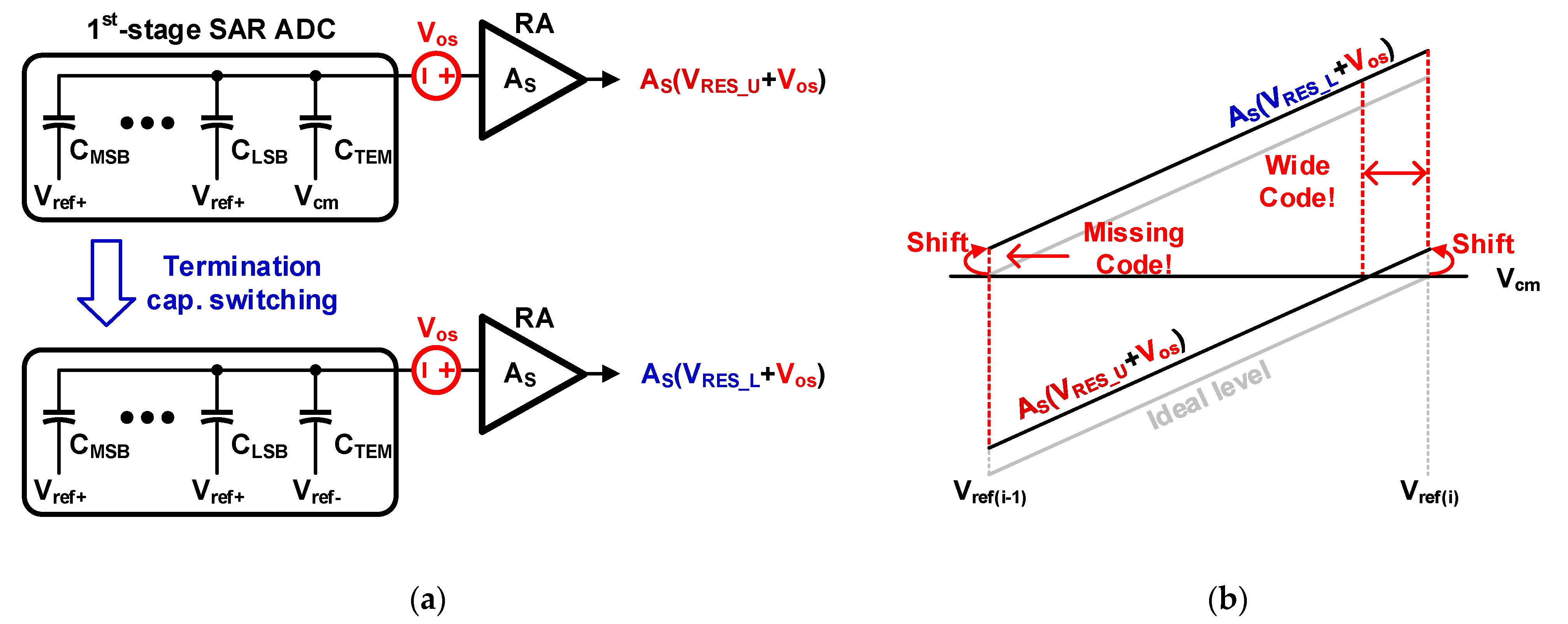

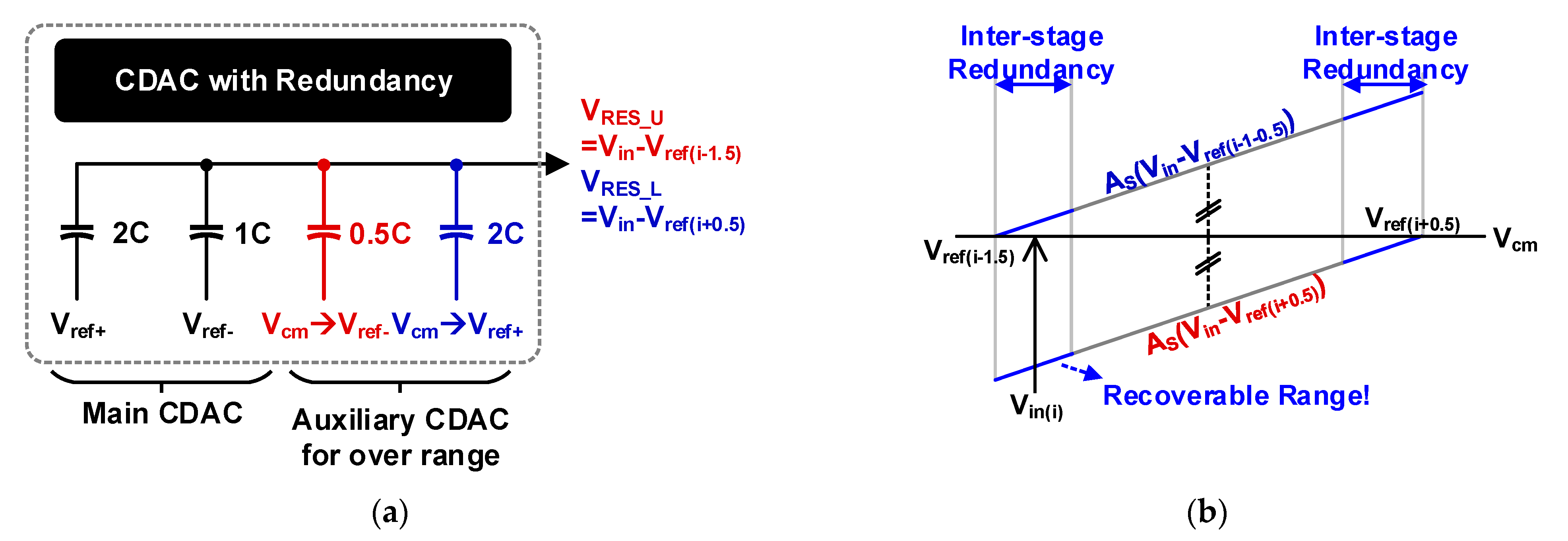

2. Review of Dual-Residue Processing Concept

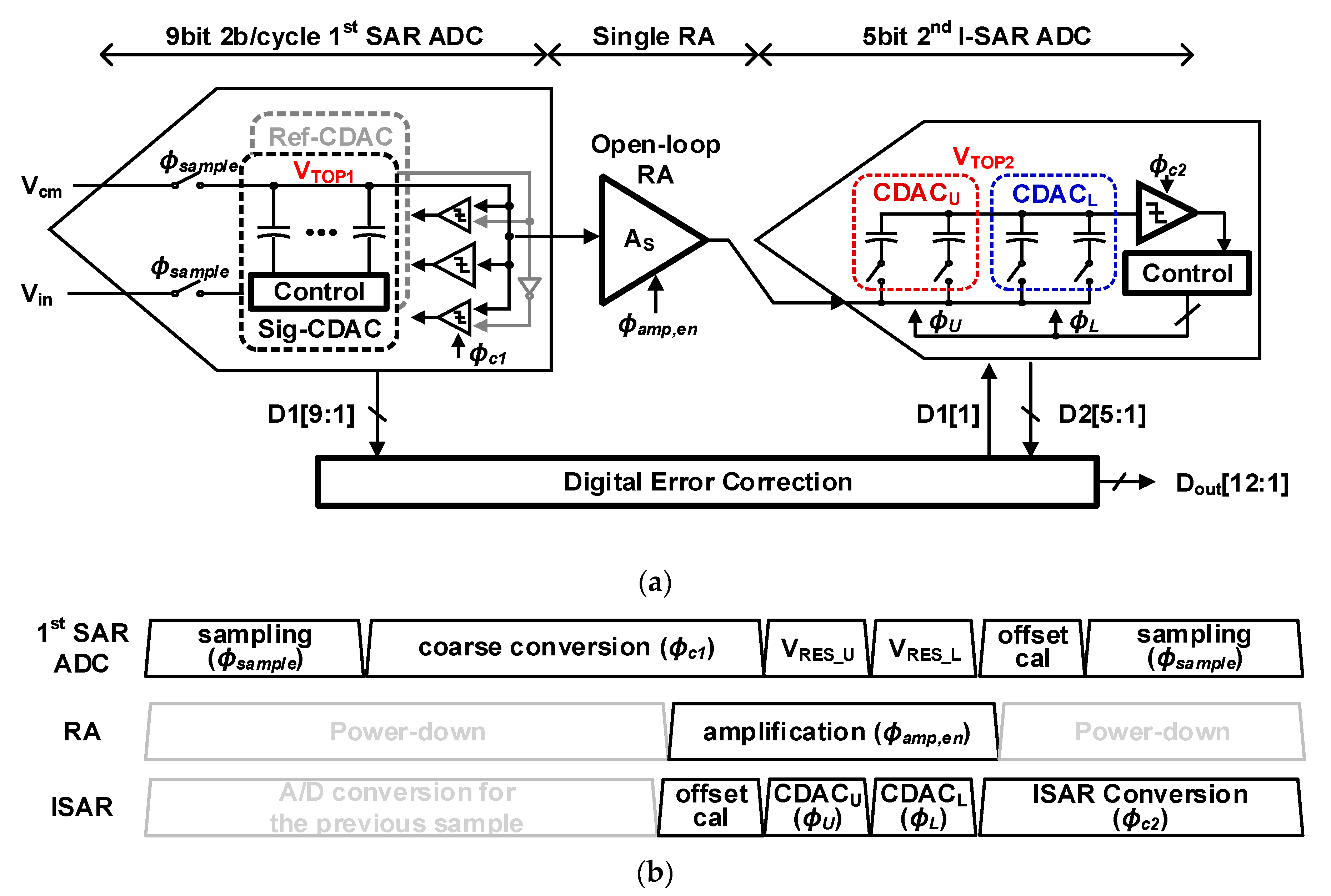

3. Proposed Architecture

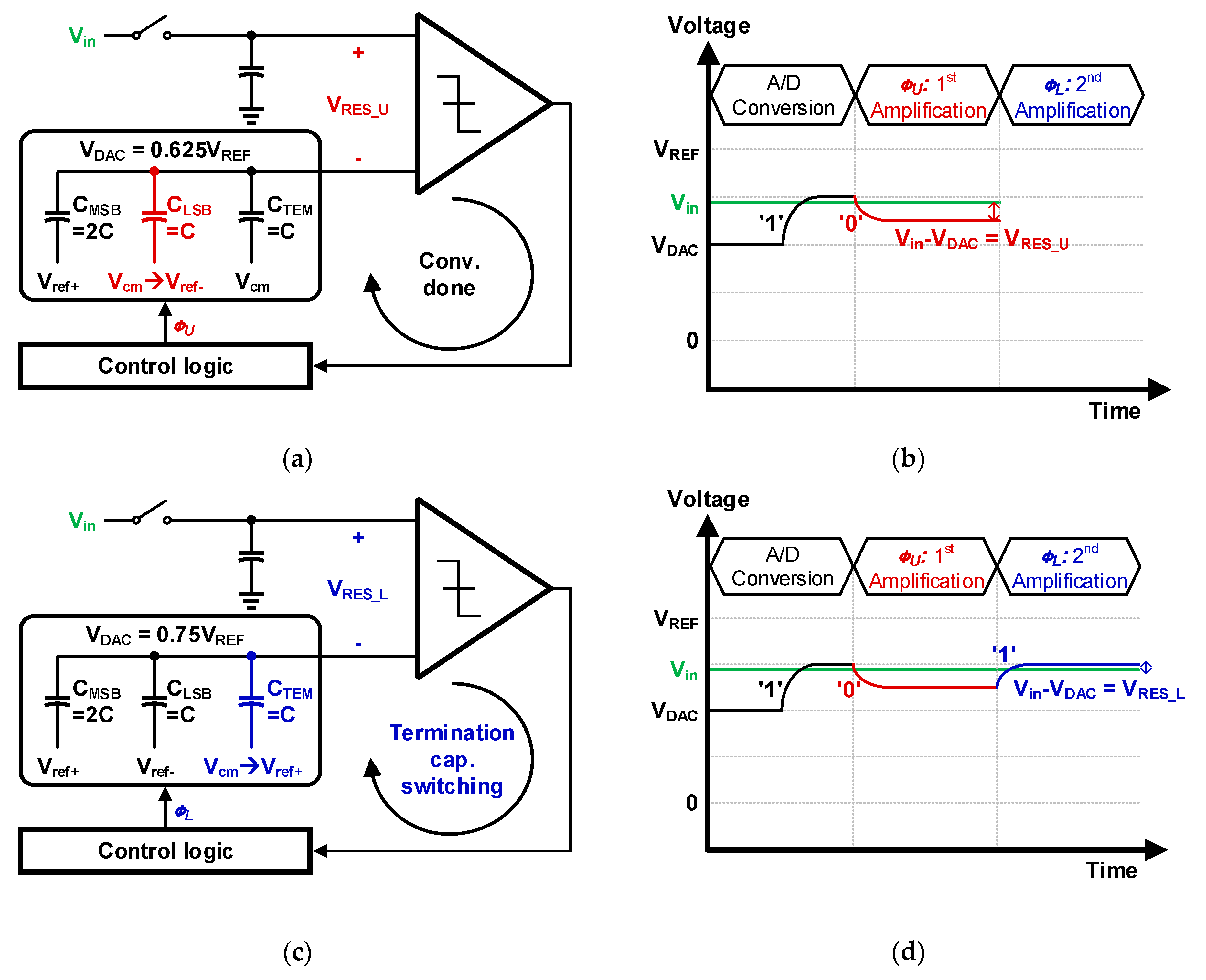

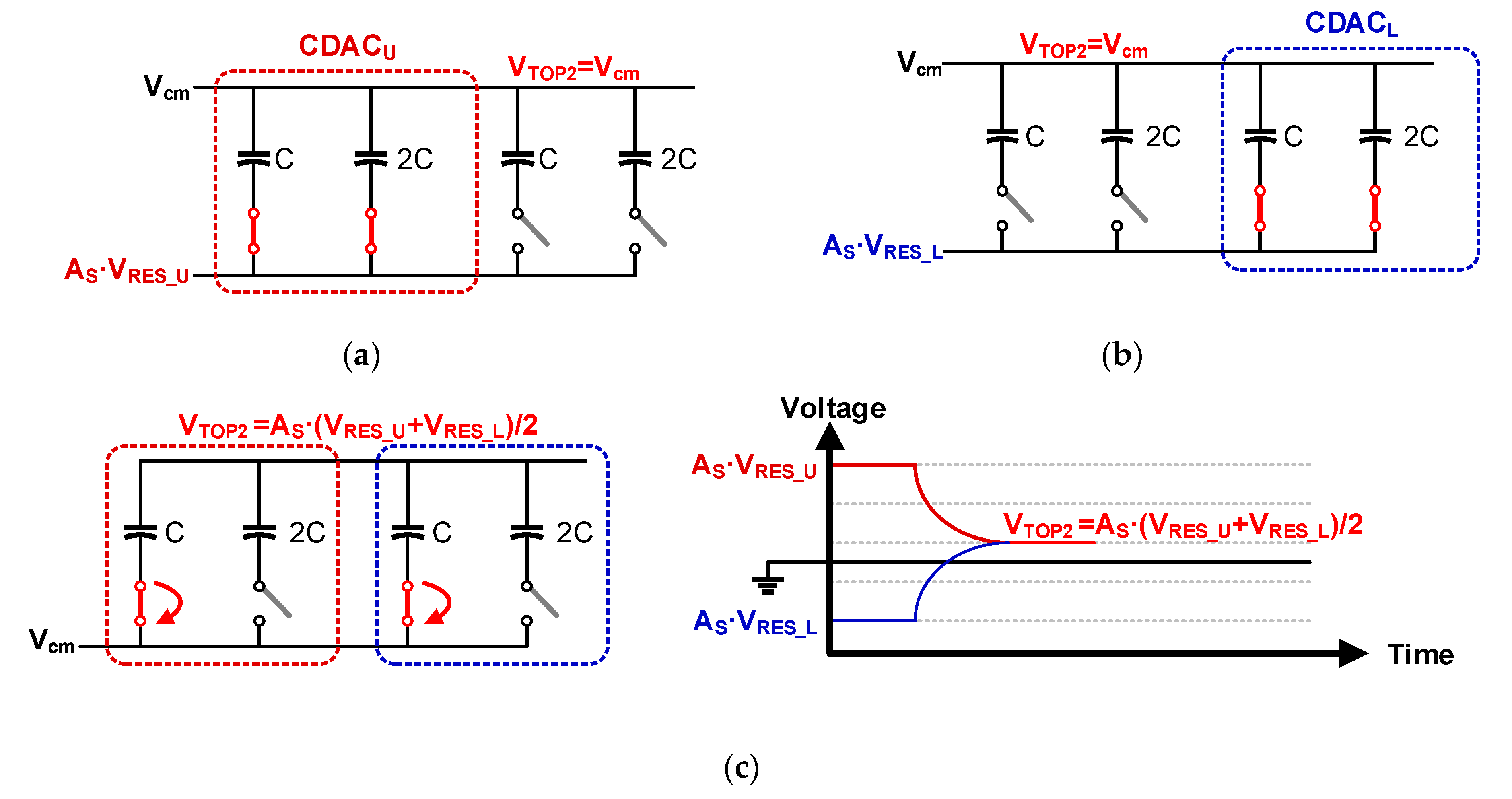

3.1. Dual-Residue Generation with a Single Amplifier

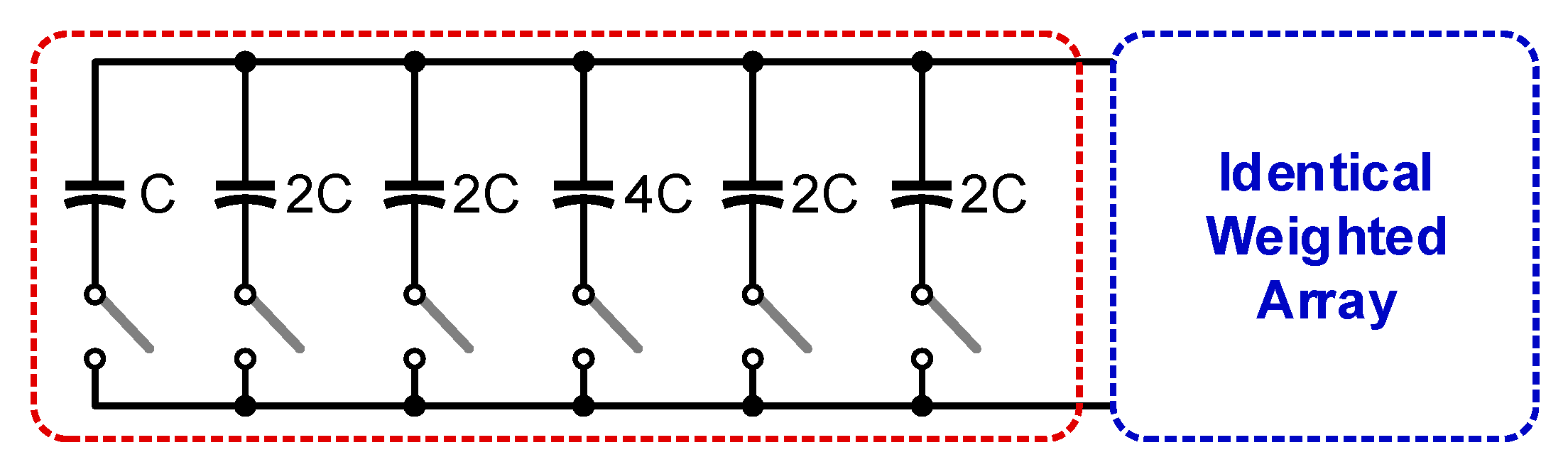

3.2. Capacitive Interpolation SAR ADC (I-SAR ADC)

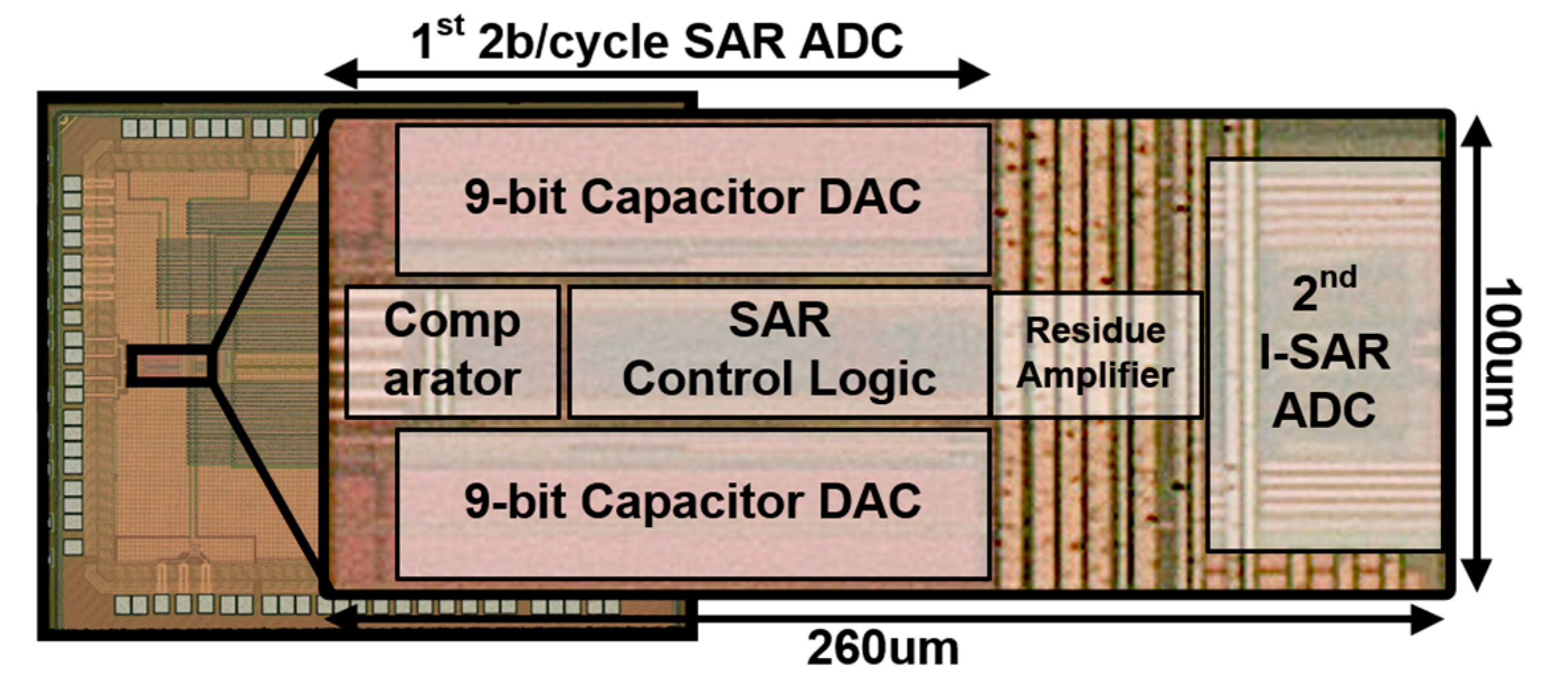

4. Hardware Implementation

4.1. 1st-Stage ADC: Multi-Bit SAR ADC with Background Calibration

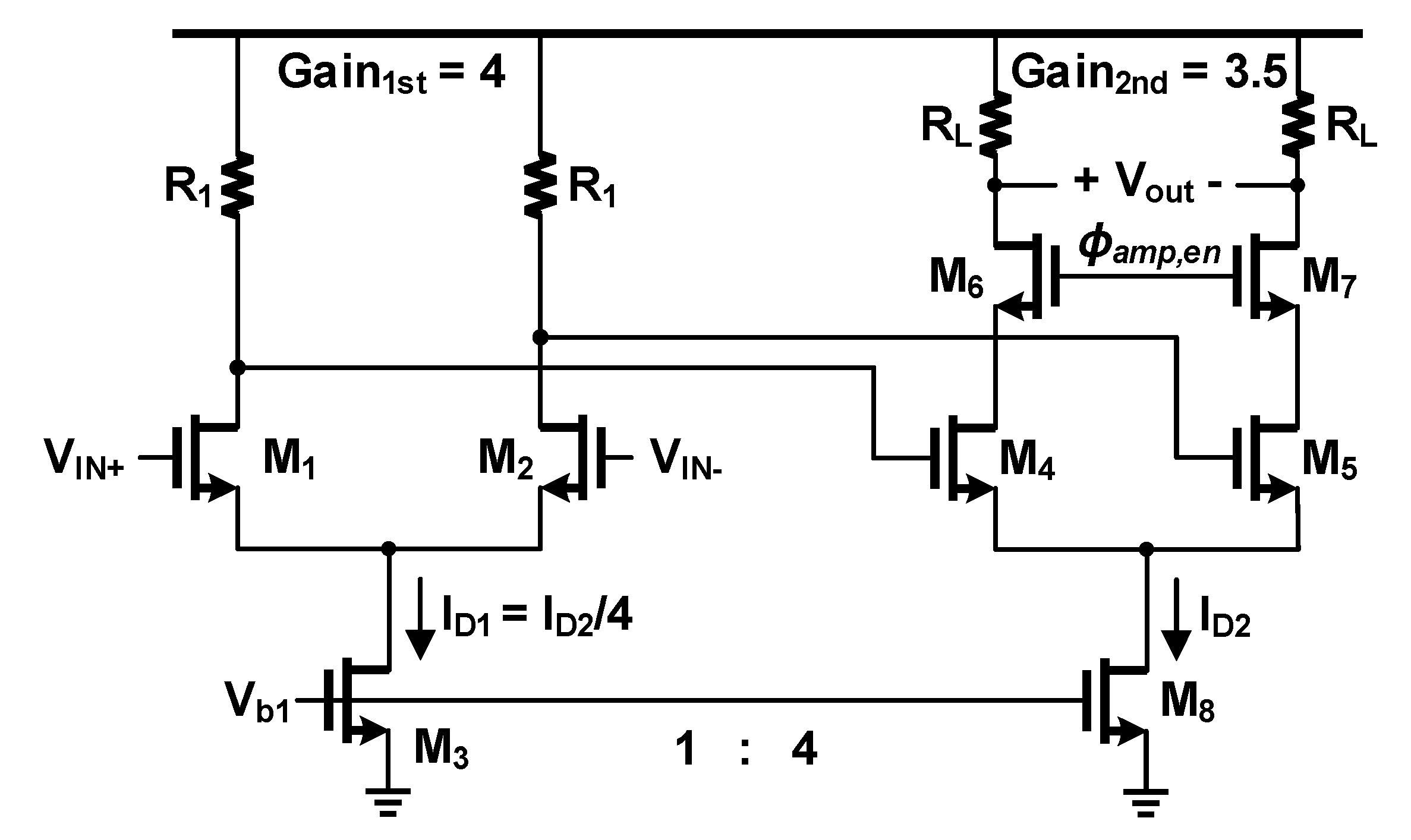

4.2. Residue Amplifier

4.3. 2nd-Stage ADC: Proposed Successive-Approximation Interpolation ADC

5. Measurement Results and Discussion

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Abbreviations

| SAR | Successive-approximation-register |

| ADC | Analog-to-digital Converter |

| RA | Residue Amplifier |

| I-SAR ADC | Interpolation SAR ADC |

| SNR | Signal-to-Noise Ratio |

| SNDR | Signal-to-Noise distortion ratio |

| SFDR | Spurious-Free Dynamic Range |

| ENOB | Effective Number of Bits |

| DNL | Differential Non-Linearity |

| INL | Integrated Non-Linearity |

| FoMw | Walden figure-of-merit |

References

- Luu, D.; Kull, L.; Toifl, T.; Menolfi, C.; Braendli, M.; Francese, P.A.; Morf, T.; Kossel, M.; Yueksel, H.; Cevrero, A.; et al. A 12-bit 300-MS/s SAR ADC with Inverter-Based Preamplifier and Common-Mode-Regulation DAC in 14-nm CMOS FinFET. IEEE J. Solid State Circuits 2018, 53, 3268–3279. [Google Scholar] [CrossRef]

- Janssen, E.; Doris, K.; Zanikopoulos, A.; Murroni, A.; van der Weide, G.; Lin, Y.; Alvado, L.; Darthenay, F.; Fregeais, Y. An 11b 3.6 GS/s time-interleaved SAR ADC in 65 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013; pp. 464–465. [Google Scholar]

- Hong, H.-K.; Kang, H.-W.; Jo, D.-S.; Lee, D.-S.; You, Y.-S.; Lee, Y.-H.; Park, H.-J.; Ryu, S.-T. A 2.6b/cycle-architecture-based 10b 1.7 GS/s 15.4 mW 4x-time-interleaved SAR ADC with a multistep hardware-retirement technique. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 25 February 2015; pp. 1–3. [Google Scholar]

- Kang, H.-W.; Hong, H.-K.; Kim, W.; Ryu, S.-T. A Time-Interleaved 12-b 270-MS/s SAR ADC with Virtual-Timing-Reference Timing-Skew Calibration Scheme. IEEE J. Solid State Circuits 2018, 53, 2584–2594. [Google Scholar] [CrossRef]

- Wang, D.; Zhu, X.; Guo, X.; Luan, J.; Zhou, L.; Wu, D.; Liu, H.; Wu, J.; Liu, X. A 2.6 GS/s 8-Bit Time-Interleaved SAR ADC in 55 nm CMOS Technology. Electronics 2019, 8, 305. [Google Scholar] [CrossRef]

- Verbruggen, B.; Deguchi, K.; Malki, B.; Craninckx, J. A 70 dB SNDR 200 MS/s 2.3 mW dynamic pipelined SAR ADC in 28 nm digital CMOS. In Proceedings of the IEEE Symposium on VLSI Circuits Digest of Technical Papers, Honolulu, HI, USA, 10–13 June 2014. [Google Scholar]

- Huang, H.; Xu, H.; Elies, B.; Chiu, Y. A Non-Interleaved 12-b 330-MS/s Pipelined-SAR ADC with PVT-Stabilized Dynamic Amplifier Achieving Sub-1-dB SNDR Variation. IEEE J. Solid State Circuits 2017, 52, 3235–3247. [Google Scholar] [CrossRef]

- Martens, E.; Hershberg, B.; Craninckx, J. A 69-dB SNDR 300-MS/s Two-Time Interleaved Pipelined SAR ADC in 16-nm CMOS FinFET With Capacitive Reference Stabilization. IEEE J. Solid State Circuits 2018, 53, 1161–1171. [Google Scholar] [CrossRef]

- Kull, L.; Luu, D.; Menolfi, C.; Braendli, M.; Francese, P.A.; Morf, T.; Kossel, M.; Yueksel, H.; Cevrero, A.; Ozkaya, I.; et al. A 10b 1.5 GS/s pipelined-SAR ADC with background second-stage common-mode regulation and offset calibration in 14 nm CMOS FinFET. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 5–9 February 2017; pp. 474–475. [Google Scholar]

- Elshater, A.; Venkatachala, P.K.; Lee, C.Y.; Muhlestein, J.; Leuenberger, S.; Sobue, K.; Hamashita, K.; Moon, U.K. A 10-MW 16-b 15-MS/s Two-Step SAR ADC with 95-DB DR Using Dual-Deadzone Ring Amplifier. IEEE J. Solid State Circuits 2019, 54, 3410–3420. [Google Scholar] [CrossRef]

- Wu, J.; Wu, J. A 12-Bit 200 MS/s Pipelined-SAR ADC Using Back-Ground Calibration for Inter-Stage Gain. Electronics 2020, 9, 507. [Google Scholar] [CrossRef]

- Ramkaj, A.T.; Pena Ramos, J.C.; Pelgrom, M.J.M.; Steyaert, M.S.J.; Verhelst, M.; Tavernier, F. A 5-GS/s 158.6-MW 9.4-ENOB Passive-Sampling Time-Interleaved Three-Stage Pipelined-SAR ADC with Analog-Digital Corrections in 28-Nm CMOS. IEEE J. Solid State Circuits 2020, 55, 1–12. [Google Scholar] [CrossRef]

- Yoshioka, K.; Sugimoto, T.; Waki, N.; Kim, S.; Kurose, D.; Ishii, H.; Furuta, M.; Sai, A.; Itakura, T. A 0.7 V 12b 160 MS/s 12.8 fJ/conv-step pipelined-SAR ADC in 28 nm CMOS with digital amplifier technique. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 5–9 February 2017; pp. 478–479. [Google Scholar]

- Moon, K.; Kang, H.; Jo, D.; Kim, M.; Baek, S.; Choi, M.; Ko, H.; Ryu, S.T. A 9.1-ENOB 6-mW 10-Bit 500-MS/s Pipelined-SAR ADC with Current-Mode Residue Processing in 28-nm CMOS. IEEE J. Solid State Circuits 2019, 54, 2532–2542. [Google Scholar] [CrossRef]

- Li, J.; Guo, X.; Luan, J.; Wu, D.; Zhou, L.; Wu, N.; Huang, Y.; Jia, H.; Zheng, X.; Wu, J.; et al. A 1 GS/s 12-Bit Pipelined/SAR Hybrid ADC in 40 nm CMOS Technology. Electronics 2020, 9, 375. [Google Scholar] [CrossRef]

- Gao, B.; Li, X.; Sun, J.; Wu, J. Modeling of High-Resolution Data Converter: Two-Step Pipelined-SAR ADC based on ISDM. Electronics 2020, 9, 137. [Google Scholar] [CrossRef]

- Lim, Y.; Flynn, M.P. A 1 mW 71.5 dB SNDR 50 MS/s 13 bit Fully Differential Ring Amplifier Based SAR-Assisted Pipeline ADC. IEEE J. Solid State Circuits 2015, 50, 2901–2911. [Google Scholar] [CrossRef]

- Lagos, J.; Hershberg, B.; Martens, E.; Wambacq, P.; Craninckx, J. A single-channel, 600 Msps, 12 bit, ringamp-based pipelined ADC in 28 nm CMOS. In Proceedings of the IEEE Symposium on VLSI Circuits Digest of Technical Papers, Kyoto, Japan, 5–8 June 2017; pp. C96–C97. [Google Scholar]

- Mangelsdorf, C.; Malik, H.; Lee, S.-H.; Hisano, S.; Martin, M. A two-residue architecture for multistage ADCs. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 24–26 February 1993; pp. 64–65. [Google Scholar]

- Miyahara, M.; Lee, H.; Paik, D.; Matsuzawa, A. A 10b 320 MS/s 40 mW open-loop interpolated pipeline ADC. In Proceedings of the IEEE Symposium on VLSI Circuits Digest of Technical Papers, Honolulu, HI, USA, 15–17 June 2011; pp. 126–127. [Google Scholar]

- Mulder, J.; van der Goes, F.M.L.; Vecchi, D.; Westra, J.R.; Ayranci, E.; Ward, C.M.; Wan, J.; Bult, K. An 800 MS/s dual-residue pipeline ADC in 40 nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 20–24 February 2011; pp. 184–186. [Google Scholar]

- Seo, M.-J.; Kim, Y.-D.; Chung, J.-H.; Ryu, S.-T. A 40 nm CMOS 12b 200 MS/s Single-amplifier Dual-residue Pipelined-SAR ADC. In Proceedings of the IEEE Symposium on VLSI Circuits Digest of Technical Papers, Kyoto, Japan, 9–14 June 2019. [Google Scholar]

- Nam, J.; Hassanpourghadi, M.; Zhang, A.; Chen, M.S.-W. A 12-Bit 1.6, 3.2, and 6.4 GS/s 4-b/Cycle Time-Interleaved SAR ADC with Dual Reference Shifting and Interpolation. IEEE J. Solid State Circuits 2018, 53, 1765–1779. [Google Scholar] [CrossRef]

- Seo, M.J.; Jin, D.H.; Kim, Y.D.; Kim, J.P.; Ryu, S.T. A Single-Supply CDAC-Based Buffer-Embedding SAR ADC with Skip-Reset Scheme Having Inherent Chopping Capability. IEEE J. Solid State Circuits 2020, 55, 2660–2669. [Google Scholar] [CrossRef]

- Kim, W.; Hong, H.-K.; Roh, Y.-J.; Kang, H.-W.; Hwang, S.-I.; Jo, D.-S.; Chang, D.-J.; Seo, M.-J.; Ryu, S.-T. A 0.6 V 12 b 10 MS/s low-noise asynchronous SAR-assisted time-interleaved SAR (SATI-SAR) ADC. IEEE J. Solid State Circuits 2016, 51, 1826–1839. [Google Scholar] [CrossRef]

- Hong, H.-K.; Kang, H.-W.; Sung, B.; Lee, C.-H.; Choi, M.; Park, H.-J.; Ryu, S.-T. An 8.6 ENOB 900 MS/s Time-Interleaved 2b/cycle SAR ADC with a 1b/cycle Reconfiguration for Resolution Enhancement. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013; pp. 470–471. [Google Scholar]

| This Work | VLSI11 Miyahara | ISSCC15 Boo | VLSI14 Zhou | ISSCC17 Yoshioka | ISSCC17 Huang | |

|---|---|---|---|---|---|---|

| Architecture | Dual residue Pipelined-SAR | Dual residue Pipeline | Pipeline | Pipelined-SAR | Pipelined-SAR | Pipelined-SAR |

| Resolution | 12 | 10 | 12 | 12 | 12 | 12 |

| Technology (nm) | 40 | 90 | 65 | 40 | 28 | 65 |

| Area (mm2) | 0.026 | 0.46 | 0.59 | 0.24 | 0.1 | 0.08 |

| Sampling Speed (1 Channel) (MS/s) | 200 | 320 | 250 | 160 | 80 | 330 |

| SNDR (dB) | 62.1 | 53 | 65.7 | 65.3 | 61.1 | 63.5 |

| SFDR (dB) | 67.1 | 65 | 84.6 | 86.9 | 72.7 | 83.4 |

| Power (dB) | 3.9 | 40 | 49.7 | 4.96 | 1.9 | 6.23 |

| FoMw 1 (fJ/conversion-step) | 19.0 | 390 | 108.5 | 20.7 | 12.8 | 15.4 |

| Inter-stage Mismatch Calibration | Not Required | Relative Gain Calibration | Off-chip Calibration | Digital Background Calibration | Assisted by Digital Amplifier | Replica Dynamic Amplifier |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Seo, M.-J. A Single-Amplifier Dual-Residue Pipelined-SAR ADC. Electronics 2021, 10, 421. https://doi.org/10.3390/electronics10040421

Seo M-J. A Single-Amplifier Dual-Residue Pipelined-SAR ADC. Electronics. 2021; 10(4):421. https://doi.org/10.3390/electronics10040421

Chicago/Turabian StyleSeo, Min-Jae. 2021. "A Single-Amplifier Dual-Residue Pipelined-SAR ADC" Electronics 10, no. 4: 421. https://doi.org/10.3390/electronics10040421

APA StyleSeo, M.-J. (2021). A Single-Amplifier Dual-Residue Pipelined-SAR ADC. Electronics, 10(4), 421. https://doi.org/10.3390/electronics10040421