Reducing Conducted Emissions at the Output of Full-Bridge DCDC Converters with High Voltage Steps

Abstract

:1. Introduction

2. Analysis

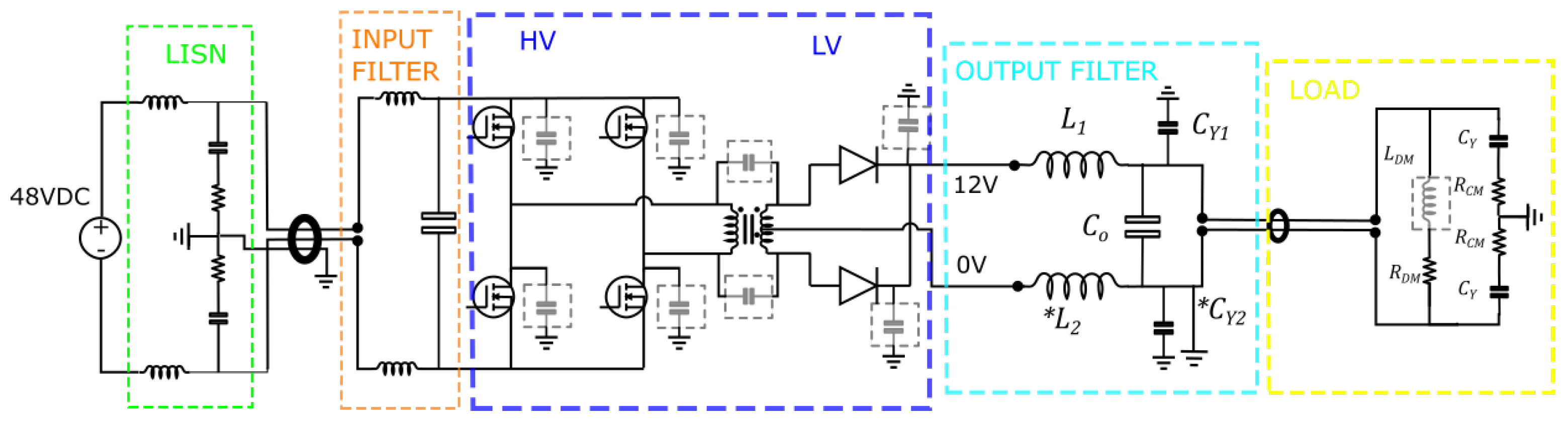

2.1. Topology of the DCDC Power Converter and Noise Sources

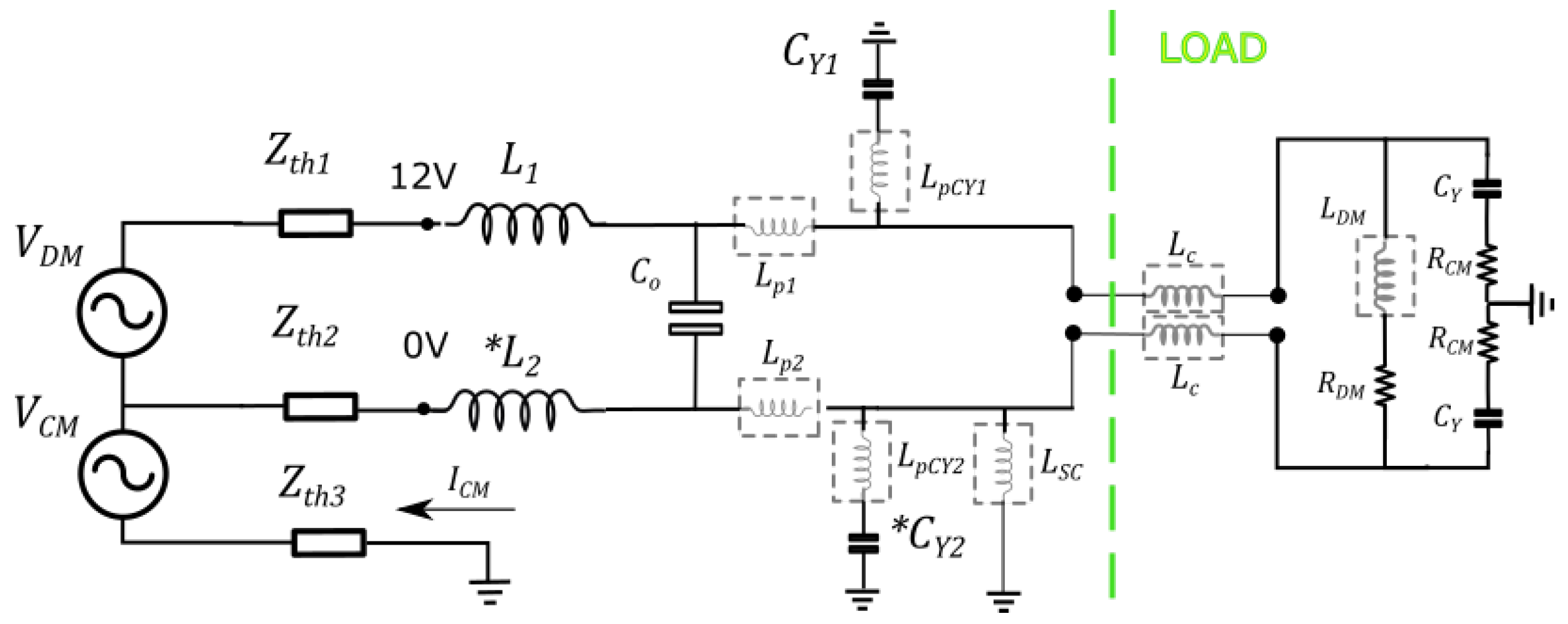

2.2. HF Model of the Converter at the Output

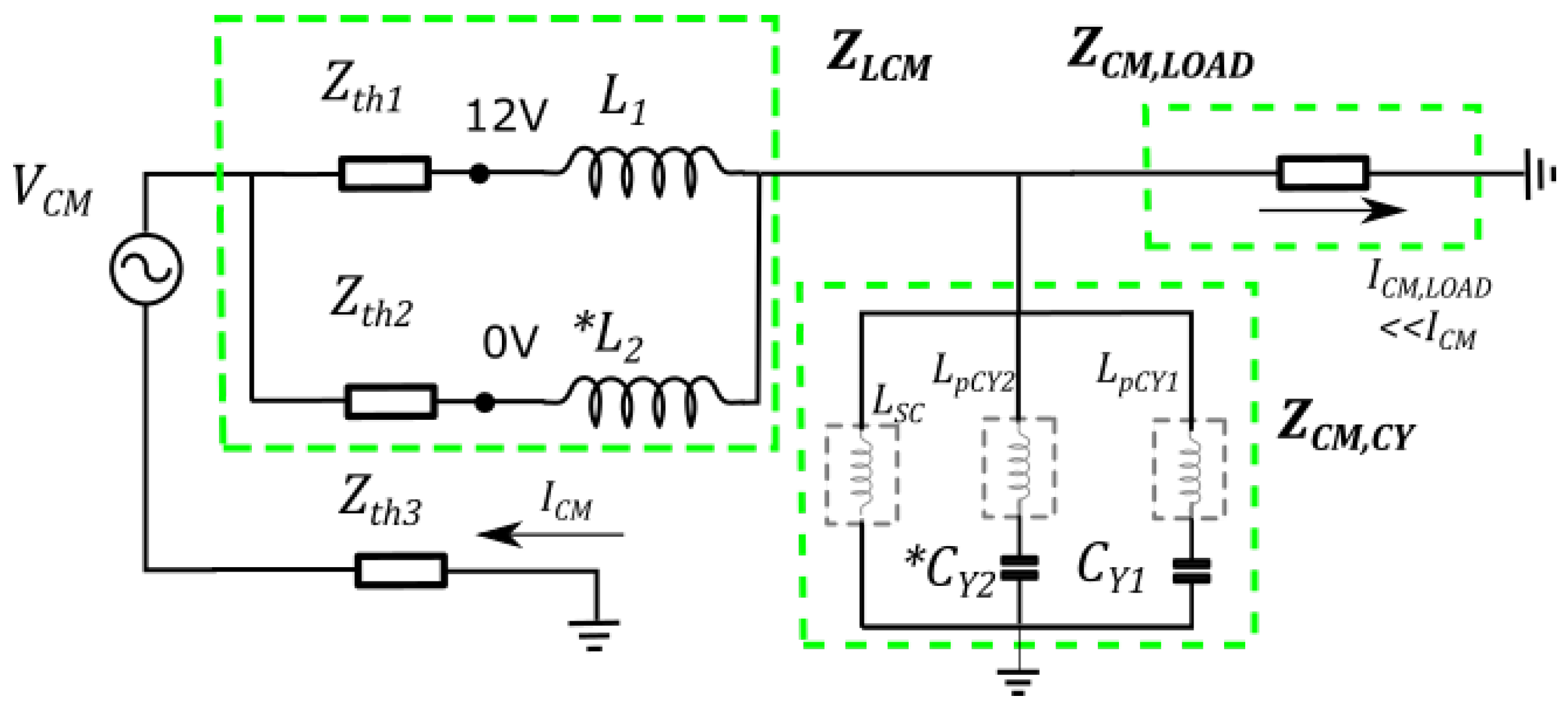

2.3. CM Conducted Emissions

- The impedance of the array of capacitors that conform is typically much lower than that of at low frequencies, and those of the parasitic inductances , , , and at high frequencies. Therefore, this array of capacitors can be regarded as a short circuit.

- The impedance of in series with both and is much larger than the rest of impedances of the filter. This assumption, together with the fact that voltage drops in and are expected to be roughly the same in ‘CC’, allows us to neglect the effect of and . Note that at low frequencies at which and can be ignored, the model in Figure 3 is also valid for both ‘CC’ and ‘C0VG’ cases.

2.4. DM Conducted Emissions

3. Materials and Methods

4. Results

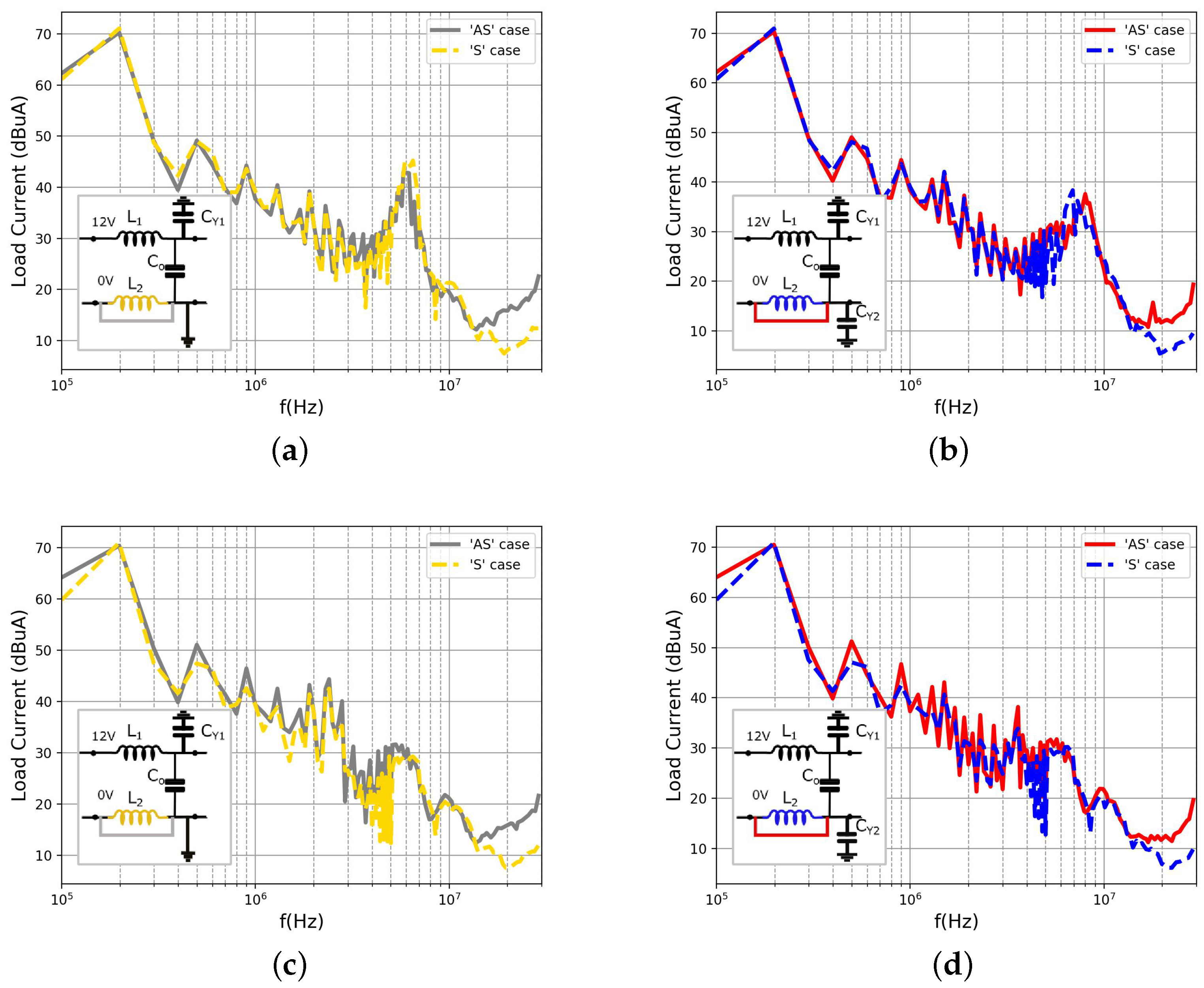

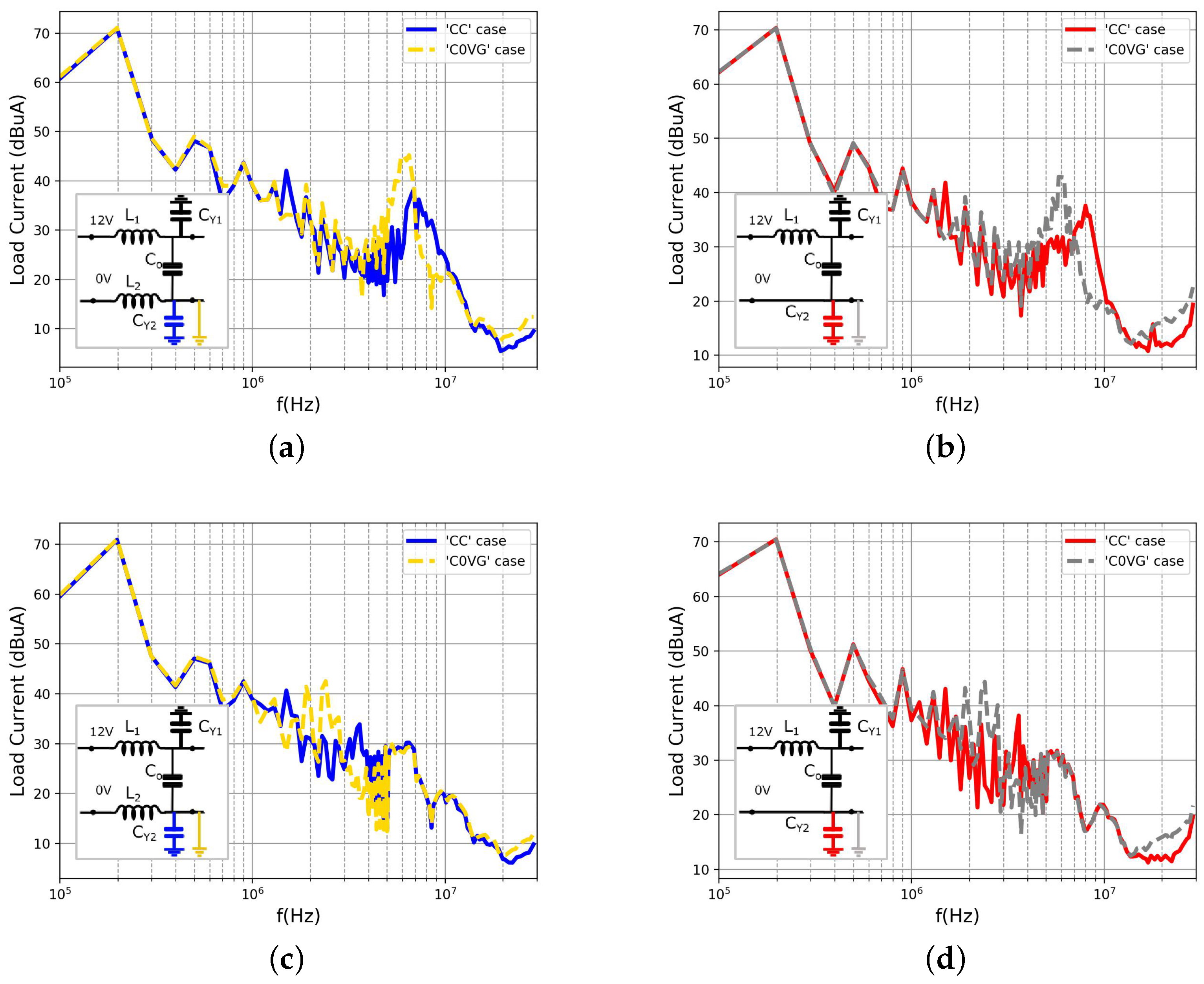

4.1. CM Conducted Emissions at the Output of the Converter

4.2. DM Conducted Emissions at the Output of the Converter

5. Discussion

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

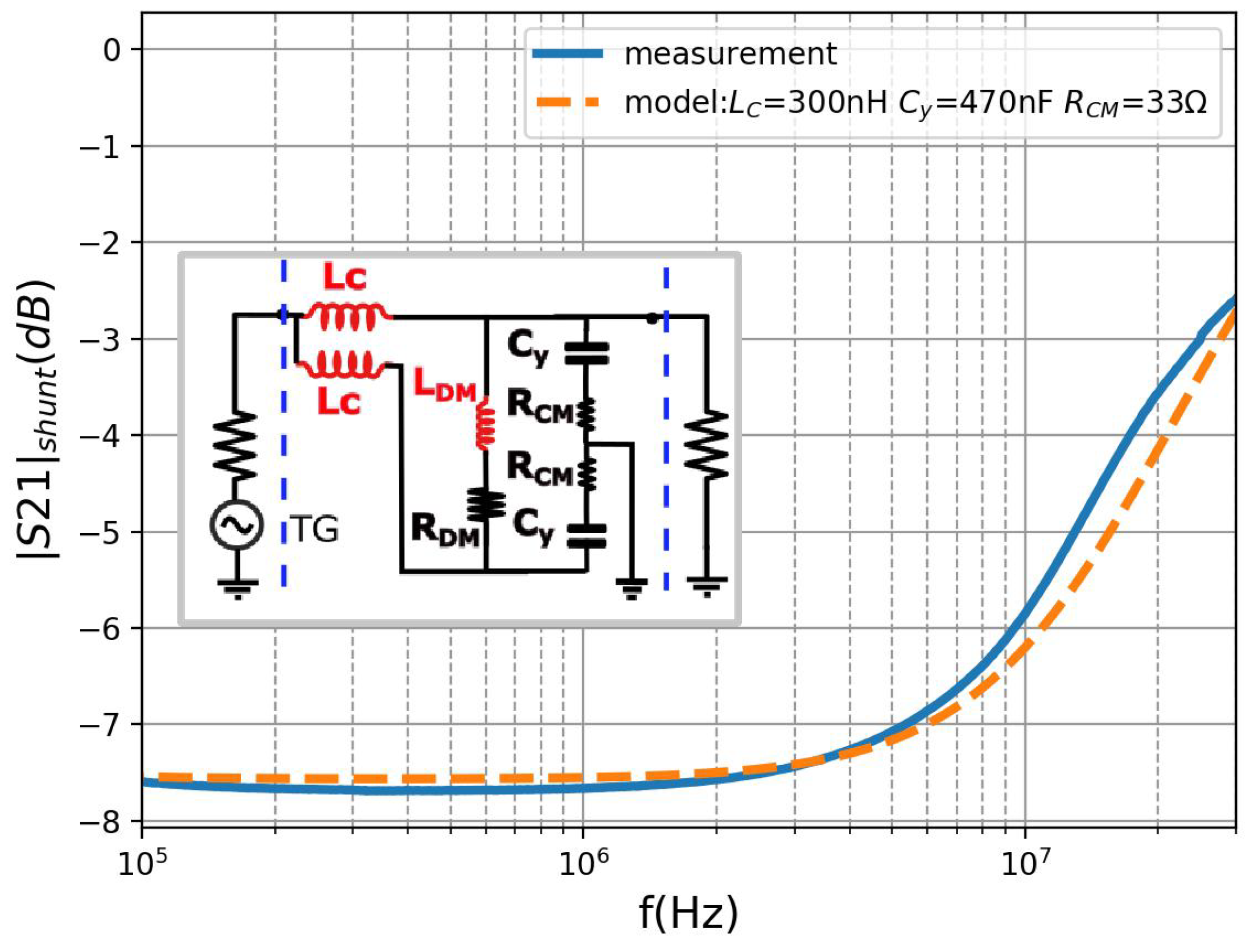

Appendix A. Extraction of Parameters of the Circuit Model

References

- Krismer, F. Modeling and Optimization of Bidirectional Dual Active Bridge DC DC Converter Topologies. Ph.D. Thesis, ETH Zurich, Zurich, Switzerland, 2010. [Google Scholar] [CrossRef]

- Hartmann, M. Ultra-Compact and Ultra-Efficient Three-Phase PWM Rectifier Systems for More Electric Aircraft. Ph.D. Thesis, ETH Zurich, Zurich, Switzerland, 2011. [Google Scholar]

- Brandelero, J.C. Conception et Réalisation d’un Convertisseur Multicellulaire DC/DC Isolé Pour Application Aéronautique. Ph.D. Thesis, INP de Toulouse, Toulouse, France, 2015. [Google Scholar]

- Badstübner, U. Ultra-High Performance Telecom DC-DC Converter. Ph.D. Thesis, ETH Zurich, Zurich, Switzerland, 2012. [Google Scholar]

- Yin, S.; Tseng, K.J.; Simanjorang, R.; Liu, Y.; Pou, J. A 50-kW High-Frequency and High-Efficiency SiC Voltage Source Inverter for More Electric Aircraft. IEEE Trans. Ind. Electron. 2017, 64, 9124–9134. [Google Scholar] [CrossRef]

- Paul, C.R. Introduction to Electromagnetic Compatibility; Wiley: Hoboken, NJ, USA, 1992; p. 280. [Google Scholar] [CrossRef]

- Gammeter, C.; Krismer, F.; Kolar, J.W. Weight and efficiency analysis of switched circuit topologies for modular power electronics in MEA. In Proceedings of the 42nd Annual Conference of the IEEE Industrial Electronics Society, Florence, Italy, 23–26 October 2016; pp. 3640–3647. [Google Scholar] [CrossRef]

- Mihalič, F.; Kos, D. Reduced conductive EMI in switched-mode dc-dc power converters without EMI filters: PWM versus randomized PWM. IEEE Trans. Power Electron. 2006, 21, 1783–1794. [Google Scholar] [CrossRef]

- Mainali, K.; Oruganti, R. Conducted EMI Mitigation Techniques for Switch-Mode Power Converters: A Survey. IEEE Trans. Power Electron. 2010, 25, 2344–2356. [Google Scholar] [CrossRef]

- Wang, Y.; De Haan, S.W.; Ferreira, J.A. Design of low-profile nanocrystalline transformer in high-current phase-shifted DC-DC converter. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE 2010), Atlanta, GA, USA, 12–16 September 2010; pp. 2177–2181. [Google Scholar] [CrossRef]

- Wang, S.; Kong, P.; Lee, F.C. Common Mode Noise Reduction for Boost Converters Using General Balance Technique. IEEE Trans. Power Electron. 2007, 22, 1410–1416. [Google Scholar] [CrossRef]

- Yazdani, M.R.; Filabadi, N.A.; Faiz, J. Conducted electromagnetic interference evaluation of forward converter with symmetric topology and passive filter. IET Power Electron. 2014, 7, 1113–1120. [Google Scholar] [CrossRef]

- Fu, D.; Wang, S.; Kong, P.; Lee, F.C.; Huang, D. Novel techniques to suppress the common-mode EMI noise caused by transformer parasitic capacitances in dc-dc converters. IEEE Trans. Ind. Electron. 2013, 60, 4968–4977. [Google Scholar] [CrossRef]

- Pahlevaninezhad, M.; Hamza, D.; Jain, P.K. An improved layout strategy for common-mode EMI suppression applicable to high-frequency planar transformers in high-power dc/dc converters used for electric vehicles. IEEE Trans. Power Electron. 2014, 29, 1211–1228. [Google Scholar] [CrossRef]

- Chu, Y.; Wang, S. A Generalized Common-Mode Current Cancelation Approach for Power Converters. IEEE Trans. Ind. Electron. 2015, 62, 4130–4140. [Google Scholar] [CrossRef]

- Xie, L.; Ruan, X.; Ye, Z. Reducing Common Mode Noise in Phase-Shifted Full-Bridge Converter. IEEE Trans. Ind. Electron. 2018, 65, 7866–7877. [Google Scholar] [CrossRef]

- EN55025:2017/CISPR 25. Vehicles, Boats and Internal Combustion Engines—Radio Disturbance Characteristics—Limits and Methods of Measurement for the Protection of On-Board Receivers; International Electrotechnical Commission: Geneva, Switzerland, 2017. [Google Scholar]

- RTCA/DO-160G. Environmental Conditions and Test Procedures for Airborne Equipment; Federal Aviation Administration: Washington, DC, USA, 2005.

- Ott, H.W. Electromagnetic Compatibility Engineering; John Wiley and Sons Ltd.: Hoboken, NJ, USA, 1976. [Google Scholar]

- Gonzalez, P.; Bejarano, C.; Ramiro, S.; Bernaly, J.; Prats, M.M. Impact of output filter layout in the conducted emissions of an on-board DC/DC converter for “More Electrical Aircraft”. In Proceedings of the 11th IEEE International Conference on Compatibility, Power Electronics and Power Engineering (CPE-POWERENG), Cadiz, Spain, 4–6 April 2017; pp. 483–488. [Google Scholar] [CrossRef]

- Sabate, J.A.; Vlatkovic, V.; Ridley, R.B.; Lee, F.C.; Cho, B.H. Design considerations for high-voltage high-power full-bridge zero-voltage-switched PWM converter. In Proceedings of the Fifth Annual Applied Power Electronics Conference and Exposition, Los Angeles, CA, USA, 11–16 March 1990; pp. 275–284. [Google Scholar] [CrossRef]

- Brunoro, M.; Vieira, J.L.F. A high-performance ZVS full-bridge DC-DC 0-50-V/0-10-A power supply with phase-shift control. IEEE Trans. Power Electron. 1999, 14, 495–505. [Google Scholar] [CrossRef]

- Joo, D.M.; Byun, J.E.; Lee, B.K.; Kim, J.S. Adaptive delay control for synchronous rectification phase-shifted full bridge converter with GaN HEMT. Electron. Lett. 2017, 53, 1541–1542. [Google Scholar] [CrossRef]

- Department of Defense. MIL-STD-461G. In Requirements for the Control of Electromagnetic Interference Characteristics of Subsystems and Equipment; CreateSpace: Scotts Valley, CA, USA, 2015. [Google Scholar]

- Tarateeraseth, V. EMI Filter Design Part I: Conducted EMI Generation Mechanism. IEEE Electromagn. Conf. Mag. 2011, 44–50. [Google Scholar] [CrossRef]

- Xie, L.; Ruan, X.; Ji, Q.; Ye, Z. Shielding-Cancelation Technique for Suppressing Common-Mode EMI in Isolated Power Converters. IEEE Trans. Ind. Electron. 2015, 62, 2814–2822. [Google Scholar] [CrossRef]

- Bishnoi, H.; Baisden, A.C.; Mattavelli, P.; Boroyevich, D. Analysis of EMI Terminal Modeling of Switched Power Converters. IEEE Trans. Power Electron. 2012, 27, 3924–3933. [Google Scholar] [CrossRef]

- Gonzalez, D.; Gago, J.; Balcells, J. New Simplified Method for the Simulation of Conducted EMI Generated by Switched Power Converters. IEEE Trans. Ind. Electron. 2003, 50, 1078–1084. [Google Scholar] [CrossRef]

- Ferrer, L.; Balcells, J.; Gonzalez, D.; Gago, J.; Lamich, M. Modelling of Differential Mode Conducted EMI Generated by Switched Power Inverters. In Proceedings of the IECON’03, 29th Annual Conference of the IEEE Industrial Electronics Society, Roanoke, VA, USA, 2–6 November 2003; Volume 3, pp. 2312–2315. [Google Scholar] [CrossRef]

- Magambo, J.S.N.T.; Bakri, R.; Margueron, X.; Le Moigne, P.; Mahe, A.; Guguen, S.; Bensalah, T. Planar Magnetic Components in More Electric Aircraft: Review of Technology and Key Parameters for DC-DC Power Electronic Converter. IEEE Trans. Transp. Electrif. 2017, 3, 831–842. [Google Scholar] [CrossRef]

- Gonzalez-Vizuete, P.; Fico, F.; Fernandez-Prieto, A.; Freire, M.J.; Mendez, J.B. Calculation of Parasitic Self- and Mutual-Inductances of Thin-Film Capacitors for Power Line Filters. IEEE Trans. Power Electron. 2019, 34, 236–246. [Google Scholar] [CrossRef]

- Mendez, J.B.; Freire, M.J.; Prats, M.A.M. Overcoming the Effect of Test Fixtures on the Measurement of Parasitics of Capacitors and Inductors. IEEE Trans. Power Electron. 2020, 35, 15–19. [Google Scholar] [CrossRef]

| Low Frequencies | |||||||

|---|---|---|---|---|---|---|---|

| S,CC | − − | 0.5 | 0.5 | ≪1 | 0.5 | 0.5 | − − |

| S,C0VG | − − | 0.5 | 0.5 | 0.5 | ≪1 | 1 | − |

| AS,CC | + + | ≪1 | 1 | 0.5 | 0.5 | 0.5 | + |

| AS,C0VG | + + | ≪1 | 1 | ≪1 | ≪1 | 1 | − |

| High Frequencies | |||||||

|---|---|---|---|---|---|---|---|

| S,CC | − − | 0.5 | 0.5 | ≪1 | 0.5 | 0.5 | − − |

| S,C0VG | − − | 0.5 | 0.5 | <0.5 | <0.5 | >0.5 | − |

| AS,CC | + + | ≪1 | 1 | 0.5 | 0.5 | 0.5 | + |

| AS,C0VG | + + | ≪1 | 1 | <0.5 | <0.5 | >0.5 | + + |

| , ‘S’ | , ‘AS’ | ||||

|---|---|---|---|---|---|

| L (μH) | (pH) | (k) | L (μH) | (pH) | (k) |

| 10.5 | 7.4 | 2 | 5.1 | 30 | 4 |

| , ‘C0VG’ | ‘10 nF’ | ‘50 nF’ | |||

| L (nH) | C (μF) | C (nF) | L (nH) | C (nF) | L (nH) |

| <5 | 88 | 10 | 10 | 50 | 20 |

| , | Load | ||||

| L (nH) | () | (μH) | (nH) | RCM () | (nF) |

| 10 | 1 | 2 | 300 | 33 | 470 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

González-Vizuete, P.; Bernal-Méndez, J.; Martín-Prats, M.A. Reducing Conducted Emissions at the Output of Full-Bridge DCDC Converters with High Voltage Steps. Electronics 2021, 10, 1373. https://doi.org/10.3390/electronics10121373

González-Vizuete P, Bernal-Méndez J, Martín-Prats MA. Reducing Conducted Emissions at the Output of Full-Bridge DCDC Converters with High Voltage Steps. Electronics. 2021; 10(12):1373. https://doi.org/10.3390/electronics10121373

Chicago/Turabian StyleGonzález-Vizuete, Pablo, Joaquín Bernal-Méndez, and María A. Martín-Prats. 2021. "Reducing Conducted Emissions at the Output of Full-Bridge DCDC Converters with High Voltage Steps" Electronics 10, no. 12: 1373. https://doi.org/10.3390/electronics10121373

APA StyleGonzález-Vizuete, P., Bernal-Méndez, J., & Martín-Prats, M. A. (2021). Reducing Conducted Emissions at the Output of Full-Bridge DCDC Converters with High Voltage Steps. Electronics, 10(12), 1373. https://doi.org/10.3390/electronics10121373