Abstract

The importance of energy-constrained processors continues to grow especially for ultra-portable sensor-based platforms for the Internet-of-Things (IoT). Processors for these IoT applications primarily operate at near-threshold (NT) voltages and have multiple power modes. Achieving high conversion efficiency within the DC–DC converter that supplies these processors is critical since energy consumption of the DC–DC/processor system is proportional to the DC–DC converter efficiency. The DC–DC converter must maintain high efficiency over a large load range generated from the multiple power modes of the processor. This paper presents a fully integrated step-down self-oscillating switched-capacitor DC–DC converter that is capable of meeting these challenges. The area of the converter is 0.0104 mm2 and is designed in 28 nm ultra-thin body and buried oxide fully-depleted SOI (UTBB FD-SOI). Back-gate biasing within FD-SOI is utilized to increase the load power range of the converter. With an input of 1 V and output of 460 mV, measurements of the converter show a minimum efficiency of 75% for 79 nW to 200 µW loads. Measurements with an off-chip NT processor load show efficiency up to 86%. The converter’s large load power range and high efficiency make it an excellent fit for energy-constrained processors.

1. Introduction

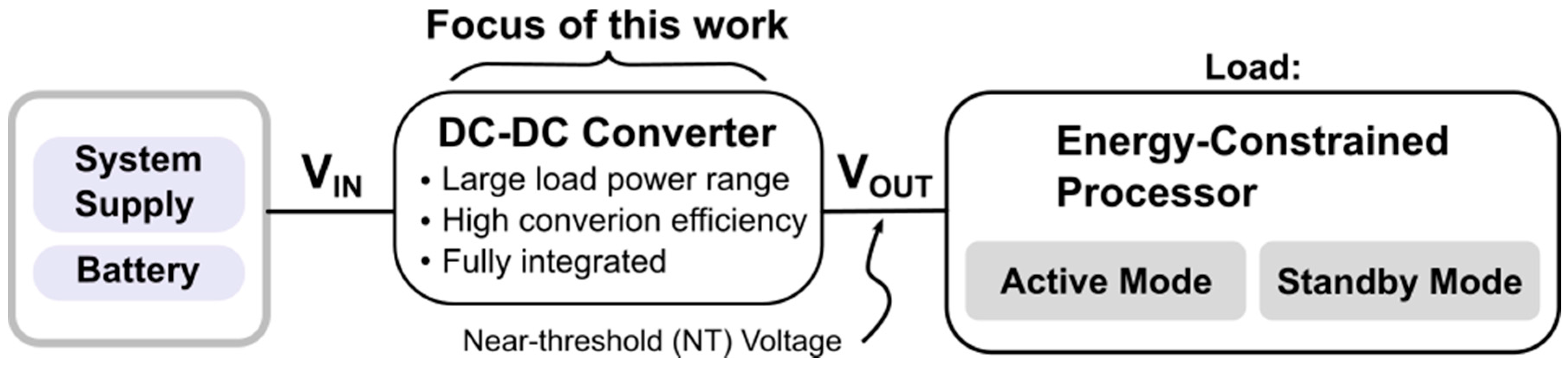

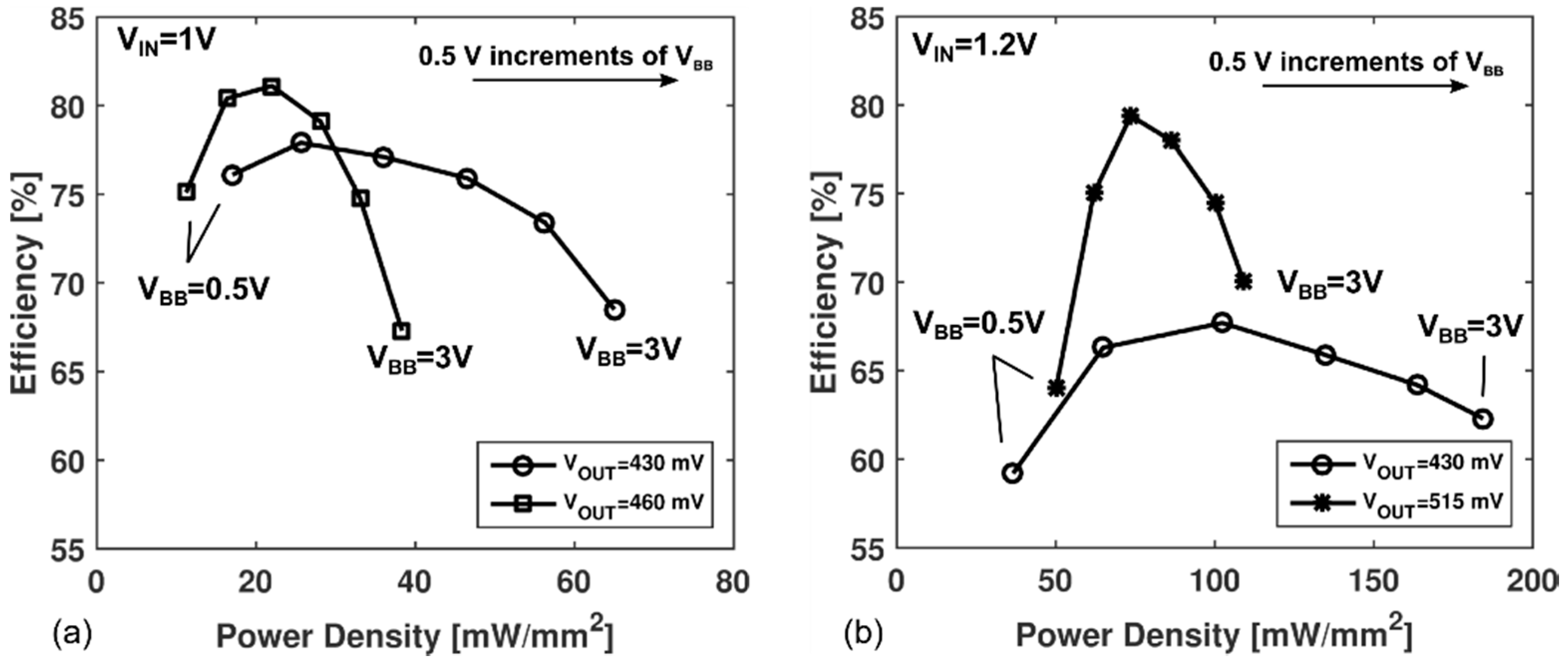

The relevance of energy-constrained processors [1,2,3,4,5,6] in sensor-based platforms for Internet-of-Things (IoT) applications continues to grow. These processors typically operate at near-threshold (NT) voltages since operation at NT significantly reduces energy consumption but avoids the large variance and performance penalties associated with sub-threshold voltages [1]. While operating at NT, energy-constrained processors utilize multiple active and standby power modes to achieve further energy savings [2,3,4]. The NT voltage must be supplied during each of these power modes to ensure functionality within always-on blocks such as memory, timers, and interrupt controllers [3,4]. As shown in Figure 1, NT voltages are typically supplied to energy-constrained processors by a DC–DC converter with a system supply or battery. The DC–DC converter is a critical block since the energy consumption of the DC–DC/processor system is proportional to the efficiency of the DC–DC converter. Achieving high efficiency in the DC–DC converter is therefore essential to realize energy savings associated with NT operation of the processor. Maintaining high efficiency over a large load range is also required since toggling between active and standby power modes induces 200× [2] to 6000× [3] changes in load power.

Figure 1.

This work is focused on the DC–DC converter that supplies energy-constrained processor loads.

Fully integrated switched-capacitor (SC) DC–DC converters are a logical choice for supplying energy-constrained processors as they can achieve high efficiency within digital CMOS processes [7]. However, achieving high efficiency in a SC DC–DC converter is challenging for the multiple order-of-magnitude changes in load power associated with different processor power modes. The SC self-oscillating topology [8] is a promising choice to meet this challenge due to its minimal control circuitry overhead and interleaved structure. The step-up self-oscillating topology introduced in [8] showed an efficiency of over 70% over a five order-of-magnitude change in load power. This excellent performance was achieved with a step-up configuration, a varying (above-threshold) output voltage, and with charge-transfer switches operating well above the threshold voltage.

In this work, the first (2:1) step-down self-oscillating DC–DC converter with a NT output voltage (VOUT) is presented [9]. It is designed in 28 nm ultra-thin body and buried oxide fully-depleted SOI (UTBB FD-SOI). The NT output voltage levels limit the maximum load power range within the self-oscillating topology since the |VGS| of the charge-transfer switches is at or below the threshold voltage. This results in a low overdrive voltage, which subsequently limits the maximum load current that the charge-transfer switches can handle. Additionally, the maximum oscillation frequency of the self-oscillating topology is limited from such low |VGS| voltages. To address both of these previous limitations associated with low |VGS|, this work utilizes body-biasing, or back-gate biasing, within the converter to increase the maximum load power. Back-gate biasing and the self-oscillating topology together enable a large load power range with high efficiency. Section 2 describes the similarities and differences of a conventional SC converter to the self-oscillating converter. The operation of the self-oscillating converter and the details of back-gate biasing are also described. Section 3 presents measurement results. Section 4 concludes the paper.

2. Self-Oscillating DC–DC Converter

2.1. Conventional Switched-Capacitor DC–DC Converter

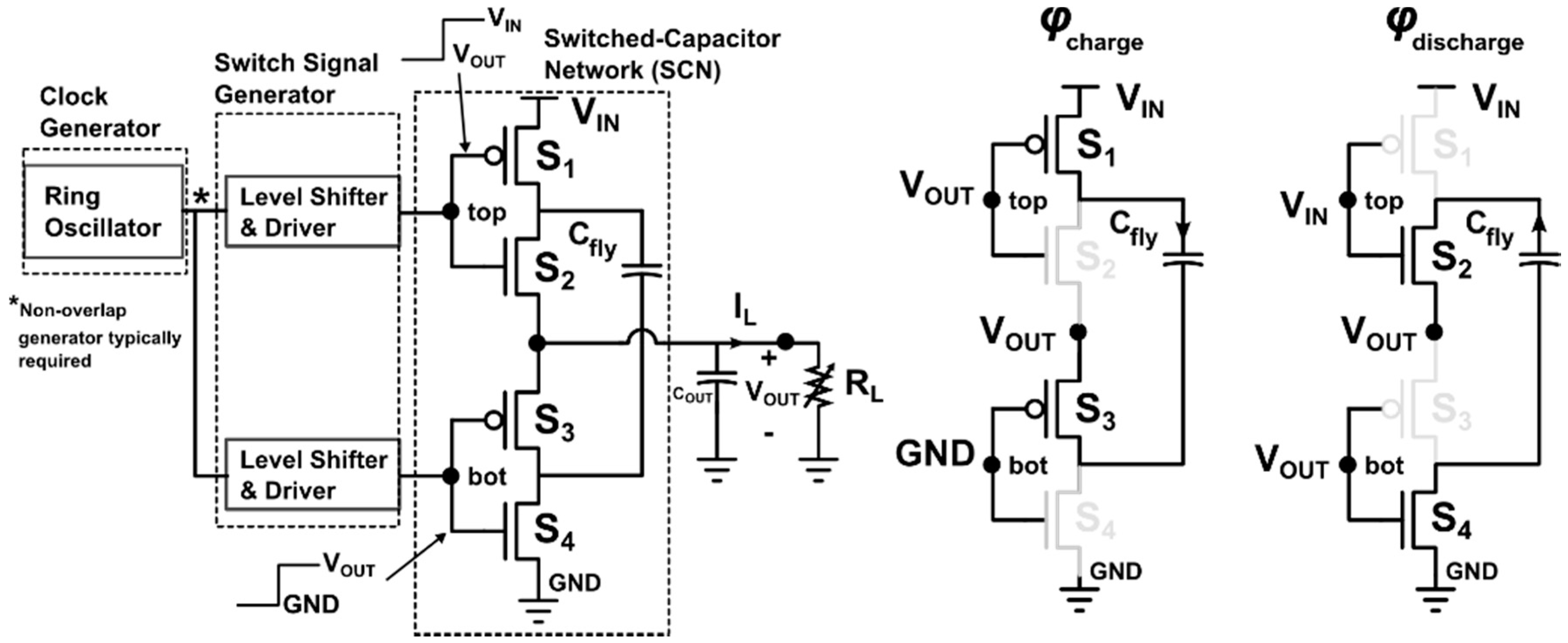

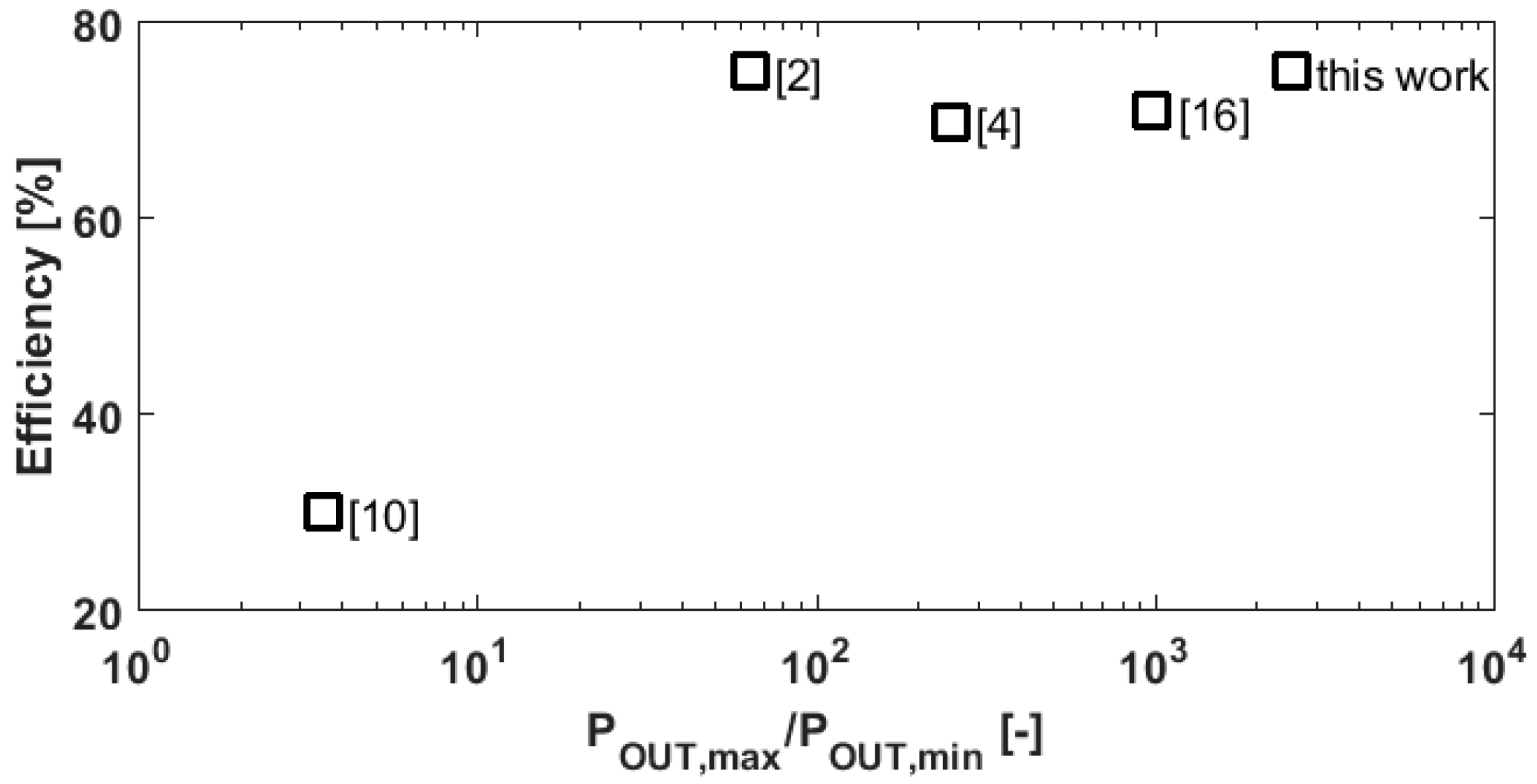

A conventional 2:1 SC DC–DC converter is shown in Figure 2. This converter steps down the input voltage (VIN) through a Switched-Capacitor Network (SCN). During a charge phase (ϕcharge), VIN charges Cfly and delivers charge to the output. A charge phase requires that only S1 and S3 be turned ON. During a discharge phase (ϕdischarge), the charge stored previously on Cfly is discharged to the output. The discharge phase requires that only S2 and S4 to be ON. The Clock Generator and Switch Signal Generator blocks provide signals to the gates of the switches (S1–S4) that ensure the correct charge or discharge phase configuration. The self-oscillating converter, which is explained in the subsequent paragraph, has an SCN that operates in the same manner as the conventional converter, but it does not require the Clock Generator and Switch Signal Generator blocks. Eliminating the need for clock generation and level conversion overhead is advantageous for low power systems since they are the dominant power losses at sub-5 μW loads [8,10].

Figure 2.

A conventional 2:1 switched-capacitor topology.

2.2. Step-Down Self-Oscillating DC–DC Converter

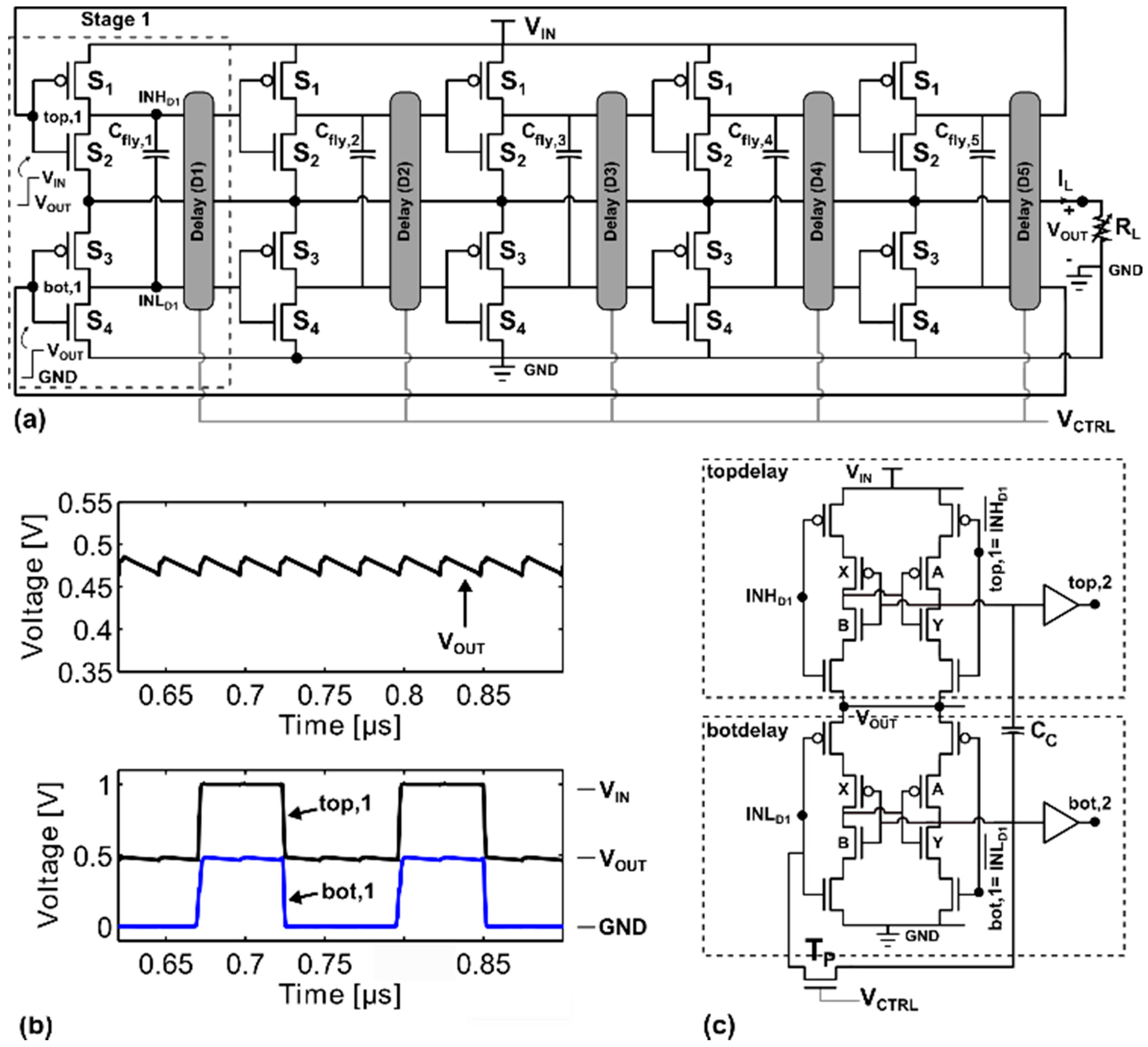

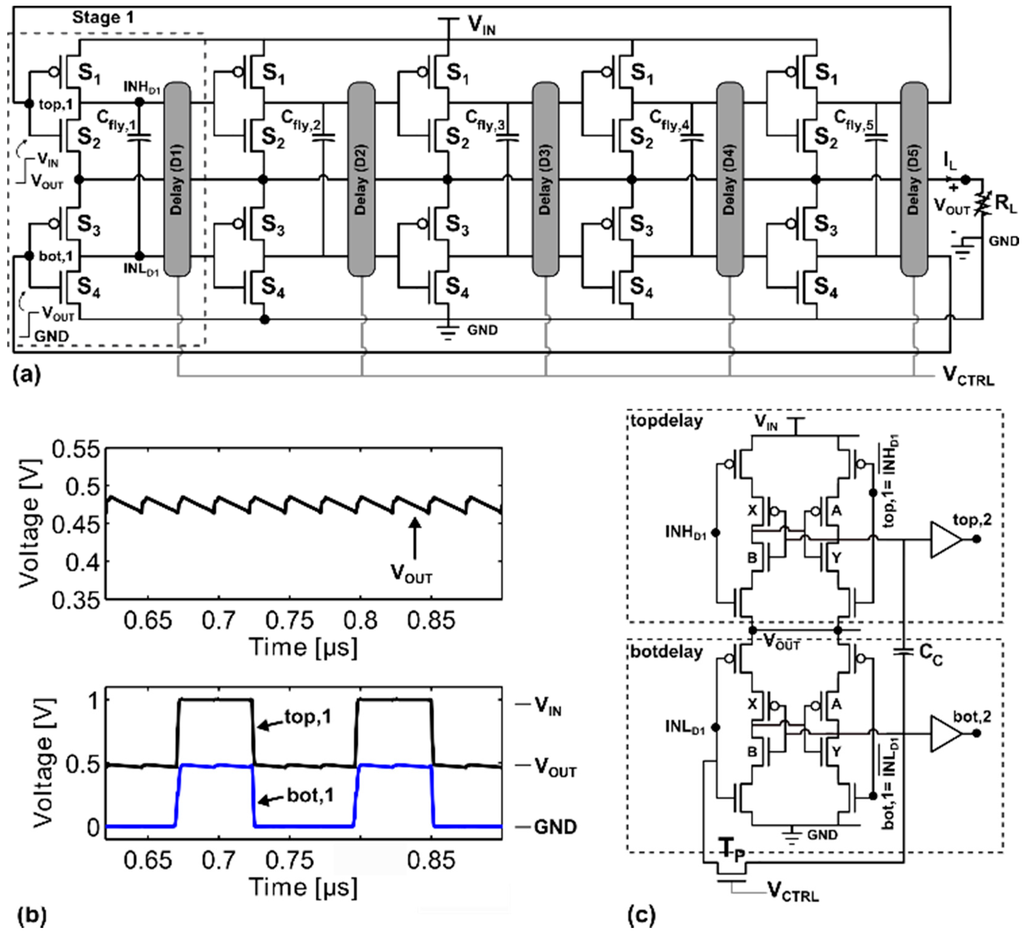

The 2:1 self-oscillating DC–DC converter is shown in Figure 3a. It is comprised of two stacked ring oscillators. The oscillators are synchronized through the fly capacitors (Cfly,1–5) and coupling capacitors Cc within the delay cell. The delay cell determines the oscillation frequency of the stacked ring oscillators. Modulating the oscillation frequency is used to maintain the output voltage over changes in load power.

Figure 3.

(a) 2:1 self-oscillating DC–DC converter; (b) Simulated output of the converter at Stage 1; (c) Delay cell schematic.

During oscillation, the SCN within each of the five stages alternates between a charge phase and discharge phase in the same manner as the conventional 2:1 converter shown previously in Figure 2. The converter is interleaved since each of the five stages delivers charge at different phase times. The simulated output from a single stage is shown in Figure 3b. The charge-transfer transistor lengths in each stage are twice the size of the minimum length to ensure leakage does not affect functionality at nW loads [11]. Only thin-oxide transistors are used within the converter. The fly capacitor in each stage is a 27pF MIM capacitor. In other words, there is 5 × 27 pF fly capacitance. Unlike MOS capacitors, the MIM capacitor does not suffer from large voltage dependences at near-threshold voltages or large bottom-plate capacitance losses. For the (active) load power levels in this design, bottom-plate capacitance is a dominant loss component.

The converter adjusts to changes in load power by tuning the delay within the delay cell. The delay cell (Di) within each stage determines the frequency of oscillation of the converter. As shown in Figure 3c, the delay cell consists of two leakage-based delay blocks [8] (topdelay and botdelay). These delay blocks operate identically and are coupled through a 0.2 pF MIM coupling capacitor Cc. The botdelay delay element from Stage 1 operates as follows. When the input to the delay cell (INLD1) transitions, two transistors within the positive feedback loop begin to leak between the drain and source. For example, for a low-to-high transition at INLD1, transistor A (B) has source-drain (drain-source) leakage. At some point, the leakage in A and B flips the state of the positive feedback loop and drives bot,2 low-to-high. The transistor TP is used to increase (decrease) the time to flip the state of the positive feedback loop by lowering (increasing) VCTRL. Unlike [8], this design does not use an additional coupling capacitor between top,2 and bot,2 since simulations showed that it had minimal effect on the converter performance.

This subsection described the operation of the step-down self-oscillating converter. In the next subsection, the effects of back-gate biasing on the converter’s performance are presented. Back-gate biasing affects both the delay cell and charge-transfer switches within the converter.

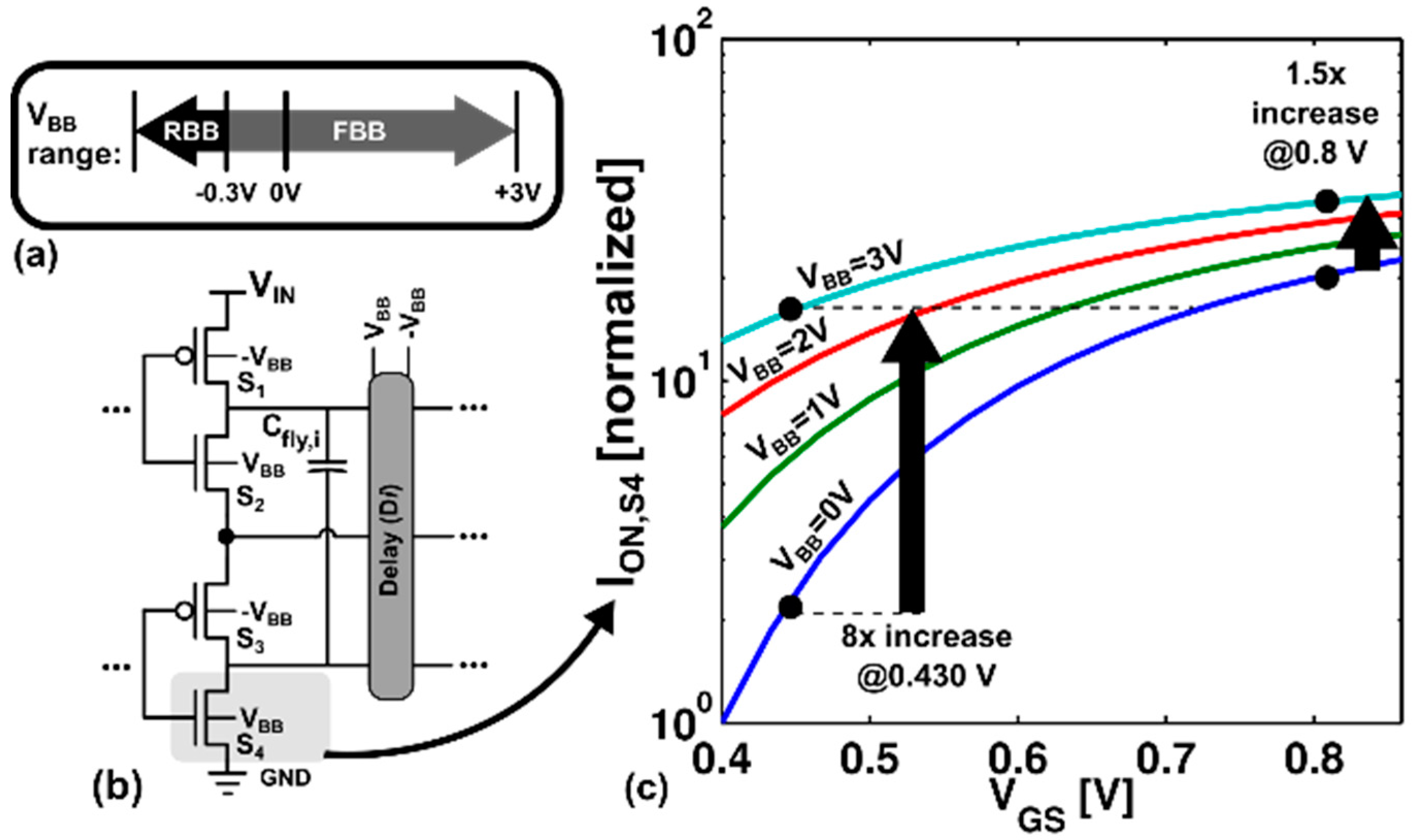

2.3. Back-Gate Biasing

Back-gate biasing is used to improve the performance of the converter. More specifically, back-gate biasing increases the maximum load power of the converter for two reasons. First, back-gate biasing increases the maximum drive strength of the charge-transfer switches. Since charge-transfer switches operate at or below the threshold voltage, the effect of back-gate biasing on drive strength is large. Second, back-gate biasing on the transistors within the delay cell increase leakage between the drain and source within the positive feedback loop, and thus, shift the oscillation frequency range to a higher values.

Back-gate biasing in UTBB FD-SOI is more effective in altering a transistor’s threshold voltage (Vth) than in nanoscale bulk CMOS for two reasons [12]. First, the range of bias voltages is not limited by diode conduction since the back-gate node is isolated from the drain and source. Second, the body-bias factor (γ) is much larger than bulk CMOS. For example, 28 nm UTBB FD-SOI has γ ≈ 85 mV/V, while bulk 28 nm CMOS has γ ≈ 25 mV/V. The converter takes advantage of the large bias range and high body-bias factor in order to increases its load power range.

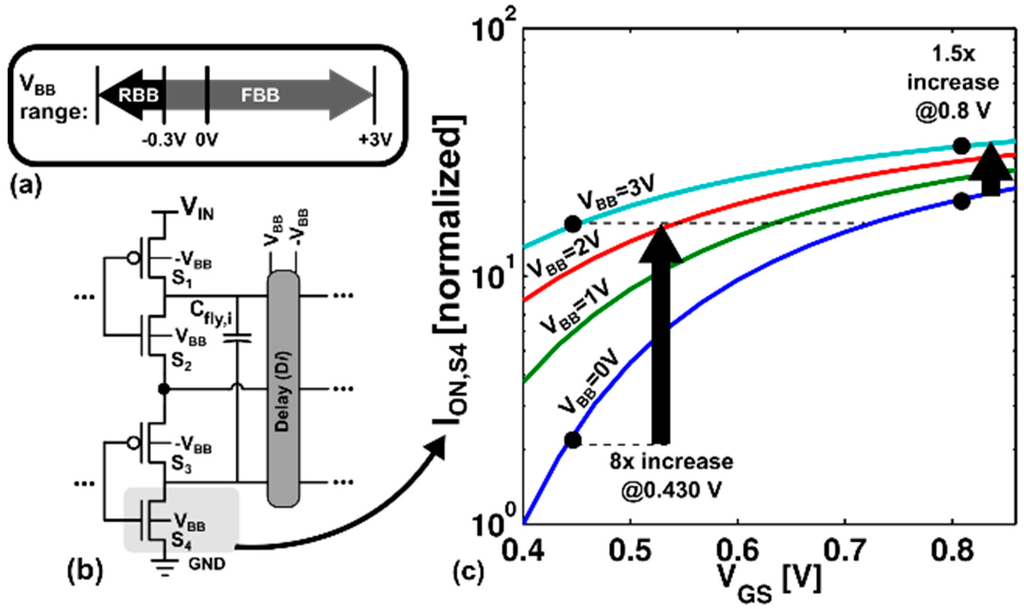

The back-gate biasing configuration for the converter is shown in Figure 4. The (LVT) PMOS transistors have a back-gate biasing voltage source opposite in polarity but equal in magnitude to the (LVT) NMOS transistors. Increasing the back-gate bias voltage (VBB) pushes both the PMOS and NMOS transistors further into forward body bias (FBB). As shown in Figure 4c, the effect of increasing VBB on a single charge-transfer switch in linear mode is larger at near-threshold values of VGS. The |VGS| of each switch within the converter is near the threshold voltage since the output of the converter is a near-threshold voltage. Thus, there is strong motivation to utilize back-gate biasing within the converter.

Figure 4.

(a) Back-gate biasing range; (b) Back-gate bias connections within the converter; (c) Simulated change in the drive strength of a single switch (S4) in linear mode.

The overall impact of back-gate biasing on the converter is found by examining the converter’s total output impedance (RO). The total output impedance depends on contributions from both the slow-switching regime impedance (RSSL) and the fast switching impedance (RFSL) as in [13]:

where KC is ¼ and KS is 4 for the 2:1 converter, Ctot is the total fly capacitance (135 pF), and Gtot is the summed switch conductance. In order to account for back-gate bias voltages in RO, Gtot needs to be identified. Gtot is described by

where m is the number of switches in one stage of the converter, k is the total number of stages within the converter, Li and Wi are the charge-transfer switch sizes, Ki is the technology constant, and VGSi is the gate-source voltage of the charge-transfer switch. From Equation (2), it can be seen that decreasing the threshold voltage (Vth,i) through increased VBB results in a larger overdrive voltage, and thus, a larger Gtot. Using the back-gate biasing configuration from Figure 4, Equation (2) expands to

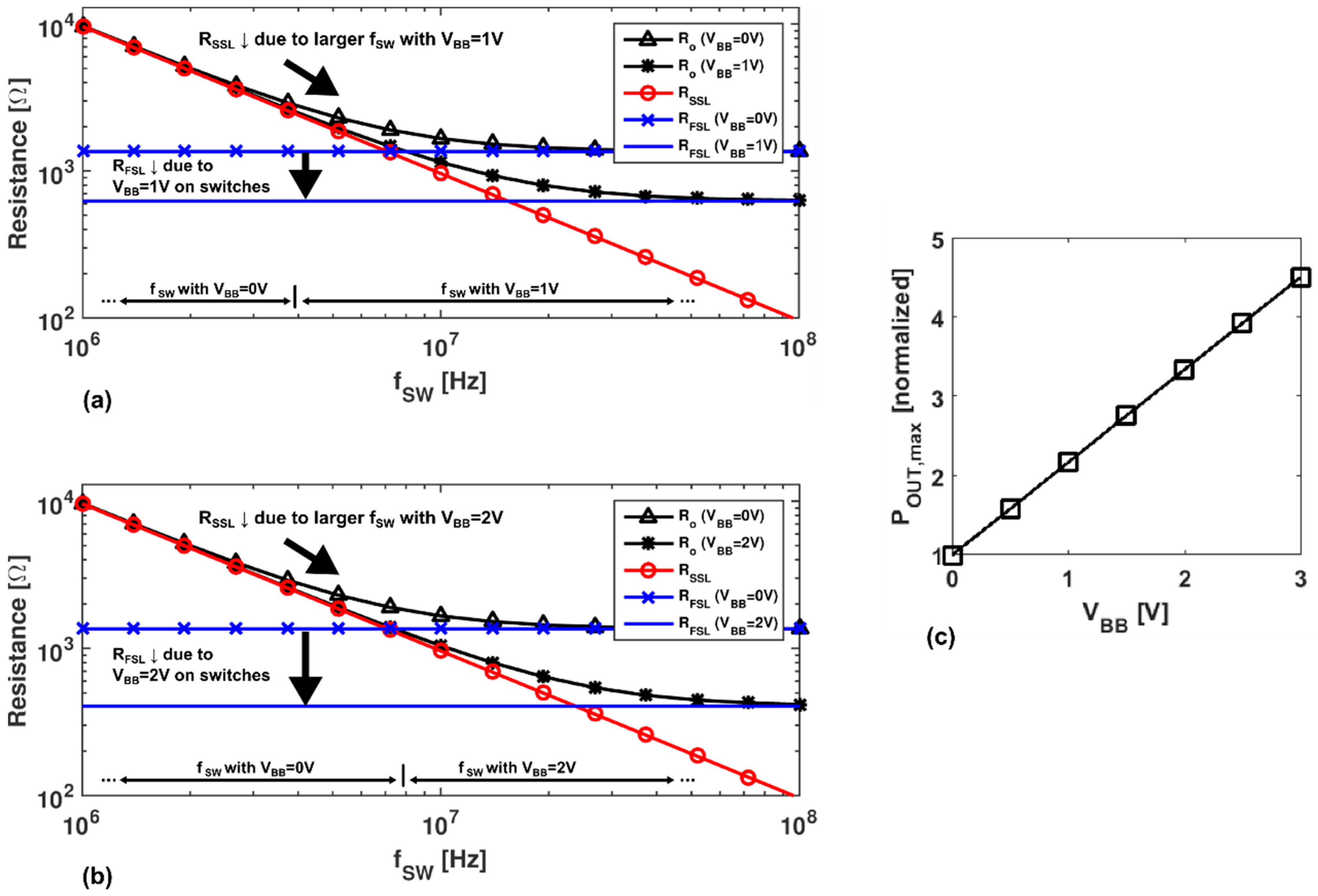

Using Gtot from Equation (3), the converter’s total output impedance RO from Equation (1) is plotted as a function of the converter’s switching frequency (fSW) as shown in Figure 5. The RO is plotted with two sets of back-gate bias voltages: VBB = 0 V and VBB = 1 V in Figure 5a and VBB = 0 V and VBB = 2 V in Figure 5b. Increasing the back-gate bias has two effects on the converter’s RO. First, increasing VBB shifts the range of fSW to larger values. This is a result of a decreased delay within the delay cells. Larger values of fSW enable larger load powers since RSSL decreases with increased fSW. Second, a larger VBB increases the overdrive voltage of the converter, and thus, decreases the RFSL. This lowers RO and allows for larger load powers. In summary, increasing the back-gate bias decreases RO. A lower RO enables a larger maximum power (POUT,max) since POUT α 1/RO.

Figure 5.

Analytical prediction of the converter output impedance from Equation (1). (a) VBB = 0 V and VBB = 1 V; (b) VBB = 0 V and VBB = 2 V; (c) Sweeping the maximum power POUT,max as a function of VBB. POUT,max is normalized to the POUT,max at VBB = 0 V and uses only RFSL contributions.

To further clarify the effects of VBB on POUT,max, Figure 5c shows the increase in POUT,max as VBB is increased from 0 to 3 V. POUT,max is estimated from Equation (1) using only the RFSL contribution and is normalized to the value of POUT,max with VBB = 0 V. Increasing VBB in the proposed converter from 0 to 3 V increases the POUT,max by 4.5×.

3. Measurement Results

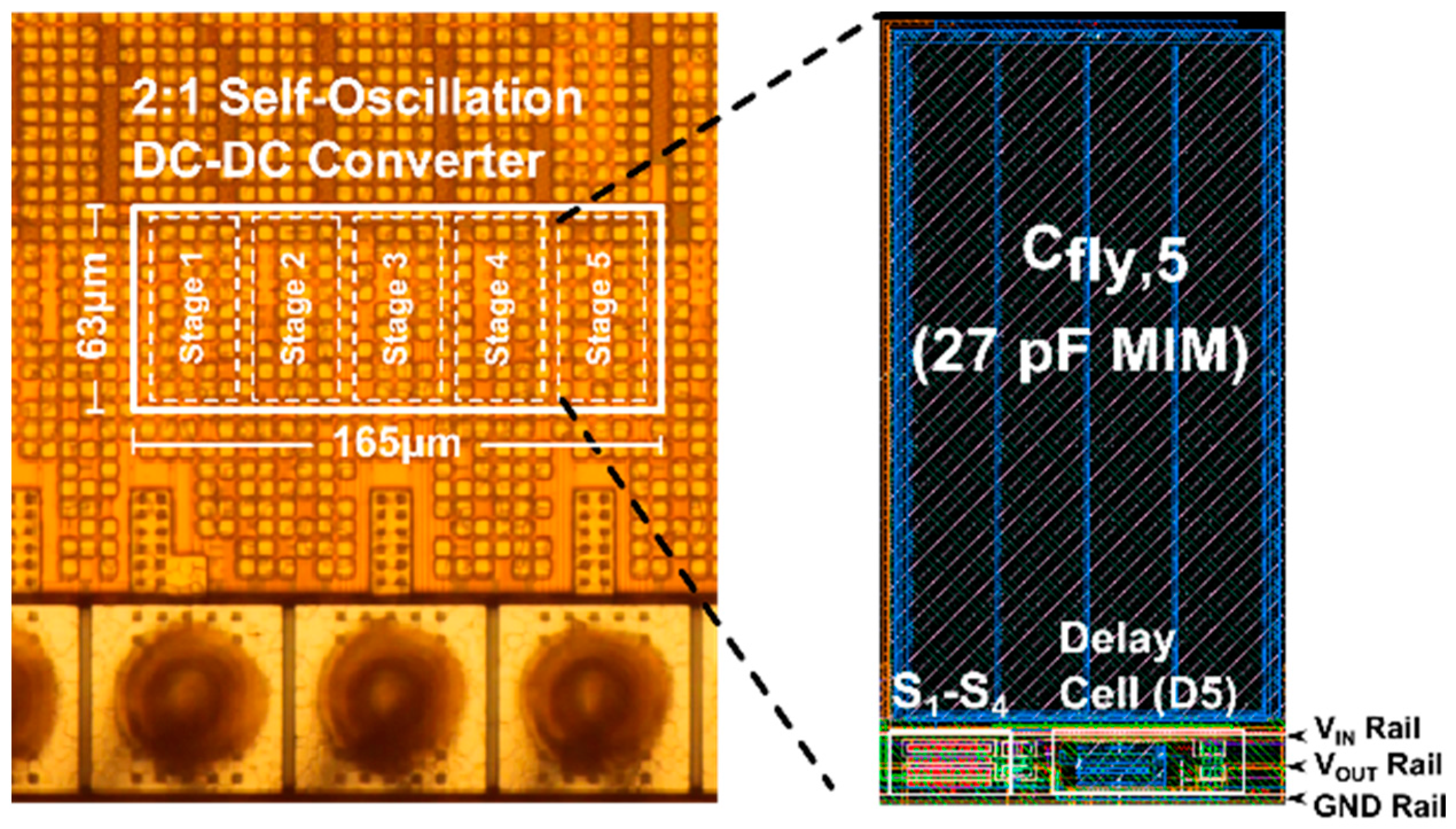

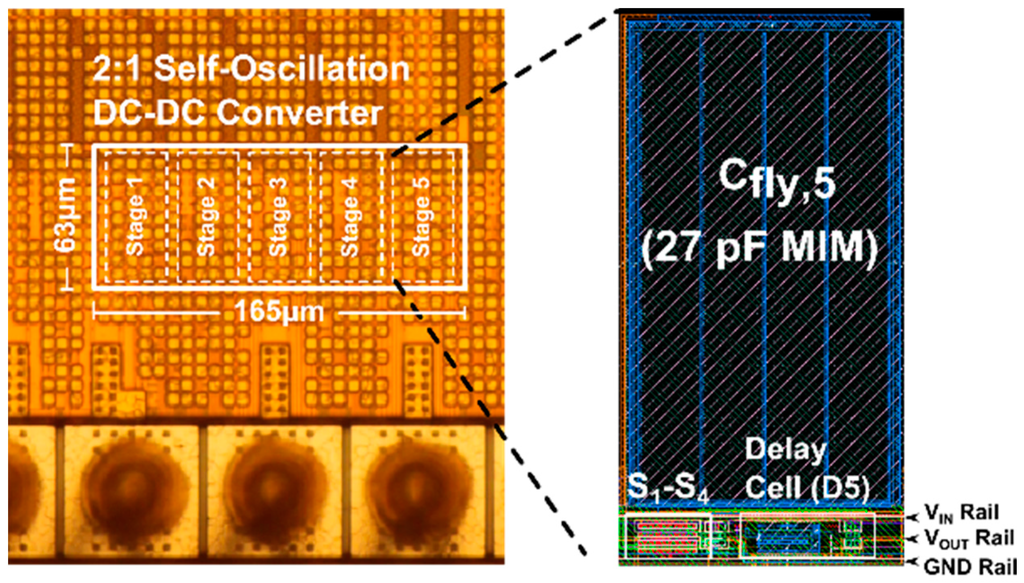

Measurement results from the 28 nm UTBB FD-SOI test chip are presented in this section. As shown in the annotated microphotograph of the test chip (Figure 6), all blocks within the converter are placed into a standard cell frame consisting of three power rails. This block organization simplifies the power routing and back-gate bias well connections between the five stages. The total area of the converter is 0.0104 mm2. The back-gate bias well area increases the total converter area by 3.7%.

Figure 6.

Annotated microphotograph of the 2:1 converter.

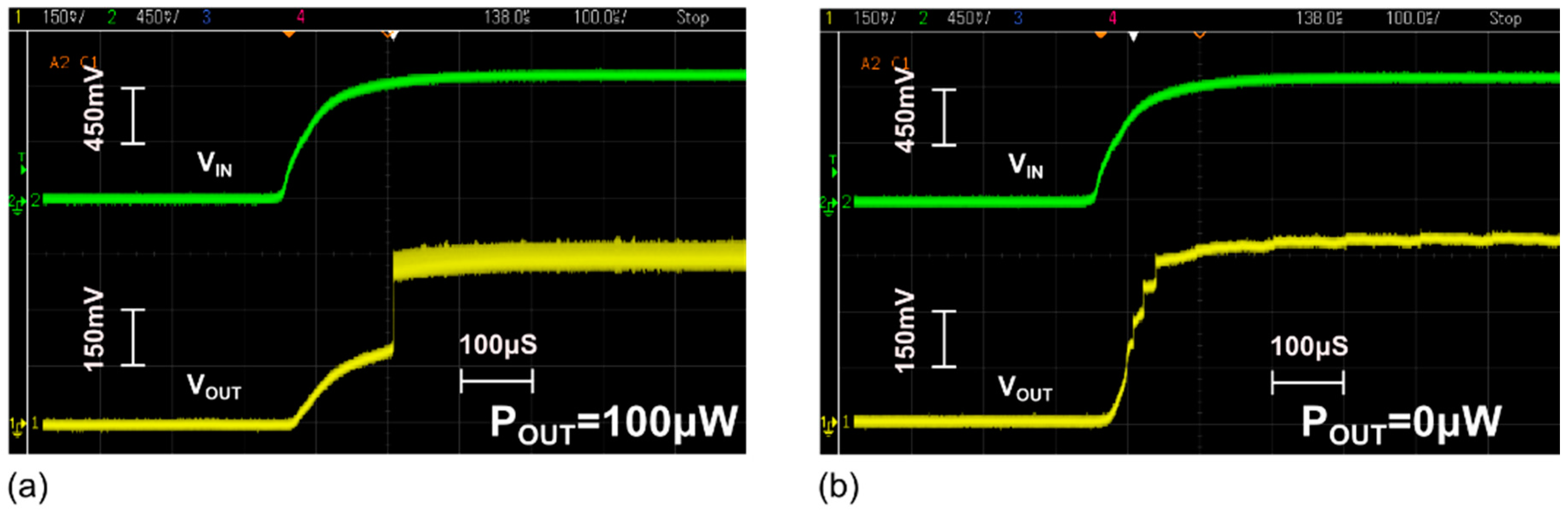

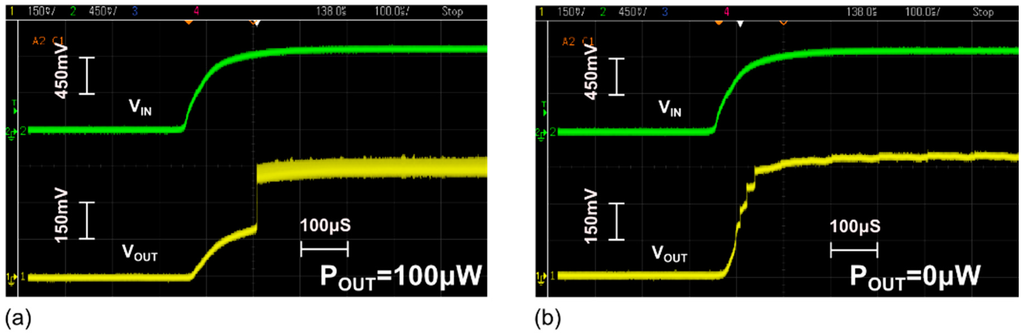

Due to the stacked ring oscillators, the self-oscillating converter is able to start-up without any auxiliary start-up control circuitry. Removing this control circuitry is especially beneficial in terms of efficiency at nW load powers (e.g., standby mode). A measurement of the converter at start-up is shown in Figure 7. An input voltage (VIN) is stepped from 0 V to 1 V using the maximum slew-rate of an off-chip voltage source. For both output power levels (POUT = 0 µW and POUT = 100 µW), the converter stabilizes at approximately the same time that VIN reaches 1 V. At POUT = 0 µW, the power consumption of the DC–DC converter is 15.6 nW.

Figure 7.

Measured start-up of the self-oscillating converter as VIN is increased from 0 V to 1 V at (a) POUT = 100 µW and (b) POUT = 0 µW.

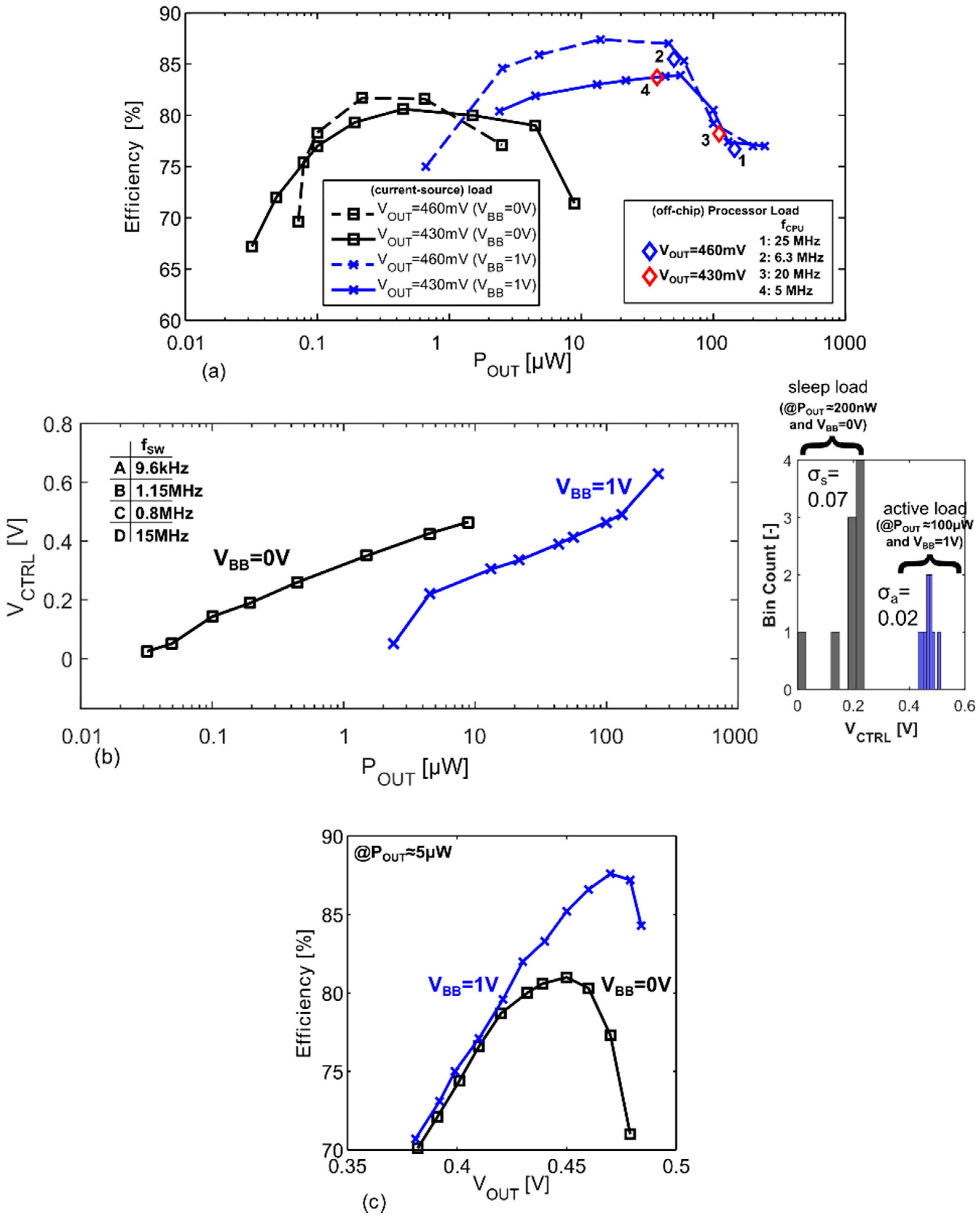

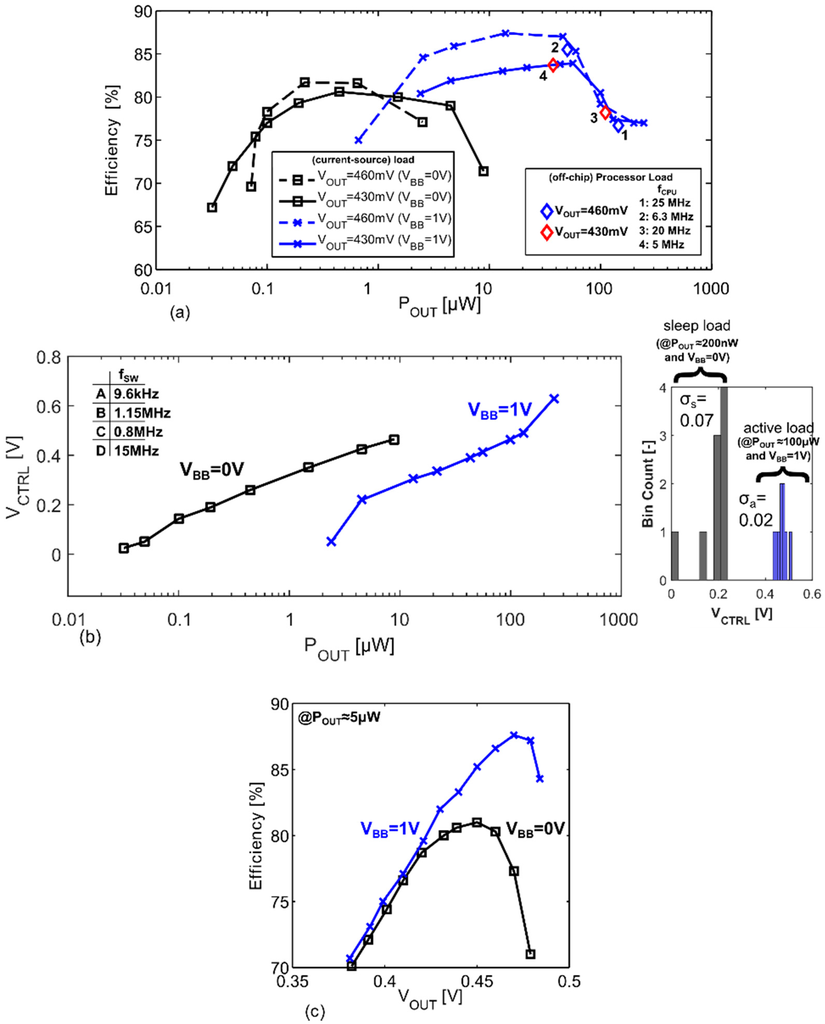

The converter’s efficiency versus the output load power (POUT) is shown in Figure 8a. The efficiency is measured at two near-threshold output voltages (VOUT = 430 mV and VOUT = 460 mV). The converter’s load power range is extended significantly by applying a back-gate bias of VBB = 1 V (i.e., PMOS back-gate biased with −1 V and NMOS with 1 V). The 1 V is generated from VIN, while the −1 V is from an off-chip voltage source. Negative body bias generators can produce −1 V with nW power consumption [14], and thus, have minimal impact on efficiency at µW load power. At VOUT = 460 mV, and using VBB = 1 V, the converter achieves a minimum efficiency of 75% for 79 nW to 200 µW (current source). With an off-chip 32-bit processor load, the converter’s efficiency closely matches the efficiency of the (current source) test load. With the processor load at fCPU = 6 MHz, the converter operates with a peak efficiency of 86%. The processor’s load power is adjusted by changing the operation frequency of the processor load (fCPU) over a range of 5 MHz to 25 MHz.

Figure 8.

Measurement results of the 2:1 converter; (a) Efficiency vs. load power; (b) VCTRL vs. load power at VOUT = 430 mV and the standard deviation of VCTRL at a sleep load power of 200 nW and an active load power of 100 µW from nine test chips; (c) Efficiency at POUT ≈ 5 µW.

To adjust for changes in the load, the control voltage (VCTRL) needs to be adjusted. Figure 8b shows the control voltage (VCTRL) required to tune the converter’s oscillation frequency (fSW) in order to achieve the efficiencies shown previously in Figure 8a. At VBB = 0 V, increasing the VCTRL is effective in increasing the POUT up to approximately 5 µW. At POUT = 5 µW, the drive strength of the charge-transfer is limited with VBB = 0 V. Moving to larger POUT (>5 µW) requires the back-gate biasing to be increased to VBB = 1 V. The measured results of nine test chips in Figure 8b show the distribution of VCTRL required to meet a sleep (POUT ≈ 200 nW) and an active load (POUT ≈ 100 µW). The standard deviation of VCTRL at the larger load power (i.e., active load) is a result of the larger VBB (i.e., 1 V). Increasing VBB decreases the transistors Vth. For a fixed VGS, a lower Vth results in an increased inversion level within the (leakage-based) delay cell transistors. As a result, VCTRL is less sensitive to intra-die variations at the active load. The VCTRL is adjusted using an off-chip voltage source; adding closed-loop control circuitry of VCTRL to meet load power demands has minimal impact on conversion efficiency [8], even by the lowest load power supported in this work (i.e., 79 nW).

The efficiency of the converter as a function of VOUT at POUT = 5 µW is shown in Figure 8c. The output impedance of the converter is reduced by increasing VBB to 1 V. A large VBB increases the switching frequency and drive strength of the charge-transfer switches. This allows for the converter to achieve larger values of VOUT before efficiency tapers off. At VBB = 0 V and VBB = 1 V, the peak efficiency is at VOUT = 0.45 V and VOUT = 0.47 V, respectively.

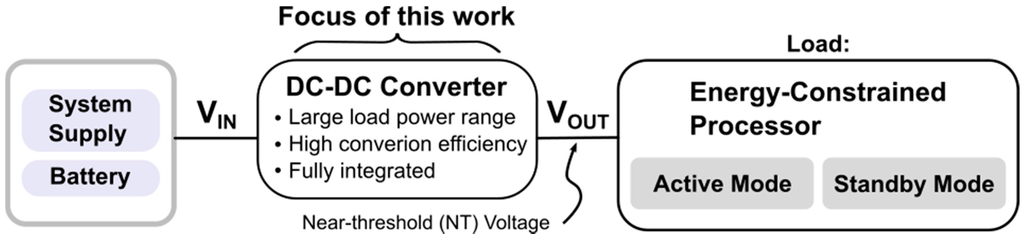

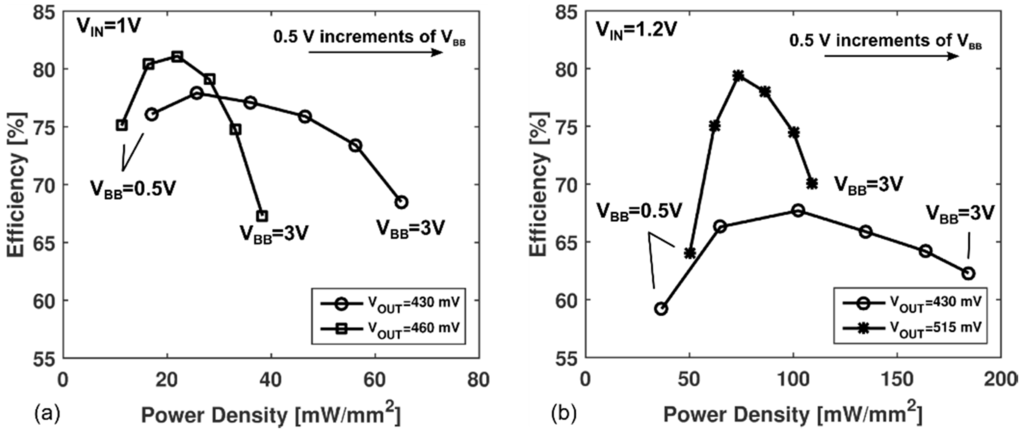

In addition to achieving high efficiencies, the converter needs to have high power density (mW/mm2) in order to be a cost-effective fully integrated solution. Achieving high power density in converters that operate with below-threshold voltage levels is challenging to the low overdrive voltages of the charge-transfer switches [15]. State-of-the-art power densities for DC–DC converters with near-threshold output voltages are between 2 and 20 mW/mm2. By using a self-oscillating converter topology with back-gate biasing, the power density can be significantly improved over the state-of-the-art. The measured power density of the converter for multiple back-gate bias voltages is shown in Figure 9. The power density of the converter can be increased by applying a larger VBB. At VIN = 1 V, the maximum power density is 65 mW/mm2. At VIN = 1.2 V, the maximum power density is 184 mW/mm2. The maximum power density is larger at VIN = 1.2 V since there is a larger overdrive on all the switches within the top ring oscillator (switches S1 and S2) of the converter. The larger overdrive voltage allows for a larger output current to be driven through the switches, thus giving a larger power density.

Figure 9.

Measurement results of efficiency vs. power density for increasing back-gate bias voltages at (a) VIN = 1 V and (b) VIN = 1.2 V.

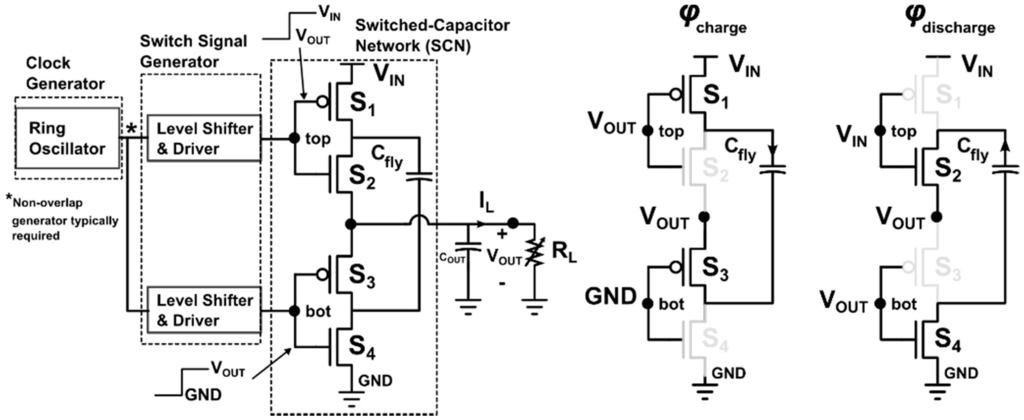

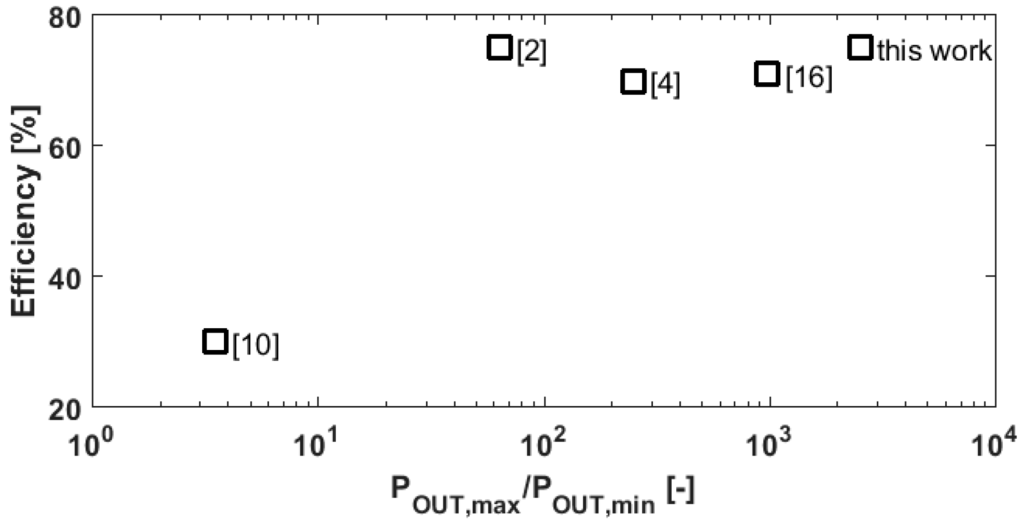

The converter is compared to state-of-the-art SC DC–DC converters in Table 1. The converter from [16] achieves the closest load range performance to the proposed converter, but at a lower power density. The converter in [5] has the closest power density, but it has a much smaller load range. Additionally, the size of COUT in [5] is not reported. The proposed converter does not use any additional on- or off-chip COUT and maintains a ripple ≤10% of VOUT. In relation to others, the proposed converter has a higher power density and is able to achieve a high minimum efficiency over a larger load power range as highlighted in Figure 10. The load power range is defined as the maximum (POUT,max) and minimum (POUT,min) load power levels at the output of the DC–DC converter.

Table 1.

Comparison of the self-oscillating 2:1 converter with state-of-the-art SC DC–DC converters.

Figure 10.

Comparison to state-of-the-art in terms of efficiency and load range (POUTmax/POUTmin).

4. Conclusions

A fully integrated step-down self-oscillating switched-capacitor DC–DC converter was presented. The converter was fabricated in 28 nm UTBB FD-SOI. The self-oscillating topology and utilization of back-gate biasing allowed the converter to achieve high efficiency over a large load power range. A minimum efficiency of 75% for 79 nW to 200 µW loads was achieved. Similar efficiency results were achieved with an off-chip processor in active mode. The converter’s peak efficiency with an off-chip processor load is 86% at VOUT = 460 mV. The power density is over 60 mW/mm2 with back-gate biasing of VBB ≥ 1 V. The large load power range, high power density, and high efficiency make the proposed converter an excellent match for near-threshold energy-constrained processors.

Acknowledgments

Academy of Finland #270585, Almari EU grant #621439, T.I.F.C.F., and the (former) Graduate School in Electronics, Telecommunications and Automation.

Author Contributions

Matthew Turnquist designed the reported DC–DC converter, performed the circuit analysis, and wrote the manuscript. Markus Hiienkari assisted in the measurements. Jani Mäkipää and Markus Hiienkari reviewed the manuscript. Lauri Koskinen supervised the work and contributed to the idea.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Hiienkari, M.; Teittinen, J.; Koskinen, L.; Turnquist, M.; Kaltiokallio, M. A 3.15pj/cyc 32-bit RISC CPU with timing-error prevention and adaptive clocking in 28 nm CMOS. In Proceedings of the 2014 IEEE Custom Integrated Circuits Conference (CICC), San Jose, CA, USA, 15–17 September 2014; pp. 1–4.

- Bol, D.; Vos, J.; Hocquet, C.; Botman, F.; Durvaux, F.; Boyd, S.; Flandre, D.; Legat, J. A 25-MHz 0.4-V Sub-mm2 7-µW/MHz Microcontroller in 65-nm LP/GP CMOS for Low-Carbon Wireless Sensor Nodes. IEEE J. Solid-State Circuits 2013, 48, 20–32. [Google Scholar] [CrossRef]

- Hanson, S.; Seok, M.; Lin, Y.-S.; Foo, Z.; Kim, D.; Lee, Y.; Liu, N.; Sylvester, D.; Blaauw, D. A Low-Voltage Processor for Sensing Applications with Picowatt Standby Mode. IEEE J. Solid-State Circuits 2009, 44, 1145–1155. [Google Scholar] [CrossRef]

- Kwong, J.; Ramadass, Y.K.; Verma, N.; Chandrakasan, A.P. A 65 nm Sub-Vt Microcontroller with Integrated SRAM and Switched Capacitor DC–DC Converter. IEEE J. Solid-State Circuits 2009, 44, 115–126. [Google Scholar] [CrossRef]

- Clerc, S.; Saligane, M.; Abouzeid, F.; Cochet, M.; Daveau, J.-M.; Bottoni, C.; Bol, D.; De-Vos, J.; Zamora, D.; Coeffic, B.; et al. A 0.33 V/−40 °C process/temperature closed-loop compensation SoC embedding all-digital clock multiplier and DC–DC converter exploiting FDSOI 28nm back-gate biasing. In Proceedings of the IEEE International Solid State Circuits Conference (ISSCC), San Francisco, CA, USA, 22–26 February 2015; pp. 1–3.

- Seongjong, K.; Mingoo, S. Variation-Tolerant, Ultra-Low-Voltage Microprocessor with a Low-Overhead, Within-a-Cycle In-Situ Timing-Error Detection and Correction Technique. IEEE J. Solid-State Circuits 2015, 50, 1478–1490. [Google Scholar]

- Sarafianos, A.; Steyaert, M. Fully Integrated Wide Input Voltage Range Capacitive DC–DC Converters: The Folding Dickson Converter. IEEE J. Solid-State Circuits 2015, 50, 1560–1570. [Google Scholar] [CrossRef]

- Jung, W.; Oh, S.; Bang, S.; Lee, Y.; Sylvester, D.; Blaauw, D. A 3nW fully integrated energy harvester based on self-oscillating switched-capacitor DC–DC converter. In Proceedings of the IEEE International Solid State Circuits Conference (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 398–399.

- Turnquist, M.; Hiienkari, M.; Mýkipýý, J.; Koskinen, L. A fully integrated self-oscillating switched-capacitor DC–DC converter for near-threshold loads. In Proceedings of the 2015 IEEE Asian Solid-State Circuit Conference (A-SSCC), Xiamen, China, 9–11 November 2015; pp. 1–4.

- Wieckowski, M.; Chen, G.K.; Seok, M.; Blaauw, D.; Sylvester, D. A hybrid DC–DC converter for sub-microwatt sub-1V implantable applications. In Proceedings of the 2009 Symposium on VLSI Circuits (VLSIC), Kyoto, Japan, 16–18 June 2009; pp. 166–167.

- Turnquist, M.; de Streel, G.; Bol, D.; Hiienkari, M. Effects of back-gate bias on switched-capacitor DC–DC converters in UTBB FD-SOI. In Proceedings of the 2014 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Millbrae, CA, USA, 6–9 October 2014; pp. 1–2.

- Jacquet, D.; Hasbani, F.; Flatresse, P.; Wilson, R.; Arnaud, F.; Cesana, G.; Di Gilio, T.; Lecocq, C.; Roy, T.; Chhabra, A.; et al. A 3 GHz Dual Core Processor ARM Cortex TM -A9 in 28 nm UTBB FD-SOI CMOS with Ultra-Wide Voltage Range and Energy Efficiency Optimization. IEEE J. Solid-State Circuits 2014, 49, 812–826. [Google Scholar] [CrossRef]

- Seeman, M.D.; Sanders, S. Analysis and Optimization of Switched-Capacitor DC–DC Converters. IEEE Trans. Power Electron. 2008, 23, 841–850. [Google Scholar] [CrossRef]

- Pique, G.V.; Meijer, M. A 350nA voltage regulator for 90nm CMOS digital circuits with Reverse-Body-Bias. In Proceedings of the 2011 European Solid-State Circuit Conference (ESSIRC), Helsinki, Finland, 12–16 September 2011; pp. 379–382.

- Zimmer, B.; Lee, Y.; Puggelli, A.; Kwak, J.; Jevtic, R.; Keller, B.; Bailey, S.; Blagojevic, M.; Chiu, P.-F.; Le, H.-P.; et al. A RISC-V vector processor with tightly-integrated switched-capacitor DC–DC converters in 28 nm FDSOI. In Proceedings of the 2015 Symposium on VLSI Circuits (VLSIC), Kyoto, Japan, 17–19 June 2015; pp. C316–C317.

- Turnquist, M.; Hiienkari, M.; Mäkipää, J.; Jevtic, R.; Koskinen, L. Fully integrated DC–DC converter and a 0.4 V 32-bit CPU with timing-error prevention supplied from a prototype 1.55 V Li-ion battery. In Proceedings of the 2015 Symposium on VLSI Circuits (VLSIC), Kyoto, Japan, 17–19 June 2015; pp. C320–C321.

© 2016 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC-BY) license (http://creativecommons.org/licenses/by/4.0/).