A CMOS Switched Capacitor Filter Based Potentiometric Readout Circuit for pH Sensing System

Abstract

1. Introduction

2. Design of Readout Circuit

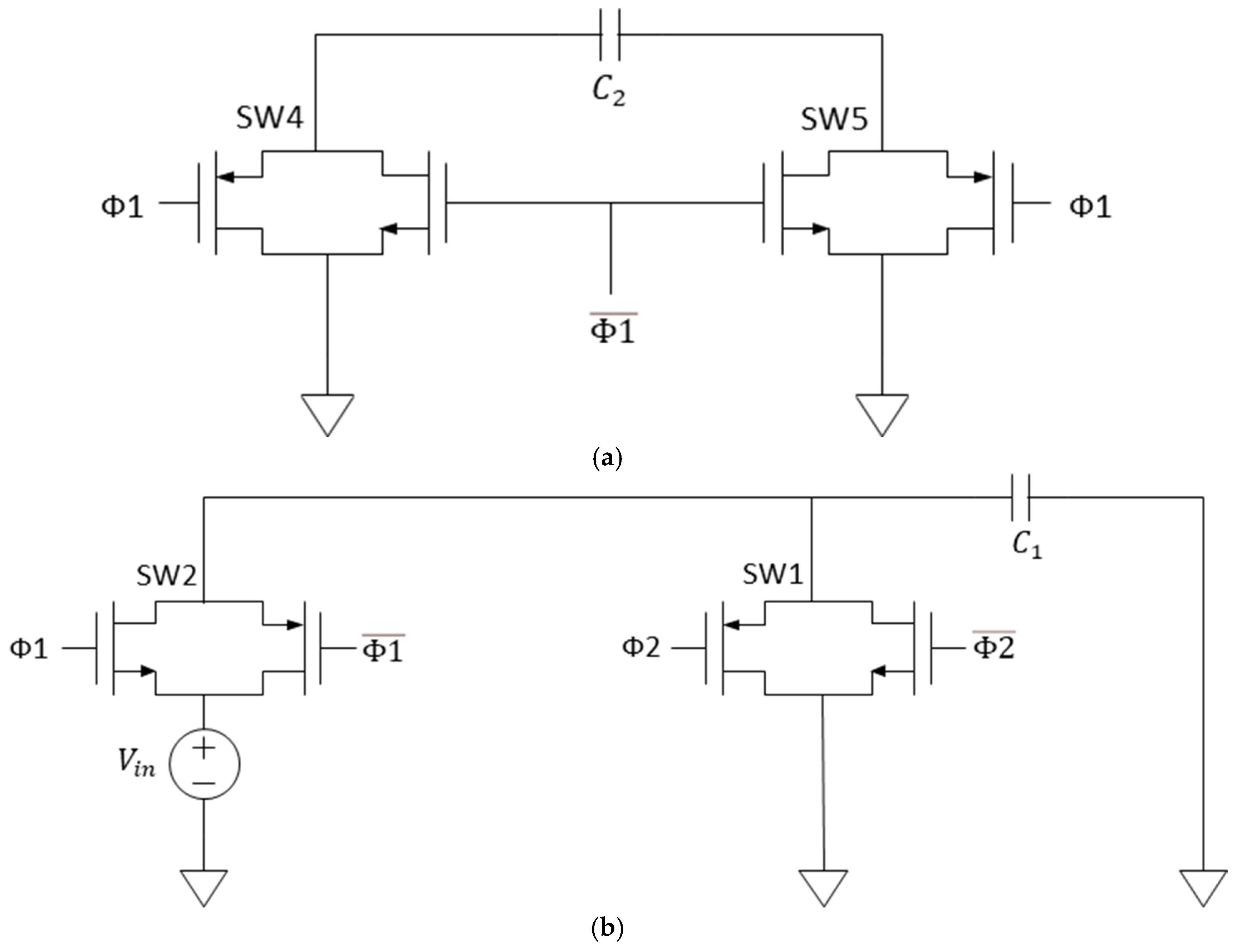

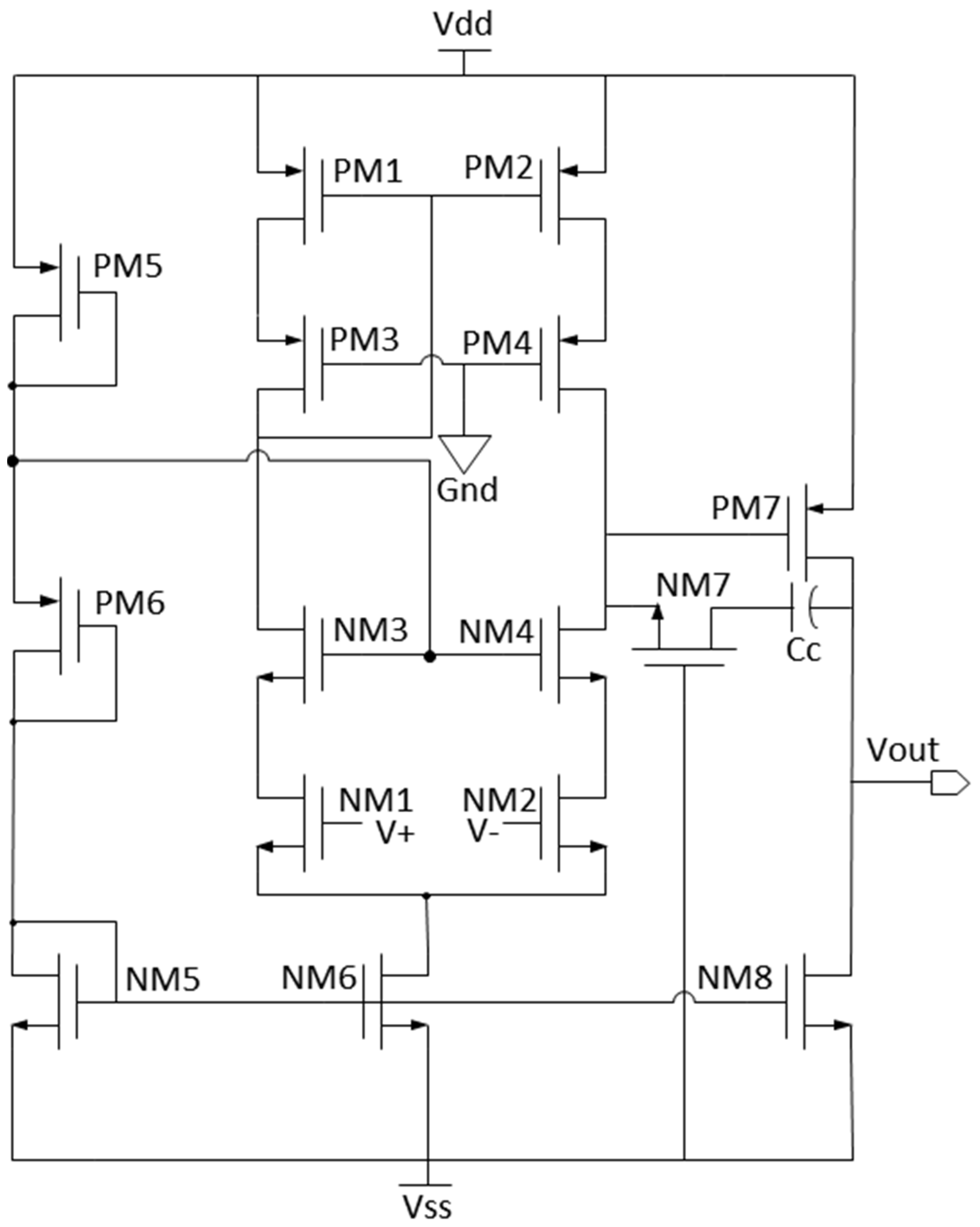

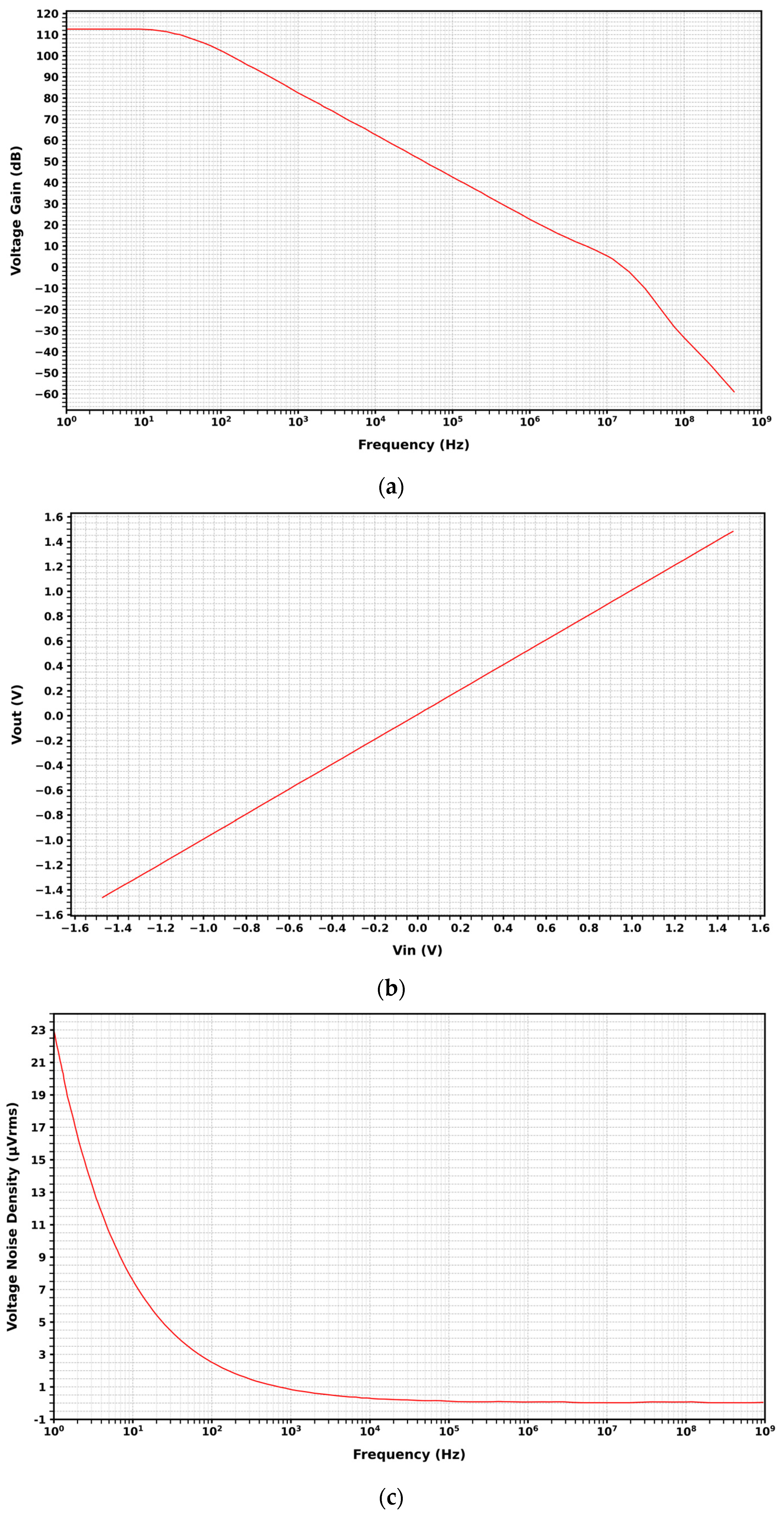

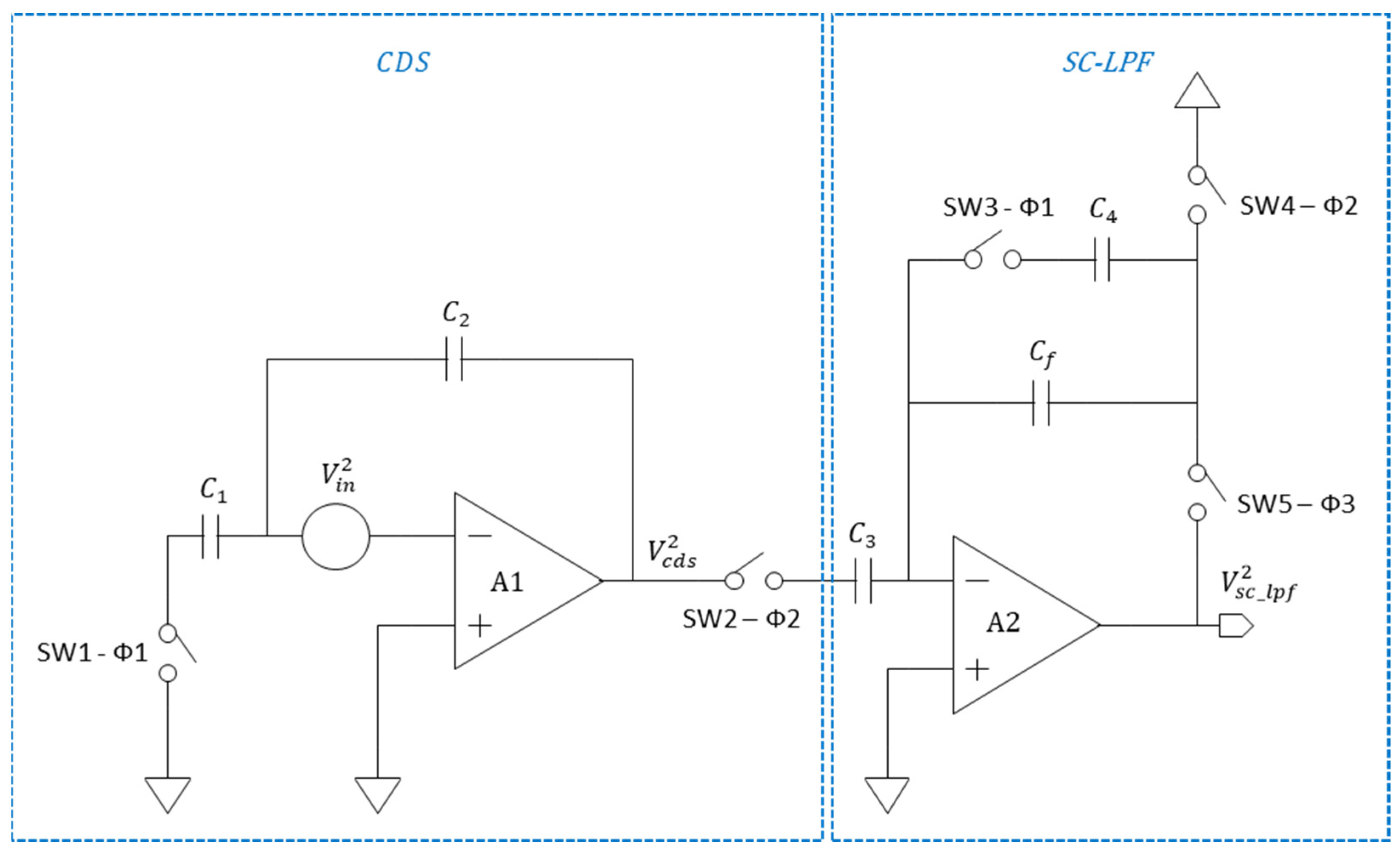

2.1. CMOS Correlated Double Sampler

2.2. CMOS Correlated Double Sampler Followed by Switched Capacitor LPF

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Wencel, D.; Abel, T.; McDonagh, C. Optical Chemical PH Sensors. Anal. Chem. 2014, 86, 15–29. [Google Scholar] [CrossRef] [PubMed]

- Das, A.; Bhadri, P.; Beyette, F.R.; Jang, A.; Bishop, P.; Timmons, W. A Potentiometric Sensor System with Integrated Circuitry for in Situ Environmental Monitoring. In Proceedings of the 2006 Sixth IEEE Conference on Nanotechnology, Cincinnati, OH, USA, 17–20 July 2006. [Google Scholar]

- Pan, C.-W.; Chou, J.-C.; Sun, T.-P.; Hsiung, S.-K. Development of the Real-Time PH Sensing System for Array Sensors. Sens. Actuators B Chem. 2005, 108, 870–876. [Google Scholar] [CrossRef]

- Punjiya, M.; Rezaei, H.; Zeeshan, M.A.; Sonkusale, S. A Flexible PH Sensing Smart Bandage with Wireless CMOS Readout for Chronic Wound Monitoring. In Proceedings of the 2017 19th International Conference on Solid-State Sensors, Actuators and Microsystems (TRANSDUCERS), Kaohsiung, Taiwan, 18–22 June 2017. [Google Scholar]

- Punjiya, M.; Nejad, H.R.; Mostafalu, P.; Sonkusale, S. PH Sensing Threads with CMOS Readout for Smart Bandages. In Proceedings of the 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, USA, 28–31 May 2017. [Google Scholar]

- Huang, X.; Yu, H.; Liu, X.; Jiang, Y.; Yan, M.; Wu, D. A Dual-Mode Large-Arrayed CMOS ISFET Sensor for Accurate and High-Throughput PH Sensing in Biomedical Diagnosis. IEEE Trans. Biomed. Eng. 2015, 62, 2224–2233. [Google Scholar] [CrossRef] [PubMed]

- Tamayol, A.; Akbari, M.; Zilberman, Y.; Comotto, M.; Lesha, E.; Serex, L.; Bagherifard, S.; Chen, Y.; Fu, G.; Ameri, S.K.; et al. PH-sensing Hydrogel Fibers: Flexible PH-sensing Hydrogel Fibers for Epidermal Applications (Adv. Healthcare Mater. 6/2016). Adv. Healthc. Mater. 2016, 5, 624. [Google Scholar] [CrossRef]

- Pourcielgouzy, M.; Assiesouleille, S.; Mazenq, L.; Launay, J.; Templeboyer, P. PH-ChemFET-Based Analysis Devices for the Bacterial Activity Monitoring. Sens. Actuators B Chem. 2008, 134, 339–344. [Google Scholar] [CrossRef]

- Ghoneim, M.T.; Nguyen, A.; Dereje, N.; Huang, J.; Moore, G.C.; Murzynowski, P.J.; Dagdeviren, C. Recent Progress in Electrochemical PH-Sensing Materials and Configurations for Biomedical Applications. Chem. Rev. 2019, 119, 5248–5297. [Google Scholar] [CrossRef]

- Baliga, S.; Muglikar, S.; Kale, R. Salivary PH: A Diagnostic Biomarker. J. Indian Soc. Periodontol. 2013, 17, 461. [Google Scholar] [CrossRef]

- Golan, R.; Gavrieli, I.; Lazar, B.; Ganor, J. The Determination of PH in Hypersaline Lakes with a Conventional Combination Glass Electrode. Limnol. Oceanogr. Methods 2014, 12, 810–815. [Google Scholar] [CrossRef]

- Veselinovic, D.; Velikic, Z. The PH Measurement with Glass Electrode in an Electromagnetic Field. J. Serb. Chem. Soc. 2016, 81, 1407–1414. [Google Scholar] [CrossRef]

- Anes, B.; Bettencourt da Silva, R.J.N.; Oliveira, C.; Camões, M.F. Seawater PH Measurements with a Combination Glass Electrode and High Ionic Strength TRIS-TRIS HCl Reference Buffers—An Uncertainty Evaluation Approach. Talanta 2019, 193, 118–122. [Google Scholar] [CrossRef]

- Chin, Y.-L.; Chou, J.-C.; Sun, T.-P.; Chung, W.-Y.; Hsiung, S.-K. A Novel PH Sensitive ISFET with on Chip Temperature Sensing Using CMOS Standard Process. Sens. Actuators B Chem. 2001, 76, 582–593. [Google Scholar] [CrossRef]

- Chung, W.-Y.; Lin, Y.-T.; Pijanowska, D.G.; Yang, C.-H.; Wang, M.-C.; Krzyskow, A.; Torbicz, W. New ISFET Interface Circuit Design with Temperature Compensation. Microelectronics 2006, 37, 1105–1114. [Google Scholar] [CrossRef]

- Bergveld, P. Thirty Years of ISFETOLOGY. Sens. Actuators B Chem. 2003, 88, 1–20. [Google Scholar] [CrossRef]

- Janata, J.; Josowicz, M. Organic Semiconductors in Potentiometric Gas Sensors. J. Solid State Electrochem. 2009, 13, 41–49. [Google Scholar] [CrossRef]

- Abdullah, M.F.; Adnan, M.A.; Aziz, M.G.A.; Hussein, Z.; Noor, M.H.M.; Azman, K.A.; Madzhi, N.K. A Comparative Study on Low Noise Precision Difet Operational Amplifier and Low Noise Operational Amplifier for Potentiometric Transduction Circuit. In Proceedings of the 2013 IEEE Business Engineering and Industrial Applications Colloquium (BEIAC), Langkawi, Malaysia, 7–9 April 2013. [Google Scholar]

- Bembnowicz, P.; Yang, G.-Z.; Anastasova, S.; Spehar-Deleze, A.-M.; Vadgama, P. Wearable Electronic Sensor for Potentiometric and Amperometric Measurements. In Proceedings of the 2013 IEEE International Conference on Body Sensor Networks, Cambridge, MA, USA, 6–9 May 2013. [Google Scholar]

- Adimulam, M.K.; Divya, A.; Tejaswi, K.; Srinivas, M.B. A Low Power, Low Noise Programmable Analog Front End (PAFE) for Biopotential Measurements. In Proceedings of the 2017 39th Annual International Conference of the IEEE Engineering in Medicine and Biology Society (EMBC), Jeju, Republic of Korea, 11–15 July 2017. [Google Scholar]

- Farouk, T.; Elkhatib, M.; Dessouky, M. A 1V Low-Power Low-Noise Biopotential Amplifier Based on Flipped Voltage Follower. In Proceedings of the 2015 IEEE International Conference on Electronics, Circuits, and Systems (ICECS), Cairo, Egypt, 6–9 December 2015. [Google Scholar]

- Park, H.; Lakshminarayana, S.; Pan, C.; Chung, H.-J.; Jung, S. An Auto Adjustable Transimpedance Readout System for Wearable Healthcare Devices. Electronics 2022, 11, 1181. [Google Scholar] [CrossRef]

- Krishnamurthy, H.K.; Robinson, D.; Rector, D.M.; La Rue, G.S. A Low Noise Low Power DC Coupled Sensor Amplifier with Offset Cancellation. In Proceedings of the 2010 IEEE Workshop on Microelectronics and Electron Devices, Boise, ID, USA, 16 April 2010. [Google Scholar]

- Chung, W.-Y.; Silverio, A.A.; Tsai, V.F.S.; Cheng, C.; Chang, S.-Y.; Zhou, M.-Y.; Kao, C.-Y.; Rustia, D.A.; Lo, Y.-W. Design of a Multi-Sensor Readout Chip for Amperometric, Potentiometric, Impedometric, and Colorimetric Bio-Sensor Applications. In Proceedings of the 2017 International Conference on Applied System Innovation (ICASI), Sapporo, Japan, 13–17 May 2017. [Google Scholar]

- Dubey, D.; Gupta, A. A Low Power Low Noise Amplifier for Biomedical Applications. In Proceedings of the 2015 IEEE International Conference on Electrical, Computer and Communication Technologies (ICECCT), Coimbatore, India, 5–7 March 2015. [Google Scholar]

- Kuo, P.-Y.; Chen, Y.-Y. A Novel Low Unity-Gain Frequency and Low Power Consumption Instrumentation Amplifier Design for RuO2 Uric Acid Biosensor Measurement. IEEE Trans. Instrum. Meas. 2021, 70, 4003409. [Google Scholar] [CrossRef]

- Wang, Z.; Keeble, L.; Moser, N.; Lande, T.S.; Georgiou, P. A Dual-Sensing CMOS Array for Combined Impedance-PH Detection of DNA with Integrated Electric Field Manipulation. In Proceedings of the 2021 IEEE International Symposium on Circuits and Systems (ISCAS), Daegu, Republic of Korea, 22–28 May 2021. [Google Scholar]

- Silverio, A.A.; Chung, W.-Y.; Tsai, V.F.S.; Cheng, C. Multi-Parameter Readout Chip for Interfacing with Amperometric, Potentiometric and Impedometric Sensors for Wearable and Point-of-Care Test Applications. Microelectronics 2020, 100, 104769. [Google Scholar] [CrossRef]

- Taheri, H.E.; Mirhassani, M. A Low-Power, High-Resolution, Adaptive Sensitivity Readout Circuit with Selective Detection Range for Capacitive Biosensors. Int. J. Electron. Commun. 2021, 131, 153599. [Google Scholar] [CrossRef]

- Springer, E.K. PH Measurement Guide. Available online: https://separations.co.za/wp-content/uploads/2014/09/pH-Measurement-Guide.pdf (accessed on 27 June 2024).

- Available online: https://www.ti.com/lit/an/snoa529a/snoa529a.pdf?ts=1652094714270 (accessed on 27 June 2024).

- Available online: https://www.hamiltoncompany.com/process-analytics/ph-and-orp-knowledge/ph-probe-operation-principles/slope-of-ph-sensor (accessed on 27 June 2024).

- Yan, L.; Georgiou, P.; Constandinou, T.G.; Garner, D.; Toumazou, C. An Auto-Offset-Removal Circuit for Chemical Sensing Based on the PG-ISFET. In Proceedings of the 2009 IEEE International Symposium on Circuits and Systems, Taipei, China, 24–27 May 2009. [Google Scholar]

- Liu, Y.; Toumazou, C. An ISFET Based Sensing Array with Sensor Offset Compensation and PH Sensitivity Enhancement. In Proceedings of the Proceedings of 2010 IEEE International Symposium on Circuits and Systems, Paris, France, 30 May–2 June 2010. [Google Scholar]

- Chen, M.-C.; Chen, H.-Y.; Lin, C.-Y.; Tsai, C.-M.; Hsieh, C.-F.; Horng, J.-T.; Qiu, J.-T.; Huang, C.-C.; Yang, F.-L. A Novel Smart Nanowire Biosensor with Hybrid Sensor/Memory/CMOS Technology. In Proceedings of the 2010 International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010. [Google Scholar]

- Lee, T.-H.; Cho, G.; Kim, H.J.; Lee, S.W.; Lee, W.; Han, S.H. Analysis of 1/f Noise in CMOS Preamplifier with CDS Circuit. IEEE Trans. Nucl. Sci. 2002, 49, 1819–1823. [Google Scholar] [CrossRef]

- Belloni, M.; Bonizzoni, E.; Fornasari, A.; Maloberti, F. A Micropower Chopper—CDS Operational Amplifier. IEEE J. Solid-State Circuits 2010, 45, 2521–2529. [Google Scholar] [CrossRef]

- Enz, C.C.; Temes, G.C. Circuit Techniques for Reducing the Effects of Op-Amp Imperfections: Autozeroing, Correlated Double Sampling, and Chopper Stabilization. Proc. IEEE Inst. Electr. Electron. Eng. 1996, 84, 1584–1614. [Google Scholar] [CrossRef]

- Gray, P.R.; Hurst, P.J.; Lewis, S.H.; Meyer, R.G. Analysis and Design of Analog Integrated Circuits, 6th ed.; John Wiley & Sons: Nashville, TN, USA, 2024; ISBN 9781394220069. [Google Scholar]

- Carusone, T.C.; Johns, D.A.; Martin, K.W. Analog Integrated Circuit Design: International Student Version, 2nd ed.; John Wiley & Sons: Nashville, TN, USA, 2012; ISBN 9781118092330. [Google Scholar]

- Razavi, B. Design of Analog CMOS Integrated Circuits, 2nd ed.; McGraw-Hill Education: Columbus, OH, USA, 2016; ISBN 9781259255090. [Google Scholar]

- Available online: https://www.magnachip.com/magnachip-offers-automotive-grade-0-18-micron-bcd-process-technology-with-up-to-200v-operation-voltage/ (accessed on 6 January 2025).

- Prathap, V.; Titus, A.H. ISFET Pixel Array with Selectable Sensitivity and Bulk-Based Offset-Drift Nullification Capability for Reduction of Non-Ideality Effects. IEEE Sens. J. 2023, 23, 1827–1836. [Google Scholar] [CrossRef]

- Duan, M.; Zhong, X.; Zhao, X.; El-Agnaf, O.M.; Lee, Y.-K.; Bermak, A. An Optical and Temperature Assisted CMOS ISFET Sensor Array for Robust E. Coli Detection. IEEE Trans. Biomed. Circuits Syst. 2021, 15, 497–508. [Google Scholar] [CrossRef] [PubMed]

- Zeng, J.; Kuang, L.; Cacho-Soblechero, M.; Georgiou, P. An Ultra-High Frame Rate Ion Imaging Platform Using ISFET Arrays with Real-Time Compression. IEEE Trans. Biomed. Circuits Syst. 2021, 15, 820–833. [Google Scholar] [CrossRef]

| Symbol | Abbreviation |

|---|---|

| CDS | Correlated double sampler |

| SC-LPF | Switched-capacitor low-pass filter |

| OPAMP noise spectral density | |

| Input voltage noise | |

| Output noise of CDS | |

| Output noise of CDS with SC-LPF | |

| Transfer function of CDS | |

| Transfer function of CDS with SC-LPF | |

| Cutoff frequency of CDS | |

| Cutoff frequency of CDS with SC-LPF | |

| Input voltage of overall system | |

| Output voltage of overall system | |

| Input resistor | |

| Feedback resistor |

| Parameter | OPAMP | CDS | CDS with SC-LPF |

|---|---|---|---|

| Output noise ( | 260.8 µ | 1.4 µ | 0.683 µ |

| Power consumption (Watt) | 44.1 µ | 70.7 µ | 124.1 µ |

| Parameter | Temperature (°C) | Corner Frequency | Supply Voltage (V) | |||||||

|---|---|---|---|---|---|---|---|---|---|---|

| −40 | 27 | 80 | SS | FF | FS | SF | −1.55 to +1.55 | −1.65 to +1.65 | −1.85 to +1.85 | |

| Opamp DC swing (V) | −1.5 to +1.49 | −1.5 to +1.47 | −1.5 to +1.5 | −1.5 to +1.49 | −1.5 to +1.48 | −1.5 to +1.5 | −1.5 to +1.5 | −1.5 to +1.49 | −1.5 to +1.48 | −1.5 to +1.5 |

| Opamp noise ) | 236.8 | 260.8 | 282.5 | 308.8 | 200.9 | 296.6 | 246 | 290.7 | 260.8 | 207.1 |

| Opamp power (µW) | 24.32 | 44.1 | 61.13 | 19.71 | 83.6 | 33.29 | 56.7 | 25.14 | 44.1 | 85.65 |

| CDS DC swing (V) | −1.5 to +1.5 | −1.5 to +1.5 | −1.5 to +1.5 | −1.5 to +1.5 | −1.5 to +1.5 | −1.5 to +1.5 | −1.5 to +1.5 | −1.5 to +1.5 | −1.5 to +1.5 | −1.5 to +1.5 |

| CDS noise | 1.45 | 1.4 | 1.87 | 1.2 | 1.23 | 1.22 | 1.21 | 1.29 | 1.39 | 1.41 |

| CDS power (µW) | 40.15 | 70.7 | 96.8 | 32.6 | 130.4 | 53.7 | 90.6 | 40.6 | 70.7 | 135.3 |

| CDS with SC-LPF DC swing (V) | −1.5 to +1.5 | −1.5 to +1.5 | −1.5 to +1.5 | −1.5 to +1.5 | −1.5 to +1.5 | −1.5 to +1.5 | −1.5 to +1.5 | −1.5 to +1.5 | −1.5 to +1.5 | −1.5 to +1.5 |

| CDS with SC-LPF noise | 0.56 | 0.68 | 0.77 | 0.70 | 0.67 | 0.67 | 0.69 | 0.67 | 0.68 | 0.74 |

| CDS with SC-LPF power (µW) | 71.15 | 124.1 | 170.73 | 57.22 | 232 | 94.9 | 159.1 | 72 | 124 | 286.34 |

| Ref | Power (Watt) | Area (mm2) | Supply (V) | Technology (µm) | Application | |

|---|---|---|---|---|---|---|

| [23] | 900 µ | 991.1 µ | N/A | 1 | CMOS 0.18 | pH sensing |

| [24] | 1.67 m | N/A | N/A | 3.3 & 1.8 | CMOS 0.18 | pH sensing |

| [25] | 15.17 µ | 2.89 µ | N/A | 3 | CMOS 0.18 | ECG |

| [26] | 397.92 µ | N/A | 0.44 | 1.5 | CMOS 0.18 | Uric acid sensing |

| [27] | 3.43 m | 114 µ | 0.31 | 1.8 | CMOS 0.18 | pH sensing |

| [28] | 1.67 m | N/A | 1.44 | 1.8 | CMOS 0.18 | Multi-purpose |

| [29] | 6.6 μ | 26.89 μ | N/A | 1.8 | CMOS 0.18 | Capacitive sensing |

| [43] | 3 m | 1.22 m | 4 | 3.3 | CMOS 0.35 | pH sensing |

| [44] | 7.98 m | 6.57 m | 3.4 | 3.3 & 1.8 | CMOS 0.18 | pH sensing |

| [45] | 240 m | N/A | 4 | 1.8 | CMOS 0.18 | pH sensing |

| This work | 124.1 µ | 0.683 µ | 0.21 | ±1.65 | CMOS 0.18 | pH sensing |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lakshminarayana, S.; Perumalsamy, R.; Pan, C.; Jung, S.; Chung, H.-J.; Park, H. A CMOS Switched Capacitor Filter Based Potentiometric Readout Circuit for pH Sensing System. J. Low Power Electron. Appl. 2025, 15, 3. https://doi.org/10.3390/jlpea15010003

Lakshminarayana S, Perumalsamy R, Pan C, Jung S, Chung H-J, Park H. A CMOS Switched Capacitor Filter Based Potentiometric Readout Circuit for pH Sensing System. Journal of Low Power Electronics and Applications. 2025; 15(1):3. https://doi.org/10.3390/jlpea15010003

Chicago/Turabian StyleLakshminarayana, Shanthala, Revathy Perumalsamy, Chenyun Pan, Sungyong Jung, Hoon-Ju Chung, and Hyusim Park. 2025. "A CMOS Switched Capacitor Filter Based Potentiometric Readout Circuit for pH Sensing System" Journal of Low Power Electronics and Applications 15, no. 1: 3. https://doi.org/10.3390/jlpea15010003

APA StyleLakshminarayana, S., Perumalsamy, R., Pan, C., Jung, S., Chung, H.-J., & Park, H. (2025). A CMOS Switched Capacitor Filter Based Potentiometric Readout Circuit for pH Sensing System. Journal of Low Power Electronics and Applications, 15(1), 3. https://doi.org/10.3390/jlpea15010003