Electrical Characteristics and Stability Improvement of Top-Gate In-Ga-Zn-O Thin-Film Transistors with Al2O3/TEOS Oxide Gate Dielectrics

Abstract

1. Introduction

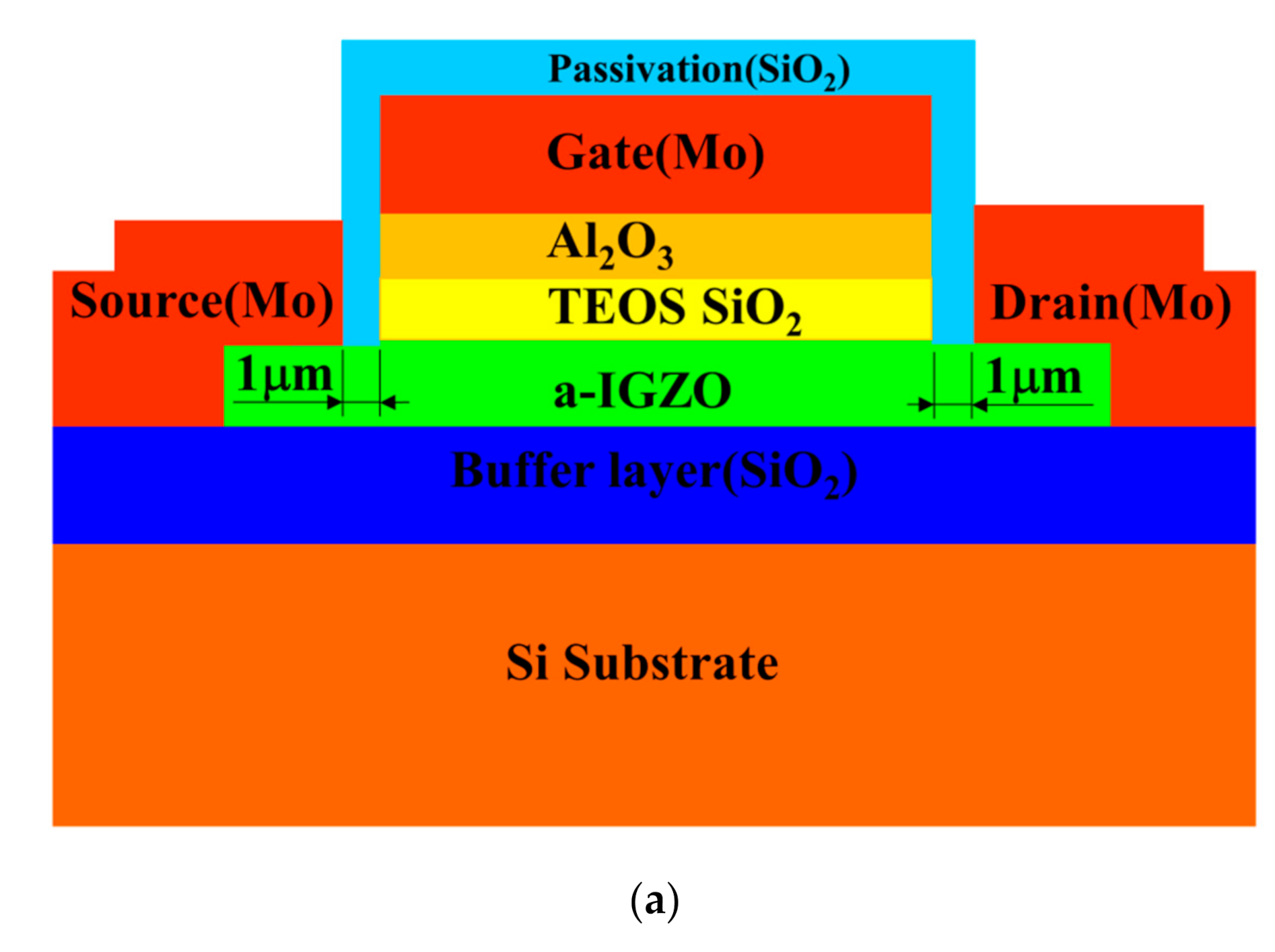

2. Experimental Methods

3. Results and Discussions

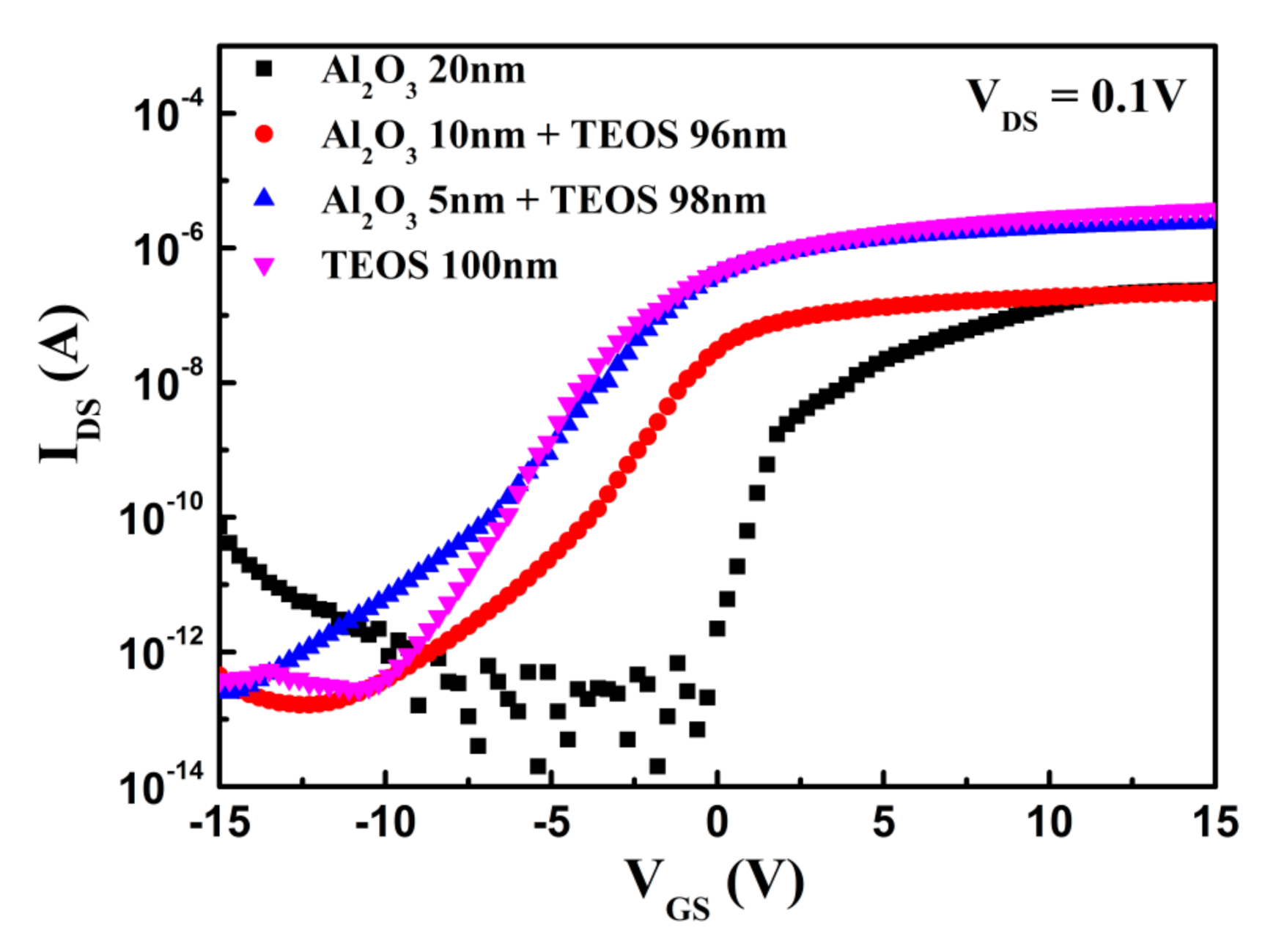

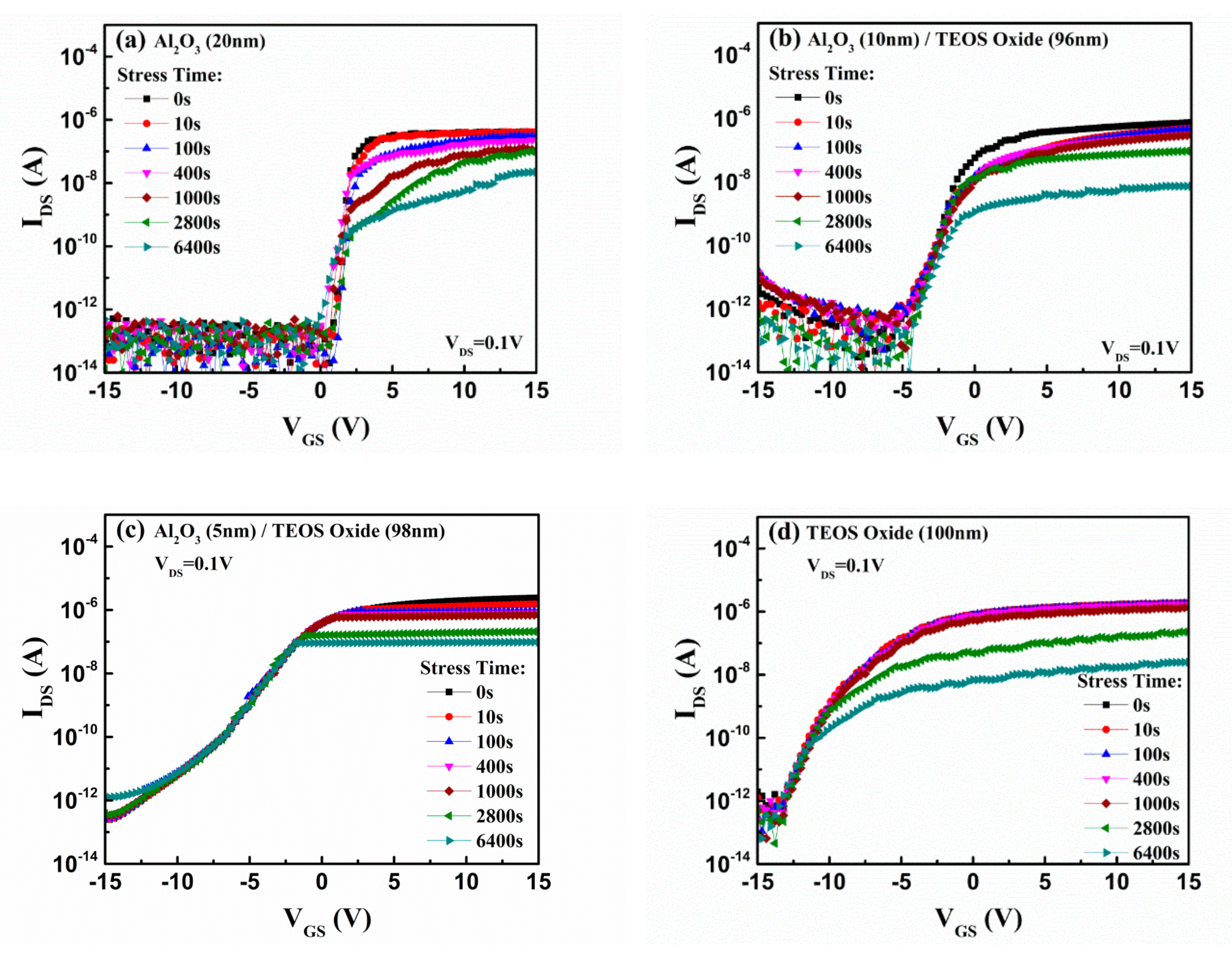

3.1. Electrical Characteristics of IGZO TFTs with Al2O3, Al2O3/TEOS Oxide, and TEOS Oxide Gate Dielectrics

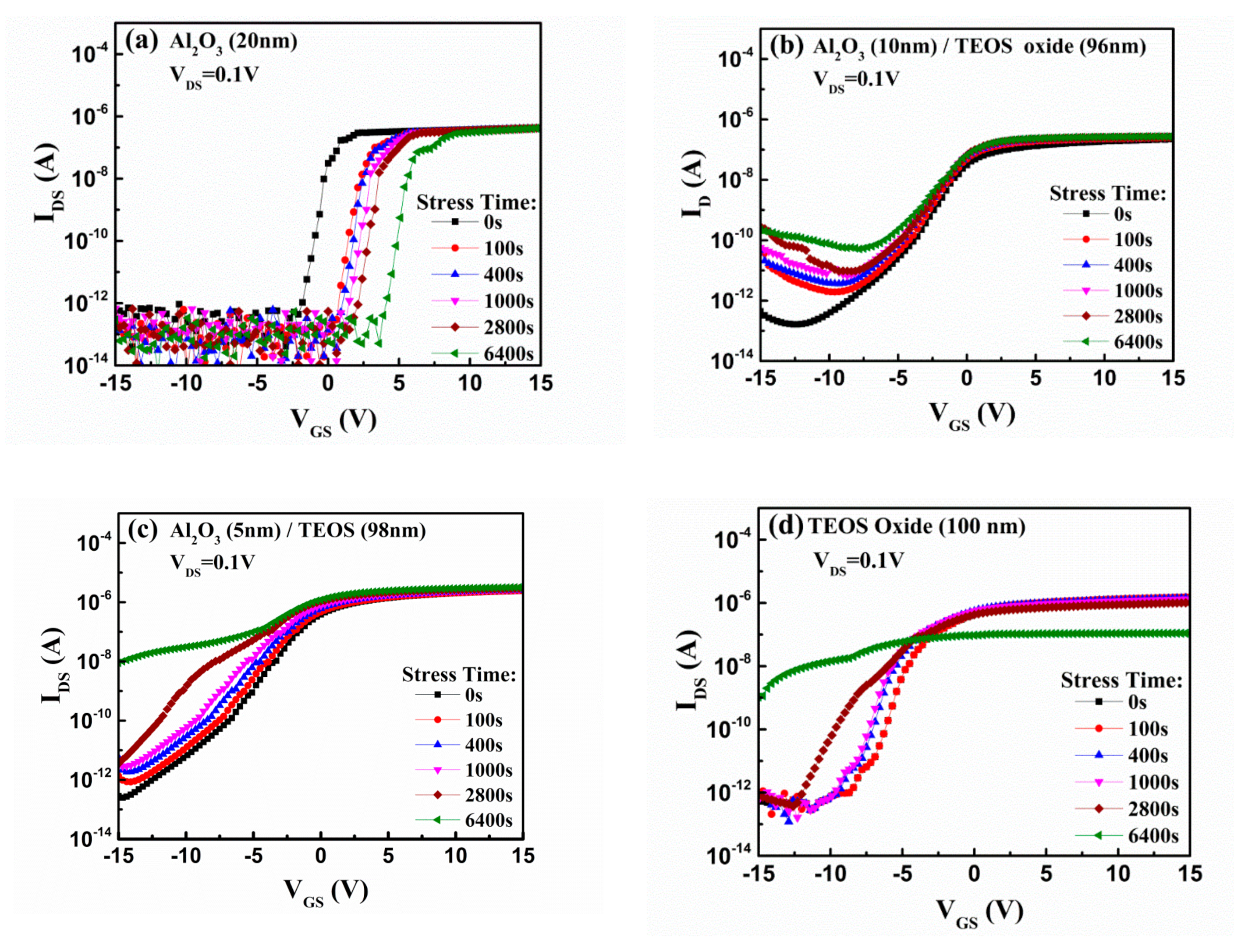

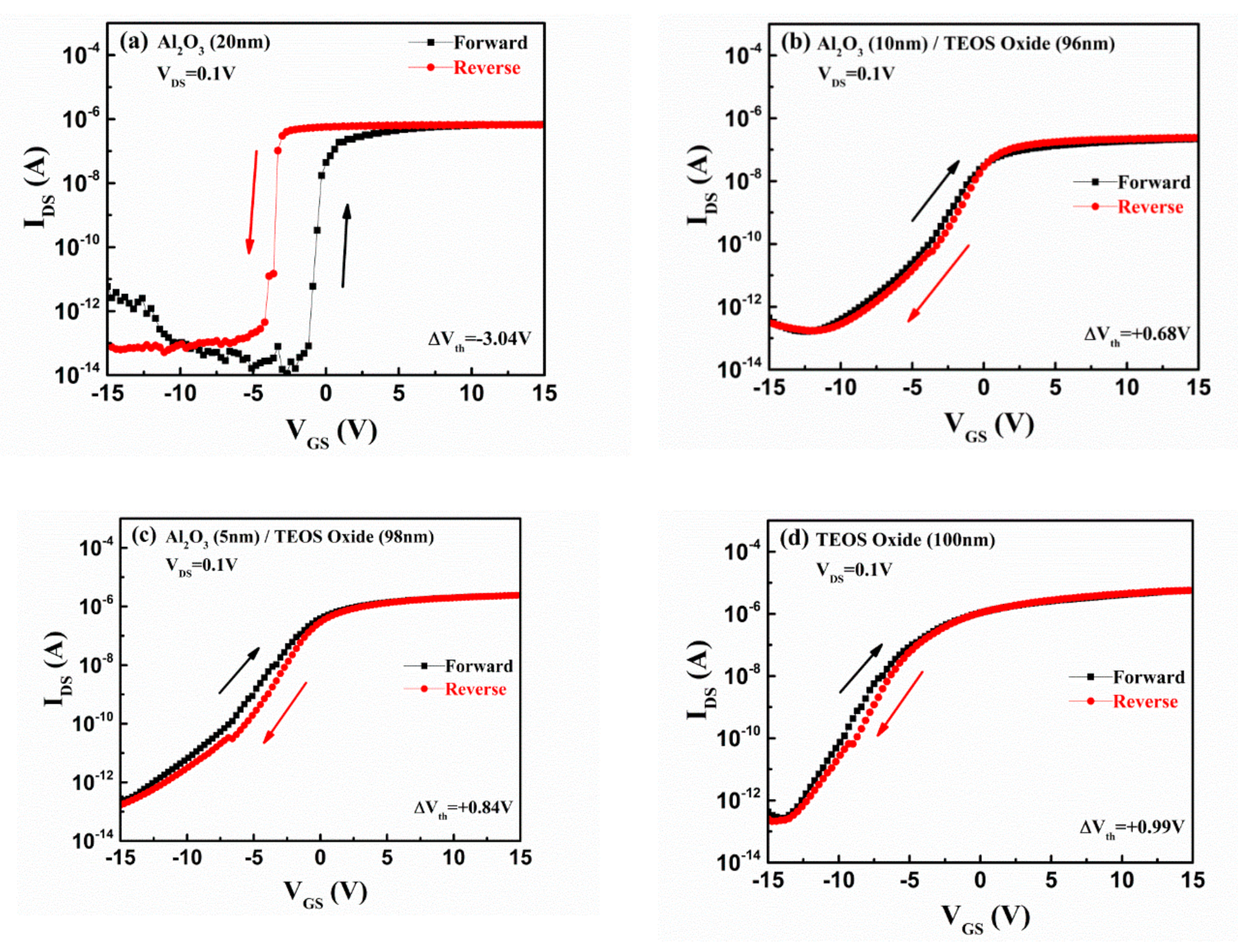

3.2. Electrical Instabilities of IGZO TFTs with Al2O3, Al2O3/TEOS Oxide, and TEOS Oxide Gate Dielectrics

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nat. Cell Biol. 2004, 432, 488–492. [Google Scholar] [CrossRef] [PubMed]

- Hosono, H. Ionic amorphous oxide semiconductors: Material design, carrier transport, and device application. J. Non Cryst. Solids 2006, 352, 851–858. [Google Scholar] [CrossRef]

- Lee, Y.-S.; Yen, T.-W.; Lin, C.-I.; Lin, H.-C.; Yeh, Y. Electrical characteristics of amorphous In–Ga–Zn–O thin-film transistors prepared by radio frequency magnetron sputtering with varying oxygen flows. Displays 2014, 35, 165–170. [Google Scholar] [CrossRef]

- Lee, Y.-S.; Fan, S.-K.; Chen, C.-W.; Yen, T.-W.; Lin, H.-C. Temperature instability of amorphous In-Ga-Zn-O thin film transistors. In Proceedings of the 2013 6th IEEE/International Conference on Advanced Infocomm Technology (ICAIT), Hsinchu, Taiwan, 6–9 July 2013. [Google Scholar] [CrossRef]

- Park, J.; Song, I.; Kim, S.; Kim, S.; Kim, C.; Lee, J.; Lee, H.; Lee, E.; Yin, H.; Kim, K.-K.; et al. Self-aligned top-gate amorphous gallium indium zinc oxide thin film transistors. Appl. Phys. Lett. 2008, 93, 053501. [Google Scholar] [CrossRef]

- Chen, R.; Zhou, W.; Zhang, M.; Wong, M.; Kwok, H.S. Self-aligned top-gate InGaZnO thin film transistors using SiO2/Al2O3 stack gate dielectric. Thin. Solid Films 2013, 548, 572. [Google Scholar] [CrossRef]

- Kamiya, T.; Nomura, K.; Hosono, H. Present status of amorphous In–Ga–Zn–O thin-film transistors. Sci. Technol. Adv. Mater. 2010, 11, 044305. [Google Scholar] [CrossRef]

- Lee, U.G.; Mativenga, M.; Kang, D.H.; Jang, J. A Three-Mask-Processed Coplanar a-IGZO TFT with Source and Drain Offsets. IEEE Electron Device Lett. 2012, 33, 812–814. [Google Scholar] [CrossRef]

- Lee, J.M.; Cho, I.-T.; Lee, J.-H.; Kwon, H.-I. Bias-stress-induced stretched-exponential time dependence of threshold voltage shift in InGaZnO thin film transistors. Appl. Phys. Lett. 2008, 93, 093504. [Google Scholar] [CrossRef]

- Chowdhury, D.H.; Migliorato, P.; Jang, J. Time-temperature dependence of positive gate bias stress and recovery in amorphous indium-gallium-zinc-oxide thin-film-transistors. Appl. Phys. Lett. 2011, 98, 153511. [Google Scholar] [CrossRef]

- Chowdhury, D.H.; Migliorato, P.; Jang, J. Light induced instabilities in amorphous indium–gallium–zinc–oxide thin-film transistors. Appl. Phys. Lett. 2010, 97, 173506. [Google Scholar] [CrossRef]

- Ryu, B.; Noh, H.-K.; Choi, E.-A.; Chang, K.J. O-vacancy as the origin of negative bias illumination stress instability in amorphous In–Ga–Zn–O thin film transistors. Appl. Phys. Lett. 2010, 97, 022108. [Google Scholar] [CrossRef]

- Mativenga, M.; Kang, D.H.; Lee, U.G.; Jang, J. Study of mechanism of stress-induced threshold voltage shift and recovery in top-gate amorphous-InGaZnO4 thin-film transistors with source- and drain-offsets. Solid State Commun. 2012, 152, 1739–1743. [Google Scholar] [CrossRef]

- Kim, J.B.; Fuentes-Hernandez, C.; Potscavage, W.J.; Zhang, X.-H.; Kippelen, B. Low-voltage InGaZnO thin-film transistors with Al2O3 gate insulator grown by atomic layer deposition. Appl. Phys. Lett. 2009, 94, 142107. [Google Scholar] [CrossRef]

- Fan, C.-L.; Tseng, F.-P.; Tseng, C.-Y. Electrical Performance and Reliability Improvement of Amorphous-Indium-Gallium-Zinc-Oxide Thin-Film Transistors with HfO2 Gate Dielectrics by CF4 Plasma Treatment. Materials 2018, 11, 824. [Google Scholar] [CrossRef] [PubMed]

- Huang, X.; Song, J.Q.; Lai, P.-T. Positive Gate Bias and Temperature-Induced Instability of -InGaZnO Thin-Film Transistor with ZrLaO Gate Dielectric. IEEE Trans. Electron Devices 2016, 63, 1899–1903. [Google Scholar] [CrossRef]

- Chang, Y.-H.; Yu, M.-J.; Lin, R.-P.; Hsu, C.-P.; Hou, T.-H. Abnormal positive bias stress instability of In–Ga–Zn–O thin-film transistors with low-temperature Al2O3 gate dielectric. Appl. Phys. Lett. 2016, 108, 033502. [Google Scholar] [CrossRef]

- Park, C.R.; Hwang, J.H. Effect of double-layered Al2O3/SiO2 dielectric materials on In–Ga–Zn–O (IGZO) -based amorphous transparent thin film transistors. Ceram. Int. 2014, 40, 12917. [Google Scholar] [CrossRef]

- Lee, Y.S.; Wang, Y.H.; Tien, T.C.; Hsieh, T.E. Positive Bias Stress Instability of In-Ga-Zn-O Thin-Film Transistors with Al2O3/TEOS Oxide Gate Dielectrics. In Proceedings of the 2017 24th International Workshop on Active-Matrix Flatpanel Displays and Devices (AM-FPD), Kyoto, Japan, 4–7 July 2017; pp. 205–206. [Google Scholar]

- Suresh, A.; Muth, J.F. Bias stress stability of indium gallium zinc oxide channel based transparent thin film transistors. Appl. Phys. Lett. 2008, 92, 033502. [Google Scholar] [CrossRef]

- Chiang, H.Q.; Wager, J.; Hoffman, R.L.; Jeong, J.; Keszler, D.A. High mobility transparent thin-film transistors with amorphous zinc tin oxide channel layer. Appl. Phys. Lett. 2005, 86, 013503. [Google Scholar] [CrossRef]

- Viana, C.E.; da Silva, A.N.R.; Morimoto, N.I.; Bonnaud, O. Analysis of SiO2 Thin Films Deposited by PECVD Using an Oxygen-TEOS-Argon Mixture. Braz. J. Phys. 2001, 31, 299. [Google Scholar] [CrossRef]

- Lee, S.; Koo, B.; Shin, J.; Lee, E.; Park, H.; Kim, H. Effects of hydroxyl groups in polymeric dielectrics on organic transistor performance. Appl. Phys. Lett. 2006, 88, 162109. [Google Scholar] [CrossRef]

- Jeon, S.; Park, S.; Song, I.; Hur, J.-H.; Park, J.; Kim, S.; Kim, S.; Yin, H.; Lee, E.; Ahn, S.; et al. 180nm gate length amorphous InGaZnO thin film transistor for high density image sensor applications. In Proceedings of the 2010 International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010. [Google Scholar] [CrossRef]

- Lee, S.K.; Hong, S.I.; Lee, Y.H.; Lee, S.W.; Cho, W.J.; Park, J.T. Comparative study of electrical instabilities in InGaZnO thin film transistors with gate dielectrics. Microelectron. Reliab. 2012, 52, 2504–2507. [Google Scholar] [CrossRef]

| Gate Insulator (Thickness) | Vth (V) | S.S. (V/Decade) | μFE (cm2 V−1 s−1) | Ion (A) | Ioff (A) |

|---|---|---|---|---|---|

| Al2O3 (20 nm) | 1.6 ± 0.4 | 0.49 ± 0.07 | 0.35 ± 0.06 | 2.40 × 10−7 | 2.00 × 10−14 |

| Al2O3 (10 nm)/TEOS (96 nm) | −2.19 ± 0.05 | 1.37 ± 0.03 | 0.42 ± 0.04 | 2.20 × 10−7 | 1.65 × 10−13 |

| Al2O3 (5 nm)/TEOS (98 nm) | −3.64 ± 0.14 | 1.55 ± 0.03 | 2.47 ± 0.85 | 2.40 × 10−6 | 2.51 × 10−13 |

| TEOS (100 nm) | −4.8 ± 1.13 | 1.08 ± 0.09 | 4.01 ± 1.46 | 3.80 × 10−6 | 2.78 × 10−13 |

| Gate Insulator (Thickness) | ∆Vth (V) | ∆S.S.(V/Decade) | ∆Ion/Ion |

|---|---|---|---|

| Al2O3 (20 nm) | +5.75 | 0.034 | −2.8% |

| Al2O3 (10 nm)/TEOS (96 nm) | −0.42 | 0.41 | +25% |

| Al2O3 (5 nm)/TEOS (98 nm) | −2.92 | 5.53 | +33% |

| TEOS (100 nm) | −8.8 | 11.32 | −93% |

| Gate Insulator (Thickness) | ∆Vth (V) | ∆S.S.(V/Decade) | ∆Ion/Ion |

|---|---|---|---|

| Al2O3 (20 nm) | −0.70 | 1.598 | −94.8% |

| Al2O3 (10 nm)/TEOS (96 nm) | −0.14 | 0.002 | −99.1% |

| Al2O3 (5 nm)/TEOS (98 nm) | −0.17 | 0.007 | −96.0% |

| TEOS (100 nm) | −1.23 | 1.89 | −98.7% |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, Y.-S.; Wang, Y.-H.; Tien, T.-C.; Hsieh, T.-E.; Lai, C.-H. Electrical Characteristics and Stability Improvement of Top-Gate In-Ga-Zn-O Thin-Film Transistors with Al2O3/TEOS Oxide Gate Dielectrics. Coatings 2020, 10, 1146. https://doi.org/10.3390/coatings10121146

Lee Y-S, Wang Y-H, Tien T-C, Hsieh T-E, Lai C-H. Electrical Characteristics and Stability Improvement of Top-Gate In-Ga-Zn-O Thin-Film Transistors with Al2O3/TEOS Oxide Gate Dielectrics. Coatings. 2020; 10(12):1146. https://doi.org/10.3390/coatings10121146

Chicago/Turabian StyleLee, Yih-Shing, Yu-Hsin Wang, Tsung-Cheng Tien, Tsung-Eong Hsieh, and Chun-Hung Lai. 2020. "Electrical Characteristics and Stability Improvement of Top-Gate In-Ga-Zn-O Thin-Film Transistors with Al2O3/TEOS Oxide Gate Dielectrics" Coatings 10, no. 12: 1146. https://doi.org/10.3390/coatings10121146

APA StyleLee, Y.-S., Wang, Y.-H., Tien, T.-C., Hsieh, T.-E., & Lai, C.-H. (2020). Electrical Characteristics and Stability Improvement of Top-Gate In-Ga-Zn-O Thin-Film Transistors with Al2O3/TEOS Oxide Gate Dielectrics. Coatings, 10(12), 1146. https://doi.org/10.3390/coatings10121146