Investigation of the Integration of Strained Ge Channel with Si-Based FinFETs

Abstract

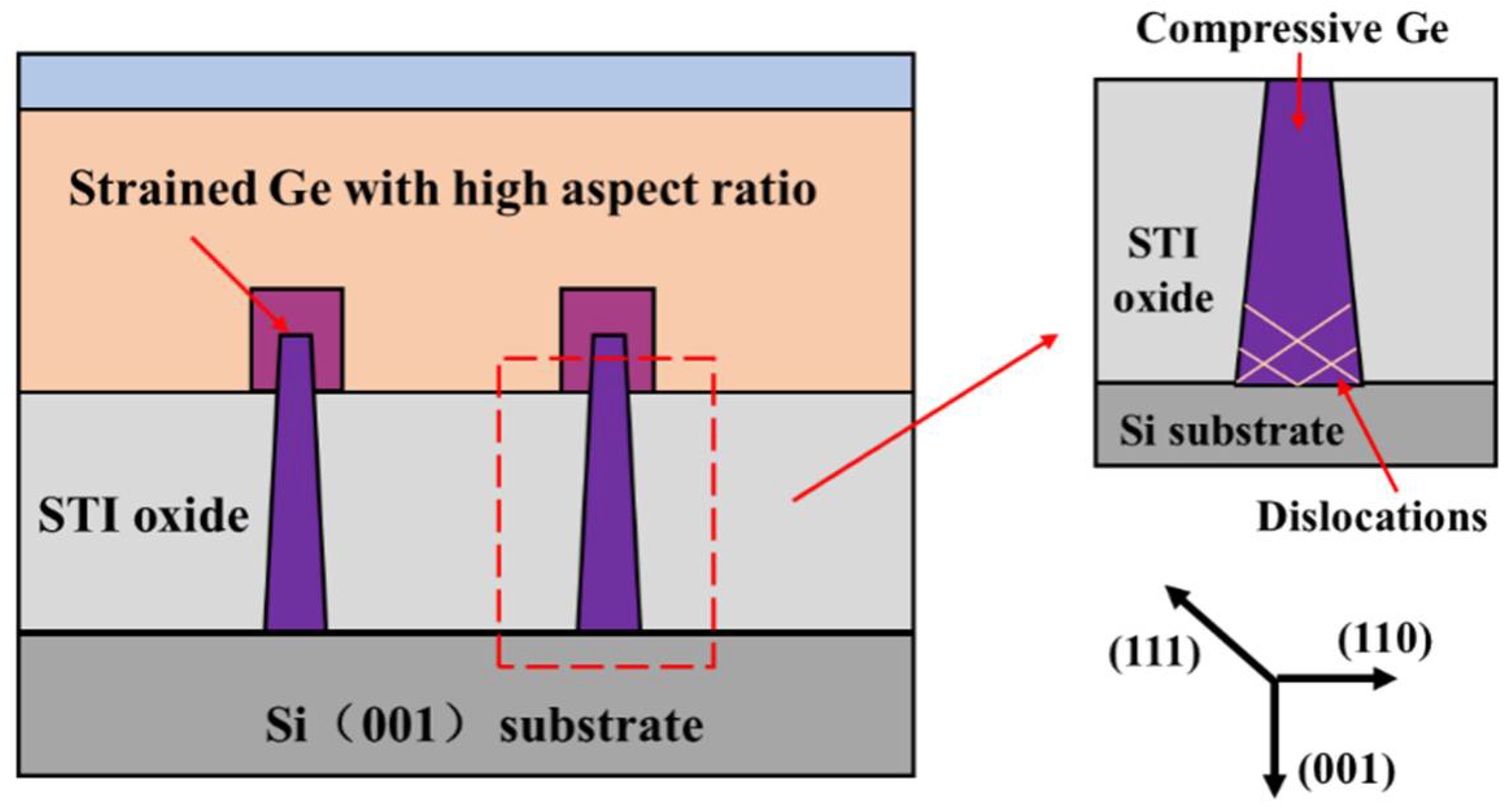

:1. Introduction

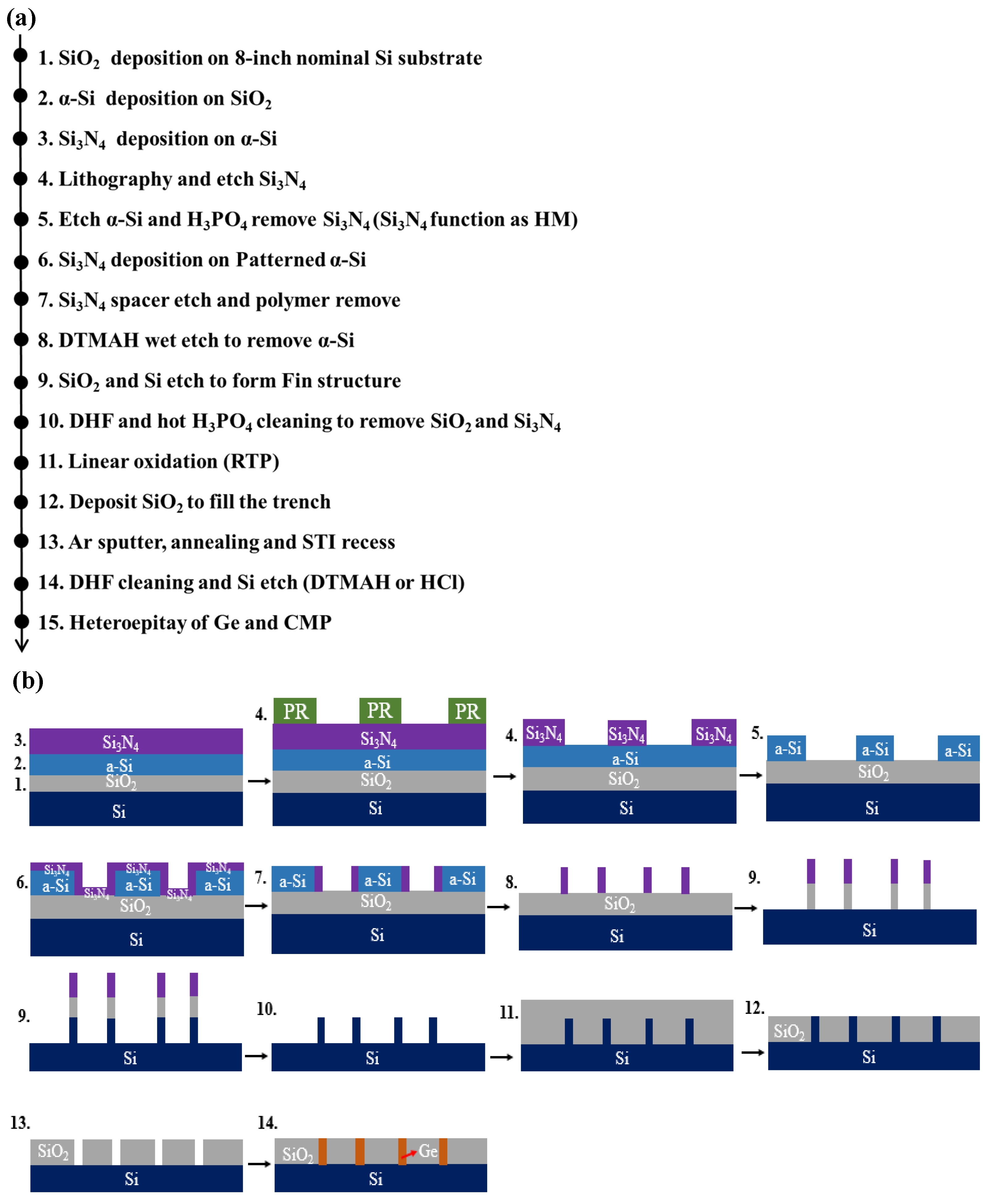

2. Experimental Details

3. Results and Discussion

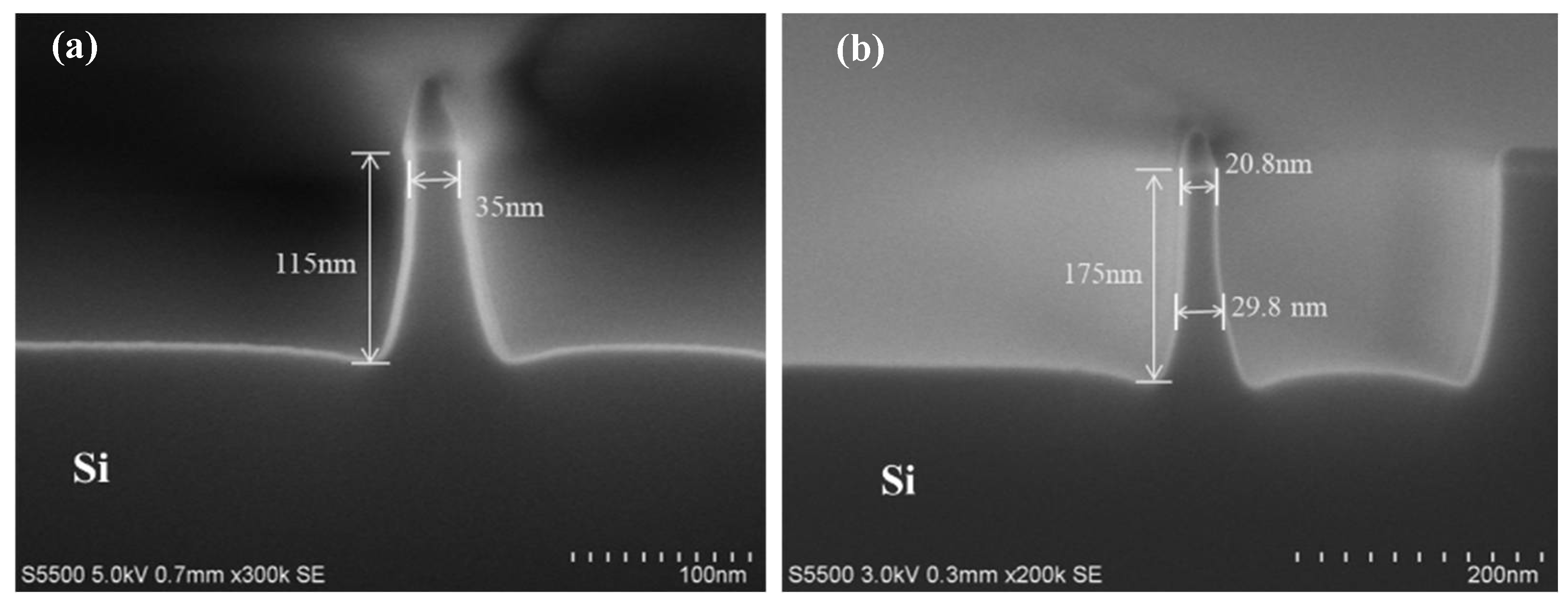

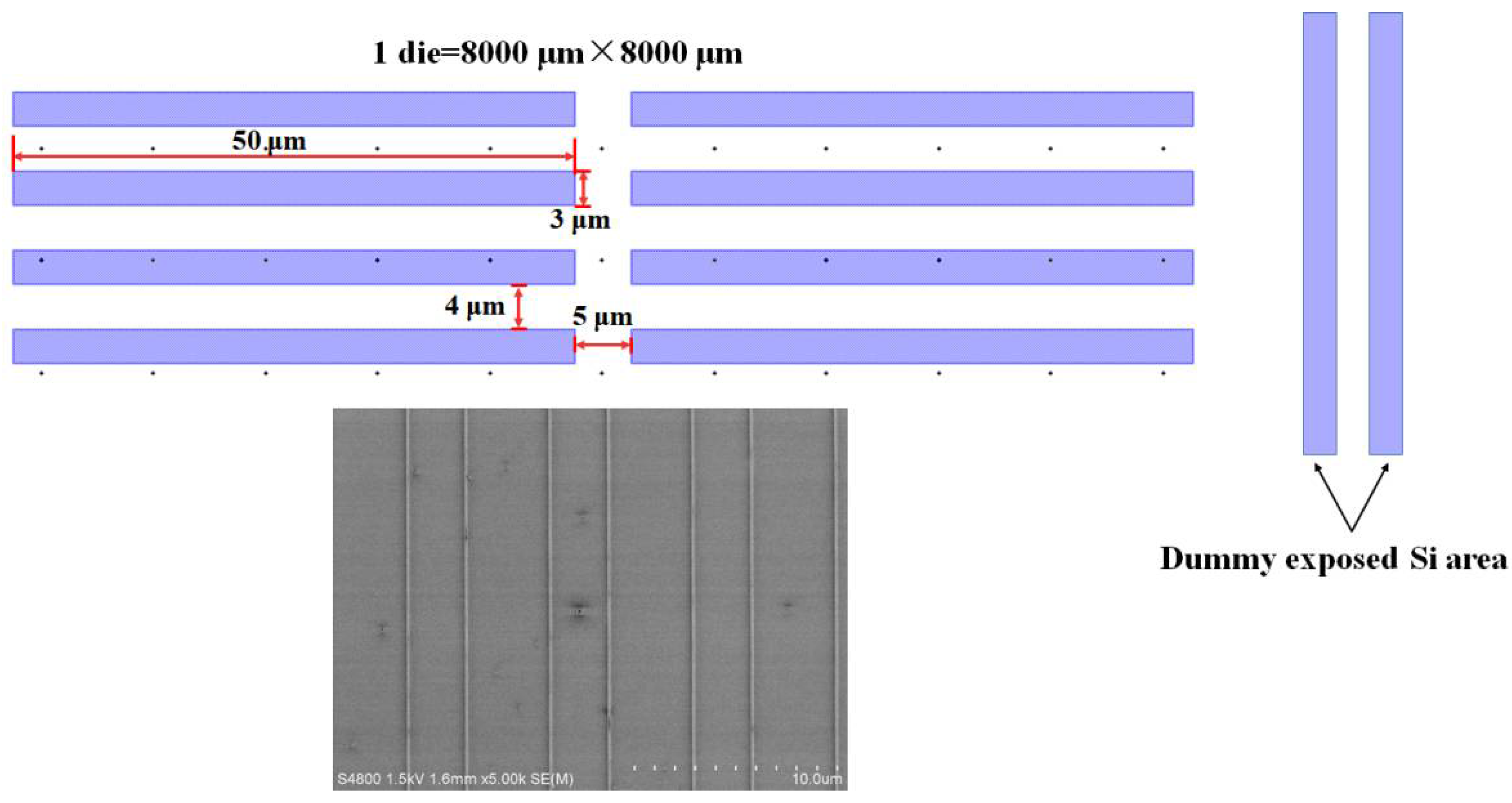

3.1. High-Aspect-Ratio Fin Structure Formation

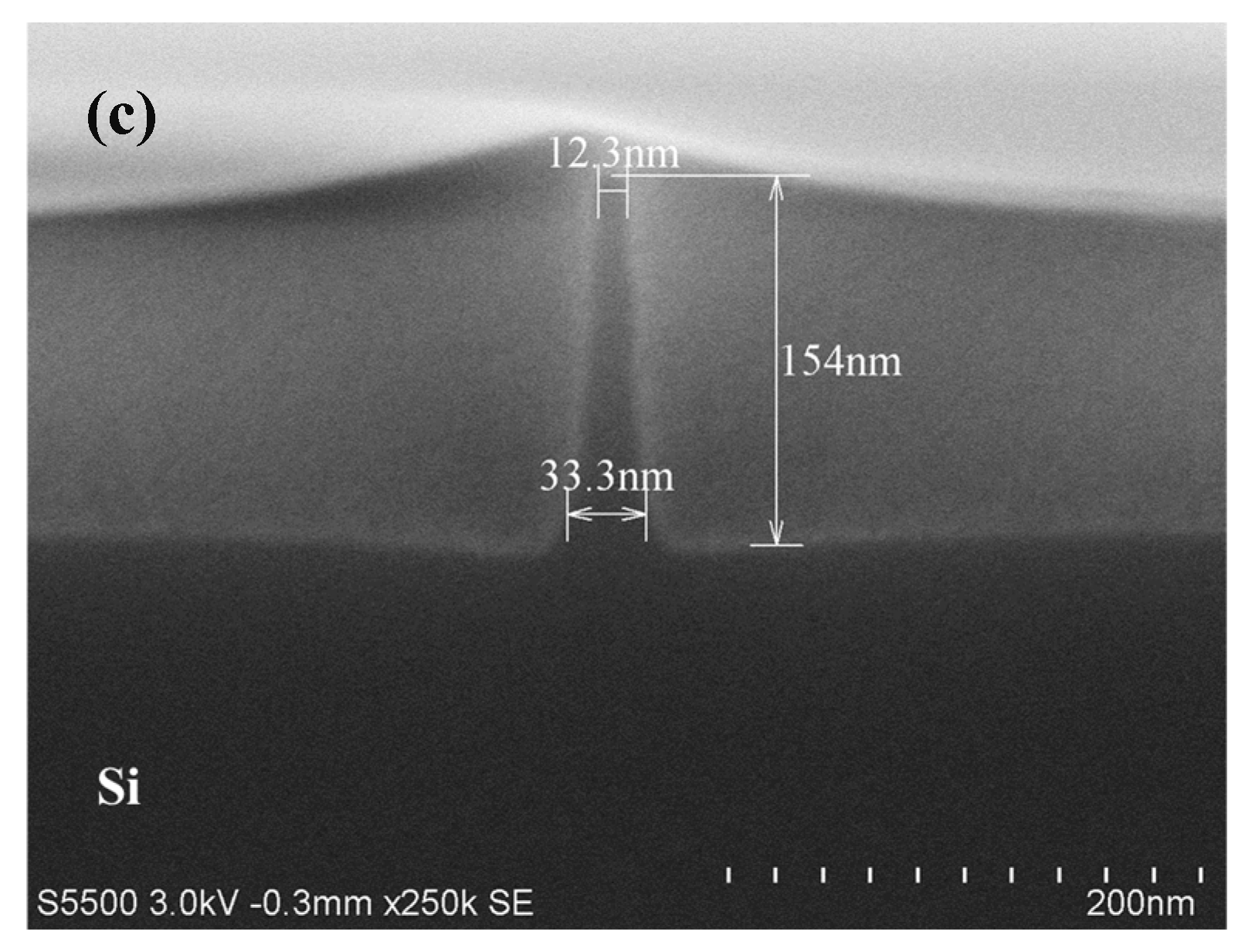

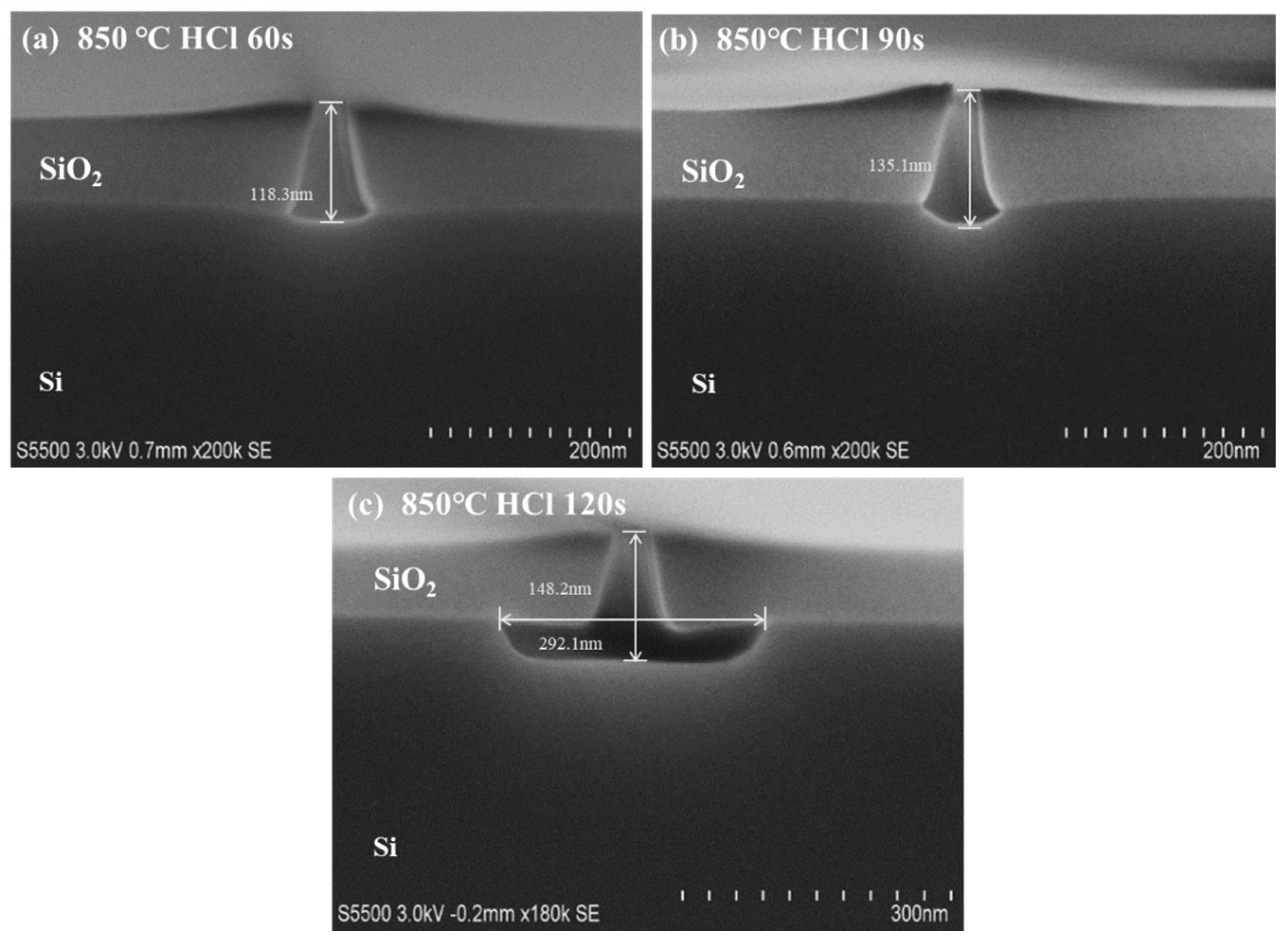

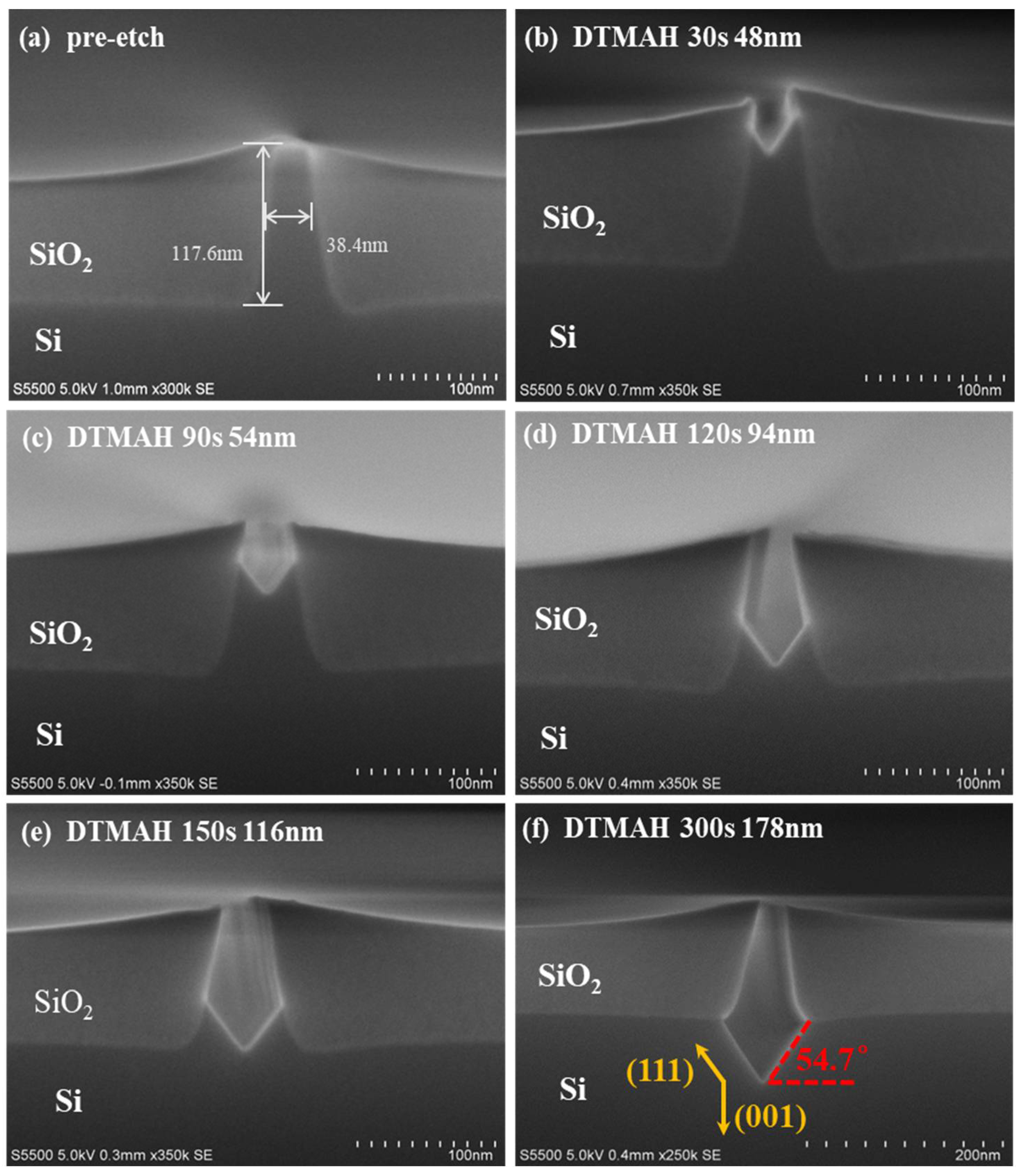

3.2. Dummy Fin Removal: Wet Etching and In Situ Dry Etching

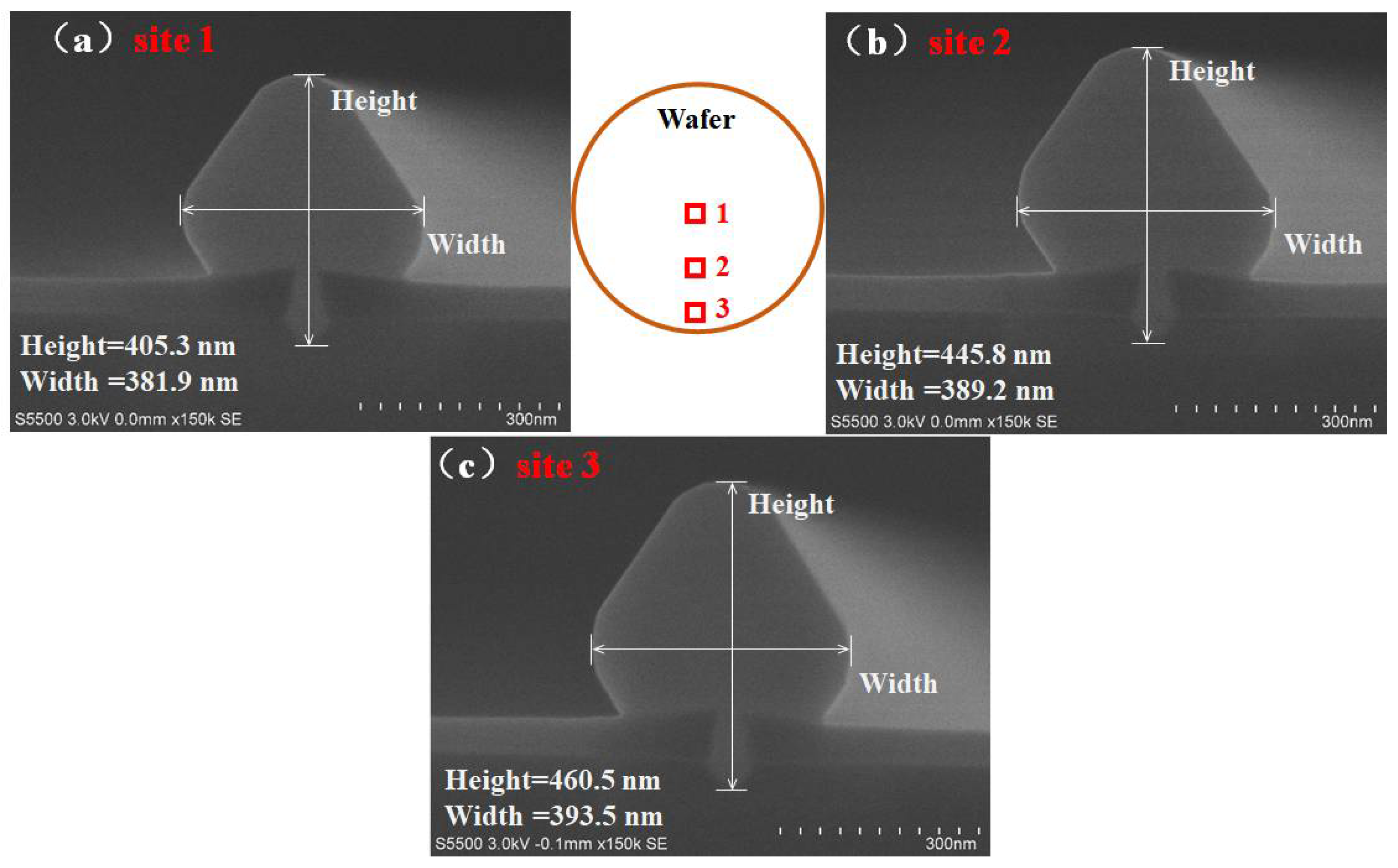

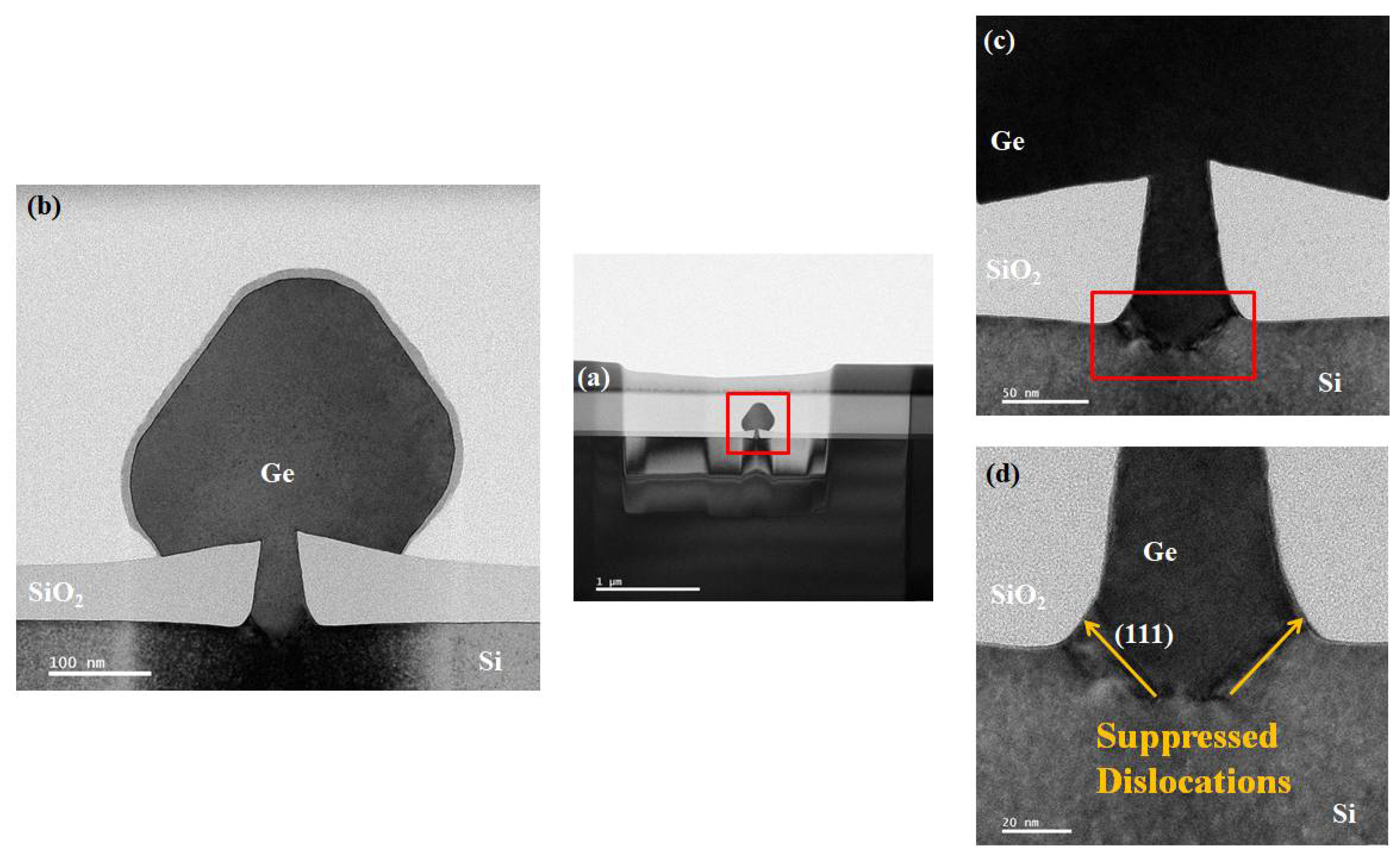

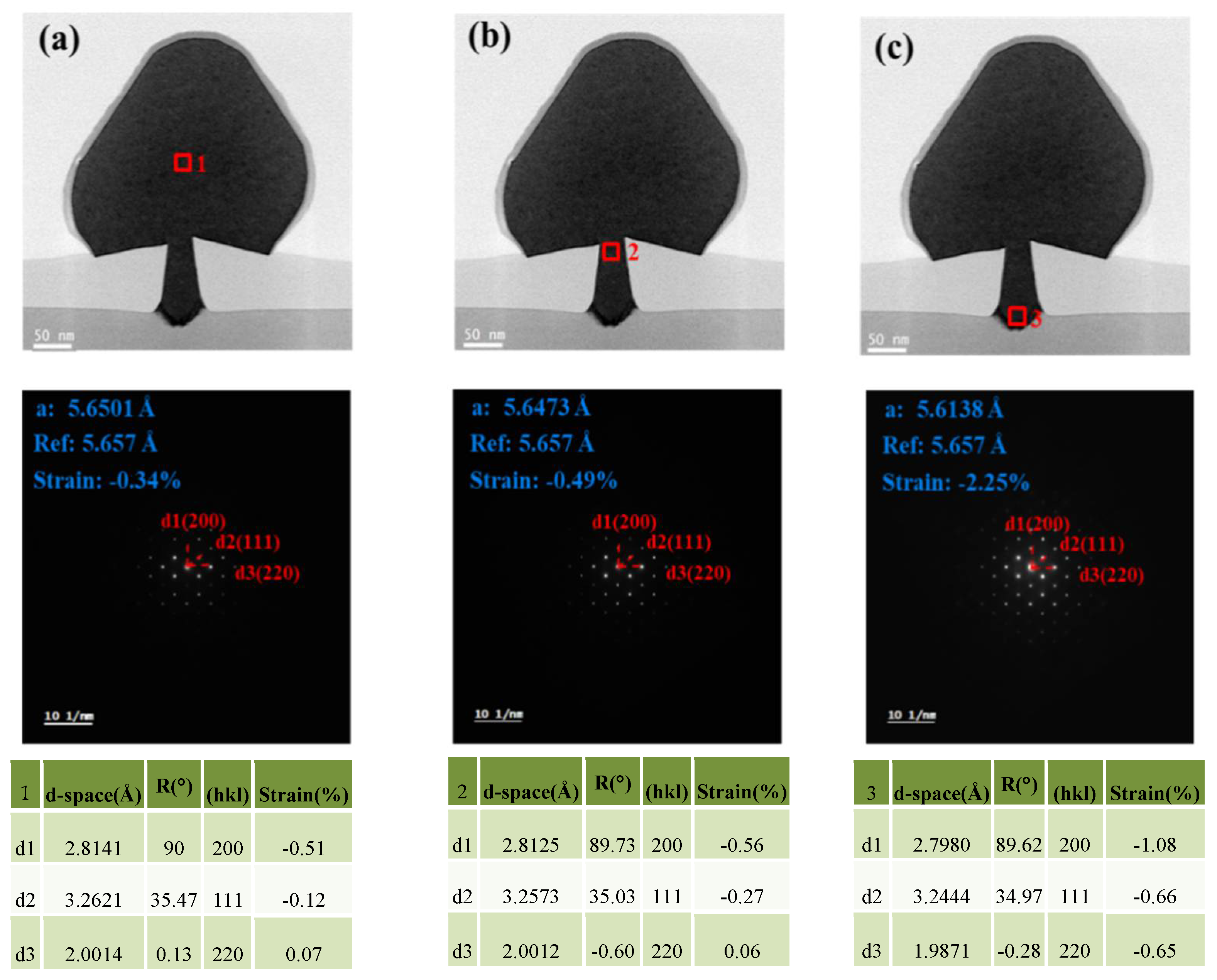

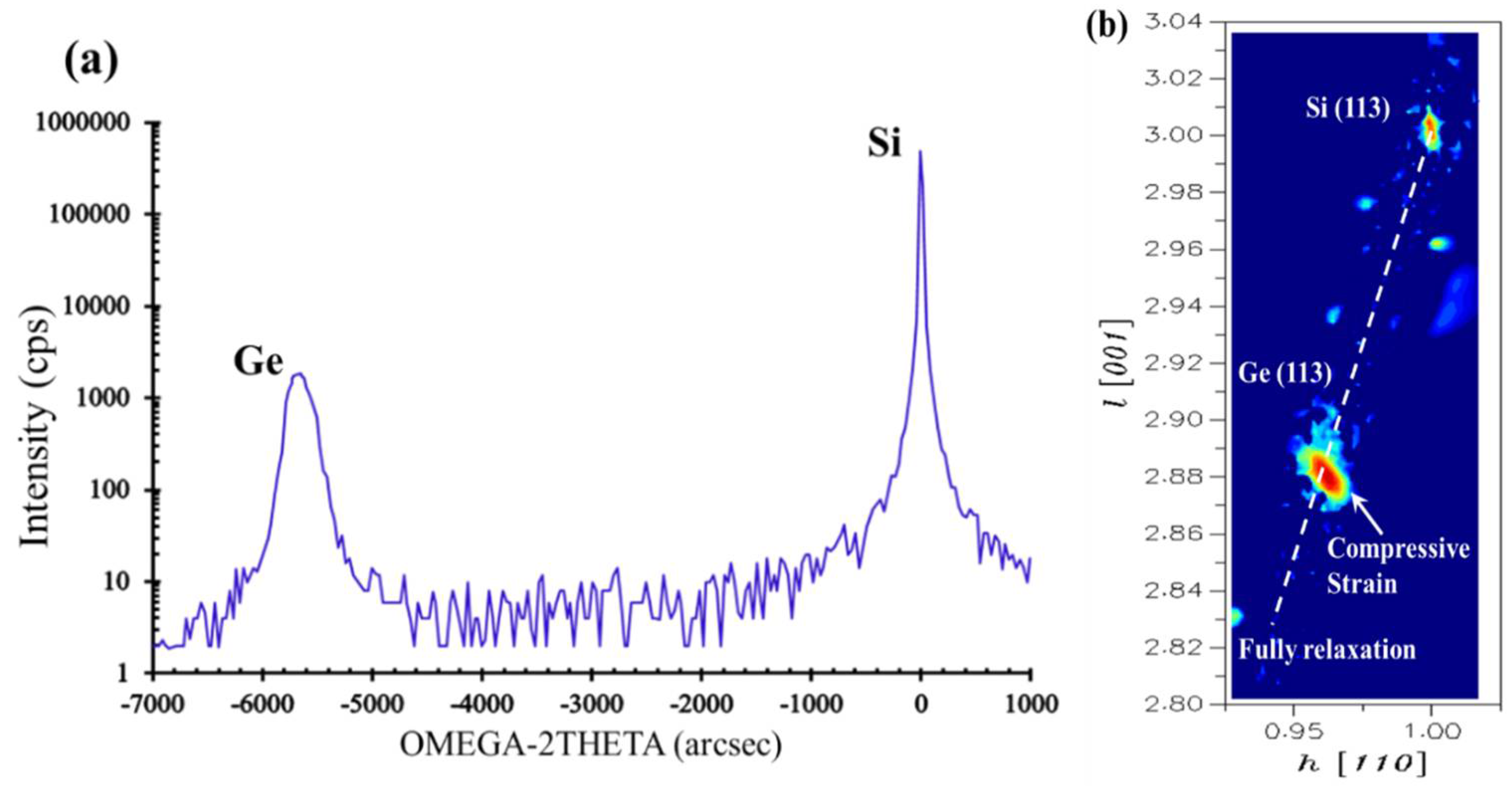

3.3. Ge Selective Epitaxy

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Dennard, R.H.; Gaensslen, F.H.; Yu, H.N.; Rideout, V.; Bassous, E.; LeBlanc, A.R. Design of ion-implanted MOSFET’s with very small physical dimensions. IEEE J. Solid State Circuits 1974, 9, 256–267. [Google Scholar] [CrossRef] [Green Version]

- Radamson, H.H.; Luo, J.; Simoen, E.; Zhao, C. CMOS Past, Present and Future; Woodhead Publishing: Cambridge, UK, 2018; ISBN 9780081021392. [Google Scholar]

- Radamson, H.H.; Zhu, H.; Wu, Z.; He, X.; Lin, H.; Liu, J.; Xiang, J.; Kong, Z.; Xiong, W.; Li, J.; et al. State of the Art and Future Perspectives in Advanced CMOS Technology. Nanomaterials 2020, 10, 1555. [Google Scholar] [CrossRef] [PubMed]

- Hisamoto, D.; Wen-chin, L.; Kedzierski, J.; Takeuchi, H.; Asano, K.; Kuo, C.; Anderson, E.; Jae king, T.; Boker, J.; Chenmin, H. FinFET—A self-aligned double-gate MOSFET scalable to 20 nm. IEEE Trans. Electron Devices 2000, 47, 2320–2325. [Google Scholar]

- Wong, H.-S.P.; Chan, K.K.; Taur, Y. Self-aligned (top and bottom) double-gate MOSFET with a 25 nm thick silicon channel. In Proceedings of the IEDM, San Francisco, CA, USA, 10 December 1997; pp. 427–430. [Google Scholar]

- Huang, X.J.; Wen-chin, L.; Kuo, C.; Hisamoto, D.; Chang, L.; Kedzierski, J.; Anderson, E.; Takeuchi, H.; Choi, Y.K.; Asano, K.; et al. Sub-50 nm P-channel FinFET. IEEE Trans Electron Devices 2000, 48, 880–886. [Google Scholar] [CrossRef] [Green Version]

- Duriez, B.; Vellianitis, G.; Dal, M.V.; Doornbos, G.; Oxland, R.; Bhuwalka, K.K.; Holland, M.; Chang, Y.S.; Hsieh, C.H.; Yin, K.M.; et al. Scaled p-channel Ge FinFET with optimized gate stack and record performance integrated on 300 mm Si wafers. In Proceedings of the IEDM, Washington, DC, USA, 9–11 December 2013; pp. 20.1.1–20.1.4. [Google Scholar]

- Gluschenkov, O.; Liu, Z.; Niimi, H.; Mochizuki, S.; Fronheiser, J.; Miao, X.; Li, J.; Demarest, J.; Zhang, C.; Niu, C.; et al. FinFET performance with Si:P and Ge:Group-III-Metal metastable contact trench alloys. In Proceedings of the IEDM, San Francisco, CA, USA, 3–7 December 2016; pp. 17.2.1–17.2.4. [Google Scholar]

- Sil, M.; Guin, S.; Nawaz, S.M.; Mallik, A. Performance of Ge p-channel junctionless FinFETs for logic applications. Appl. Phys. A 2019, 125, 782. [Google Scholar] [CrossRef]

- Bae, G.; Bae, D.I.; Kang, M.; Hwang, S.M.; Kim, S.S.; Seo, B.; Kwon, T.Y.; Lee, T.J.; Moon, C.; Choi, Y.M.; et al. 3 nm GAA technology featuring multi-bridge-channel FET for low power and high performance applications. In Proceedings of the IEDM, San Francisco, CA, USA, 1–5 December 2018; pp. 28.7.1–28.7.4. [Google Scholar]

- Najmzadeh, M.; Bouvet, D.; Grabinski, W.; Sallese, J.M.; Ionescu, A.M. Accumulation-mode gate-all-around Si nanowire nMOSFETs with sub-5 nm cross-section and high uniaxial tensile strain. Solid-State Electron. 2012, 74, 114–120. [Google Scholar] [CrossRef] [Green Version]

- Dash, T.P.; Dey, S.; Das, S.; Mohapatra, E.; Jena, J.; Maiti, C.K. Strain-engineering in nanowire field-effect transistors at 3 nm technology node. Phys. E Low-Dimens. Syst. Nanostruct. 2020, 118, 113964. [Google Scholar] [CrossRef]

- Thakur, R.R.; Chaturvedi, N. Gate-All-Around GaN Nanowire FET as a Potential Transistor at 5 nm Technology for Low-Power Low-Voltage Applications. Nano 2021, 16, 2150096. [Google Scholar] [CrossRef]

- Dey, S.; Jena, J.R.; Mohapatra, E.; Dash, T.P.; Das, S.; Maiti, C.K. Design and simulation of vertically-stacked nanowire transistors at 3 nm technology nodes. Phys. Scr. 2019, 95, 014001. [Google Scholar] [CrossRef]

- Yakimets, D.; Eneman, G.; Schuddinck, P.; Bao, T.H.; Bardon, M.G.; Raghavan, P.; Veloso, A.; Collaert, N.; Mercha, A.; Verkest, D.; et al. Vertical GAAFETs for the ultimate CMOS scaling. IEEE Trans. Electron Devices 2015, 62, 1433–1439. [Google Scholar] [CrossRef]

- Veloso, A.; Altamirano-Sánchez, E.; Brus, S.; Chan, B.T.; Cupak, M.; Dehan, M.; Delvaux, C.; Devriendt, K.; Eneman, G.; Ercken, M.; et al. Vertical Nanowire FET Integration and Device Aspects. ECS Trans. 2016, 72, 31–42. [Google Scholar] [CrossRef]

- Wu, H.; Wu, W.; Si, M.; Peide, D.Y. First demonstration of Ge nanowire CMOS circuits: Lowest SS of 64 mV/dec, highest gmax of 1057 μS/μm in Ge nFETs and highest maximum voltage gain of 54 V/V in Ge CMOS inverters. In Proceedings of the IEDM, Washington, DC, USA, 7–9 December 2015; pp. 2.1.1–2.1.4. [Google Scholar]

- Zhang, Y.K.; Ai, X.Z.; Yin, X.; Zhu, H.; Yang, H.; Wang, G.L.; Li, J.J.; Du, A.Y.; Li, C.; Huang, W.X.; et al. Vertical Sandwich GAA FETs with Self-Aligned High-k Metal Gate Made by Quasi Atomic Layer Etching Process. IEEE Trans. Electron Devices 2021, 68, 2604–2610. [Google Scholar] [CrossRef]

- Li, C.; Zhu, H.L.; Zhang, Y.K.; Yin, X.; Jia, K.; Li, J.; Wang, G.; Kong, Z.; Du, A.; Yang, T.; et al. Selective Digital Etching of Silicon-Germanium Using Nitric and Hydrofluoric Acids. ACS Appl. Mater. Interfaces 2020, 12, 48170–48178. [Google Scholar] [CrossRef]

- Wostyn, K.; Sebaai, F.; Rip, J.; Mertens, H.; Witters, L.; Loo, R.; Hikavyy, A.; Milenin, A.; Horiguichi, N.; Collaert, N.; et al. Selective Etch of Si and SiGe for Gate All-Around Device Architecture. ECS Trans. 2015, 69, 147–152. [Google Scholar] [CrossRef]

- Bollani, M.; Salvalaglio, M.; Benali, A.; Bouabdellaoui, M.; Naffouti, M.; Lodari, M.; Corato, S.D.; Fedorov, A.; Voigt, A.; Fraj, I.; et al. Templated dewetting of single-crystal sub-millimeter-long nanowires and on-chip silicon circuits. Nat. Commun. 2019, 10, 5632. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- International Roadmap for Devices and Systems 2017 Edition More Moore. Available online: https://irds.ieee.org/images/files/pdf/2017/2017IRDS_MM.pdf (accessed on 30 December 2018).

- Lim, S.W. Toward the Surface Preparation of InGaAs for the Future CMOS Integration. Solid State Phenom. 2018, 282, 39–42. [Google Scholar] [CrossRef]

- Radamson, H.H.; Thylen, L. Monolithic Nanoscale Photonics Electronics Integration in Silicon and Other Group IV Elements; Elsevier: Amsterdam, The Netherlands; Academic Press: Cambridge, MA, USA, 2014; ISBN 978-012-419-975-0. [Google Scholar]

- Thompson, S.E.; Armstrong, M.; Auth, C.; Cea, S.; Chau, R.; Glass, G.; Hoffman, T.; Klaus, J.; Ma, Z.Y.; Mcintyre, B.; et al. A logic nanotechnology featuring strained-silicon. IEEE Trans. Electron Devices 2004, 25, 191–193. [Google Scholar] [CrossRef]

- Ye, H.; Yu, J. Germanium epitaxy on silicon. Sci. Technol. Adv. Mater. 2014, 15, 024601. [Google Scholar] [CrossRef] [Green Version]

- Du, Y.; Wang, G.; Miao, Y.; Xu, B.; Li, B.; Kong, Z.; Yu, J.; Zhao, X.; Lin, H.; Su, J.; et al. Strain Modulation of Selectively and/or Globally Grown Ge Layers. Nanomaterials 2021, 11, 1421. [Google Scholar] [CrossRef]

- Mahmood, A.; Jabbar, W.A.; Hashim, Y.; Manap, H.B. Electrical Characterization of Ge-FinFET Transistor Based on Nanoscale Channel Dimensions. J. Nano-Electron. Phys. 2019, 11, 1. [Google Scholar] [CrossRef]

- Eneman, G.; Brunco, D.P.; Witters, L.; Vincent, B.; Favia, P.; Hikavyy, A.; De Keersgieter, A.; Mitard, J.; Loo, R.; Veloso, A.; et al. Stress simulations for optimal group IV p- and nMOS FinFETs for the 14 nm node and beyond. In Proceedings of the IEDM, San Francisco, CA, USA, 10–13 December 2012; pp. 131–134. [Google Scholar]

- Eneman, G.; Hellings, G.; De Keersgieter, A.; Collaert, N.; Thean, A. Quantum-barriers and ground-plane isolation: A path for scaling Bulk-FinFET technologies to the 7 nm-node and beyond. In Proceedings of the IEDM, Washington, DC, USA, 9–11 December 2013; pp. 320–323. [Google Scholar]

- Van Dal, M.J.H.; Vellianitis, G.; Doornbos, G.; Duriez, B.; Shen, T.M.; Wu, C.C.; Oxland, R.; Bhuwalka, K.; Holland, M.; Lee, T.L.; et al. Demonstration of scaled Ge p-channel FinFETs integrated on Si. In Proceedings of the IEDM, San Francisco, CA, USA, 10–13 December 2012; pp. 521–524. [Google Scholar]

- Pei, G.; Kedzierski, J.; Oldiges, P.; Ieong, M.; Kan, E.C.-C. FinFET design considerations based on 3-D simulation and analytical modeling. IEEE Trans. Electron Devices 2002, 49, 1411–1419. [Google Scholar] [CrossRef]

- Scopece, D.; Montalenti, F.; Bollani, M.; Chrastina, D.; Bonera, E. Straining Ge bulk and nanomembranes for optoelectronic applications: A systematic numerical analysis. Semicond. Sci. Technol. 2014, 29, 095012.33. [Google Scholar] [CrossRef]

- Kolahdouz, M.; Maresca, L.; Ghandi, R.; Khatibi, A.; Radamson, H.H. Kinetic model of SiGe selective epitaxial growth using RPCVD technique. J. Electrochem. Soc. ECS Trans. 2011, 158, 581–593. [Google Scholar] [CrossRef]

- Fischer, A.C.; Belova, L.M.; Rikers, Y.G.; Malm, B.G.; Radamson, H.H.; Kolahdouz, M.; Gylfason, K.B.; Stemme, G.; Niklaus, F. 3D Free-Form Patterning of Silicon by Ion Implantation, Silicon Deposition, and Selective Silicon Etching. Adv. Func. Mater. 2012, 22, 4004–4008. [Google Scholar] [CrossRef] [Green Version]

- Hartmann, J.; Clavelier, L.; Jahan, C.; Holliger, P.; Rolland, G.; Billon, T.; Defranoux, C. Selective epitaxial growth of boron- and phosphorus-doped Si and SiGe for raised sources and drains. J. Cryst. Growth 2004, 264, 36–47. [Google Scholar] [CrossRef]

- Vincent, B.; Witters, L.; Richard, O.; Hikavyy, A.; Bender, H.; Loo, R.; Caymax, M.; Thean, A. Selective growth of strained Ge channel on relaxed SiGe buffer in shallow trench isolation for high mobility Ge planar and FIN p-FET. ECS Trans. 2012, 50, 39–45. [Google Scholar] [CrossRef]

- Wang, G.; Abedin, A.; Moeen, M.; Kolahdouz, M.; Luo, J.; Guo, Y.; Chen, T.; Yin, H.X.; Zhu, H.L.; Li, J.F.; et al. Integration of highly-strained SiGe materials in 14 nm and beyond nodes FinFET technology. Solid-State Electron. 2015, 103, 222–228. [Google Scholar] [CrossRef]

- Nayfeh, A.; Chui, C.O.; Saraswat, K.C.; Yonehara, T. Effects of hydrogen annealing on heteroepitaxial-Ge layers on Si: Surface roughness and electrical quality. Appl. Phys. Lett. 2004, 85, 2815–2817. [Google Scholar] [CrossRef] [Green Version]

- Miao, Y.-H.; Hu, H.-Y.; Li, X.; Song, J.-J.; Xuan, R.-X.; Zhang, H.-M. Evaluation of threading dislocation density of strained Ge epitaxial layer by high resolution X-ray diffraction. Chin. Phys. B 2017, 26, 127309. [Google Scholar] [CrossRef]

- Kim, H.-W.; Shin, K.W.; Lee, G.-D.; Yoon, E. High quality Ge epitaxial layers on Si by ultrahigh vacuum chemical vapor deposition. Thin Solid Films 2009, 517, 3990–3994. [Google Scholar] [CrossRef]

- Kolahdouz, M.; Hallstedt, J.; Khatibi, A.; Östling, M.; Wise, R.; Riley, D.J.; Radamson, H. Comprehensive Evaluation and Study of Pattern Dependency Behavior in Selective Epitaxial Growth of B-Doped SiGe Layers. IEEE Trans. Nanotechnol. 2009, 8, 291–297. [Google Scholar] [CrossRef]

- Hallstedt, J.; Hellstrm, P.E.; Radamson, H.H. Sidewall transfer lithography for reliable fabrication of nanowires and deca-nanometer MOSFETs. Thin Solid Films 2008, 517, 117–120. [Google Scholar] [CrossRef]

- Weng, C.J. Feasible approach for processes integration of CMOS transistor gate/side-wall spacer patterning fabrication. Microelectron. Reliab. 2010, 50, 1951–1960. [Google Scholar] [CrossRef]

- Choi, Y.K.; King, T.J.; Hu, C.M. A spacer patterning technology for nanoscale CMOS. IEEE Trans. Electron Devices 2002, 49, 436–441. [Google Scholar] [CrossRef] [Green Version]

- Wang, G.; Kolahdouz, M.; Luo, J.; Qin, C.; Gu, S.; Kong, Z.; Yin, X.; Xiong, W.; Zhao, X.; Liu, J.; et al. Growth of SiGe layers in source and drain regions for 10 nm node complementary metal-oxide semiconductor (CMOS). J. Mater. Sci. Mater. Electron. 2019, 31, 26–33. [Google Scholar] [CrossRef]

- Radamson, H.H.; Kolahdouz, M. Selective epitaxy growth of Si1xGex layers for MOSFETs and FinFETs. J. Mater. Sci. Mater. Electron. 2015, 2, 4584–4603. [Google Scholar] [CrossRef]

- Menon, C.; Lindgren, A.C.; Persson, P.; Hultman, L.; Radamson, H.H. Selective epitaxy of Si1-xGex layers for complementary metal oxide semiconductor applications. J. Electrochem. Soc. 2009, 150, G253–G257. [Google Scholar] [CrossRef]

- Hallstedt, J.; Isheden, C.; Oestling, M.; Baubinas, R.; Matukas, J.; Palenskis, V.; Radamson, H.H. Application of selective epitaxy for formation of ultra shallow SiGe-based junctions. Mater. Sci. Eng. B 2004, 114–115, 180–183. [Google Scholar] [CrossRef]

- Kolahdouz, M.; Maresca, L.; Ostling, M.; Riley, D.; Wise, R.; Radamson, H.H. New method to calibrate the pattern dependency of selective epitaxy of SiGe layers. Solid State Electron. 2009, 53, 858–861. [Google Scholar] [CrossRef]

- Loo, R.; Wang, G.; Souriau, L.; Lin, J.C.; Takeuchi, S.; Brammertz, G.; Caymax, M. Epitaxial Ge on standard STI patterned Si wafers: High quality virtual substrates for Ge pMOS and III/V nMOS. ECS Trans. 2009, 25, 335–350. [Google Scholar] [CrossRef]

- Holt, J.R.; Harley, E.C.; Adam, T.N.; Jeng, S.J.; Schepis, D.J. SiGe Selective Epitaxy: Morphology and Thickness Control for High Performance CMOS Technology. ECS Trans. 2008, 16, 475. [Google Scholar] [CrossRef]

- Hartmann, J.M.; Bertin, F.; Rolland, G.; Laugier, F.; Séméria, M.N. Selective epitaxial growth of Si and SiGe for metal oxide semiconductor transistors. J. Cryst. Growth 2003, 259, 419–427. [Google Scholar] [CrossRef]

- Vescan, L. Selective epitaxial growth of SiGe alloys–influence of growth parameters on film properties. Mater. Sci. Eng. B 1994, 28, 1–8. [Google Scholar] [CrossRef]

- Knutson, K.L.; Carr, R.W.; Liu, W.H.; Campbell, S.A. A kinetics and transport model of dichiorosilane chemical vapor deposition. J. Cryst. Growth. 1994, 140, 191–204. [Google Scholar] [CrossRef]

- Hallstedt, J.; Kolahdouz, M.; Ghandi, R.; Radamson, H.H.; Wise, R. Pattern dependency in selective epitaxy of B-doped SiGe layers for advanced metal oxide semiconductor field effect transistors. J. Appl. Phys. 2008, 103, 054907. [Google Scholar] [CrossRef]

- Bodnar, S.; de Berranger, E.; Bouillon, P.; Mouis, M.; Skotnicki, T.; Regolini, J.L. Selective Si and SiGe epitaxial heterostructures grown using an industrial low-pressure chemical vapor deposition module. J. Vac. Sci. Technol. B Microelectron. Nanometer Struct. 1997, 15, 712. [Google Scholar] [CrossRef]

| Etch Method | Etch Time (s) | Etch Depth (nm) | Etch Rate (Å/s) |

|---|---|---|---|

| DTMAH wet etching | 30 | 48 | 16 |

| 90 | 54 | 6 | |

| 120 | 94 | 7.83 | |

| 150 | 116 | 7.73 | |

| 300 | 178 | 5.93 | |

| In situ HCl dry etching | 60 | 118 | 19.7 |

| 90 | 135 | 15.0 | |

| 120 | 148 | 12.6 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xu, B.; Wang, G.; Du, Y.; Miao, Y.; Wu, Y.; Kong, Z.; Su, J.; Li, B.; Yu, J.; Radamson, H.H. Investigation of the Integration of Strained Ge Channel with Si-Based FinFETs. Nanomaterials 2022, 12, 1403. https://doi.org/10.3390/nano12091403

Xu B, Wang G, Du Y, Miao Y, Wu Y, Kong Z, Su J, Li B, Yu J, Radamson HH. Investigation of the Integration of Strained Ge Channel with Si-Based FinFETs. Nanomaterials. 2022; 12(9):1403. https://doi.org/10.3390/nano12091403

Chicago/Turabian StyleXu, Buqing, Guilei Wang, Yong Du, Yuanhao Miao, Yuanyuan Wu, Zhenzhen Kong, Jiale Su, Ben Li, Jiahan Yu, and Henry H. Radamson. 2022. "Investigation of the Integration of Strained Ge Channel with Si-Based FinFETs" Nanomaterials 12, no. 9: 1403. https://doi.org/10.3390/nano12091403

APA StyleXu, B., Wang, G., Du, Y., Miao, Y., Wu, Y., Kong, Z., Su, J., Li, B., Yu, J., & Radamson, H. H. (2022). Investigation of the Integration of Strained Ge Channel with Si-Based FinFETs. Nanomaterials, 12(9), 1403. https://doi.org/10.3390/nano12091403