A Simple Doping Process Achieved by Modifying the Passivation Layer for Self-Aligned Top-Gate In-Ga-Zn-O Thin-Film Transistors at 200 °C

Abstract

1. Introduction

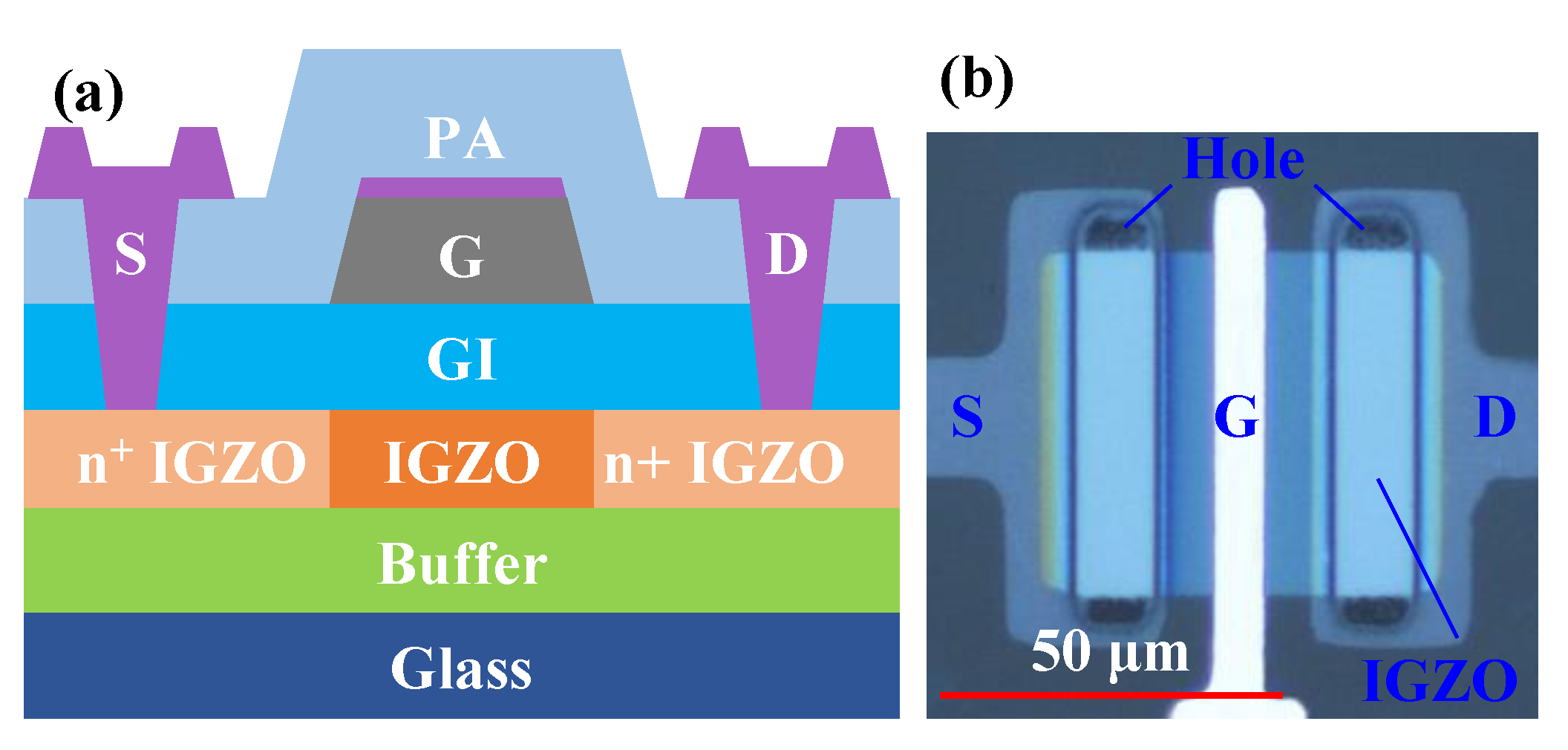

2. Materials and Methods

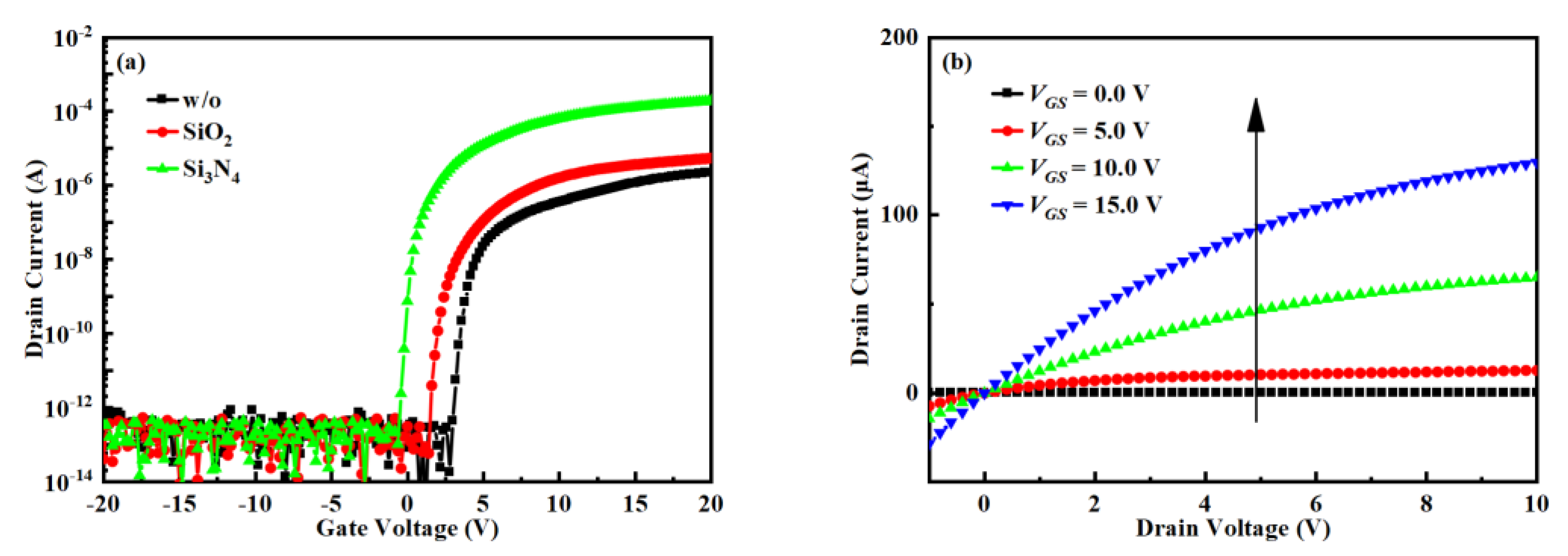

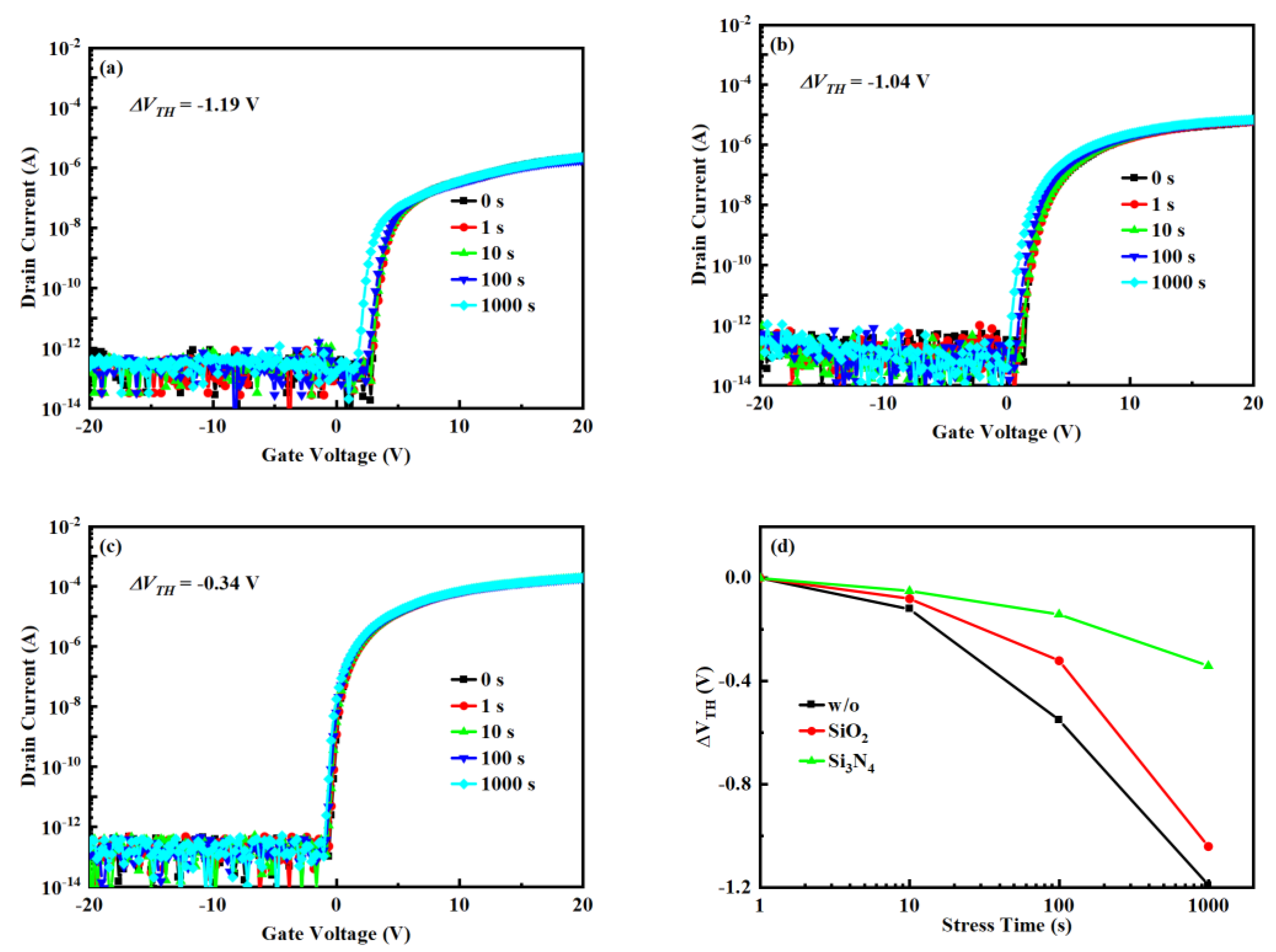

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Kim, D.G.; Ryu, S.H.; Jeong, H.J.; Park, J.S. Facile and Stable n+ Doping Process Via Simultaneous Ultraviolet and Thermal Energy for Coplanar ALD-IGZO Thin-Film Transistors. ACS Appl. Electron. Mater. 2021, 3, 3530–3537. [Google Scholar] [CrossRef]

- Wang, X.; Liang, L.; Zhang, H.; Wu, H.; Li, W.; Ning, C.; Yuan, G.; Cao, H. Huge mobility enhancement of InSnZnO thin-film transistors via Al-induced microstructure regularization. Appl. Phys. Lett. 2021, 119, 212102. [Google Scholar] [CrossRef]

- Peng, C.; Jiang, W.; Li, Y.; Li, X.; Zhang, J. Photoelectric IGZO Electric-double-layer transparent artificial synapses for emotional state simulation. ACS Appl. Electron. Mater. 2019, 1, 2406–2414. [Google Scholar] [CrossRef]

- Peng, C.; Yang, S.; Pan, C.; Li, X.; Zhang, J. Effect of Two-Step Annealing on High Stability of a-IGZO Thin-Film Transistor. IEEE Trans. Electron Devices 2020, 67, 4262–4268. [Google Scholar] [CrossRef]

- Peng, H.; Chang, B.; Fu, H.; Yang, H.; Zhang, Y.; Zhou, X.; Lu, L.; Zhang, S. Top-Gate Amorphous Indium-Gallium-Zinc-OxideThin-Film Transistors With Magnesium Metallized Source/Drain Regions. IEEE Trans. Electron Devices 2020, 67, 1619–1624. [Google Scholar] [CrossRef]

- Sun, J.; Xu, S.; Ren, H.; Wu, S.-T.P. 1:Distinguished Student Poster Paper: Submillisecond-response Polymer Network Liquid Crystal Cylindrical Microlens Array for 3D Displays. SID Symp. Dig. Tech. Pap. 2013, 44, 989–992. [Google Scholar] [CrossRef]

- Zhang, W.; Fan, Z.; Shen, A.; Dong, C. Atmosphere Effect in Post-Annealing Treatments for Amorphous InGaZnO Thin-Film Transistors with SiOx Passivation Layers. Micromachines 2021, 12, 1551. [Google Scholar] [CrossRef]

- Choi, S.; Park, J.; Hwang, S.H.; Kim, C.; Kim, Y.S.; Oh, S.; Baeck, J.H.; Bae, J.U.; Noh, J.; Lee, S.W.; et al. Excessive Oxygen Peroxide Model-Based Analysis of Positive-Bias-Stress and Negative-Bias-Illumination-Stress Instabilities in Self-Aligned Top-Gate Coplanar In-Ga-Zn-O Thin-Film Transistors. Adv. Electron. Mater. 2022, 8, 2101062. [Google Scholar] [CrossRef]

- Takechi, K.; Lin, F.; He, S.; Yuan, Y.; Tanaka, J.; Sera, K. Short-Channel Top-Gate InGaZnO Thin-Film Transistors Fabricated with Boron Implantation into Source/Drain Regions. IEEE Trans. Electron Devices 2021, 68, 4161–4163. [Google Scholar] [CrossRef]

- Yang, H.; Zhou, X.; Fu, H.; Chang, B.; Min, Y.; Peng, H.; Lu, L.; Zhang, S. Metal Reaction-Induced Bulk-Doping Effect in Forming Conductive Source-Drain Regions of Self-Aligned Top-Gate Amorphous InGaZnO Thin-Film Transistors. ACS Appl Mater Interfaces 2021, 13, 11442–11448. [Google Scholar] [CrossRef]

- Kim, Y.G.; Bukke, R.N.; Lee, J.; Saha, J.K.; Jang, J. Formation of F-Doped Offset Region for Spray Pyrolyzed Self-Aligned Coplanar Amorphous Zinc-Tin-Oxide Thin-Film Transistor by NF3 Plasma Treatment. IEEE Trans. Electron Devices 2021, 68, 1057–1062. [Google Scholar] [CrossRef]

- Chen, H.; Chen, J.; Zhou, K.; Chen, G.; Kuo, C.; Shih, Y.; Su, W.; Yang, C.; Huang, H.; Shih, C.; et al. Hydrogen Diffusion and Threshold Voltage Shifts in Top-Gate Amorphous InGaZnO Thin-Film Transistors. IEEE Trans. Electron Devices 2020, 67, 3123–3128. [Google Scholar] [CrossRef]

- Katsouras, I.; Frijters, C.; Poodt, P.; Gelinck, G.; Kronemeijer, A.J. Large-area spatial atomic layer deposition of amorphous oxide semiconductors at atmospheric pressure. J. Soc. Inf. Disp. 2019, 27, 304–312. [Google Scholar] [CrossRef]

- Zhang, Y.-Y.; Shin, S.-H.; Kang, H.-J.; Jeon, S.; Hwang, S.H.; Zhou, W.; Jeong, J.-H.; Li, X.; Kim, M. Anti-reflective porous Ge by open-circuit and lithography-free metal-assisted chemical etching. Appl. Surf. Sci. 2021, 546, 149083. [Google Scholar] [CrossRef]

- Kim, H.E.; Furuta, M.; Yoon, S.M. A Facile Doping Process of the Organic Inter-Layer Dielectric for Self-Aligned Coplanar In-Ga-Zn-O Thin-Film Transistors. IEEE Electron Device Lett. 2020, 41, 393–396. [Google Scholar] [CrossRef]

- Kim, M.M.; Kim, M.H.; Ryu, S.m.; Lim, J.H.; Choi, D.K. Coplanar homojunction a-InGaZnO thin film transistor fabricated using ultraviolet irradiation. RSC Adv. 2015, 5, 82947–82951. [Google Scholar] [CrossRef]

- Bukke, R.N.; Mude, N.N.; Saha, J.K.; Jang, J. High Performance of a-IZTO TFT by Purification of the Semiconductor Oxide Precursor. Adv. Mater. Interfaces 2019, 6, 1900277. [Google Scholar] [CrossRef]

- Taniguchi, S.; Yokozeki, M.; Ikeda, M.; Suzuki, T.-K. Transparent Oxide Thin-Film Transistors Using n-(In2O3)0.9(SnO2)0.1/InGaZnO4 Modulation-Doped Heterostructures. Jpn. J. Appl. Phys. 2011, 50, DF11. [Google Scholar] [CrossRef]

- Chen, C.; Yang, B.; Li, G.; Zhou, H.; Huang, B.; Wu, Q.; Zhan, R.; Noh, Y.; Minari, T.; Zhang, S.; et al. Analysis of Ultrahigh Apparent Mobility in Oxide Field-Effect Transistors. Adv Sci 2019, 6, 1801189. [Google Scholar] [CrossRef]

- Rabbi, M.H.; Billah, M.M.; Siddik, A.B.; Lee, S.; Lee, J.; Jang, J. Extremely Stable Dual Gate Coplanar Amorphous InGaZnO Thin Film Transistor With Split Active Layer by N2O Annealing. IEEE Electron Device Lett. 2020, 41, 1782–1785. [Google Scholar] [CrossRef]

- Bang, J.; Matsuishi, S.; Hosono, H. Hydrogen anion and subgap states in amorphous In–Ga–Zn–O thin films for TFT applications. Appl. Phys. Lett. 2017, 110, 232105. [Google Scholar] [CrossRef]

- Peng, C.; Dong, P.; Li, X. Improvement of solution-processed Zn-Sn-O active-layer thin film transistors by novel high valence Mo Doping. Nanotechnology 2020, 32, 025207. [Google Scholar] [CrossRef] [PubMed]

- Chowdhury, M.D.H.; Mativenga, M.; Um, J.G.; Mruthyunjaya, R.K.; Heiler, G.N.; Tredwell, T.J.; Jang, J. Effect of SiO2 and SiO2/SiNx Passivation on the Stability of Amorphous Indium-Gallium Zinc-Oxide Thin-Film Transistors Under High Humidity. IEEE Trans. Electron Devices 2015, 62, 869–874. [Google Scholar] [CrossRef]

| Treatment Methods | μ (cm2V−1s−1) | Resistivity (Ω·cm) | Temperature (℃) | References |

|---|---|---|---|---|

| PA/GI | 15.15 | 1.5 × 10−3 | 200 | This Work |

| Ion implantations | 7 | - | 350 | 2021 [9] |

| Metal reaction-induced | 13 | 2.4 × 10−3 | 200 | 2021 [10] |

| Plasma | 5.13 | 2 × 10−3 | 350 | 2021 [11] |

| Zeocoat | 18.84 | 3.8 × 10−4 | 150 | 2020 [15] |

| Interlayer dielectric layer | 14 | 3 × 10−3 | 250 | 2019 [13] |

| ultraviolet irradiation | 6.7 | 3 × 10−5 | 300 | 2015 [16] |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Peng, C.; Huang, H.; Xu, M.; Chen, L.; Li, X.; Zhang, J. A Simple Doping Process Achieved by Modifying the Passivation Layer for Self-Aligned Top-Gate In-Ga-Zn-O Thin-Film Transistors at 200 °C. Nanomaterials 2022, 12, 4021. https://doi.org/10.3390/nano12224021

Peng C, Huang H, Xu M, Chen L, Li X, Zhang J. A Simple Doping Process Achieved by Modifying the Passivation Layer for Self-Aligned Top-Gate In-Ga-Zn-O Thin-Film Transistors at 200 °C. Nanomaterials. 2022; 12(22):4021. https://doi.org/10.3390/nano12224021

Chicago/Turabian StylePeng, Cong, Huixue Huang, Meng Xu, Longlong Chen, Xifeng Li, and Jianhua Zhang. 2022. "A Simple Doping Process Achieved by Modifying the Passivation Layer for Self-Aligned Top-Gate In-Ga-Zn-O Thin-Film Transistors at 200 °C" Nanomaterials 12, no. 22: 4021. https://doi.org/10.3390/nano12224021

APA StylePeng, C., Huang, H., Xu, M., Chen, L., Li, X., & Zhang, J. (2022). A Simple Doping Process Achieved by Modifying the Passivation Layer for Self-Aligned Top-Gate In-Ga-Zn-O Thin-Film Transistors at 200 °C. Nanomaterials, 12(22), 4021. https://doi.org/10.3390/nano12224021