Cryogenic Transport Characteristics of P-Type Gate-All-Around Silicon Nanowire MOSFETs

Abstract

1. Introduction

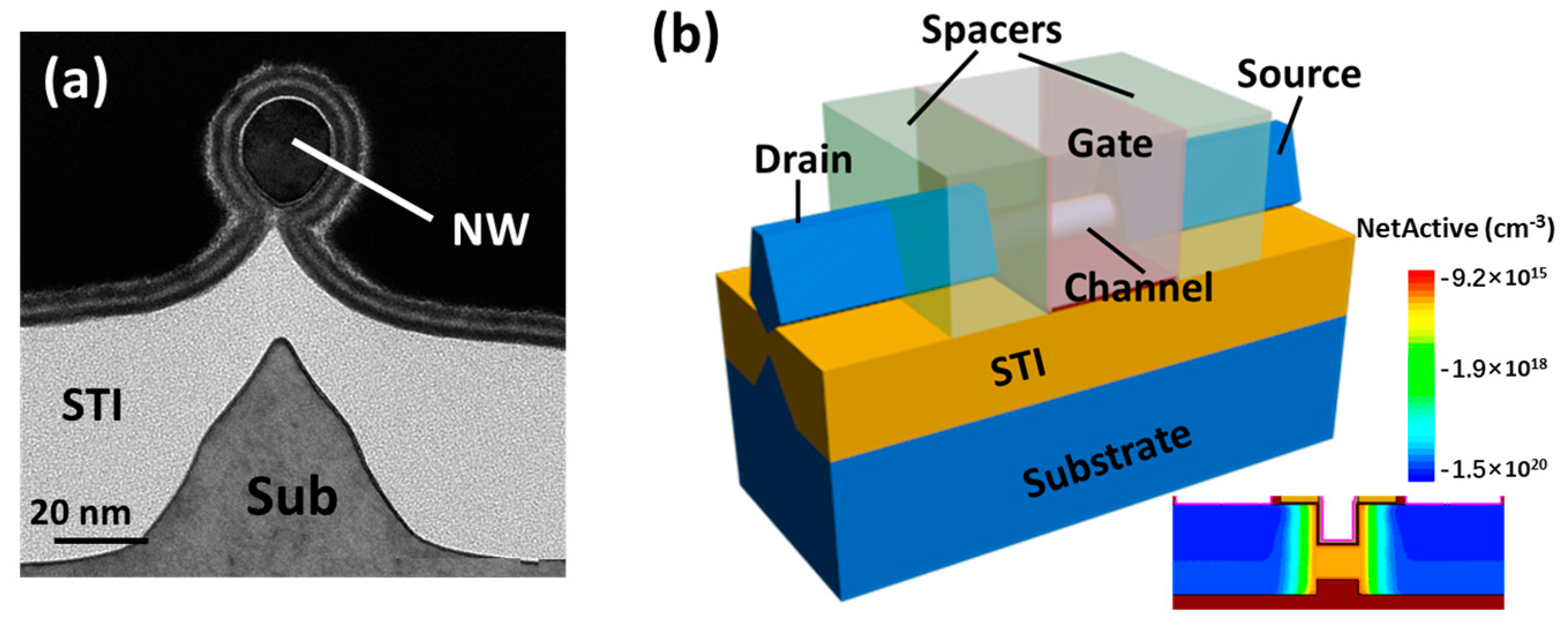

2. Materials and Methods

3. Results and Discussion

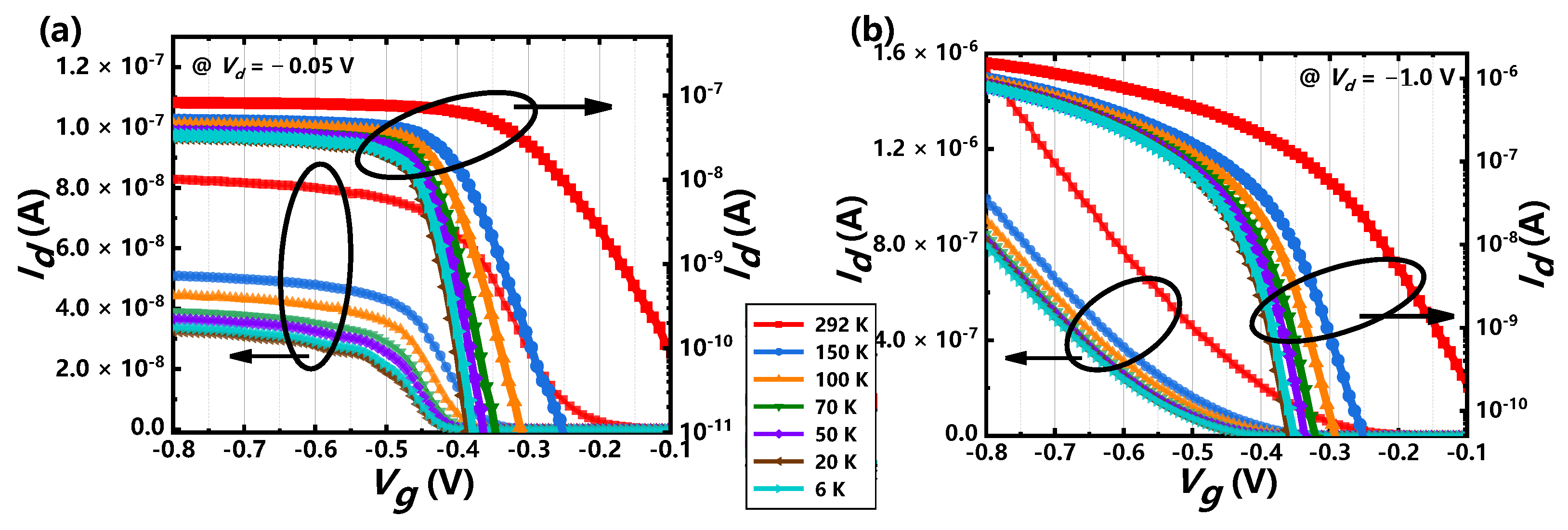

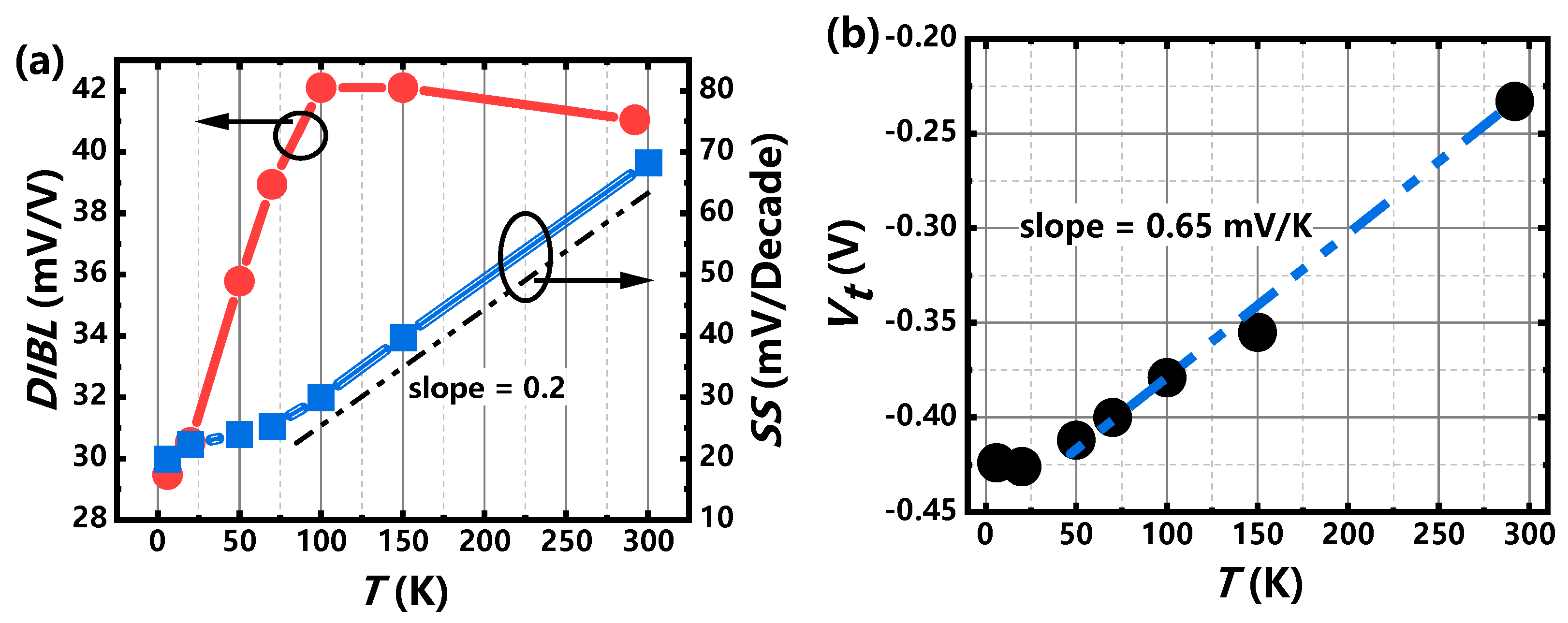

3.1. Cryogenic CMOS Characteristics

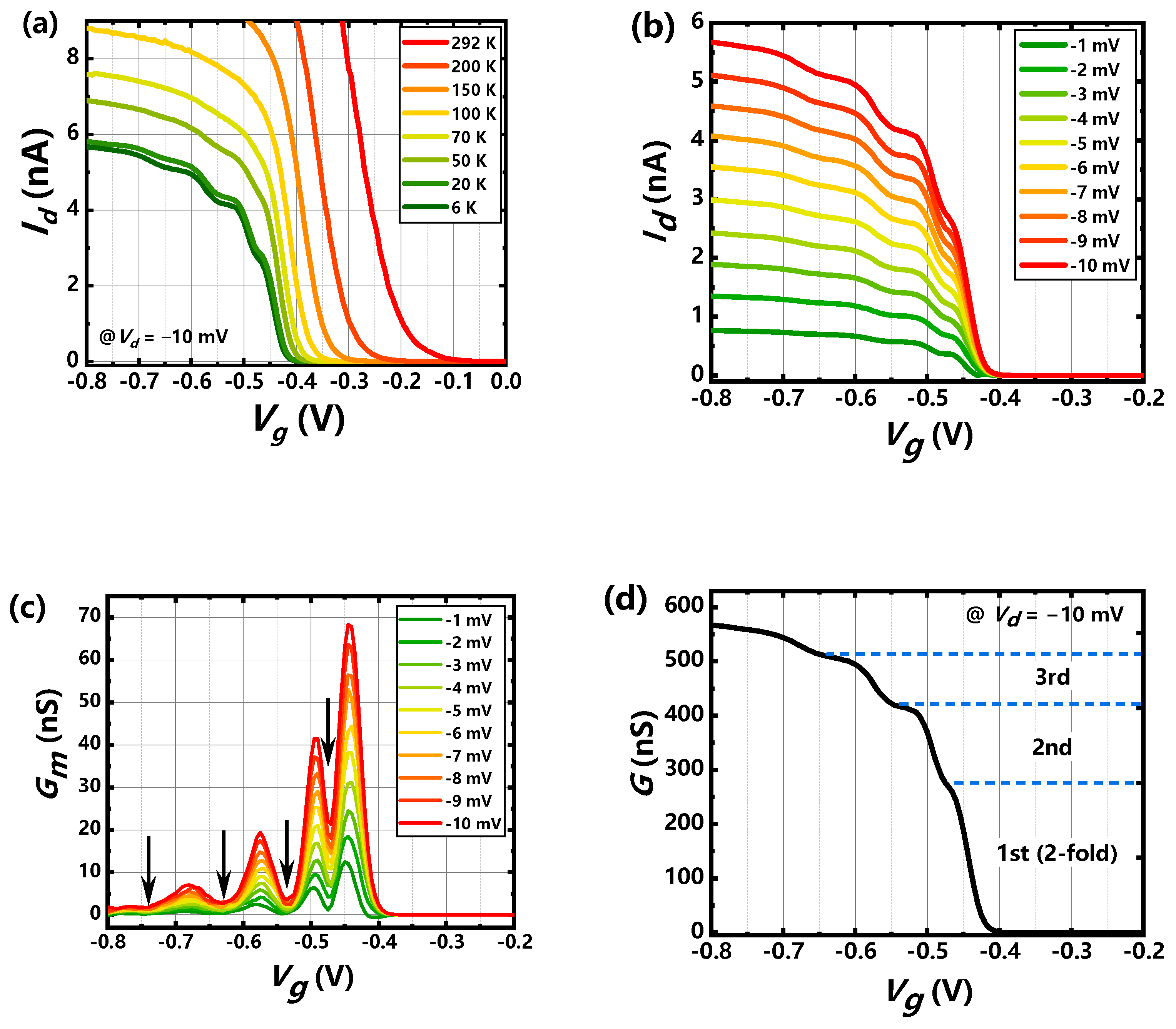

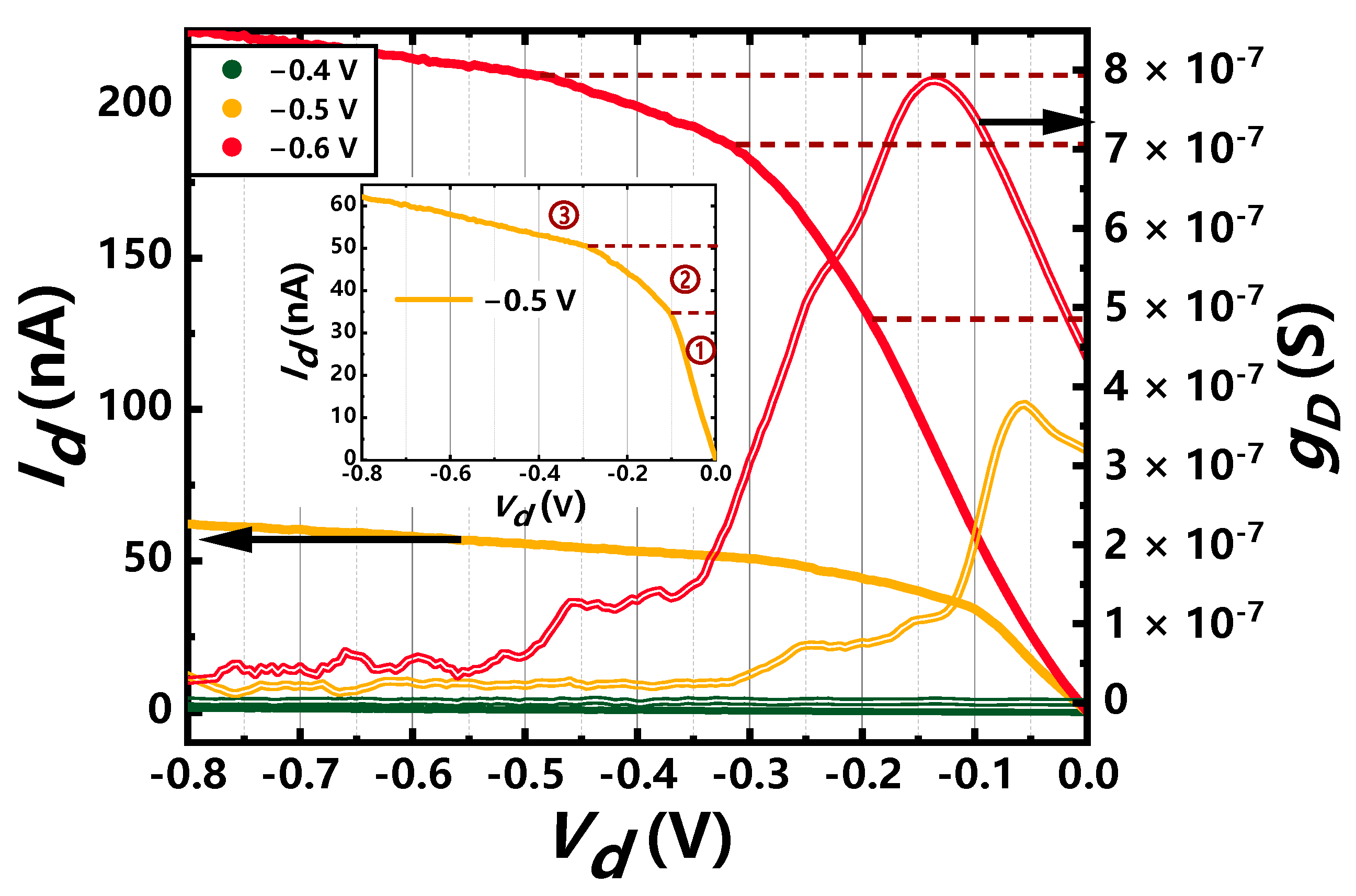

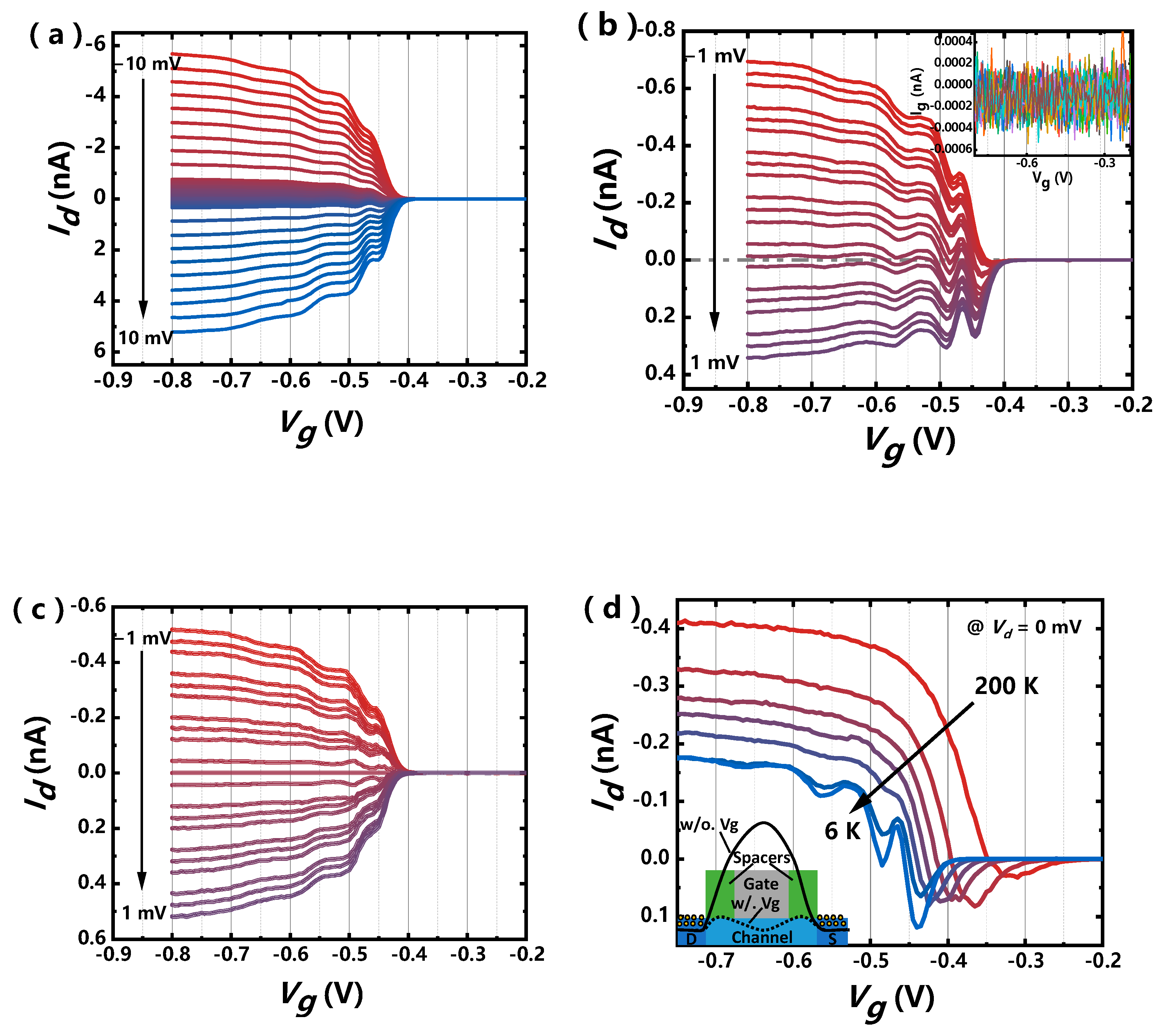

3.2. Low-Dimensional Hole Transport

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Kolodrubetz, M.H.; Petta, J.R. Coherent holes in a semiconductor quantum dot. Science 2009, 325, 42–43. [Google Scholar] [CrossRef]

- Reilly, D.J. Challenges in Scaling-up the Control Interface of a Quantum Computer. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 31.37.31–31.37.36. [Google Scholar]

- Maurand, R.; Jehl, X.; Kotekar-Patil, D.; Corna, A.; Bohuslavskyi, H.; Laviéville, R.; Hutin, L.; Barraud, S.; Vinet, M.; Sanquer, M.; et al. A CMOS silicon spin qubit. Nat. Commun. 2016, 7, 13575. [Google Scholar] [CrossRef]

- Bourdet, L.; Hutin, L.; Bertrand, B.; Corna, A.; Bohuslavskyi, H.; Amisse, A.; Crippa, A.; Maurand, R.; Barraud, S.; Urdampilleta, M.; et al. All-electrical control of a hybrid electron spin/valley quantum bit in SOI CMOS technology. IEEE Trans. Electron Devices 2018, 65, 5151–5156. [Google Scholar] [CrossRef]

- Pillarisetty, R.; George, H.C.; Watson, T.F.; Lampert, L.; Thomas, N.; Bojarski, S.; Amin, P.; Caudillo, R.; Henry, E.; Kashani, N.; et al. High Volume Electrical Characterization of Semiconductor Qubits. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 31.35.31–31.35.34. [Google Scholar]

- Gong, J.; Chen, Y.; Sebastiano, F.; Charbon, E.; Babaie, M. 19.3 A 200dB FoM 4-to-5GHz Cryogenic Oscillator with an Automatic Common-Mode Resonance Calibration for Quantum Computing Applications. In Proceedings of the 2020 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 308–310. [Google Scholar]

- Beckers, A.; Jazaeri, F.; Enz, C. Cryogenic MOS Transistor Model. IEEE Trans. Electron Devices 2018, 65, 3617–3625. [Google Scholar] [CrossRef]

- Beckers, A.; Jazaeri, F.; Ruffino, A.; Bruschini, C.; Baschirotto, A.; Enz, C. Cryogenic characterization of 28 nm bulk CMOS technology for quantum computing. In Proceedings of the 2017 47th European Solid-State Device Research Conference (ESSDERC), Leuven, Belgium, 11–14 September 2017; pp. 62–65. [Google Scholar]

- Bohuslavskyi, H.; Barraud, S.; Cassé, M.; Barrai, V.; Bertrand, B.; Hutin, L.; Arnaud, F.; Galy, P.; Sanquer, M.; De Franceschi, S. 28 nm Fully-depleted SOI technology: Cryogenic control electronics for quantum computing. In Proceedings of the Silicon Nanoelectronics Workshop (SNW), Kyoto, Japan, 4–5 June 2017; pp. 143–144. [Google Scholar]

- Paz, B.C.; Pavanello, M.A.; Cassé, M.; Barraud, S.; Reimbold, G.; Vinet, M.; Faynot, O. Cryogenic operation of Ω-gate p-type SiGe-on-insulator nanowire MOSFETs. In Proceedings of the 2018 Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon (EUROSOI-ULIS), Granada, Spain, 19–21 March 2018; pp. 1–4. [Google Scholar]

- Bohuslavskyi, H.; Jansen, A.G.M.; Barraud, S.; Barral, V.; Cassé, M.; Guevel, L.L.; Jehl, X.; Hutin, L.; Bertrand, B.; Billiot, G.; et al. Cryogenic Subthreshold Swing Saturation in FD-SOI MOSFETs Described With Band Broadening. IEEE Electron Device Lett. 2019, 40, 784–787. [Google Scholar] [CrossRef]

- Guevel, L.L.; Billiot, G.; Jehl, X.; Franceschi, S.D.; Zurita, M.; Thonnart, Y.; Vinet, M.; Sanquer, M.; Maurand, R.; Jansen, A.G.M.; et al. 19.2 A 110mK 295µW 28nm FDSOI CMOS Quantum Integrated Circuit with a 2.8GHz Excitation and nA Current Sensing of an On-Chip Double Quantum Dot. In Proceedings of the 2020 IEEE International Solid- State Circuits Conference—(ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 306–308. [Google Scholar]

- Patra, B.; Dijk, J.P.G.v.; Subramanian, S.; Corna, A.; Xue, X.; Jeon, C.; Sheikh, F.; Juarez-Hernandez, E.; Esparza, B.P.; Rampurawala, H.; et al. 19.1 A Scalable Cryo-CMOS 2-to-20GHz Digitally Intensive Controller for 4 × 32 Frequency Multiplexed Spin Qubits/Transmons in 22nm FinFET Technology for Quantum Computers. In Proceedings of the 2020 IEEE International Solid- State Circuits Conference—(ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 304–306. [Google Scholar]

- Saremi, M.; Afzali-Kusha, A.; Mohammadi, S. Ground plane fin-shaped field effect transistor (GP-FinFET): A FinFET for low leakage power circuits. Microelectron. Eng. 2012, 95, 74–82. [Google Scholar] [CrossRef]

- Molaei Imen Abadi, R.; Saremi, M. A Resonant Tunneling Nanowire Field Effect Transistor with Physical Contractions: A Negative Differential Resistance Device for Low Power Very Large Scale Integration Applications. J. Electron. Mater. 2017, 47, 1091–1098. [Google Scholar] [CrossRef]

- Imenabadi, R.M.; Saremi, M.; Vandenberghe, W.G. A Novel PNPN-Like Z-Shaped Tunnel Field- Effect Transistor With Improved Ambipolar Behavior and RF Performance. IEEE Trans. Electron Devices 2017, 64, 4752–4758. [Google Scholar] [CrossRef]

- Radamson, H.H.; Zhu, H.; Wu, Z.; He, X.; Lin, H.; Liu, J.; Xiang, J.; Kong, Z.; Xiong, W.; Li, J.; et al. State of the Art and Future Perspectives in Advanced CMOS Technology. Nanomaterials 2020, 10, 1555. [Google Scholar] [CrossRef]

- Kim, S.; Kim, J.; Jang, D.; Ritzenthaler, R.; Parvais, B.; Mitard, J.; Mertens, H.; Chiarella, T.; Horiguchi, N.; Lee, J.W. Comparison of Temperature Dependent Carrier Transport in FinFET and Gate-All-Around Nanowire FET. Appl. Sci. 2020, 10, 2979. [Google Scholar] [CrossRef]

- Colinge, J.P. Quantum-wire effects in trigate SOI MOSFETs. Solid-State Electron. 2007, 51, 1153–1160. [Google Scholar] [CrossRef]

- Kim, R.; Lundstrom, M.S. Characteristic Features of 1-D Ballistic Transport in Nanowire MOSFETs. IEEE Trans. Nanotechnol. 2008, 7, 787–794. [Google Scholar] [CrossRef]

- Yao, J.; Yin, H.; Wang, W.; Li, J.; Luo, K.; Yu, J.; Zhang, Q.; Hou, Z.; Gu, J.; Yang, W.; et al. Physical Insights on Quantum Confinement and Carrier Mobility in Si, Si0.45Ge0.55, Ge Gate-All-Around NSFET for 5 nm Technology Node. IEEE J. Electron Devices Soc. 2018, 6, 841–848. [Google Scholar] [CrossRef]

- Zhang, Q.; Yin, H.; Meng, L.; Yao, J.; Li, J.; Wang, G.; Li, Y.; Wu, Z.; Xiong, W.; Yang, H.; et al. Novel GAA Si nanowire p-MOSFETs with excellent short-channel effect immunity via an advanced forming process. IEEE Electron Device Lett. 2018, 39, 464–467. [Google Scholar] [CrossRef]

- Burchak, O.; Keller, C.; Lapertot, G.; Salaun, M.; Danet, J.; Chen, Y.; Bendiab, N.; Pepin-Donat, B.; Lombard, C.; Faure-Vincent, J.; et al. Scalable chemical synthesis of doped silicon nanowires for energy applications. Nanoscale 2019, 11, 22504–22514. [Google Scholar] [CrossRef]

- Leonardi, A.A.; Nastasi, F.; Morganti, D.; Lo Faro, M.J.; Picca, R.A.; Cioffi, N.; Franzò, G.; Serroni, S.; Priolo, F.; Puntoriero, F.; et al. New Hybrid Light Harvesting Antenna Based on Silicon Nanowires and Metal Dendrimers. Adv. Opt. Mater. 2020, 8. [Google Scholar] [CrossRef]

- Zhang, Q.; Yin, H.; Luo, J.; Yang, H.; Meng, L.; Li, Y.; Wu, Z.; Zhang, Y.; Zhang, Y.; Qin, C.; et al. FOI FinFET with ultra-low parasitic resistance enabled by fully metallic source and drain formation on isolated bulk-fin. In Proceedings of the Electron Devices Meeting (IEDM), 2016 IEEE International, San Francisco, CA, USA, 3–7 December 2016; pp. 17.13.11–17.13.14. [Google Scholar]

- Beckers, A.; Jazaeri, F.; Bohuslavskyi, H.; Hutin, L.; De Franceschi, S.; Enz, C. Characterization and modeling of 28-nm FDSOI CMOS technology down to cryogenic temperatures. Solid-State Electron. 2019, 159, 106–115. [Google Scholar] [CrossRef]

- Yan, Z.X.; Deen, M.J. Substrate bias effects on drain-induced barrier lowering in short channel PMOS devices at 77 K. Cryogenics 1990, 30, 1160–1165. [Google Scholar] [CrossRef]

- Pavanello, M.A.; Martino, J.A.; Simoen, E.; Claeys, C. Analysis of Temperature-Induced Saturation Threshold Voltage Degradation in Deep-Submicrometer Ultrathin SOI MOSFETs. IEEE Trans. Electron Devices 2005, 52, 2236–2242. [Google Scholar] [CrossRef]

- Achour, H.; Cretu, B.; Routoure, J.M.; Carin, R.; Talmat, R.; Benfdila, A.; Simoen, E.; Claeys, C. In depth static and low-frequency noise characterization of n-channel FinFETs on SOI substrates at cryogenic temperature. Solid-State Electron. 2014, 98, 12–19. [Google Scholar] [CrossRef]

- Hafez, I.M.; Ghibaudo, G.; Balestra, F. Assessment of interface state density in silicon metal-oxide-semiconductor transistors at room, liquid-nitrogen, and liquid-helium temperatures. J. Appl. Phys. 1990, 67, 1950–1952. [Google Scholar] [CrossRef]

- Kawaura, H.; Sakamoto, T.; Baba, T. Observation of source-to-drain direct tunneling current in 8 nm gate electrically variable shallow junction metal–oxide–semiconductor field-effect transistors. Appl. Phys. Lett. 2000, 76, 3810–3812. [Google Scholar] [CrossRef]

- Wei, H.W.; Ruslan, S.H. Investigation of FDSOI and PDSOI MOSFET characteristics. In Proceedings of the Advances in electrical and electronic engineering: From theory to applications (series 2): Proceedings of the International Conference of Electrical and Electronic Engineering (ICon3E 2019), Putrajaya, Malaysia, 24–25 June 2019. [Google Scholar]

- Groeseneken, G.; Colinge, J.P.; Maes, H.E.; Alderman, J.C.; Holt, S. Temperature dependence of threshold voltage in thin-film SOI MOSFETs. IEEE Electron Device Lett. 1990, 11, 329–331. [Google Scholar] [CrossRef]

- Omura, Y.; Nakakubo, A.; Nakatsuji, H. Quantum mechanical effect in temperature dependence of threshold voltage of extremely thin SOI MOSFETs. Solid-State Electron. 2004, 48, 1661–1666. [Google Scholar] [CrossRef]

- Jonscher, A.K. Semiconductors at cryogenic temperatures. Proc. IEEE 1964, 52, 1092–1104. [Google Scholar] [CrossRef]

- Trivedi, K.; Yuk, H.; Floresca, H.C.; Kim, M.J.; Hu, W. Quantum Confinement Induced Performance Enhancement in Sub-5-nm Lithographic Si Nanowire Transistors. Nano Lett. 2011, 11, 1412–1417. [Google Scholar] [CrossRef]

- Li, X.; Han, W.; Wang, H.; Ma, L.; Zhang, Y.; Du, Y.; Yang, F. Low-temperature electron mobility in heavily n-doped junctionless nanowire transistor. Appl. Phys. Lett. 2013, 102. [Google Scholar] [CrossRef]

- Yi, K.S.; Trivedi, K.; Floresca, H.C.; Yuk, H.; Hu, W.; Kim, M.J. Room-temperature quantum confinement effects in transport properties of ultrathin Si nanowire field-effect transistors. Nano Lett. 2011, 11, 5465–5470. [Google Scholar] [CrossRef]

- Neophytou, N.; Paul, A.; Klimeck, G. Bandstructure Effects in Silicon Nanowire Hole Transport. IEEE Trans. Nanotechnol. 2008, 7, 710–719. [Google Scholar] [CrossRef][Green Version]

- Shin, M.; Lee, S.; Klimeck, G. Computational Study on the Performance of Si Nanowire pMOSFETs Based on the $ k\cdot p $ Method. IEEE Trans. Electron Devices 2010, 57, 2274–2283. [Google Scholar] [CrossRef]

- Ford, A.C.; Kumar, S.B.; Kapadia, R.; Guo, J.; Javey, A. Observation of degenerate one-dimensional sub-bands in cylindrical InAs nanowires. Nano Lett. 2012, 12, 1340–1343. [Google Scholar] [CrossRef] [PubMed]

- Wharam, D.A.; Thornton, T.J.; Newbury, R.; Pepper, M.; Ahmed, H.; Frost, J.E.F.; Hasko, D.G.; Peacock, D.C.; Ritchie, D.A.; Jones, G.A.C. One-dimensional transport and the quantisation of the ballistic resistance. J. Phys. C Solid State Phys. 1988, 21, L209–L214. [Google Scholar] [CrossRef]

- Natori, K.; Kimura, Y.; Shimizu, T. Characteristics of a carbon nanotube field-effect transistor analyzed as a ballistic nanowire field-effect transistor. J. Appl. Phys. 2005, 97, 034306. [Google Scholar] [CrossRef]

- Schupp, F.J.; Mirza, M.M.; MacLaren, D.A.; Briggs, G.A.D.; Paul, D.J.; Mol, J.A. Quantum interference in silicon one-dimensional junctionless nanowire field-effect transistors. Phys. Rev. B 2018, 98, 235428. [Google Scholar] [CrossRef]

- Biercuk, M.J.; Mason, N.; Martin, J.; Yacoby, A.; Marcus, C.M. Anomalous conductance quantization in carbon nanotubes. Phys. Rev. Lett. 2005, 94, 026801. [Google Scholar] [CrossRef]

- Nakashima, H.; Uozumi, K. Zero-bias current in a single-electron transistor with identical trapezoidal tunnelling barriers for finite fixed gate voltages. J. Phys. Condens. Matter 1998, 10, 4291–4296. [Google Scholar] [CrossRef]

| Gate Length | EOT | NW Diameter | Channel Concentration | S/D Concentration |

|---|---|---|---|---|

| 16 nm | 1 nm | 18 nm | 1 × 1017 cm−3 | 1 × 1020 cm−3 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gu, J.; Zhang, Q.; Wu, Z.; Yao, J.; Zhang, Z.; Zhu, X.; Wang, G.; Li, J.; Zhang, Y.; Cai, Y.; et al. Cryogenic Transport Characteristics of P-Type Gate-All-Around Silicon Nanowire MOSFETs. Nanomaterials 2021, 11, 309. https://doi.org/10.3390/nano11020309

Gu J, Zhang Q, Wu Z, Yao J, Zhang Z, Zhu X, Wang G, Li J, Zhang Y, Cai Y, et al. Cryogenic Transport Characteristics of P-Type Gate-All-Around Silicon Nanowire MOSFETs. Nanomaterials. 2021; 11(2):309. https://doi.org/10.3390/nano11020309

Chicago/Turabian StyleGu, Jie, Qingzhu Zhang, Zhenhua Wu, Jiaxin Yao, Zhaohao Zhang, Xiaohui Zhu, Guilei Wang, Junjie Li, Yongkui Zhang, Yuwei Cai, and et al. 2021. "Cryogenic Transport Characteristics of P-Type Gate-All-Around Silicon Nanowire MOSFETs" Nanomaterials 11, no. 2: 309. https://doi.org/10.3390/nano11020309

APA StyleGu, J., Zhang, Q., Wu, Z., Yao, J., Zhang, Z., Zhu, X., Wang, G., Li, J., Zhang, Y., Cai, Y., Xu, R., Xu, G., Xu, Q., Yin, H., Luo, J., Wang, W., & Ye, T. (2021). Cryogenic Transport Characteristics of P-Type Gate-All-Around Silicon Nanowire MOSFETs. Nanomaterials, 11(2), 309. https://doi.org/10.3390/nano11020309