Exploring Strategies to Contact 3D Nano-Pillars

Abstract

1. Introduction

2. Experimental Section

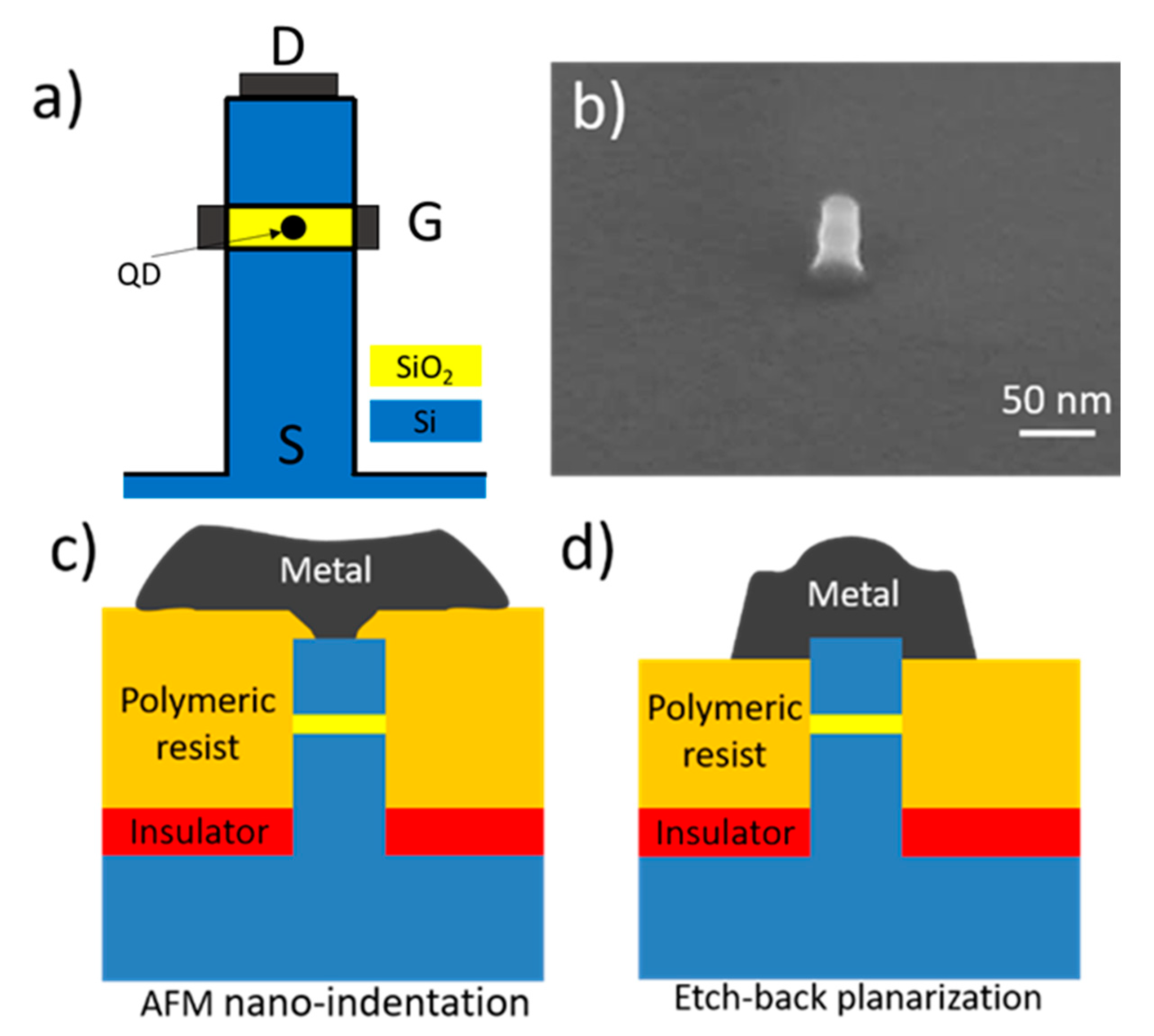

2.1. Device Concept and Fabrication Process

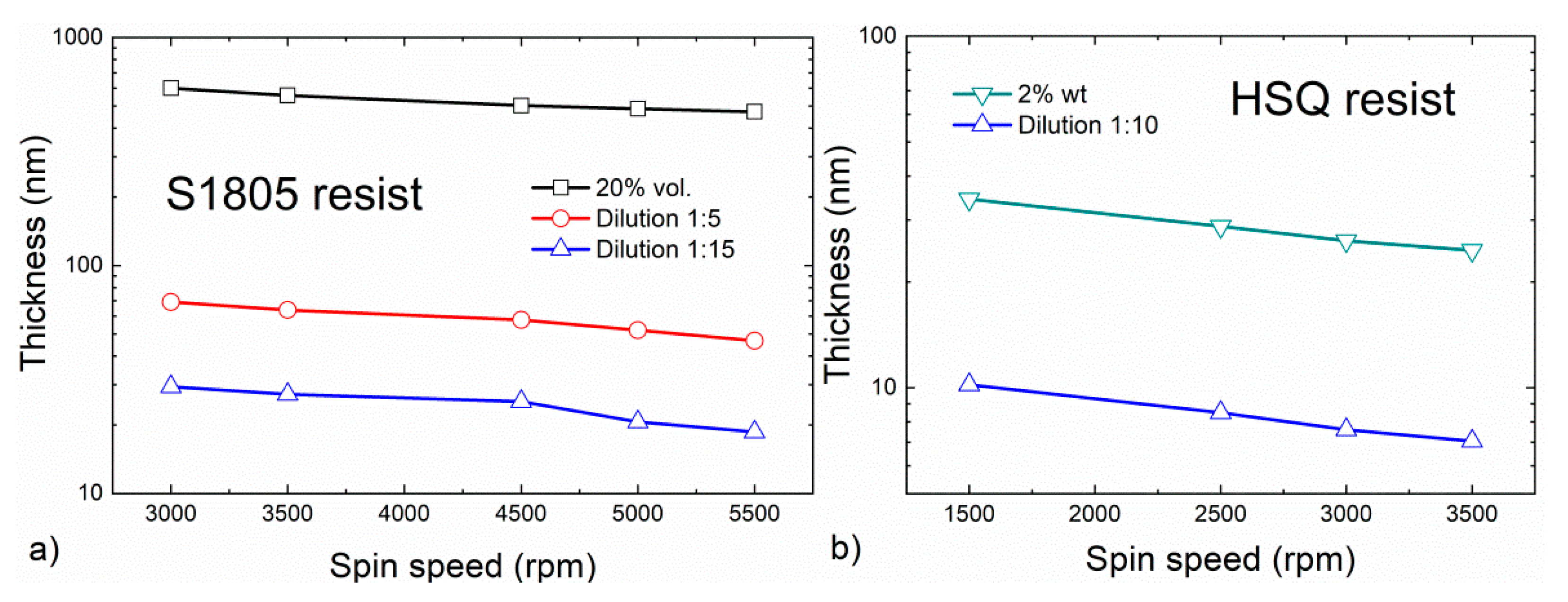

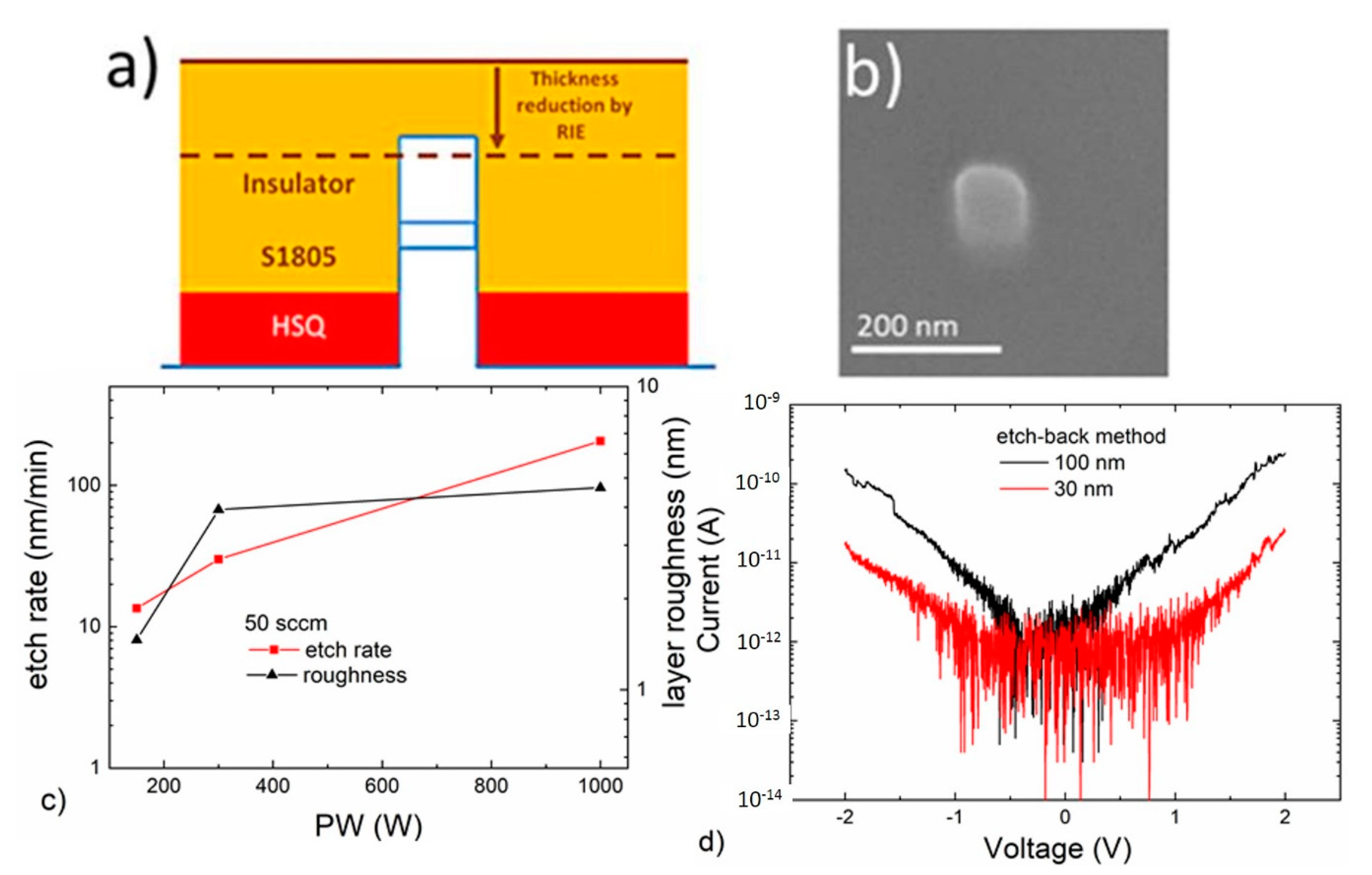

2.2. Planarization

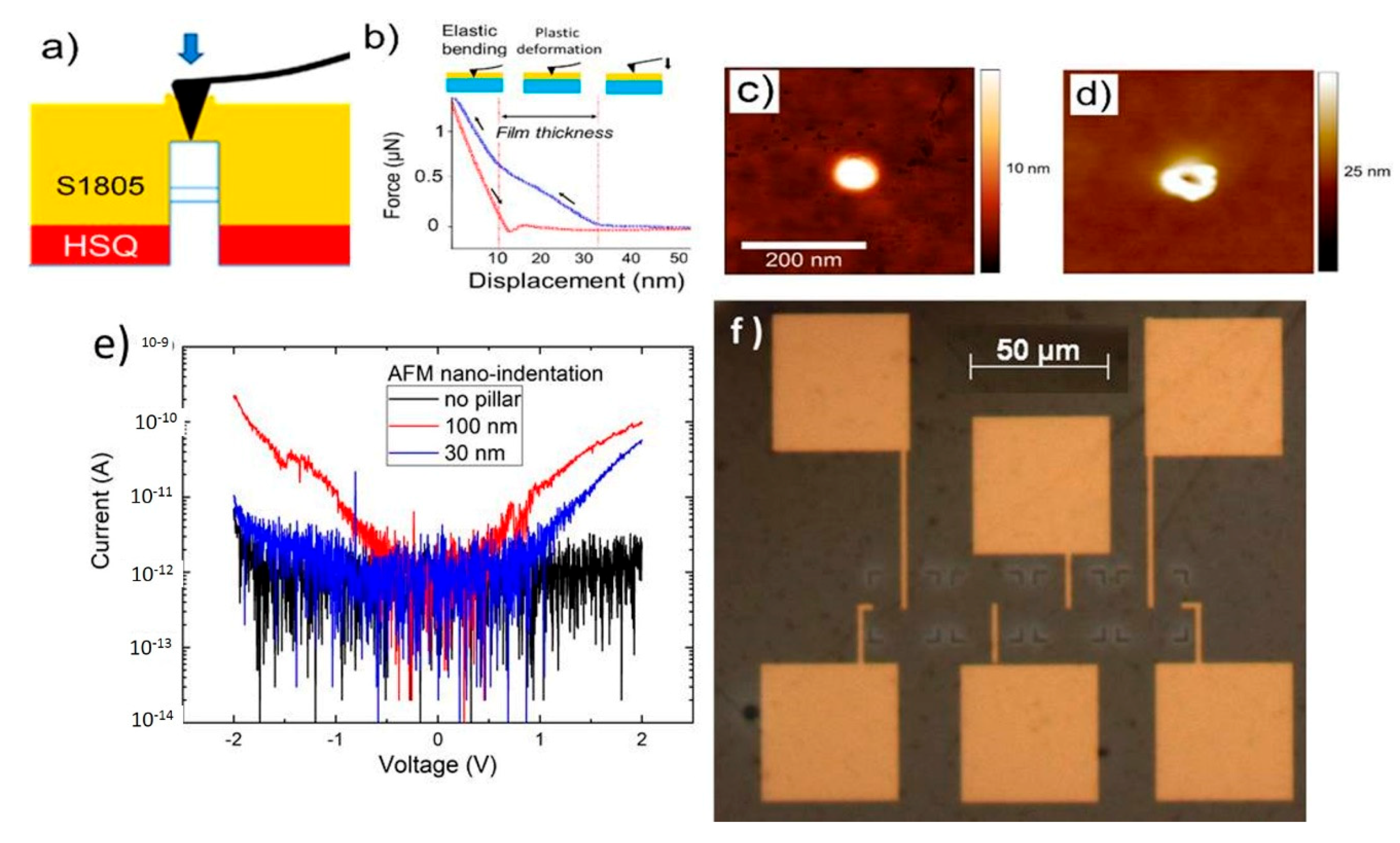

2.3. AFM Nano-Indentation and Characterization

2.4. Definition of Metal Contacts

3. Realization of Top Metal Contacts

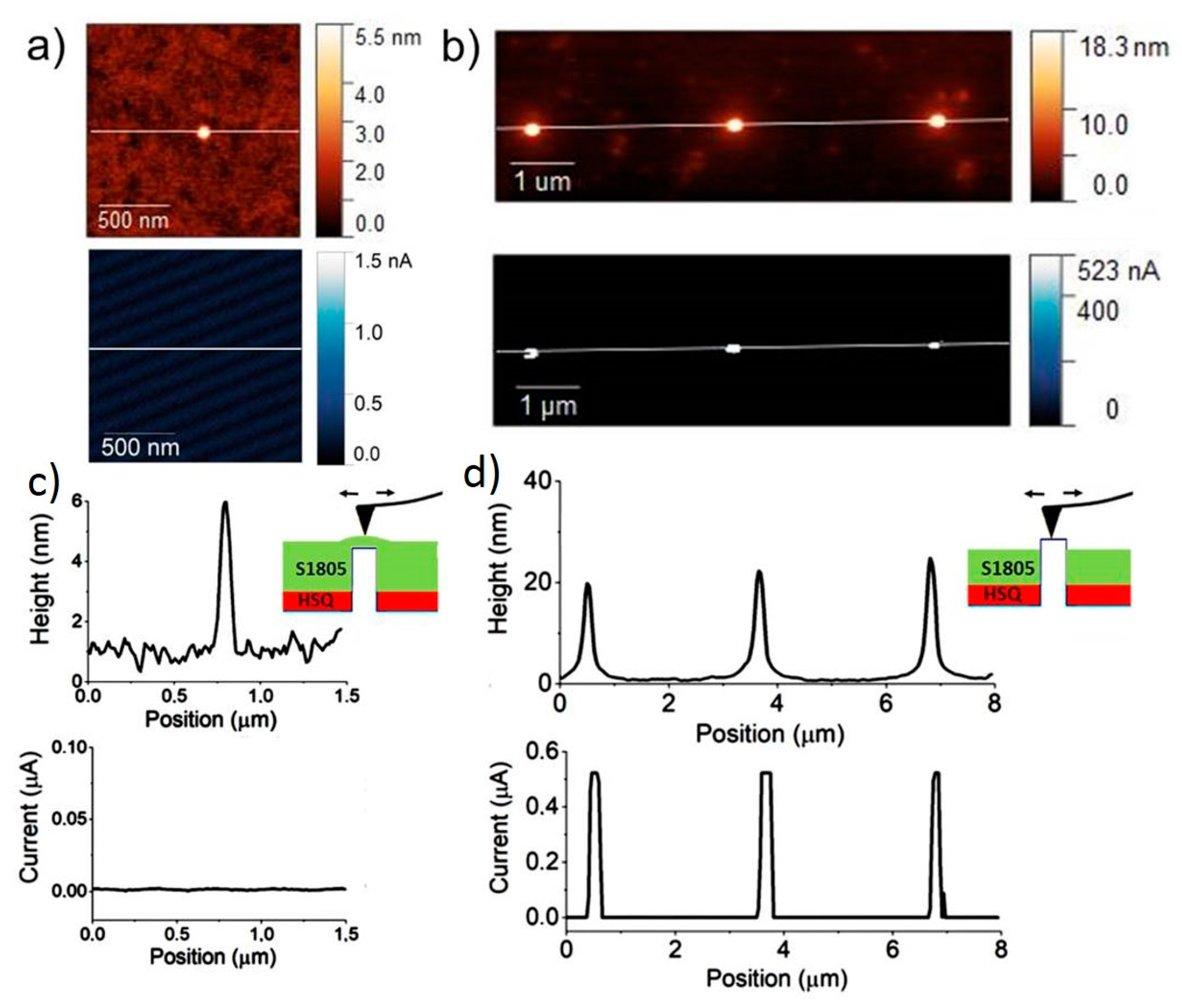

3.1. Contacting by AFM Nano-Indentation

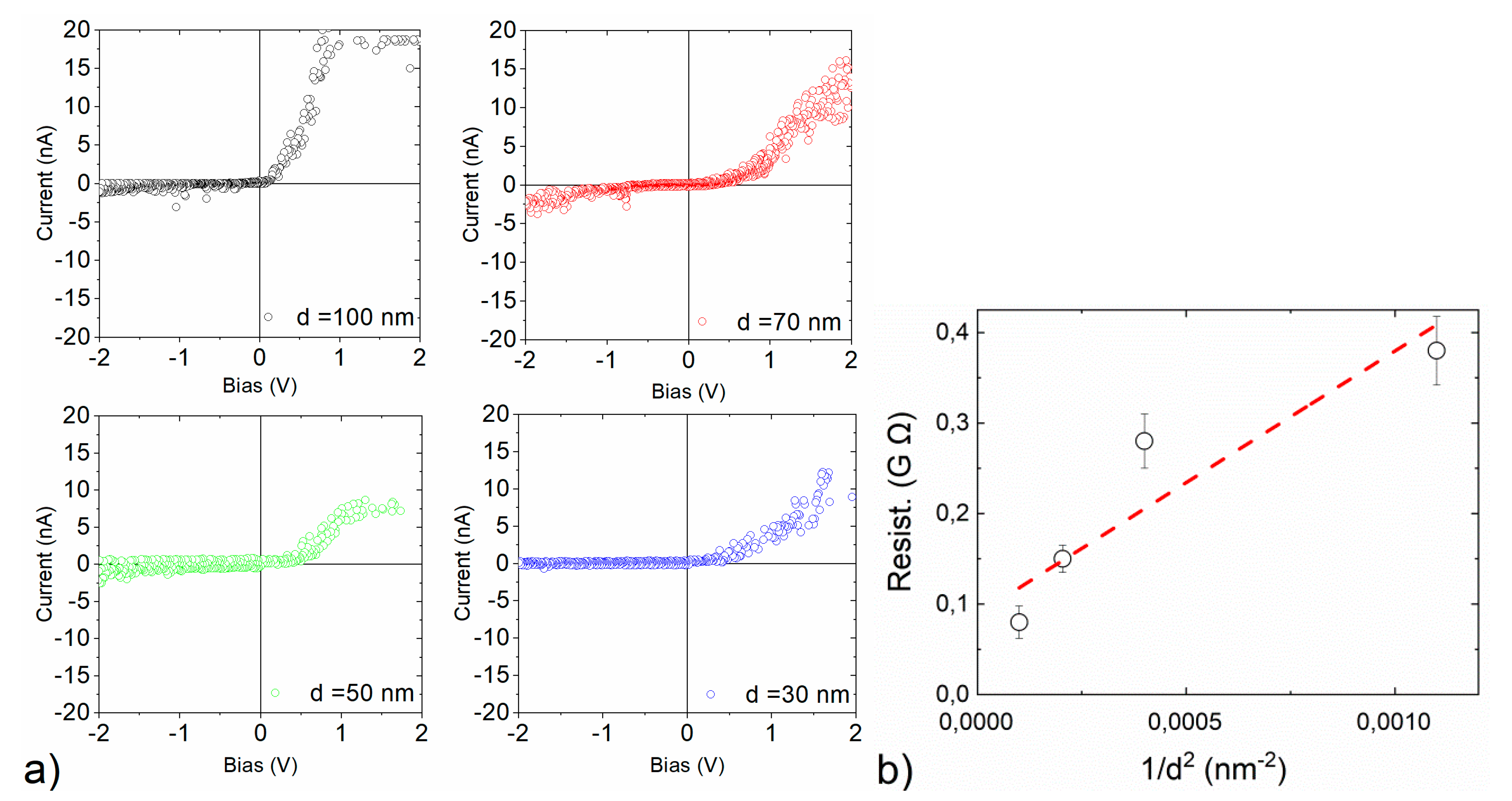

3.2. Pillars Contacted by Etch-Back Process

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Keshavarzi, A.; Somasekhar, D.; Rashed, M.; Ahmed, S.; Maitra, K.; Miller, R.; Knorr, A.; Cho, J.; Augur, R.; Banna, S.; et al. Architecting advanced technologies for 14nm and beyond with 3D FinFET transistors for the future SoC applications. IEEE Int. Electron. Devices Meet. 2011, 1–4. [Google Scholar]

- Yakimets, D.; Bao, T.H.; Bardon, M.G.; Dehan, M.; Collaert, N.; Mercha, A.; Tokei, Z.; Thean, A.; Verkest, D.; De Meyer, K. Lateral versus vertical gate-all-around FETs for beyond 7nm technologies. Device Res. Conf. 2014, 133–134. [Google Scholar]

- Klüpfel, F.J.; Pichler, P. 3D simulation of silicon-based single-electron transistors. Int. Conf. Simul. Semicond. Process. Devices 2017, 77–80. [Google Scholar]

- Amat, E.; Bausells, J.; Perez-Murano, F. Exploring the Influence of Variability on Single-Electron Transistors Into SET-Based Circuits. IEEE Trans. Electron. Devices 2017, 64, 5172–5180. [Google Scholar] [CrossRef]

- Choi, C.; Yoon, Y.; Hong, D.; Oh, Y.; Talke, F.E.; Jin, S. Planarization of patterned magnetic recording media to enable head flyability. Microsyst. Technol. 2011, 17, 395–402. [Google Scholar] [CrossRef]

- Guerfi, Y.; Larrieu, G. Vertical Silicon Nanowire Field Effect Transistors with Nanoscale Gate-All-Around. Nanoscale Res. Lett. 2016, 11, 1–7. [Google Scholar] [CrossRef] [PubMed]

- Wiesauer, K.; Springholz, G. Fabrication of semiconductor nanostructures by nanoindentation of photoresist layers using atomic force microscopy. J. Appl. Phys. 2000, 88. [Google Scholar] [CrossRef]

- Bouzehouane, K.; Fusil, S.; Bibes, M.; Carrey, J.; Blon, T.; Dû, M.L.; Seneor, P.; Cros, V.; Vila, L. Nanolithography Based on Real-Time Electrically Controlled Indentation with an Atomic Force Microscope for Nanocontact Elaboration. Nano Lett. 2003, 3, 1599–1602. [Google Scholar] [CrossRef][Green Version]

- Jeon, S.; Ryu, B.; Jhe, W.; Khim, Z.G.; Kim, B.I. Reproducible nanostructure fabrication using atomic force microscopy indentation with minimal tip damage. J. Vac. Sci. Technol. B 2014, 32. [Google Scholar] [CrossRef]

- Gharbi, A.; Tiron, R.; Argoud, M.; Chamiot-Maitral, G.; Fouquet, A.; Lapeyre, C.; Pimenta-Barros, P.; Delachat, F.; Bos, S.; Bouanani, S.; et al. Process highlights to enhance directed self-assembly contact patterning performances. J. Micro/Nanolithogr. MEMS MOEMS 2016, 15, 43503–43506. [Google Scholar] [CrossRef]

- Pourteau, M.-L.; Gharbi, A.; Brianceau, P.; Dallery, J.-A.; Laulagnet, F.; Rademaker, G.; Tiron, R.; von Borany, J.; Heining, K.H.; Engelmann, H.-J.; et al. Sub-15 nm multilayer nanopillar patterning for hybrid SET/CMOS integration. In Proceedings of the Micro and Nanotechnology Conference, Macau, China, 22–26 July 2019. [Google Scholar]

- Tavakkoli, K.G.A.; Piramanayagam, S.N.; Ranjbar, M.; Sbiaa, R.; Chong, T.C. Path to achieve sub-10-nm half-pitch using electron beam lithography. J. Vac. Sci. Technol. B 2011, 29. [Google Scholar] [CrossRef]

- Grigorescu, A.E.; Hagen, C.W. Resists for sub-20-nm electron beam lithography with a focus on HSQ: State of the art. Nanotechnology 2009, 20, 292001. [Google Scholar] [CrossRef] [PubMed]

- Lorenzoni, M.; Pérez-Murano, F. Conductive Atomic Force Microscopy for Nanolithography Based on Local Anodic Oxidation. In Conductive Atomic Force Microscopy; Wiley-VCH Verlag GmbH & Co. KGaA: Weinheim, Germany, 2017; pp. 211–223. ISBN 9783527699773. [Google Scholar]

- Fourdrinier, L.; Le Poche, H.; Chevalier, N.; Mariolle, D.; Rouviere, E. Electrical properties measurements on individual carbon nanofibers by scanning spreading resistance microscopy. J. Appl. Phys. 2008, 104, 114305. [Google Scholar] [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Amat, E.; del Moral, A.; Fernández-Regúlez, M.; Evangelio, L.; Lorenzoni, M.; Gharbi, A.; Rademaker, G.; Pourteau, M.-L.; Tiron, R.; Bausells, J.; et al. Exploring Strategies to Contact 3D Nano-Pillars. Nanomaterials 2020, 10, 716. https://doi.org/10.3390/nano10040716

Amat E, del Moral A, Fernández-Regúlez M, Evangelio L, Lorenzoni M, Gharbi A, Rademaker G, Pourteau M-L, Tiron R, Bausells J, et al. Exploring Strategies to Contact 3D Nano-Pillars. Nanomaterials. 2020; 10(4):716. https://doi.org/10.3390/nano10040716

Chicago/Turabian StyleAmat, Esteve, Alberto del Moral, Marta Fernández-Regúlez, Laura Evangelio, Matteo Lorenzoni, Ahmed Gharbi, Guido Rademaker, Marie-Line Pourteau, Raluca Tiron, Joan Bausells, and et al. 2020. "Exploring Strategies to Contact 3D Nano-Pillars" Nanomaterials 10, no. 4: 716. https://doi.org/10.3390/nano10040716

APA StyleAmat, E., del Moral, A., Fernández-Regúlez, M., Evangelio, L., Lorenzoni, M., Gharbi, A., Rademaker, G., Pourteau, M.-L., Tiron, R., Bausells, J., & Perez-Murano, F. (2020). Exploring Strategies to Contact 3D Nano-Pillars. Nanomaterials, 10(4), 716. https://doi.org/10.3390/nano10040716