Improved Pulse-Controlled Conductance Adjustment in Trilayer Resistors by Suppressing Current Overshoot

Abstract

1. Introduction

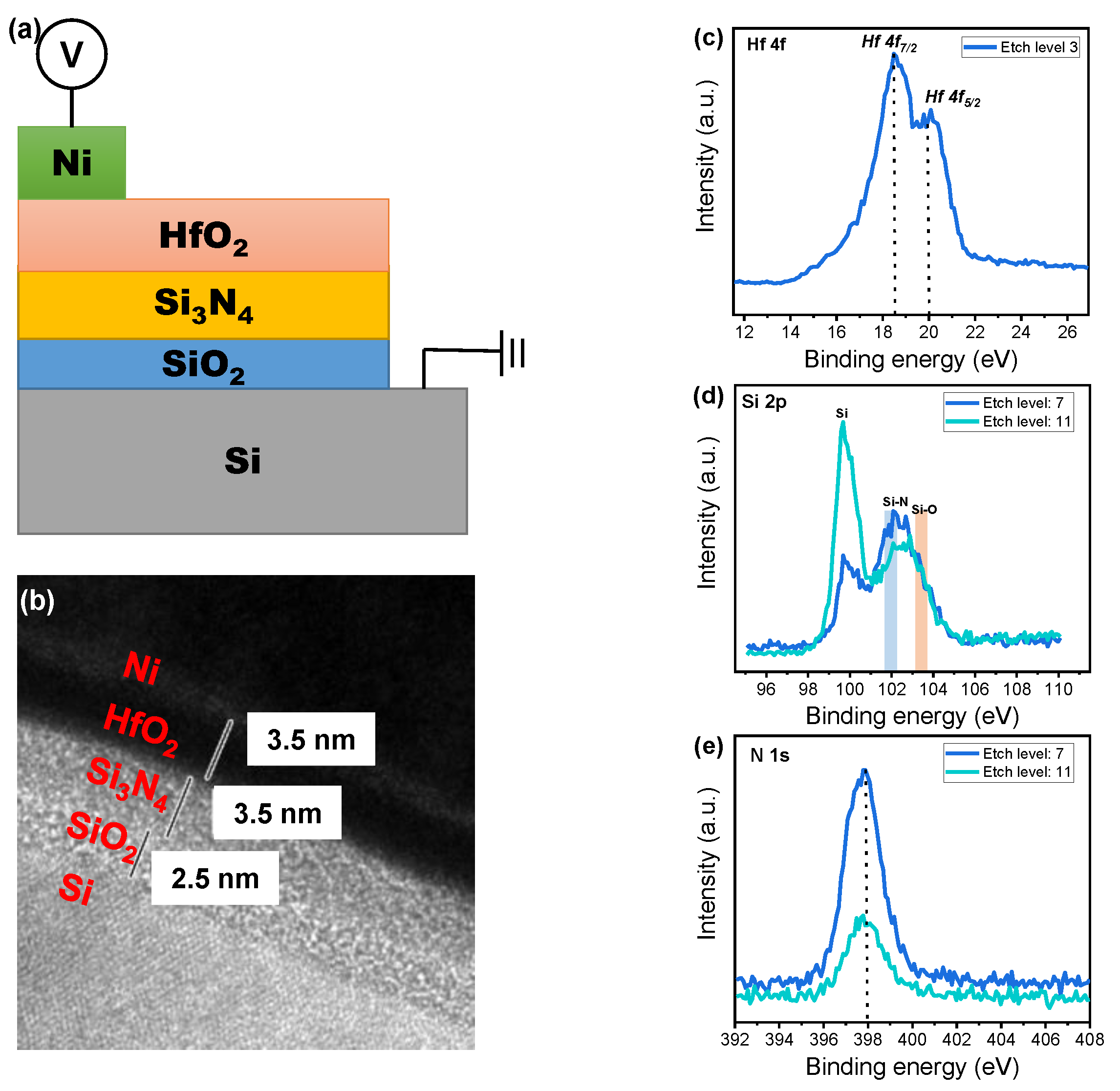

2. Materials and Methods

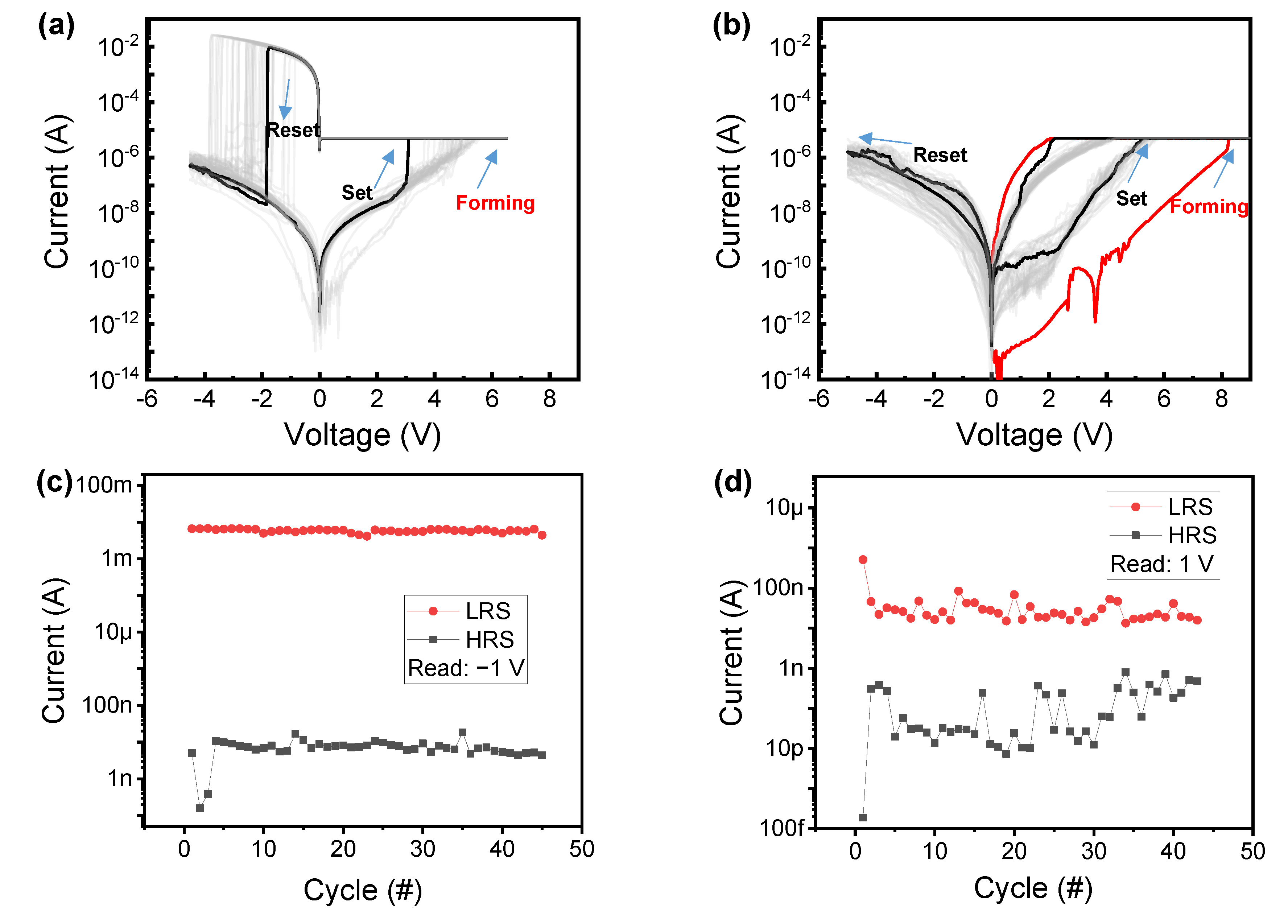

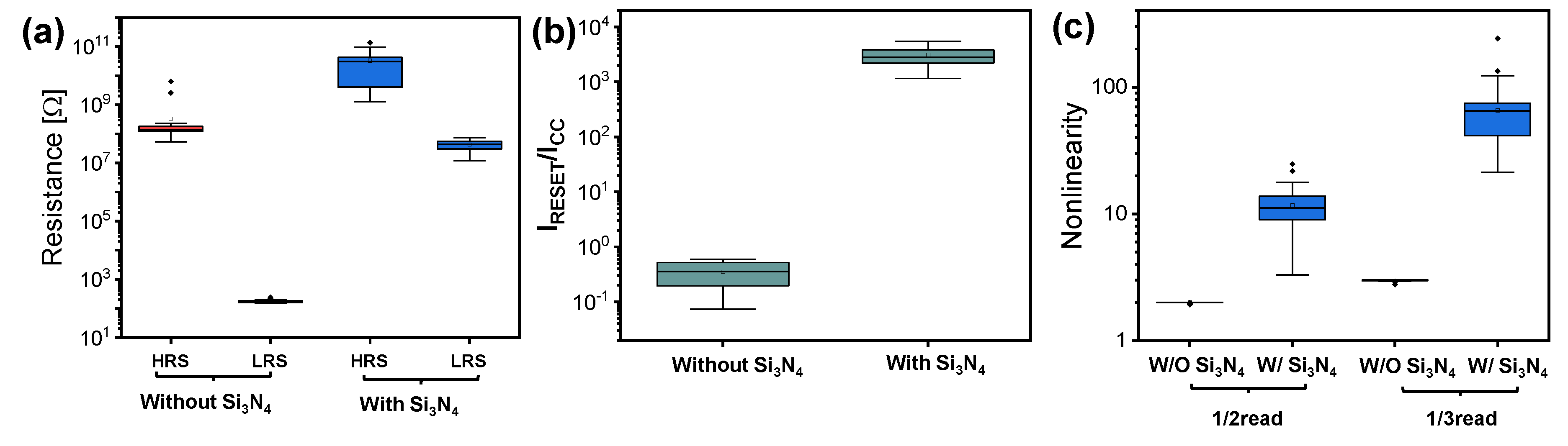

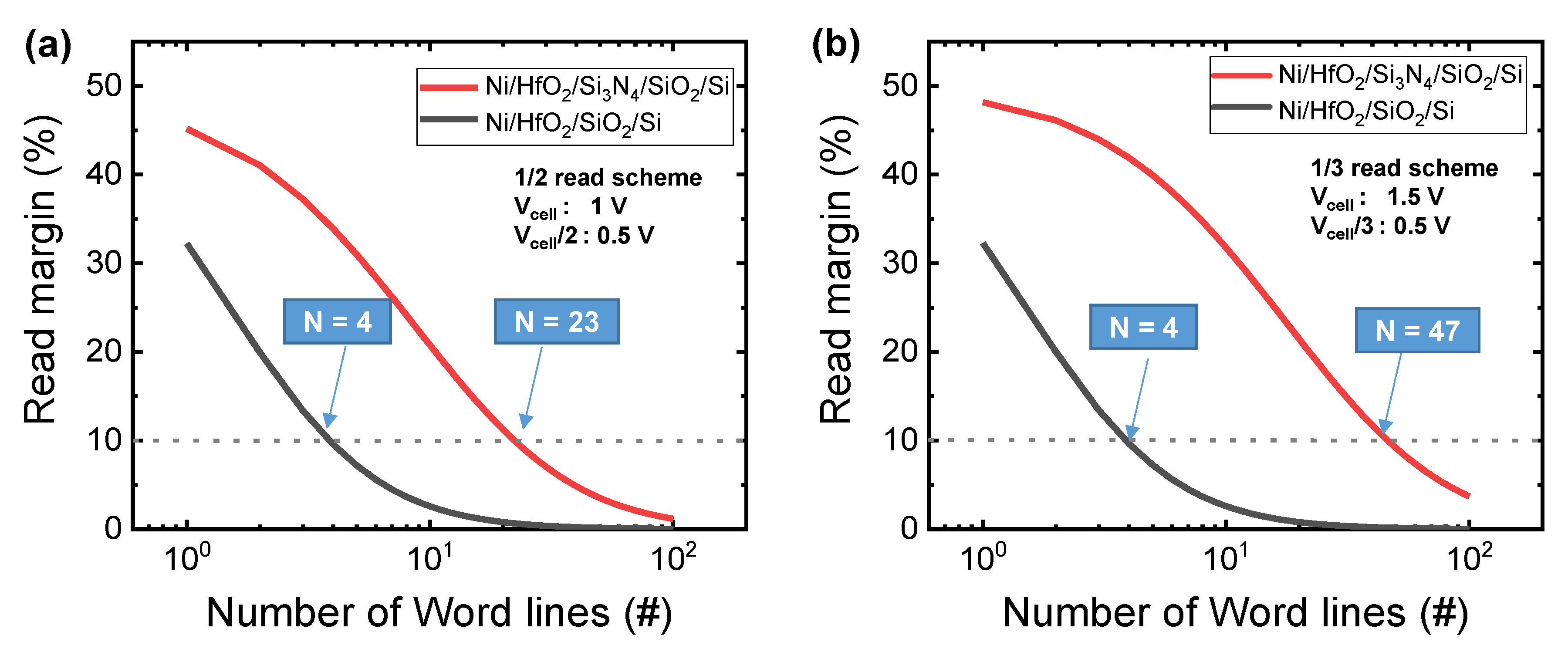

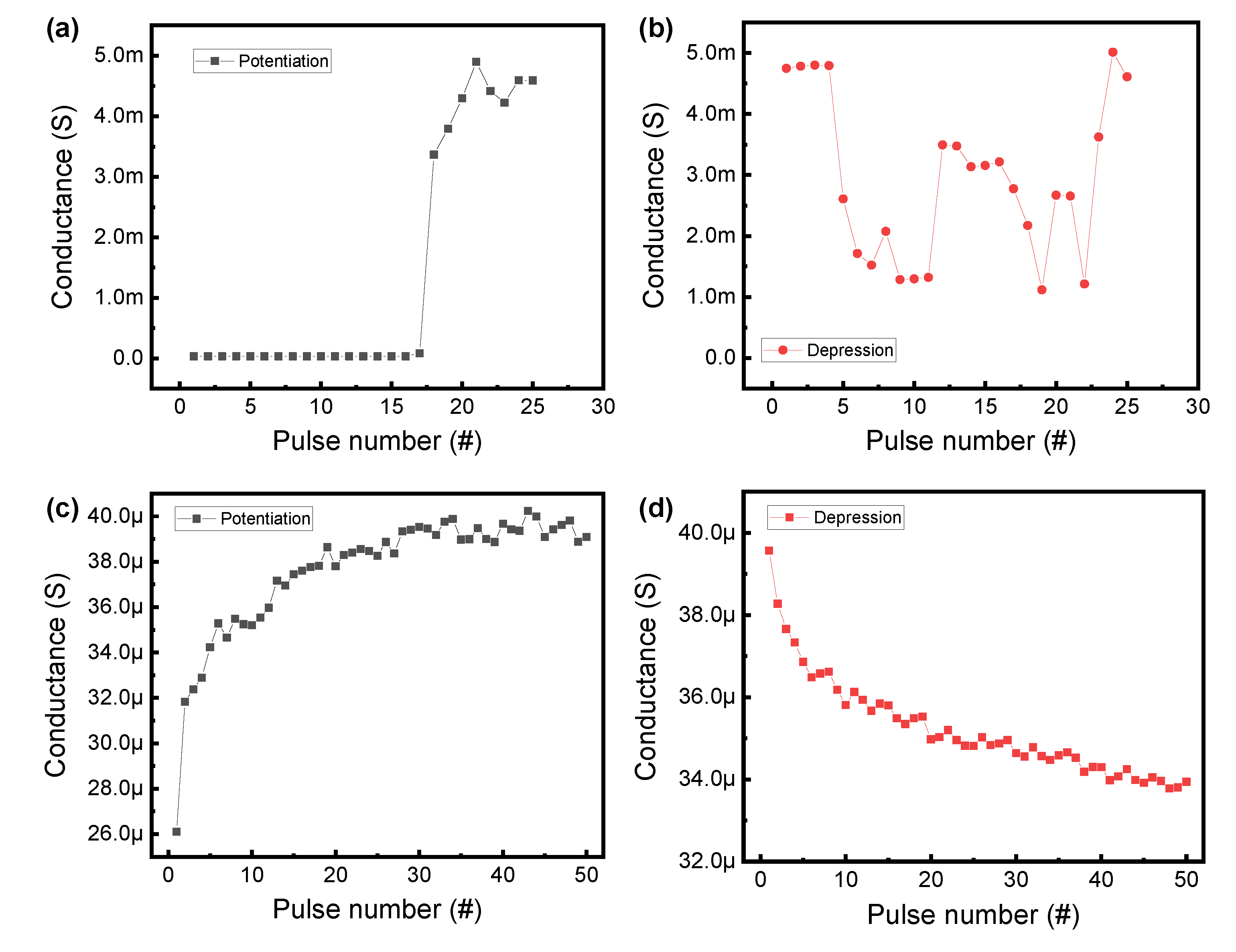

3. Results and Discussion

4. Conclusions

Supplementary Materials

Author Contributions

Funding

Conflicts of Interest

References

- Lanza, M.; Wong, H.-S.P.; Pop, E.; Ielmini, D.; Strukov, D.; Regan, B.C.; Larcher, L.; Villena, M.A.; Yang, J.J.; Goux, L.; et al. Recommended Methods to Study Resistive Switching Devices. Adv. Electron. Mater. 2018, 5, 1800143. [Google Scholar] [CrossRef]

- Linn, E.; Rosezin, R.; Kügeler, C.; Waser, R. Complementary resistive switches for passive nanocrossbar memories. Nat. Mater. 2010, 9, 403–406. [Google Scholar] [CrossRef]

- Kim, S.; Jung, S.; Kim, M.-H.; Chen, Y.-C.; Chang, T.-C.; Ryoo, K.-C.; Cho, S.; Lee, J.-H.; Park, B.-G. Scaling Effect on Silicon Nitride Memristor with Highly Doped Si Substrate. Small 2018, 14, 1704062. [Google Scholar] [CrossRef]

- Zhou, F.; Chang, Y.F.; Fowler, B.; Byun, K.; Lee, J.C. Stabilization of multiple resistance levels by current-sweep in SiOx-based resistive switching memory. Appl. Phys. Lett. 2015, 106, 063508. [Google Scholar] [CrossRef]

- Pan, F.; Gao, S.; Chen, C.; Song, C.; Zeng, F. Recent progress in resistive random access memories: Materials, switching mechanisms, and performance. Mater. Sci. Eng. R Rep. 2014, 83, 1–59. [Google Scholar] [CrossRef]

- Maikap, S.; Banergee, W. In Quest of Nonfilamentary Switching: A Synergistic Approach of Dual Nanostructure Engineering to Improve the Variability and Reliability of Resistive Random-Access-Memory Devices. Adv. Electron. Mater. 2020, 6, 2000209. [Google Scholar] [CrossRef]

- Mikhaylov, A.; Pimashkin, A.; Pigareva, Y.; Gerasimova, S.; Gryaznov, E.; Shchanikov, S.; Zuev, A.; Talanov, M.; Lavrov, I.; Demin, V.; et al. Neurohybrid Memristive CMOS-Integrated Systems for Biosensors and Neuroprosthetics. Front. Mol. Neurosci. 2020, 14, 358. [Google Scholar] [CrossRef] [PubMed]

- Kuzum, D.; Yu, S.; Wong, H.-S.P. Synaptic electronics: Materials, devices and applications. Nanotechnology 2013, 24, 382001. [Google Scholar] [CrossRef] [PubMed]

- Graves, C.E.; Li, C.; Sheng, X.; Miller, D.; Ignowski, J.; Kiyama, L.; Strachan, J.P. In-Memory Computing with Memristor Content Addressable Memories for Pattern Matching. Adv. Mater. 2020, 32, 2003437. [Google Scholar] [CrossRef] [PubMed]

- Xia, Q.; Yang, J.J. Memristive crossbar arrays for brain-inspired computing. Nat. Mater. 2019, 18, 309–323. [Google Scholar] [CrossRef]

- Ryu, H.; Kim, S. Pseudo-Interface Switching of a Two-Terminal TaOx/HfO2 Synaptic Device for Neuromorphic Applications. Nanomaterials 2020, 10, 1550. [Google Scholar] [CrossRef] [PubMed]

- Choi, J.; Kim, S. Nonlinear Characteristics of Complementary Resistive Switching in HfAlOx-Based Memristor for High-Density Cross-Point Array Structure. Coatings 2020, 10, 765. [Google Scholar] [CrossRef]

- Ryu, H.; Kim, S. Voltage Amplitude-Controlled Synaptic Plasticity from Complementary Resistive Switching in Alloying HfOx with AlOx-Based RRAM. Metals 2020, 11, 1410. [Google Scholar] [CrossRef]

- Cho, S.; Kim, S. Emulation of Biological Synapse Characteristics from Cu/AlN/TiN Conductive Bridge Random Access Memory. Nanomaterials 2020, 10, 1709. [Google Scholar] [CrossRef] [PubMed]

- Kim, S.; Kim, H.; Jung, S.; Kim, M.H.; Lee, S.; Cho, S.; Park, B.G. Tuning resistive switching parameters in Si3N4-based RRAM for three-dimensional vertical resistive memory applications. J. Alloy. Compd. 2016, 663, 419–423. [Google Scholar] [CrossRef]

- Emelyanov, A.V.; Nikiruy, K.E.; Serenko, A.V.; Sitnikov, A.V.; Presnyakov, M.Y.; Rybka, R.B.; Sboev, A.G.; Rylkov, V.V.; Kashkarov, P.K.; Kovalchuk, M.V.; et al. Self-adaptive STDP-based learning of a spiking neuron with nanocomposite memristive weights. Nanotechnology 2020, 31, 045201. [Google Scholar] [CrossRef]

- Li, D.; Wu, B.; Zhu, X.; Wang, J.; Ryu, B.; Lu, W.D.; Liang, X. MoS2 Memristors Exhibiting Variable Switching Characteristics toward Biorealistic Synaptic Emulation. ACS Nano 2018, 12, 9240–9252. [Google Scholar] [CrossRef]

- Chand, U.; Alawein, M.; Fariborzi, H. Enhancement of Endurance in HfO2-Based CBRAM Device by Introduction of a TaN diffusion Blocking Layer. ECS Trans. 2017, 77, 1971–1976. [Google Scholar] [CrossRef]

- Chand, U.; Huang, K.C.; Huang, C.Y.; Ho, C.H.; Lin, C.H.; Tseng, T.Y. Investigation of thermal stability and reliability of HfO2 based resistive random access memory devices with cross-bar structure. J. Appl. Phys. 2015, 117, 184105. [Google Scholar] [CrossRef]

- Mahata, C.; Lee, C.; An, Y.; Kim, M.H.; Bang, S.; Kim, C.S.; Ryu, J.H.; Kim, S.; Kim, H.; Park, B.G. Resistive switching and synaptic behaviors of an HfO2/Al2O3 stack on ITO for neuromorphic systems. J. Alloy. Compd. 2020, 826, 154434. [Google Scholar] [CrossRef]

- Mikhaylov, A.; Belov, A.; Korolev, D.; Antonov, I.; Kotomina, V.; Kotina, A.; Gryaznov, E.; Sharapov, A.; Koryazhkina, M.; Kryukov, R.; et al. Multilayer Metal-Oxide Memristive Device with Stabilized Resistive Switching. Adv. Mater. Technol. 2020, 5, 1900607. [Google Scholar] [CrossRef]

- Kim, S.; Park, B.G. Nonlinear and multilevel resistive switching memory in Ni/Si3N4/Al2O3/TiN structures. Appl. Phys. Lett. 2016, 108, 212103. [Google Scholar] [CrossRef]

- Kim, M.H.; Kim, S.; Bang, S.; Kim, T.H.; Lee, D.K.; Cho, S.; Park, B.G. Uniformity Improvement of SiNx-Based Resistive Switching Memory by Suppressed Internal Overshoot Current. IEEE Trans. Nanotechnol. 2018, 17, 824–828. [Google Scholar] [CrossRef]

- Jung, R. Fermi-Level Pinning at the Poly-Si/HfO2 Interface. J. Korean Phys. Soc. 2009, 55, 2501–2504. [Google Scholar] [CrossRef]

- Bommali, R.K.; Singh, S.P.; Prakash, G.V.; Ghosh, S.; Srivastava, P. Growth and tailoring of physical properties of Si quantum dots in a-SiNx:H matrix. Energy Procedia 2013, 41, 50–56. [Google Scholar] [CrossRef]

- Kim, T.; Koka, S.; Surthi, S.; Zhuang, K. Direct Impact of Chemical Bonding of Oxynitride on Boron Penetration and Electrical Oxide Hardening for Nanoscale Flash Memory. IEEE Electron. Dev. Lett. 2013, 34, 405–407. [Google Scholar] [CrossRef]

- Ielemini, D. Modeling the Universal Set/Reset Characteristics of Bipolar RRAM by Field- and Temperature-Driven Filament Growth. IEEE Trans. Electron Devices 2011, 58, 4309. [Google Scholar] [CrossRef]

- Aldana, S.; García-Fernández, P.; Rodríguez-Fernández, A.; Romero-Zaliz, R.; González, M.B.; Jiménez-Molinos, F.; Campabadal, F.; Gómez-Campos, F.; Roldán, J.B. A 3D kinetic Monte Carlo simulation study of resistive switching processes in Ni/HfO2/Si-n+-based RRAMs. J. Phys. D Appl. Phys. 2017, 50, 335103. [Google Scholar] [CrossRef]

- Vandelli, L.; Padovani, A.; Larcher, L.; Bersuker, G. Microscopic Modeling of Electrical Stress-Induced Breakdown in Poly-Crystalline Hafnium Oxide Dielectrics. IEEE Trans. Electron Devices 2013, 60, 1754. [Google Scholar] [CrossRef]

- Guy, J.; Molas, G.; Blaise, P.; Bernard, M.; Roule, A.; Carval, G.L.; Delaye, V.; Toffoli, A.; Ghibaudo, G.; Clermidy, F.; et al. Investigation of Forming, SET, and Data Retention of Conductive-Bridge Random-Access Memory for Stack Optimization. IEEE Trans. Electron Devices 2015, 62, 3482. [Google Scholar] [CrossRef]

- Roldán, J.B.; Alonso, F.J.; Aguilera, A.M.; Maldonado, D.; Lanza, M. Time series statistical analysis: A powerful tool to evaluate the variability of resistive switching memories. J. Appl. Phys. 2019, 125, 174504. [Google Scholar] [CrossRef]

- Miranda, E.; Mehonic, A.; Ng, W.H.; Kenyon, A.J. Simulation of Cycle-to-Cycle Instabilities in SiOx-Based ReRAM Devices Using a Self-Correlated Process With Long-Term Variation. IEEE Electron Device Lett. 2019, 40, 28. [Google Scholar] [CrossRef]

- Kim, C.-H.; Lim, S.; Woo, S.Y.; Kang, W.M.; Seo, Y.-T.; Lee, S.T.; Lee, S.; Kwon, D.; Oh, S.; Noh, Y. Emerging memory technologies for neuromorphic computing. Nanotechnology 2018, 30, 032001. [Google Scholar] [CrossRef] [PubMed]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ryu, H.; Kim, S. Improved Pulse-Controlled Conductance Adjustment in Trilayer Resistors by Suppressing Current Overshoot. Nanomaterials 2020, 10, 2462. https://doi.org/10.3390/nano10122462

Ryu H, Kim S. Improved Pulse-Controlled Conductance Adjustment in Trilayer Resistors by Suppressing Current Overshoot. Nanomaterials. 2020; 10(12):2462. https://doi.org/10.3390/nano10122462

Chicago/Turabian StyleRyu, Hojeong, and Sungjun Kim. 2020. "Improved Pulse-Controlled Conductance Adjustment in Trilayer Resistors by Suppressing Current Overshoot" Nanomaterials 10, no. 12: 2462. https://doi.org/10.3390/nano10122462

APA StyleRyu, H., & Kim, S. (2020). Improved Pulse-Controlled Conductance Adjustment in Trilayer Resistors by Suppressing Current Overshoot. Nanomaterials, 10(12), 2462. https://doi.org/10.3390/nano10122462