## Supplementary Materials

## Improved Pulse-Controlled Conductance Adjustment in Trilayer Resistors by Suppressing Current Overshoot

## Hojeong Ryu and Sungjun Kim\*

Division of Electronics and Electrical Engineering, Dongguk University, Seoul 04620, Korea; hojeong.ryu95@gmail.com

\* Correspondence: sungjun@dongguk.edu

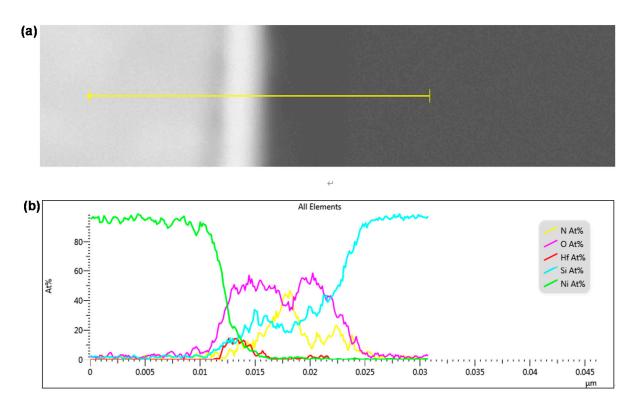

Figure S1. (a) STEM image and (b) EDS line scan of Ni/HfO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub>/Si device.

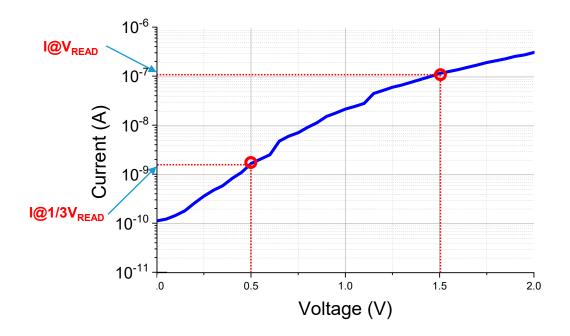

Figure S2. Definition of nonlinearity of I–V in the LRS.

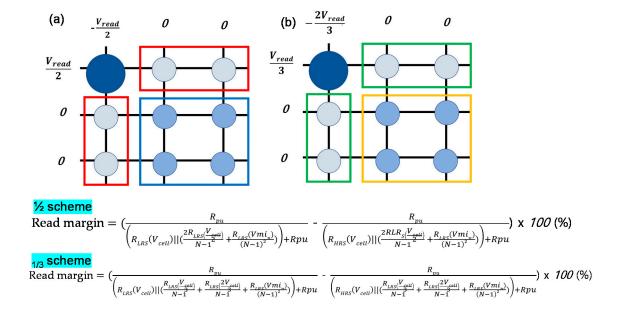

Figure S3. Read scheme: (a) half bias scheme and (b) 1/3 bias scheme and their equation for read margin.