Improving Device Characteristics of Dual-Gate IGZO Thin-Film Transistors with Ar–O2 Mixed Plasma Treatment and Rapid Thermal Annealing

Abstract

:1. Introduction

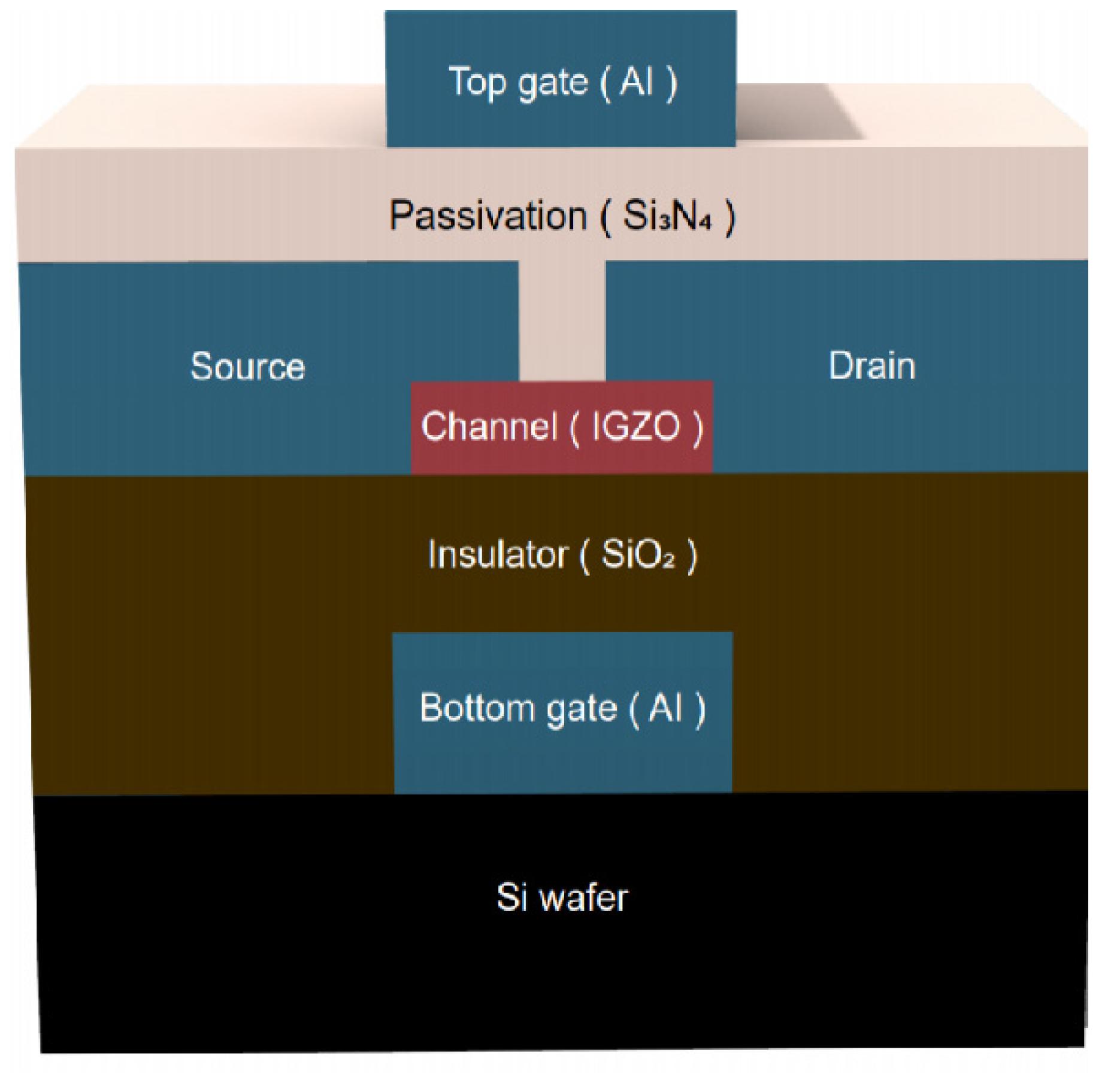

2. Materials and Methods

3. Results and Discussion

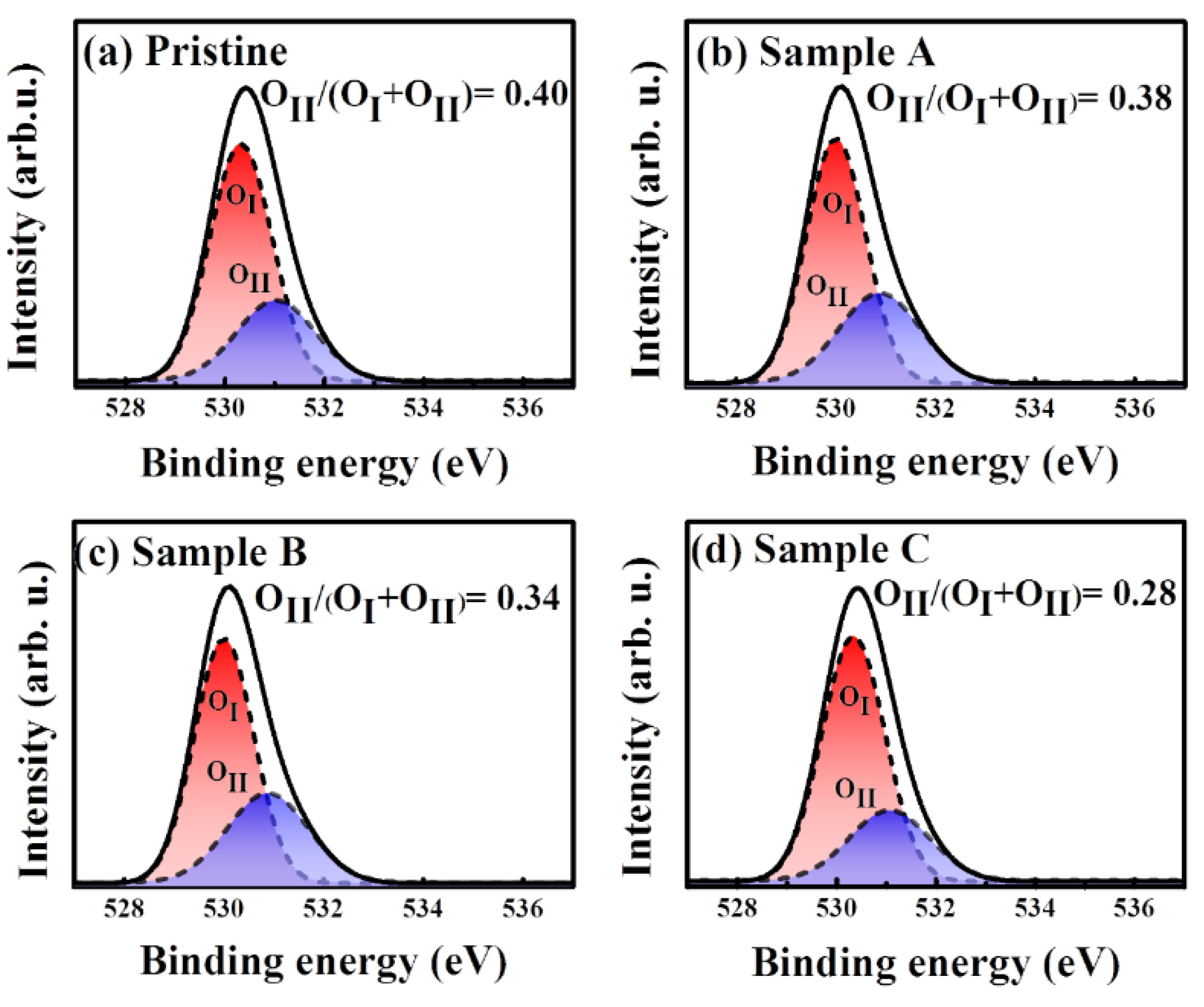

3.1. XPS

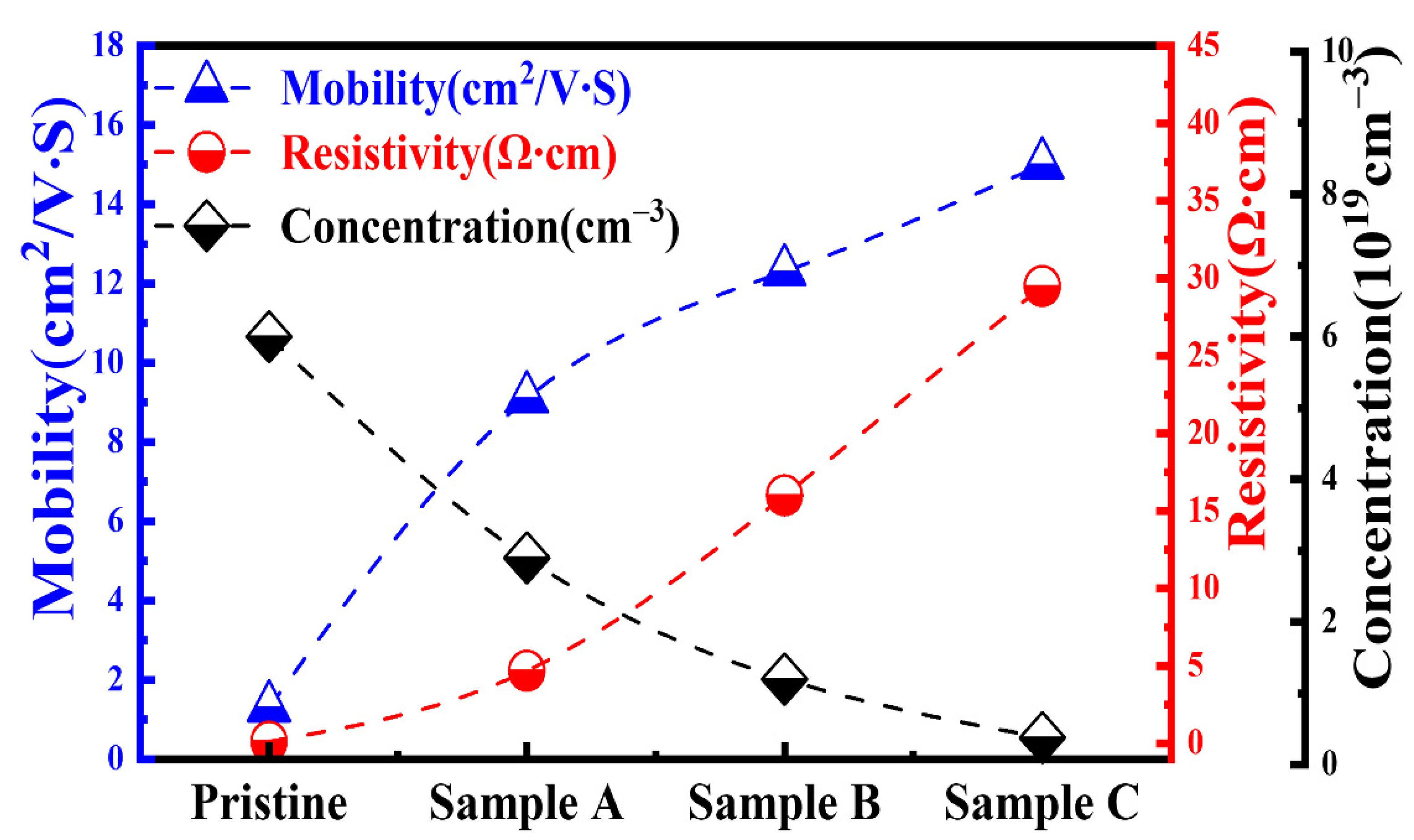

3.2. Hall-Effect Measurements

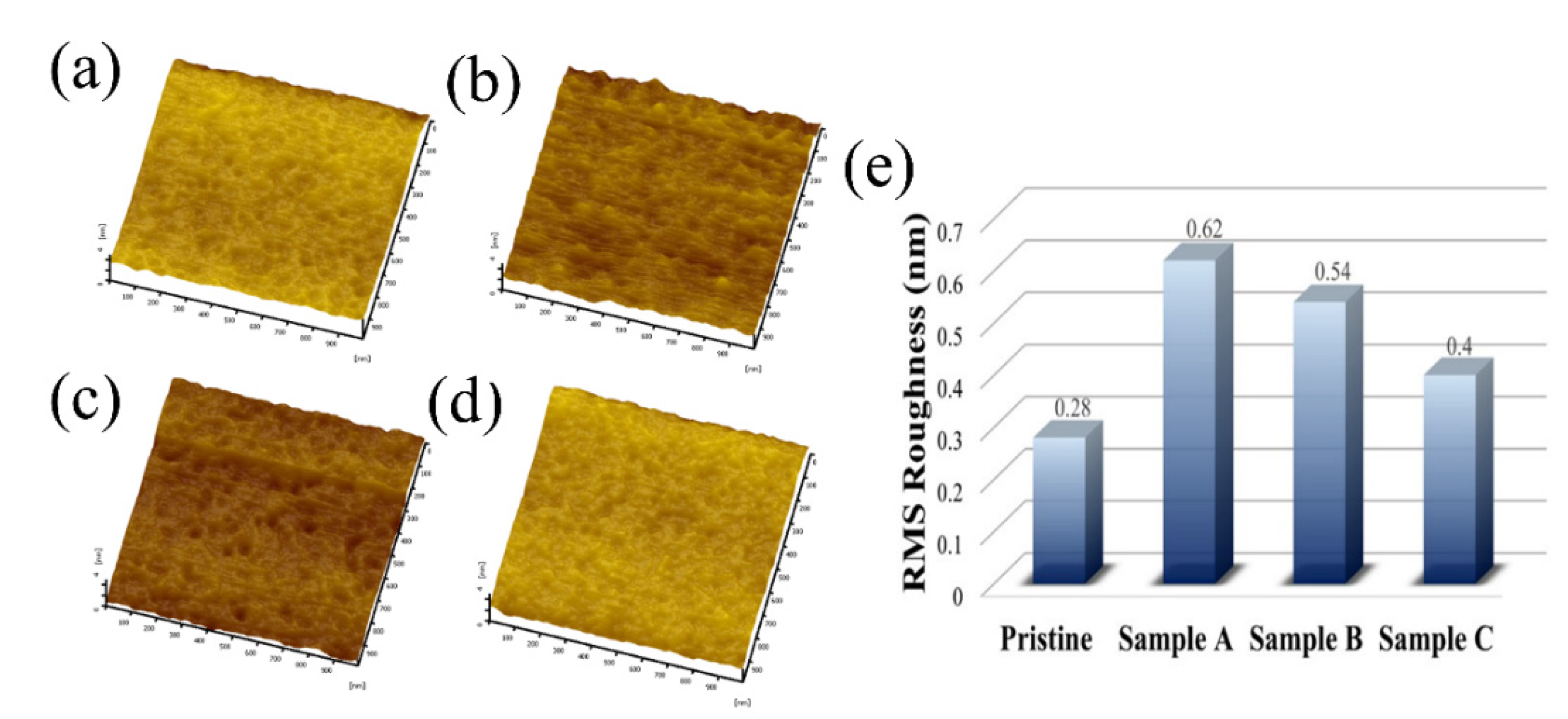

3.3. AFM

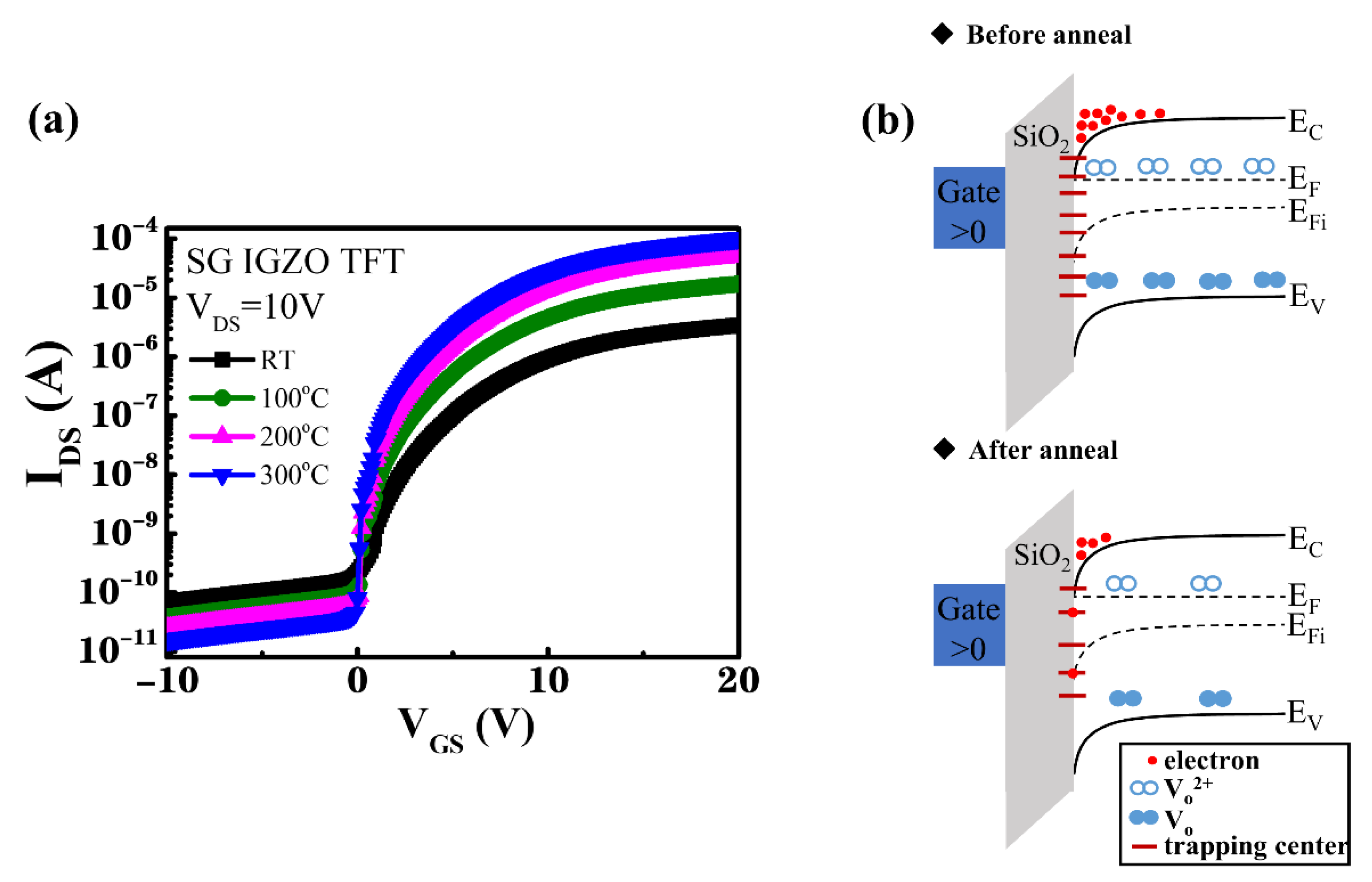

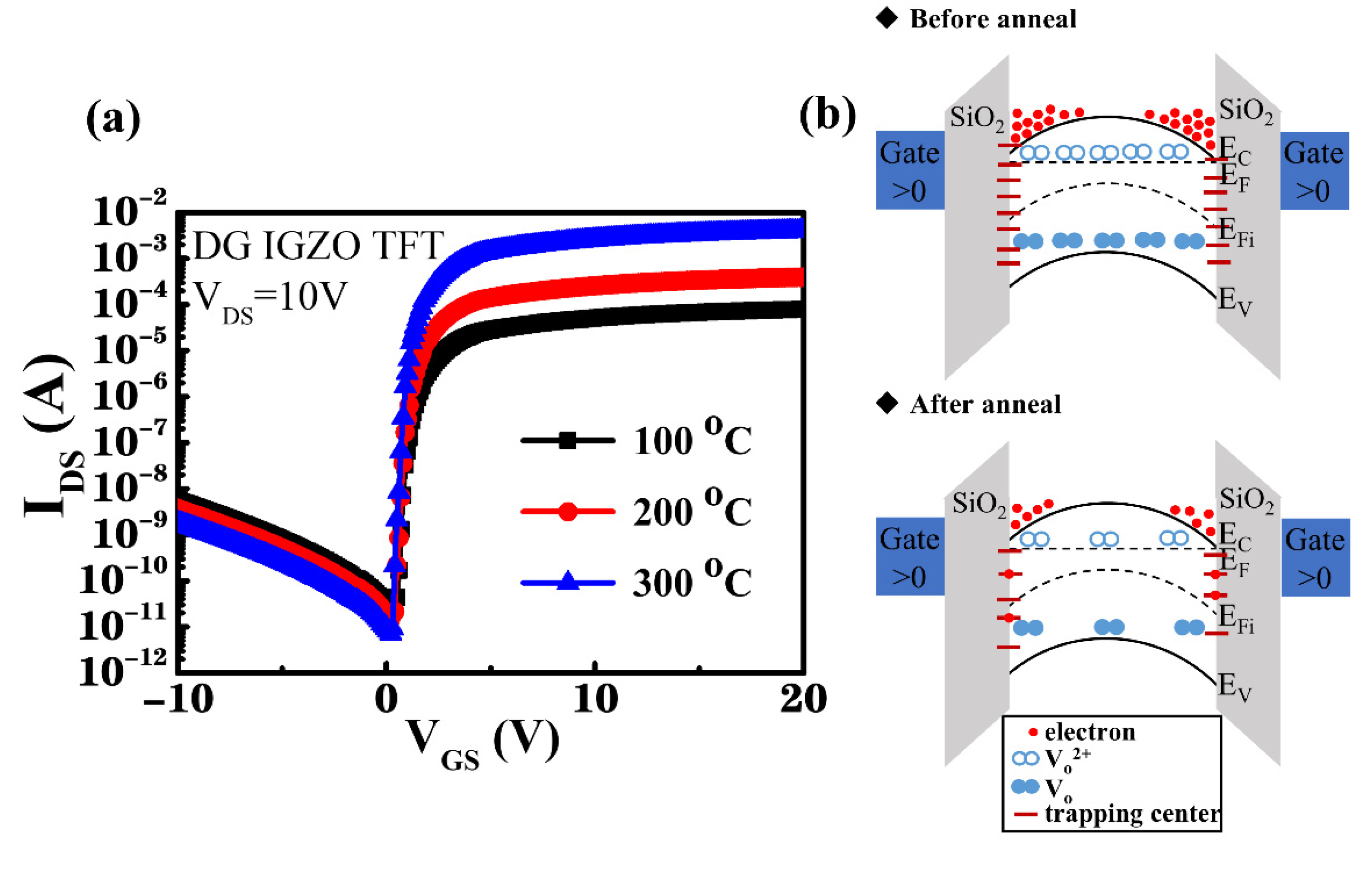

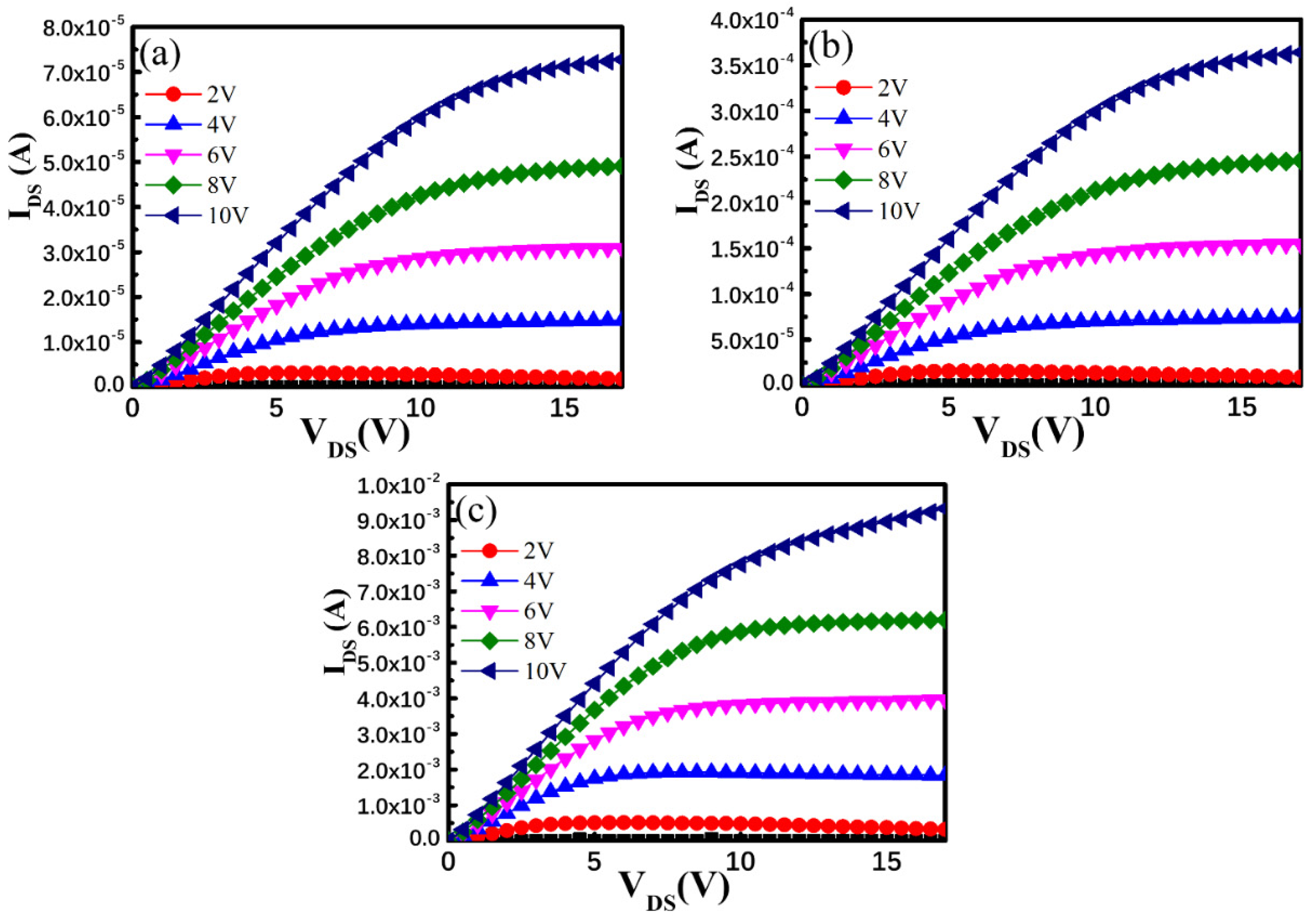

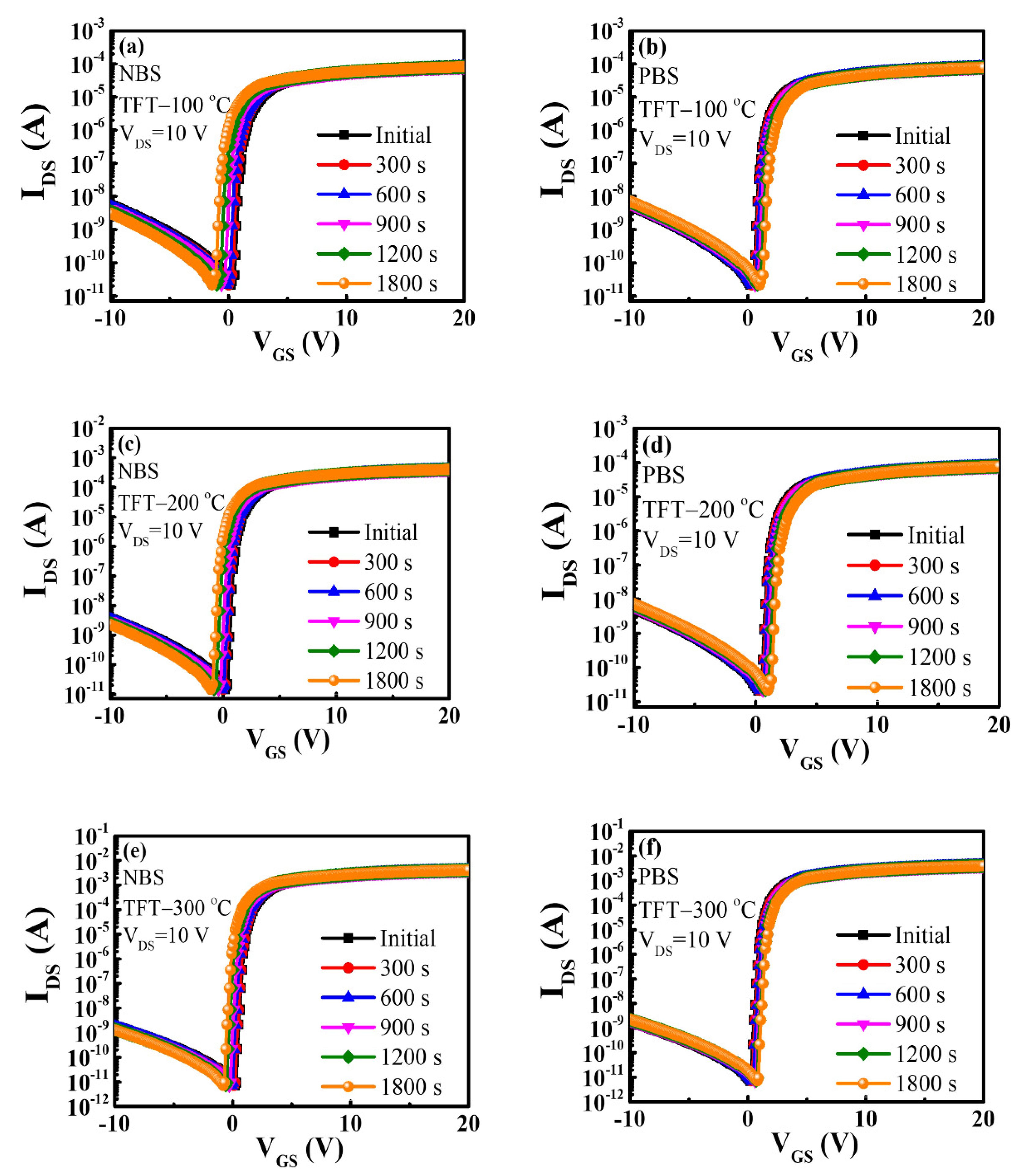

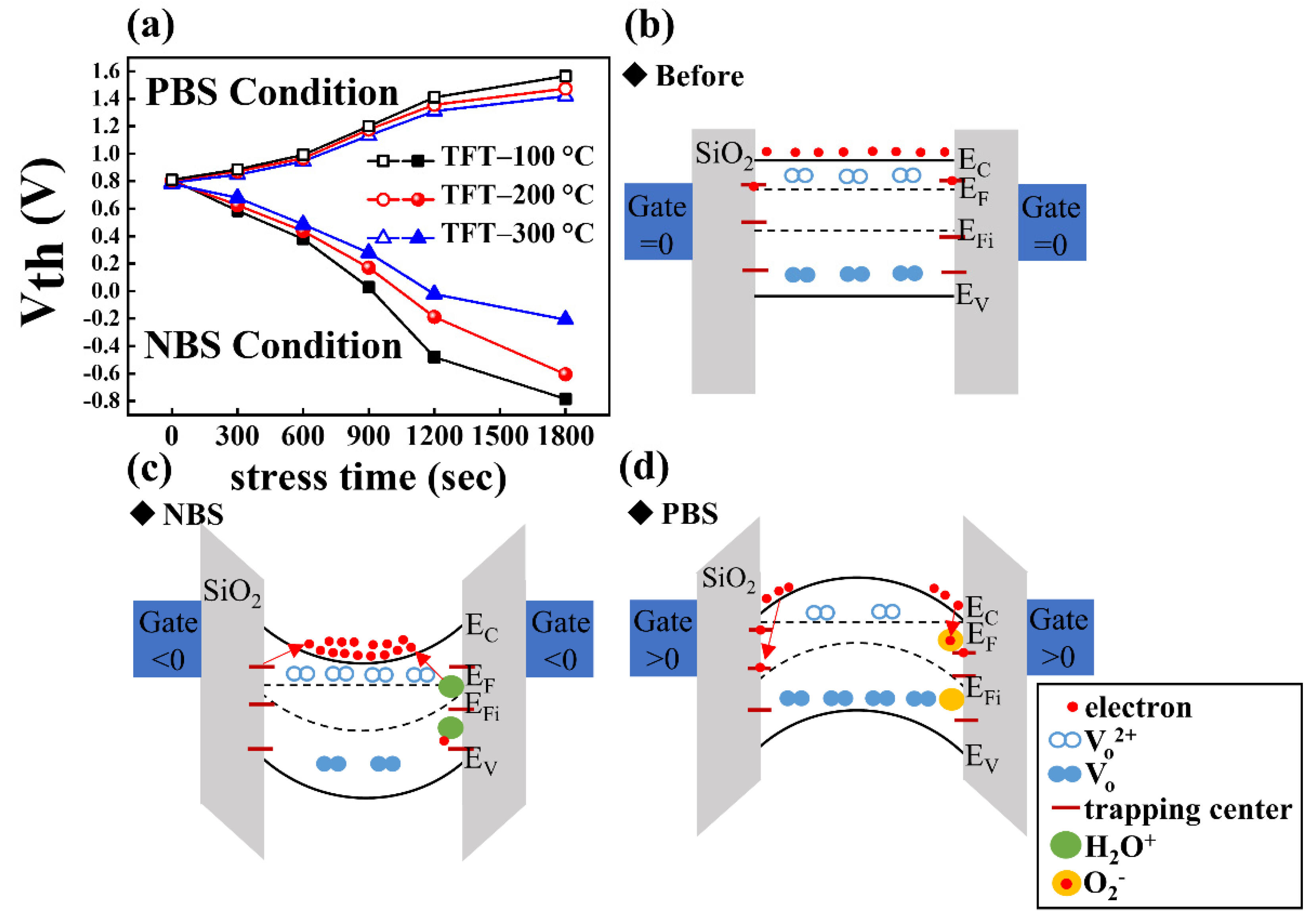

3.4. Device Characteristics

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Baek, G.; Bie, L.; Abe, K.; Kumomi, H.; Kanicki, J. Electrical instability of double-gate a-IGZO TFTs with metal source/drain recessed electrodes. IEEE Trans. Electron Devices 2014, 61, 1109–1115. [Google Scholar] [CrossRef]

- Cao, Q.; Kim, H.S.; Pimparkar, N.; Kulkarni, J.P.; Wang, C.; Shim, M.; Roy, K.; Alam, M.A.; Rogers, J.A. Rogers, Medium-scale carbon nanotube thin-film integrated circuits on flexible plastic substrates. Nature 2008, 454, 495–500. [Google Scholar] [CrossRef]

- Lin, C.L.; Chang, W.Y.; Hung, C.C. Compensating pixel circuit driving AMOLED display with a-IGZO TFTs. IEEE Electron Device Lett. 2013, 34, 1166–1168. [Google Scholar] [CrossRef]

- Seok, M.J.; Choi, M.H.; Mativenga, M.; Geng, D.; Kim, D.Y.; Jang, J. A full-swing a-IGZO TFT-based inverter with a top-gate-bias-induced depletion load. IEEE Electron Device Lett. 2011, 32, 1089–1091. [Google Scholar] [CrossRef]

- Kang, D.H.; Kang, I.; Ryu, S.H.; Jang, J. Self-aligned coplanar a-IGZO TFTs and application to high-speed circuits. IEEE Electron Device Lett. 2011, 32, 1385–1387. [Google Scholar] [CrossRef]

- Arias, A.C.; MacKenzie, J.D.; McCulloch, I.; Rivnay, J.; Salleo, A. Materials and applications for large area electronics: Solution-based approaches. Chem. Rev. 2010, 110, 3–24. [Google Scholar] [CrossRef] [PubMed]

- Kim, D.; Kim, D.; Kim, H.; So, H.; Hong, M. Effect of ammonia (NH3) plasma treatment on silicon nitride (SiNx) gate dielectric for organic thin film transistor with soluble organic semiconductor. Curr. Appl. Phys. 2011, 11, S67–S72. [Google Scholar] [CrossRef]

- Kamiya, T.; Nomura, K.; Hosono, H. Present status of amorphous In–Ga–Zn–O thin-film transistors. Sci. Technol. Adv. Mater. 2010, 11, 044305. [Google Scholar] [CrossRef] [PubMed]

- Liu, W.-S.; Lin, Y.-H.; Huang, C.-L.; Wang, C.-W. Device Performance Improvement of Transparent Thin-Film Transistors with a Ti-Doped GaZnO/InGaZnO/Ti-Doped GaZnO Sandwich Composite-Channel Structure. IEEE Trans Electron Devices 2017, 64, 2533–2541. [Google Scholar] [CrossRef]

- Fortunato, E.; Barquinha, P.; Martins, R. Oxide Semiconductor Thin-Film Transistors: A Review of Recent Advances. Adv. Mater. 2012, 24, 2945–2986. [Google Scholar] [CrossRef]

- Liu, W.-S.; Chen, Y.-F.; Wang, Y.-M. Capping Ti-Doped GaZnO on InGaZnO Layer as the Composite-Channel Structure for Enhancing the Device Performances and Stability of Thin-Film Transistors. IEEE/OSA J. Disp. Technol. 2016, 12, 1554–1559. [Google Scholar] [CrossRef]

- Mo, Y.G.; Kim, M.; Kang, C.K.; Jeong, J.H.; Park, Y.S.; Choi, C.G.; Kim, H.D.; Kim, S.S. Amorphous-oxide TFT backplane for large-sized AMOLED TVs. J. Inf. Disp. 2011, 19, 16–20. [Google Scholar] [CrossRef]

- Hosono, H.; Kim, J.; Toda, Y.; Kamiya, T.; Watanabe, S. Transparent amorphous oxide semiconductors for organic electronics: Application to inverted OLEDs. Proc. Natl. Acad. Sci. USA 2017, 114, 233–238. [Google Scholar] [CrossRef] [Green Version]

- Noh, J.Y.; Han, D.M.; Jeong, W.C.; Kim, J.W.; Cha, S.Y. Development of 55” 4K UHD OLED TV employing the internal gate IC with high reliability and short channel IGZO TFTs. J. Soc. Inf. Disp. 2018, 26, 36–41. [Google Scholar] [CrossRef]

- Shim, G.W.; Hong, W.; Cha, J.; Park, J.H.; Lee, K.J.; Choi, S. TFT Channel Materials for Display Applications: From Amorphous Silicon to Transition Metal Dichalcogenides. Adv. Mater. 2020, 32, 1907166. [Google Scholar] [CrossRef]

- Shen, Y.; Feng, Z.; Zhang, H. Study of indium tin oxide films deposited on colorless polyimide film by magnetron sputtering. Mater. Des. 2020, 193, 108809. [Google Scholar] [CrossRef]

- Wang, X.-L.; Shao, Y.; Wu, X.; Zhang, M.-N.; Li, L.; Liu, W.-J.; Zhang, D.W.; Ding, S.-J. Ding, Light response behaviors of amorphous In-Ga-Zn-O thin-film transistors: Via in situ interfacial hydrogen doping modulation. RSC Adv. 2020, 10, 3572–3578. [Google Scholar] [CrossRef] [Green Version]

- Sakai, M.; Honda, T.; Kudo, K.; Okada, Y.; Sadamitsu, Y.; Hashimoto, Y.; Onodera, N. Onodera, Initial carrier-injection dynamics in organic thin-film transistor observed with time domain reflectometry in thickness direction. Appl. Phys. Express 2019, 12, 051004. [Google Scholar] [CrossRef]

- Kamiya, T.; Nomura, K.; Hosono, H. Effects of Intense Pulsed Light (IPL) Rapid Annealing and Back-Channel Passivation on Solution-Processed In-Ga-Zn-O Thin Film Transistors Array. Micromachines 2020, 11, 508. [Google Scholar] [CrossRef]

- Choi, S.; Kim, S.; Jang, J.; Ahn, G.; Jang, J.T.; Yoon, J.; Park, T.J.; Park, B.G.; Kim, D.M.; Choi, S.J.; et al. Implementing an artificial synapse and neuron using a Si nanowire ion-sensitive field-effect transistor and indium-gallium-zinc-oxide memristors. IEEE Trans. Nanotechnol. 2019, 296, 126616. [Google Scholar] [CrossRef]

- Yang, C.-M.; Yang, Y.-C.; Chen, C.-H. Thin-film light-addressable potentiometric sensor with SnOx as a photosensitive semiconductor. Vacuum 2019, 168, 108809. [Google Scholar] [CrossRef]

- Kim, J.; Kim, M.; Kang, Y.; Kim, K.-T.; Heo, J.-S.; Park, S.K.; Kim, Y.-H. Photoactivated high-k lanthanum oxide-aluminum oxide (La2O3–Al2O3) alloy-type gate dielectrics for low-voltage-operating flexible transistors. J. Alloys Compd. 2020, 842, 155671. [Google Scholar] [CrossRef]

- Zhan, S.; Han, S.; Bang, S.Y.; Li, B.; Chun, Y.T.; Hou, B.; Kim, J.M. Organic materials as a passivation layer for metal oxide semiconductors. J. Mater. Chem. C 2020, 217, 1900832. [Google Scholar] [CrossRef]

- Troughton, J.; Atkinson, D. Amorphous InGaZnO and metal oxide semiconductor devices: An overview and current status. J. Mater. Chem. C 2019, 7, 12388–12414. [Google Scholar] [CrossRef]

- Nakano, S.; Saito, N.; Miura, K.; Sakano, T.; Ueda, T.; Sugi, K.; Yamaguchi, H.; Amemiya, I.; Hiramatsu, M.; Ishida, A. Highly reliable a-IGZO TFTs on a plastic substrate for flexible AMOLED displays. J. Soc. Inf. Disp. 2012, 20, 493–498. [Google Scholar] [CrossRef]

- Park, J.-S.; Kim, T.-W.; Stryakhilev, D.; Lee, J.-S.; An, S.-G.; Pyo, Y.-S.; Lee, D.-B.; Mo, Y.G.; Jin, D.-U.; Chung, H.K. Flexible full color organic light-emitting diode display on polyimide plastic substrate driven by amorphous indium gallium zinc oxide thin-film transistors. Appl. Phys. Lett. 2019, 95, 013503. [Google Scholar] [CrossRef]

- Münzenrieder, N.; Voser, P.; Petti, L.; Zysset, C.; Buthe, L.; Vogt, C.; Salvatore, G.A.; Troster, G. Flexible self-aligned double-gate IGZO TFT. IEEE Electron Device Lett. 2014, 35, 69–71. [Google Scholar] [CrossRef]

- JSmith, J.T.; Shah, S.S.; Goryll, M.; Stowell, J.R.; Allee, D.R. Allee, Flexible ISFET biosensor using IGZO metal oxide TFTs and an ITO sensing layer. IEEE Sens. J. 2014, 14, 937–938. [Google Scholar] [CrossRef]

- Jeong, J.K. The status and perspectives of metal oxide thin-film transistors for active matrix flexible displays. Semicond. Sci. Technol. 2011, 26, 034008. [Google Scholar] [CrossRef]

- Abliz, A.; Gao, Q.; Wan, D.; Liu, X.; Xu, L.; Liu, C.; Jiang, C.; Li, X.; Chen, H.; Guo, T.; et al. Effects of Nitrogen and Hydrogen Codoping on the Electrical Performance and Reliability of InGaZnO Thin-Film Transistors. ACS Appl. Mater. Interfaces 2017, 9, 10798. [Google Scholar] [CrossRef]

- Abliz, A. Effects of hydrogen plasma treatment on the electrical performances and reliability of InGaZnO thin-film transistors. J. Alloys Compd. 2020, 831, 154694. [Google Scholar] [CrossRef]

- Pu, H.; Zhou, Q.; Yue, L.; Zhang, Q. Investigation of oxygen plasma treatment on the device performance of solution-processed a-IGZO thin film transistors. Appl. Surf. Sci. 2013, 283, 722–726. [Google Scholar] [CrossRef]

- Liu, W.-S.; Hsu, C.-H.; Jiang, Y.; Lai, Y.-C.; Kuo, H.-C. Improvement of device characteristics of plasma-treated indium gallium zinc oxide thin-film transistors through thermal annealing. Semicond. Sci. Technol. 2021, 36, 045007. [Google Scholar] [CrossRef]

- Chun, M.; Um, J.G.; Park, M.S.; Chowdhury, D.H.; Jang, J. Effect of top gate potential on bias-stress for dual gate amorphous indium-gallium-zinc-oxide thin film transistor. AIP Adv. 2016, 6, 075217. [Google Scholar] [CrossRef] [Green Version]

- Mativenga, M.; An, S.; Jang, J. Bulk accumulation a-IGZO TFT for high current and turn-on voltage uniformity. IEEE Electron Device Lett. 2013, 34, 1533–1535. [Google Scholar] [CrossRef]

- Nayak, P.K.; Hedhili, M.N.; Cha, D.K.; Alshareef, H.N. High performance solution-deposited amorphous indium gallium zinc oxide thin film transistors by oxygen plasma treatment. Appl. Phys. Lett. 2012, 100, 202106. [Google Scholar] [CrossRef] [Green Version]

- Ahn, J.-S.; Lee, K.-B. Control of the threshold voltage by using the oxygen partial pressure in sputter-deposited InGaZnO4 thin-film transistors. J. Korean Phys. Soc. 2012, 60, 1625–1628. [Google Scholar] [CrossRef]

- Park, J.-S.; Jeong, J.K.; Mo, Y.-G.; Kim, H.D.; Kim, S.-I. Improvements in the device characteristics of amorphous indium gallium zinc oxide thin-film transistors by Ar plasma treatment. Appl. Phys. Lett. 2007, 90, 262106. [Google Scholar] [CrossRef]

- Ide, K.; Kikuchi, Y.; Nomura, K.; Kimura, M.; Kamiya, T.; Hosono, H. Effects of excess oxygen on operation characteristics of amorphous In-Ga-Zn-O thin-film transistors. Appl. Phys. Lett. 2011, 99, 093507. [Google Scholar] [CrossRef]

- Nomura, K.; Kamiya, T.; Ohta, H.; Hirano, M.; Hosono, H. Defect passivation and homogenization of amorphous oxide thin-film transistor by wet O2 annealing. Appl. Phys. Lett. 2008, 93, 192107. [Google Scholar] [CrossRef]

- Nomura, K.; Kamiya, T.; Hosono, H. Variation of Oxygen Deficiency in Solution-Processed Ultra-Thin Zinc-Tin Oxide Films to Their Transistor Characteristics. ECS J. Solid State Sci. Technol. 2013, 2, Q59–Q64. [Google Scholar] [CrossRef]

- Kang, D.H. Amorphous gallium indium zinc oxide thin film transistors: Sensitive to oxygen molecules. Appl. Phys. Lett. 2007, 90, 192101. [Google Scholar] [CrossRef]

- Tadatsugu, M. Transparent conducting oxide semiconductors for transparent electrodes. Semicond. Sci. Technol. 2005, 20, S35–S44. [Google Scholar] [CrossRef]

- Yao, J.K. Electrical and Photosensitive Characteristics of a-IGZO TFTs Related to Oxygen Vacancy. IEEE Trans. Electron Devices 2011, 58, 1121–1126. [Google Scholar] [CrossRef]

- Chen, W.T. Oxygen-Dependent Instability and Annealing/Passivation Effects in Amorphous In–Ga–Zn–O Thin-Film Transistors. IEEE Electron Device Lett. 2011, 32, 1552–1554. [Google Scholar] [CrossRef]

- Kim, J.S. Effect of acid scavengers on electrochemical performance of lithium–sulfur batteries: Functional additives for utilization of LiPF6. Jpn. J. Appl. Phys. 2014, 53, 08NK01. [Google Scholar] [CrossRef]

- Jeong, J.; Kim, J. Electrical characterization of graphene source/drain electrodes in amorphous indium-gallium-zinc-oxide thin-film transistors employing plasma treatment in contact regions. Jpn. J. Appl. Phys. 2019, 58, 071003. [Google Scholar] [CrossRef]

- Jeong, J.K.; Jeong, J.H.; Yang, H.W.; Park, J.-S.; Mo, Y.-G.; Kim, H.D. High performance thin film transistors with cosputtered amorphous indium gallium zinc oxide channel. Appl. Phys. Lett. 2007, 91, 113505. [Google Scholar] [CrossRef]

- Noh, H.-K.; Chang, K.J.; Ryu, B.; Lee, W.-J. Electronic structure of oxygen-vacancy defects in amorphous In-Ga-Zn-O semiconductors. Phys. Rev. B Condens. Matter Mater. Phys. 2011, 84, 115205. [Google Scholar] [CrossRef]

- Uraoka, Y.; Bermundo, J.P.; Fujii, M.N.; Uenuma, M.; Ishikawa, Y. Degradation phenomenon in metal-oxide-semiconductor thin-film transistors and techniques for its reliability evaluation and suppression. Jpn. J. Appl. Phys. 2019, 58, 090502. [Google Scholar] [CrossRef]

- Lee, S.; Paine, D.C. Identification of the native defect doping mechanism in amorphous indium zinc oxide thin films studied using ultra high pressure oxidation. Appl. Phys. Lett. 2013, 102, 052101. [Google Scholar] [CrossRef]

- Gan, J.; Lu, X.; Wu, J.; Xie, S.; Zhai, T.; Yu, M.; Zhang, Z.; Mao, Y.; Wang, S.C.I.; Shen, Y.; et al. Oxygen vacancies promoting photoelectrochemical performance of In2O3 nanocubes. Sci. Rep. 2013, 3, 1021. [Google Scholar] [CrossRef] [Green Version]

- YKesorn, P.; Bermundo, J.P.; Nonaka, T.; Fujii, M.N.; Ishikawa, Y.; Uraoka, Y. High Performance Amorphous In–Ga–Zn–O Thin-Film Transistors with Low Temperature High-k Solution Processed Hybrid Gate Insulator. ECS J. Solid State Sci. Technol. 2020, 9, 025002. [Google Scholar] [CrossRef]

- Nguyen, T.T.T.; Renault, O.; Aventurier, B.; Rodriguez, G.; Barnes, J.-P.; Templier, F. Analysis of IGZO Thin-Film Transistors by XPS and Relation with Electrical Characteristics. J. Disp. Technol. 2013, 9, 770–774. [Google Scholar] [CrossRef]

- Chen, C.; Liu, C.; Zheng, J.; Li, G.; Li, S.; Wu, Q.; Wu, J.; Liu, C. Orders-of-magnitude enhancement in conductivity tuning in InGaZnO thin-film transistors via SiNx passivation and dual-gate modulation. J. Inf. Disp. 2019, 20, 161–167. [Google Scholar] [CrossRef] [Green Version]

- Liu, W.-S.; Huang, C.-L.; Lin, Y.-H.; Hsu, C.-H.; Chu, Y.-M. Improving device characteristics of IGZO thin-film transistors by using pulsed DC magnetron sputtering deposition. Semicond. Sci. Technol. 2020, 35, 025004. [Google Scholar] [CrossRef]

- Abliz, A.; Wan, D.; Chen, J.-Y.; Xu, L.; He, J.; Yang, Y.; Duan, H.; Liu, C.; Jiang, C.; Chen, H.; et al. Enhanced Reliability of In–Ga–ZnO Thin-Film Transistors Through Design of Dual Passivation Layers. IEEE Trans. Electron Devices 2018, 65, 2844. [Google Scholar] [CrossRef]

- Hu, S.; Lu, K.; Ning, H.; Zheng, Z.; Zhang, H.; Fang, Z.; Yao, R.; Xu, M.; Wang, L.; Lan, L.; et al. High Mobility Amorphous Indium-Gallium-Zinc-Oxide Thin-Film Transistor by Aluminum Oxide Passivation Layer. IEEE Electron Device Lett. 2017, 38, 879. [Google Scholar] [CrossRef]

- Abliz, A. Hydrogenation of Mg-Doped InGaZnO Thin-Film Transistors for Enhanced Electrical Performance and Stability. IEEE Trans. Electron Devices 2021, 68, 3379–3383. [Google Scholar] [CrossRef]

| SG TFT (°C) | VTH (V) | Off Current (A) | ION/IOFF | μ (cm2/V·s) | S.S. (V/Decade) | Nt (cm−2·eV−1) |

|---|---|---|---|---|---|---|

| RT | 2.2 | 4.58 × 10−11 | 7.55 × 105 | 18.0 | 1.25 | 1.72 × 1012 |

| 100 | 2 | 2.56 × 10−11 | 8.74 × 106 | 36.9 | 1.09 | 1.49 × 1012 |

| 200 | 1.2 | 1.65 × 10−11 | 3.14 × 106 | 37.0 | 0.74 | 9.85 × 1011 |

| 300 | 1.1 | 1.04 × 10−11 | 9.93 × 106 | 38.8 | 0.7 | 9.27 × 1011 |

| DG TFT (°C) | VTH (V) | Off Current (A) | ION/IOFF | μ (cm2/V·s) | S.S. (V/Decade) | Nt (cm−2·eV−1) |

|---|---|---|---|---|---|---|

| 100 | 0.8 | 2.17 × 10−11 | 3.64 × 106 | 39.7 | 0.27 | 3.05 × 1011 |

| 200 | 0.8 | 1.45 × 10−11 | 2.73 × 107 | 42.6 | 0.20 | 2.03 × 1011 |

| 300 | 0.8 | 7.23 × 10−12 | 5.46 × 108 | 58.8 | 0.12 | 8.75 × 1010 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liu, W.-S.; Hsu, C.-H.; Jiang, Y.; Lai, Y.-C.; Kuo, H.-C. Improving Device Characteristics of Dual-Gate IGZO Thin-Film Transistors with Ar–O2 Mixed Plasma Treatment and Rapid Thermal Annealing. Membranes 2022, 12, 49. https://doi.org/10.3390/membranes12010049

Liu W-S, Hsu C-H, Jiang Y, Lai Y-C, Kuo H-C. Improving Device Characteristics of Dual-Gate IGZO Thin-Film Transistors with Ar–O2 Mixed Plasma Treatment and Rapid Thermal Annealing. Membranes. 2022; 12(1):49. https://doi.org/10.3390/membranes12010049

Chicago/Turabian StyleLiu, Wei-Sheng, Chih-Hao Hsu, Yu Jiang, Yi-Chun Lai, and Hsing-Chun Kuo. 2022. "Improving Device Characteristics of Dual-Gate IGZO Thin-Film Transistors with Ar–O2 Mixed Plasma Treatment and Rapid Thermal Annealing" Membranes 12, no. 1: 49. https://doi.org/10.3390/membranes12010049

APA StyleLiu, W.-S., Hsu, C.-H., Jiang, Y., Lai, Y.-C., & Kuo, H.-C. (2022). Improving Device Characteristics of Dual-Gate IGZO Thin-Film Transistors with Ar–O2 Mixed Plasma Treatment and Rapid Thermal Annealing. Membranes, 12(1), 49. https://doi.org/10.3390/membranes12010049