WRTU-16T: Write-Enhanced Low-Power Radiation-Tolerant SRAM for Space Applications

Abstract

1. Introduction

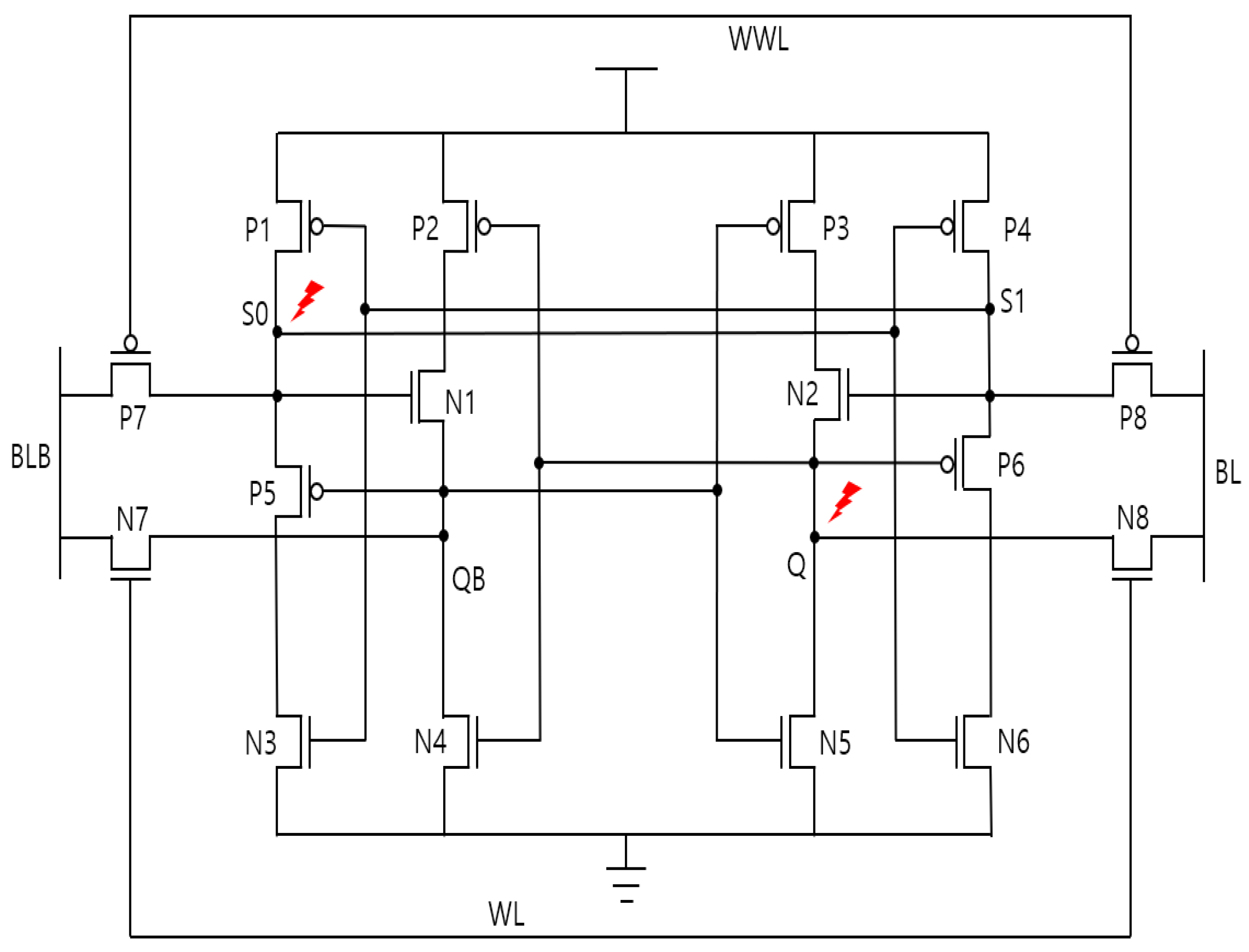

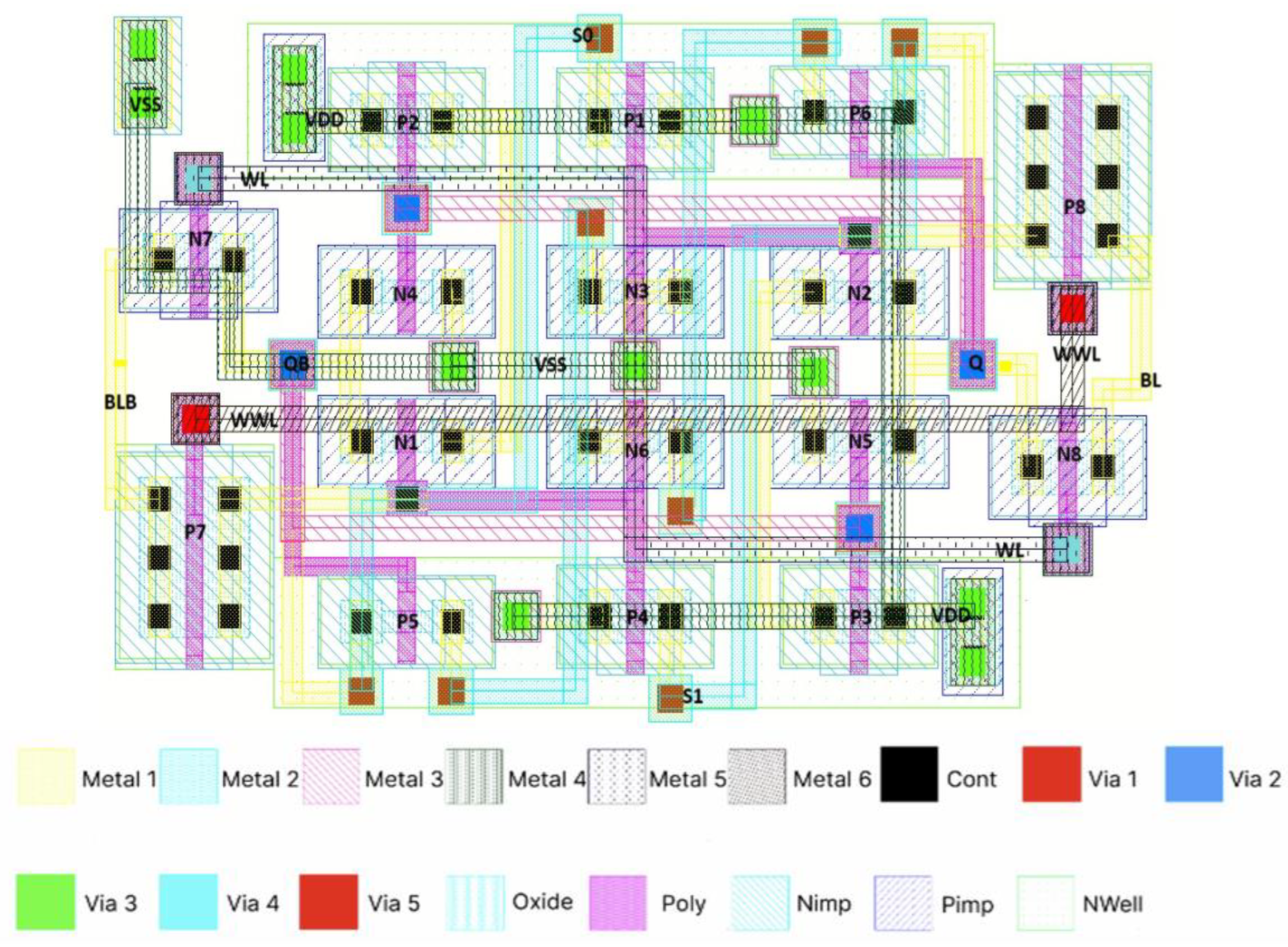

2. Proposed WRTU-16T SRAM Architecture

2.1. Proposed Cell Design

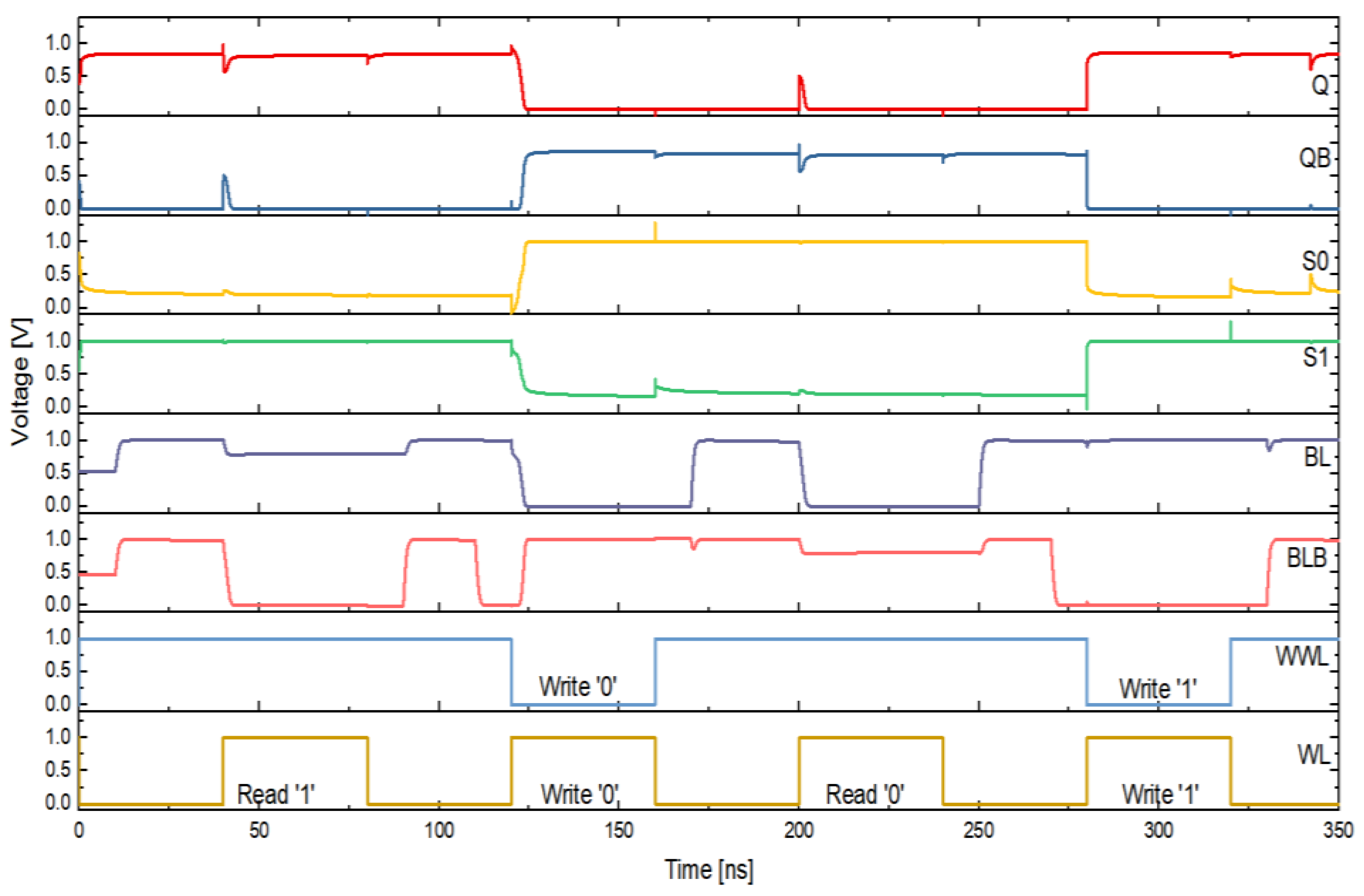

2.2. Hold Operation

2.3. Write Operation

2.4. Read Operation

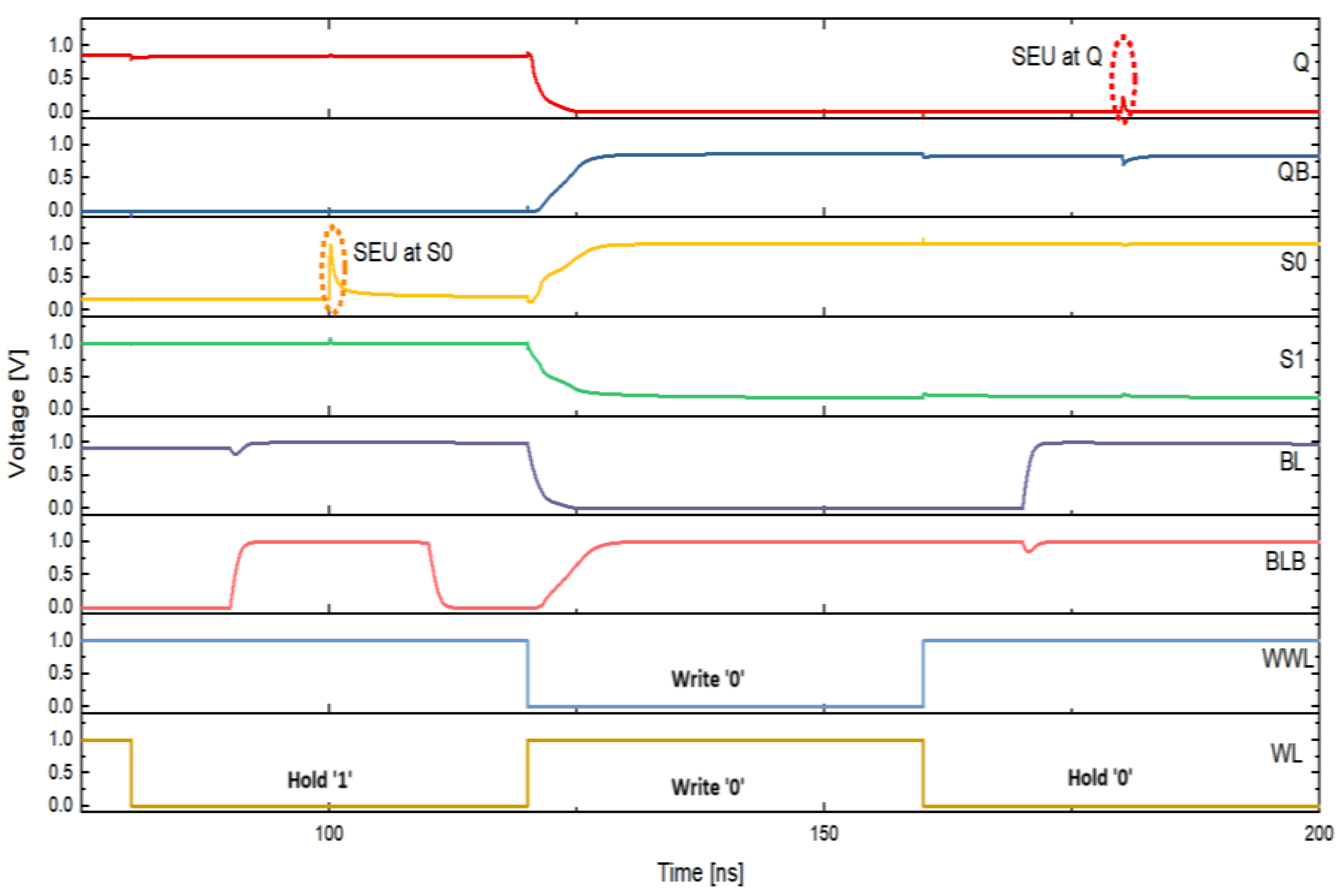

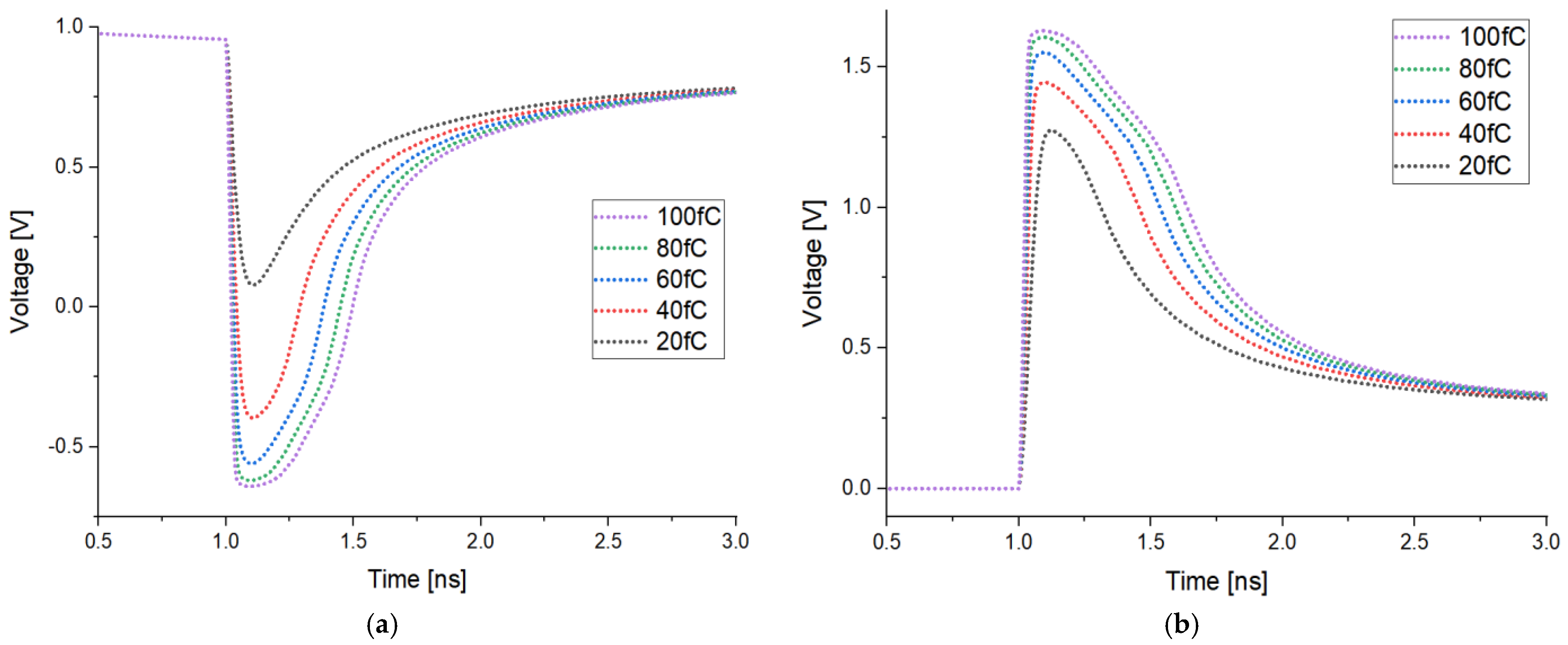

2.5. SEU Recovery Analysis

2.5.1. SEU at Node Q

2.5.2. SEU at Node S0

2.5.3. SEMNU at Node Pair Q-S0

3. Implementation Results and Analysis

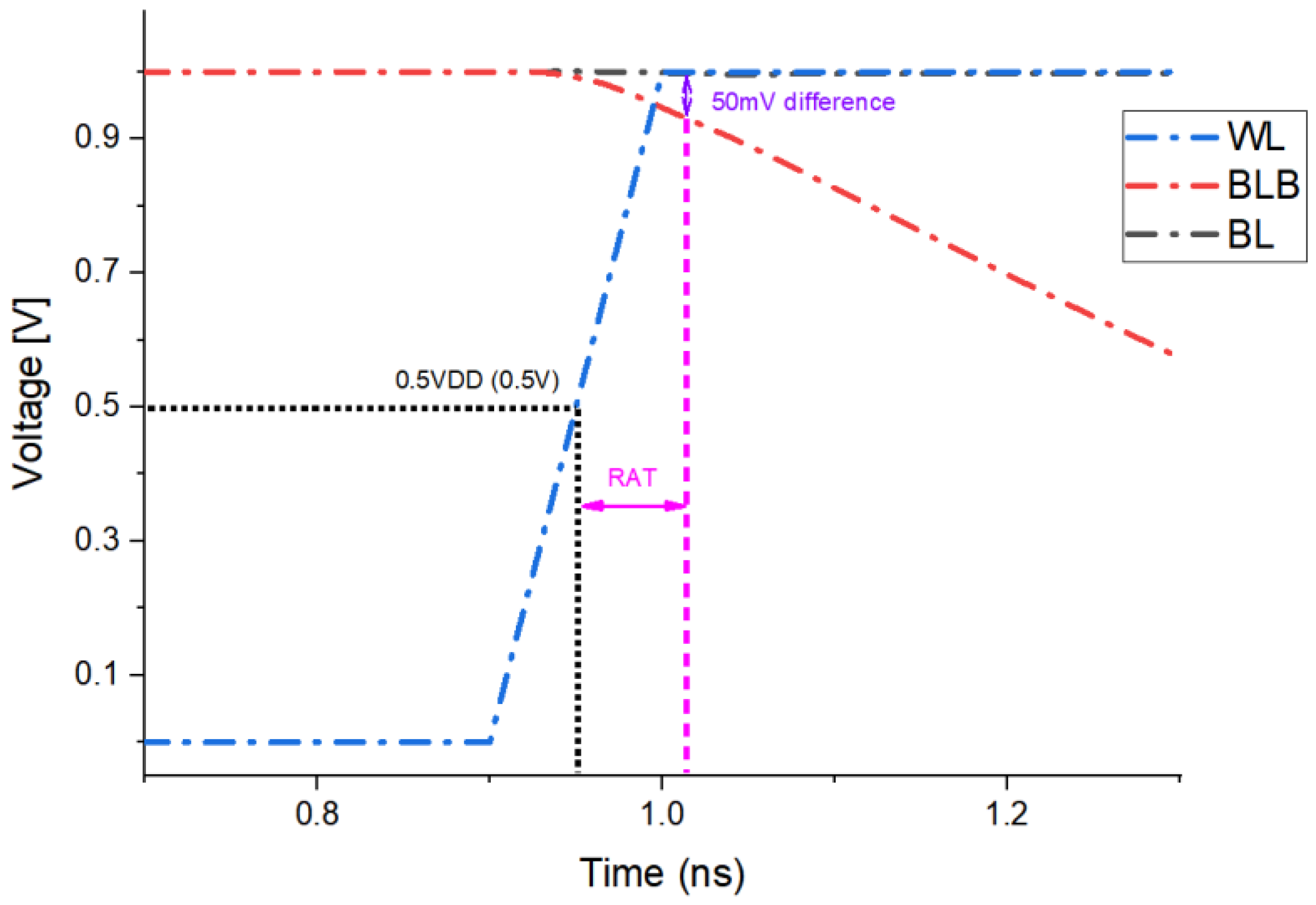

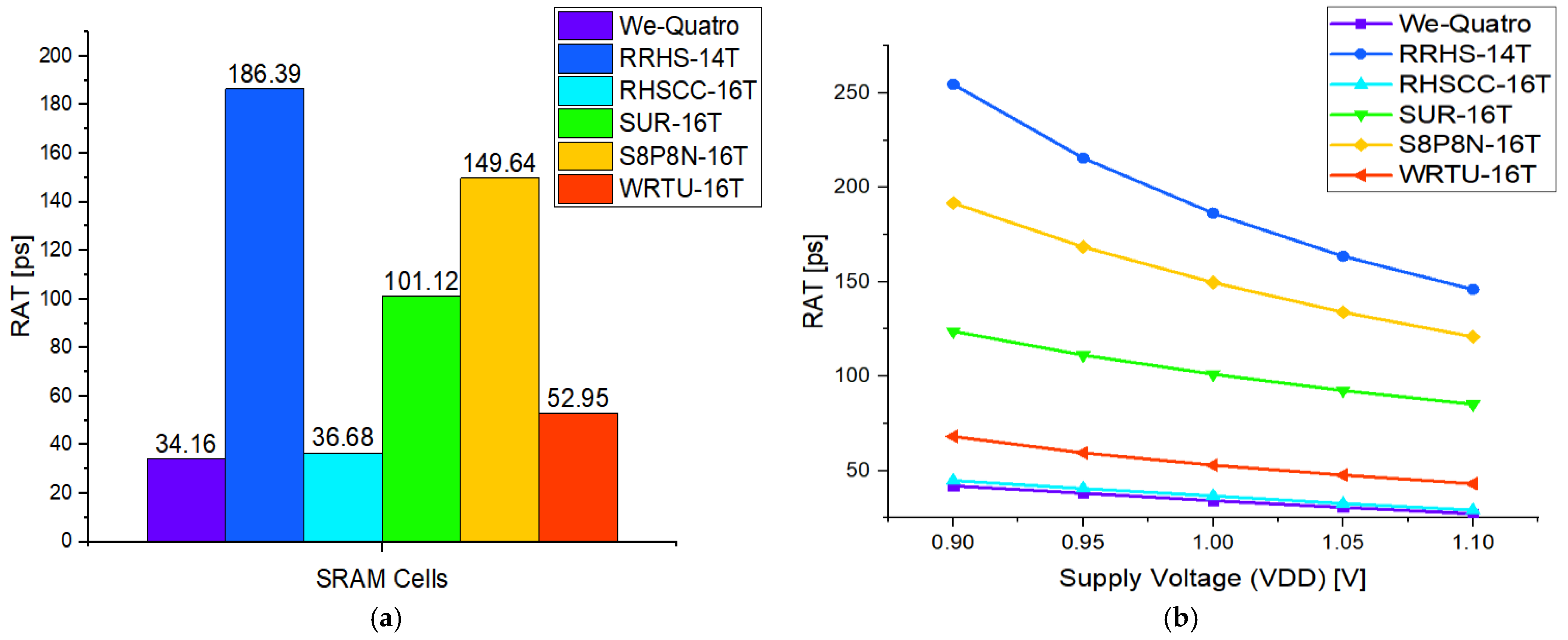

3.1. Read Access Time

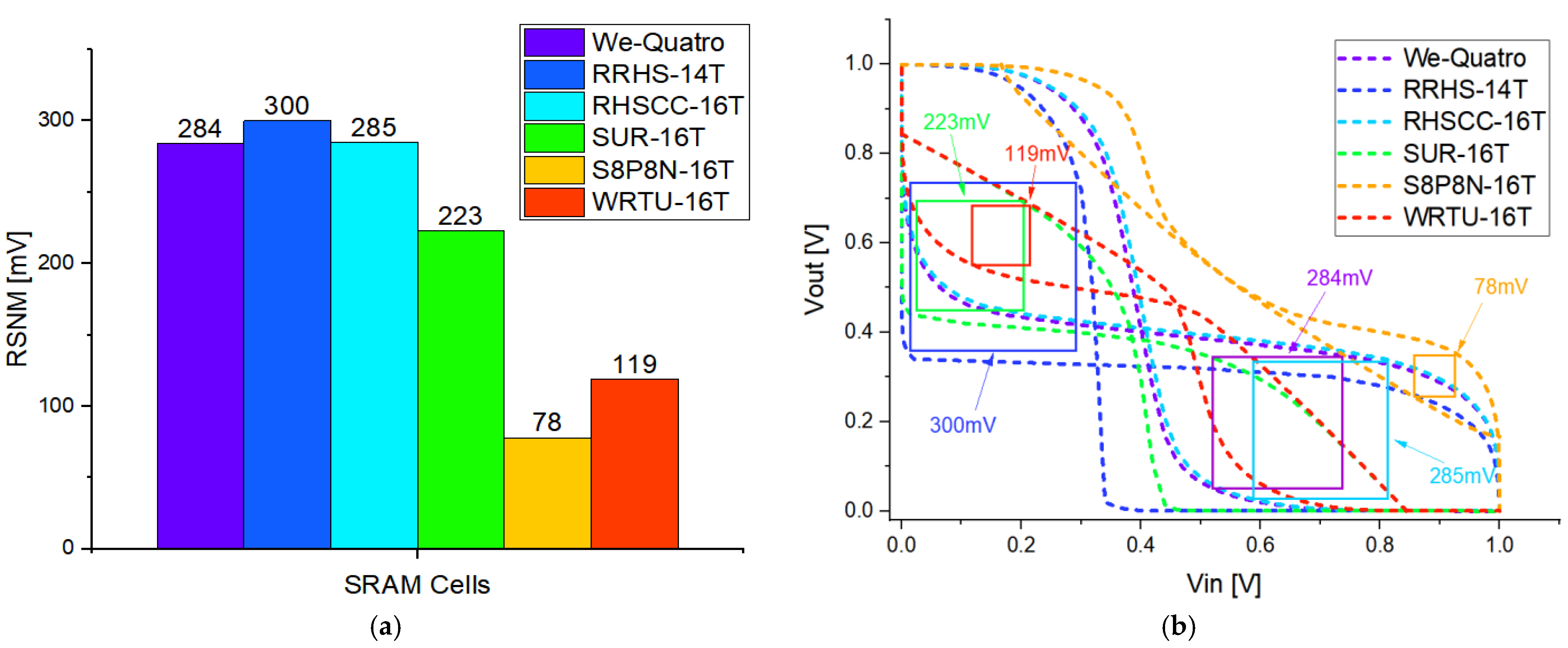

3.2. Read Static Noise Margin

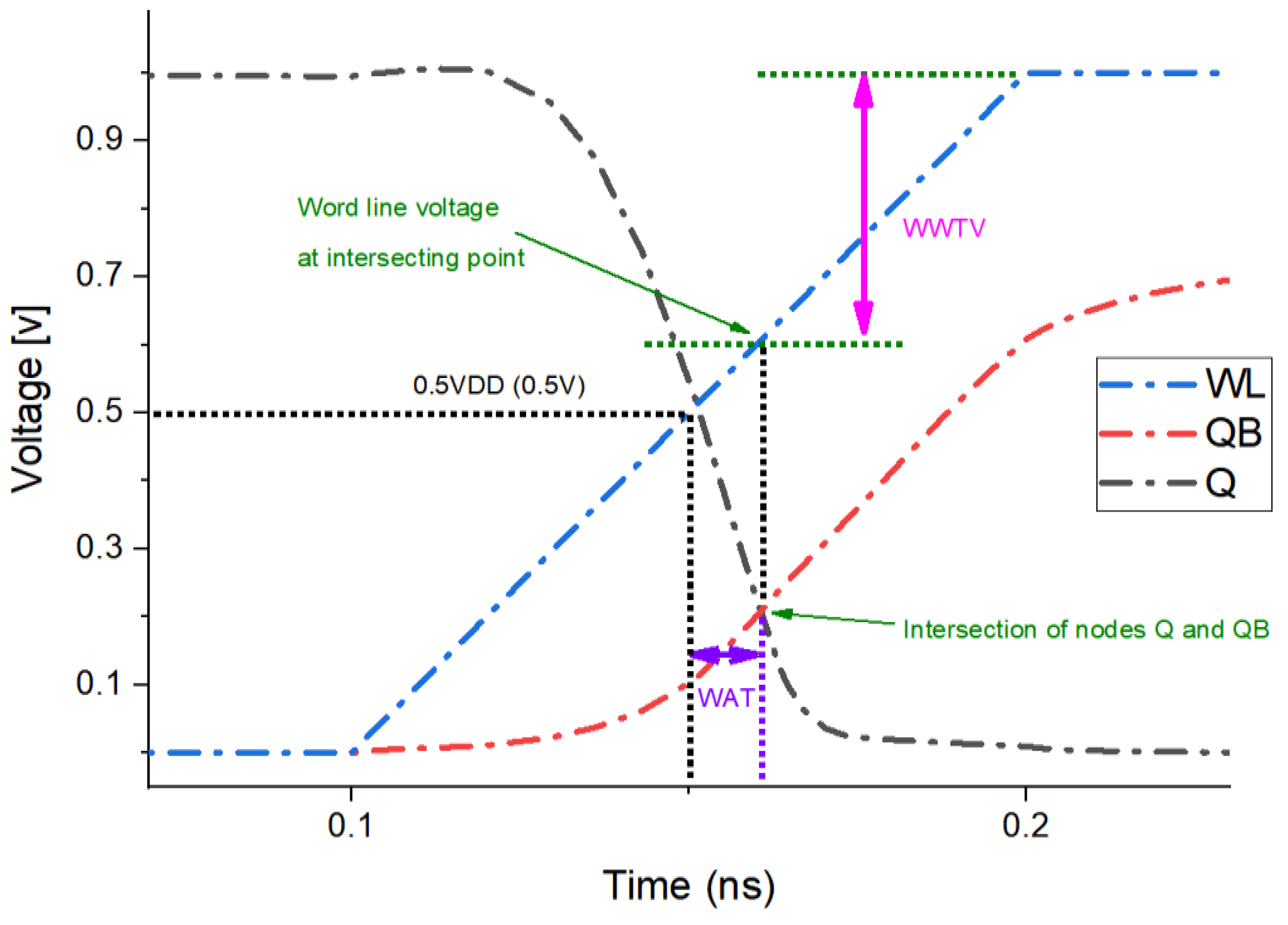

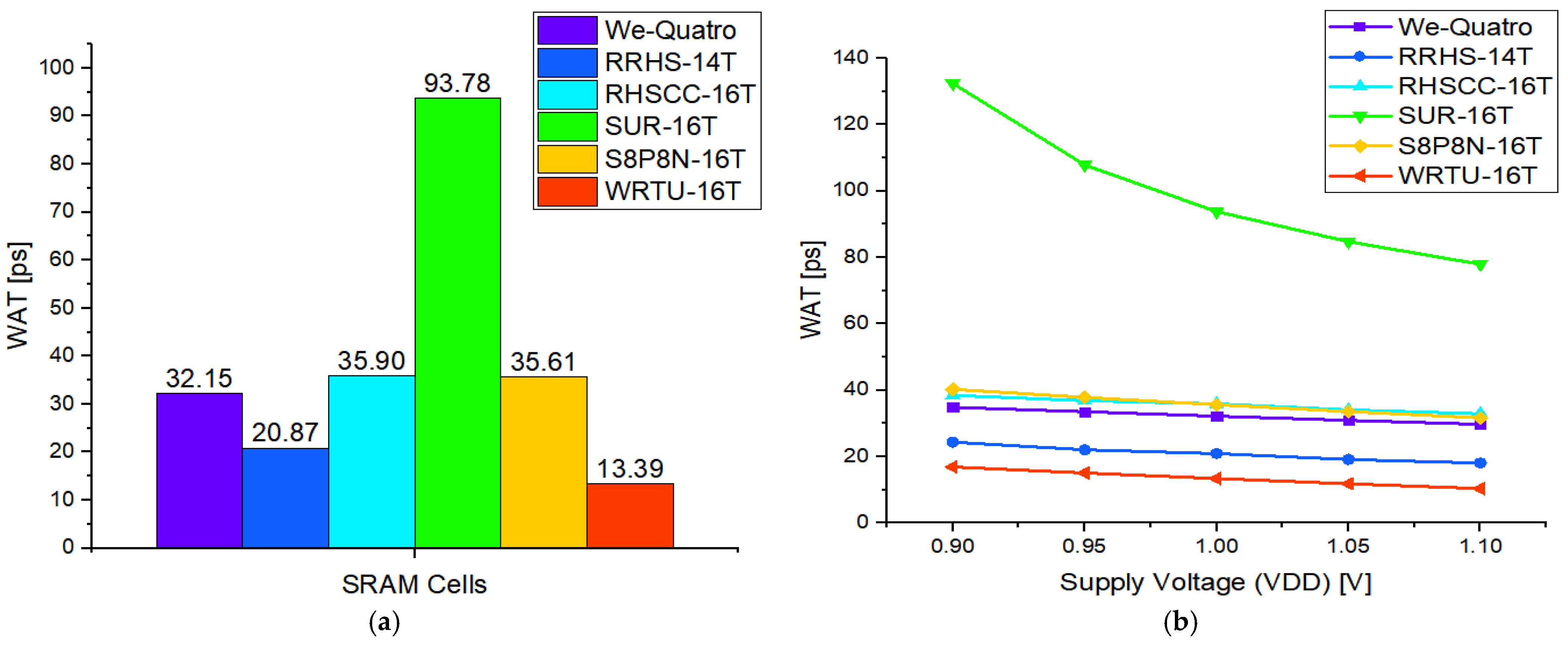

3.3. Write Access Time

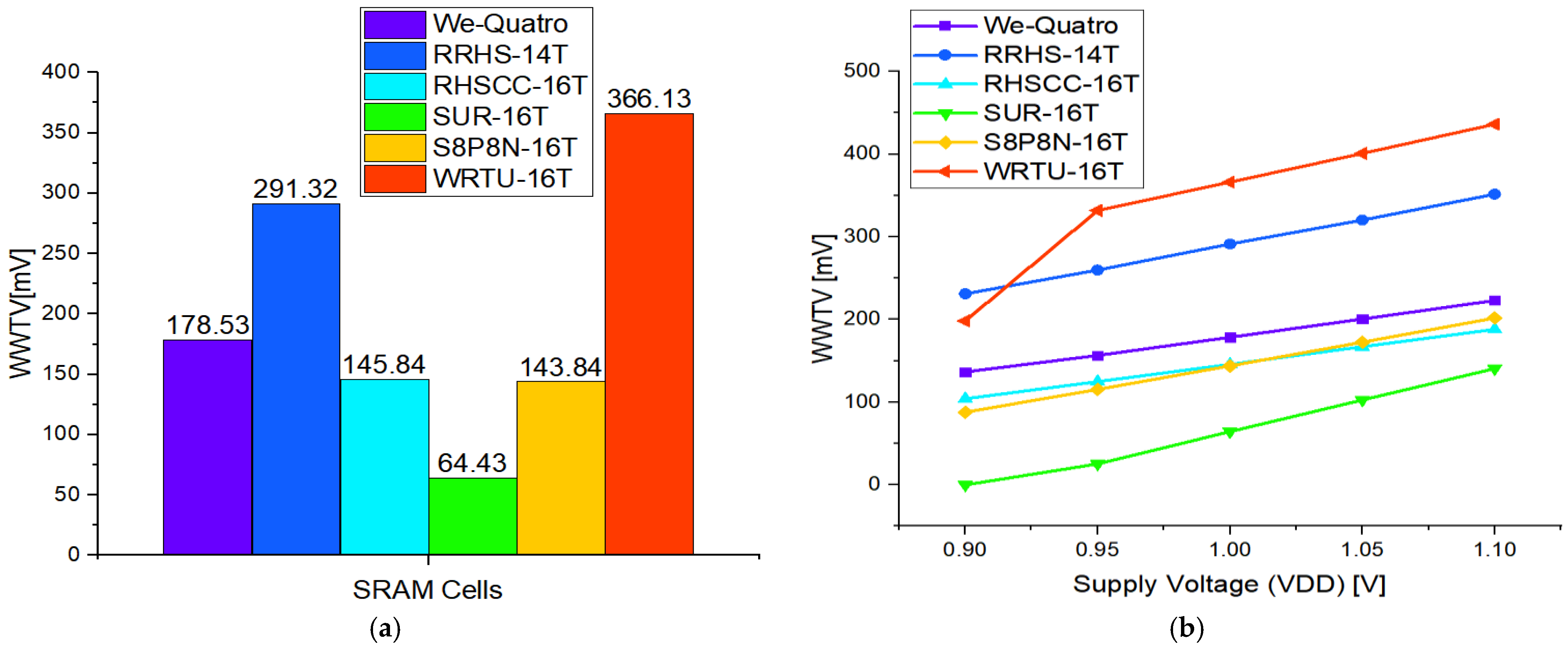

3.4. Word Line Write Trip Voltage

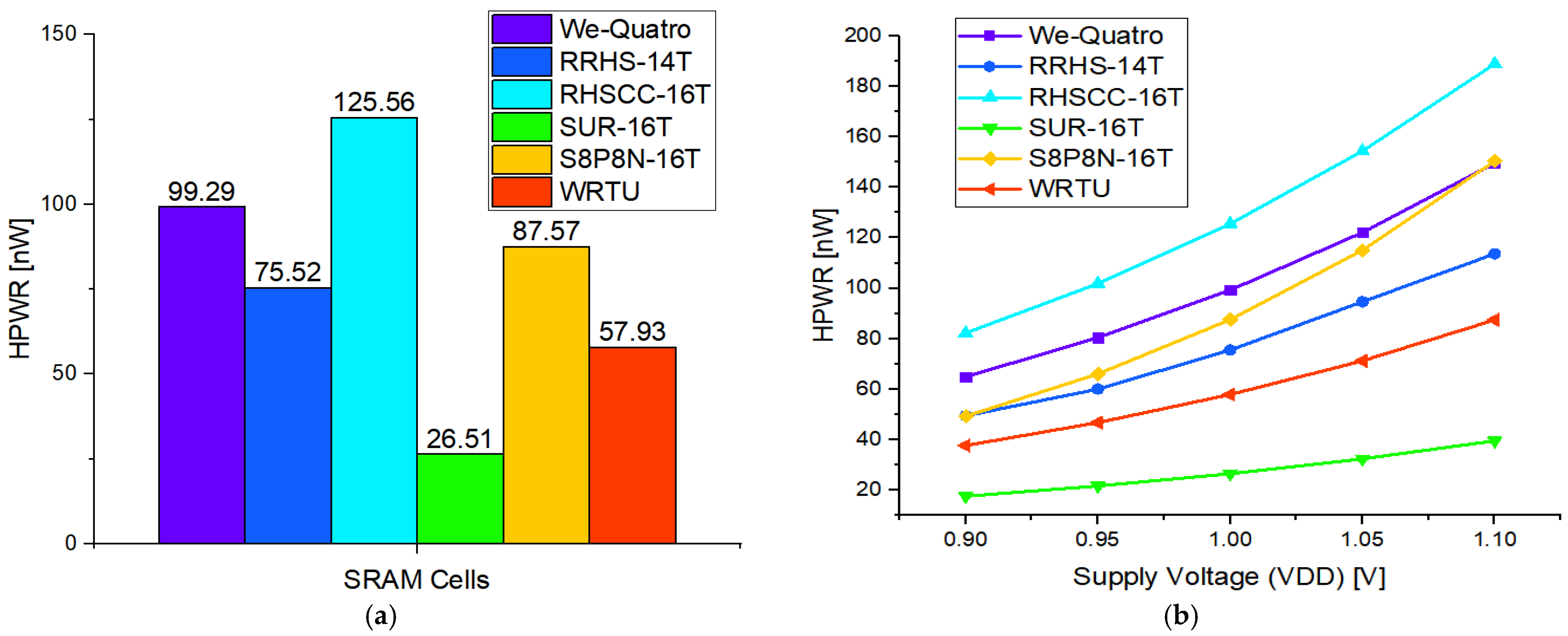

3.5. Hold Power

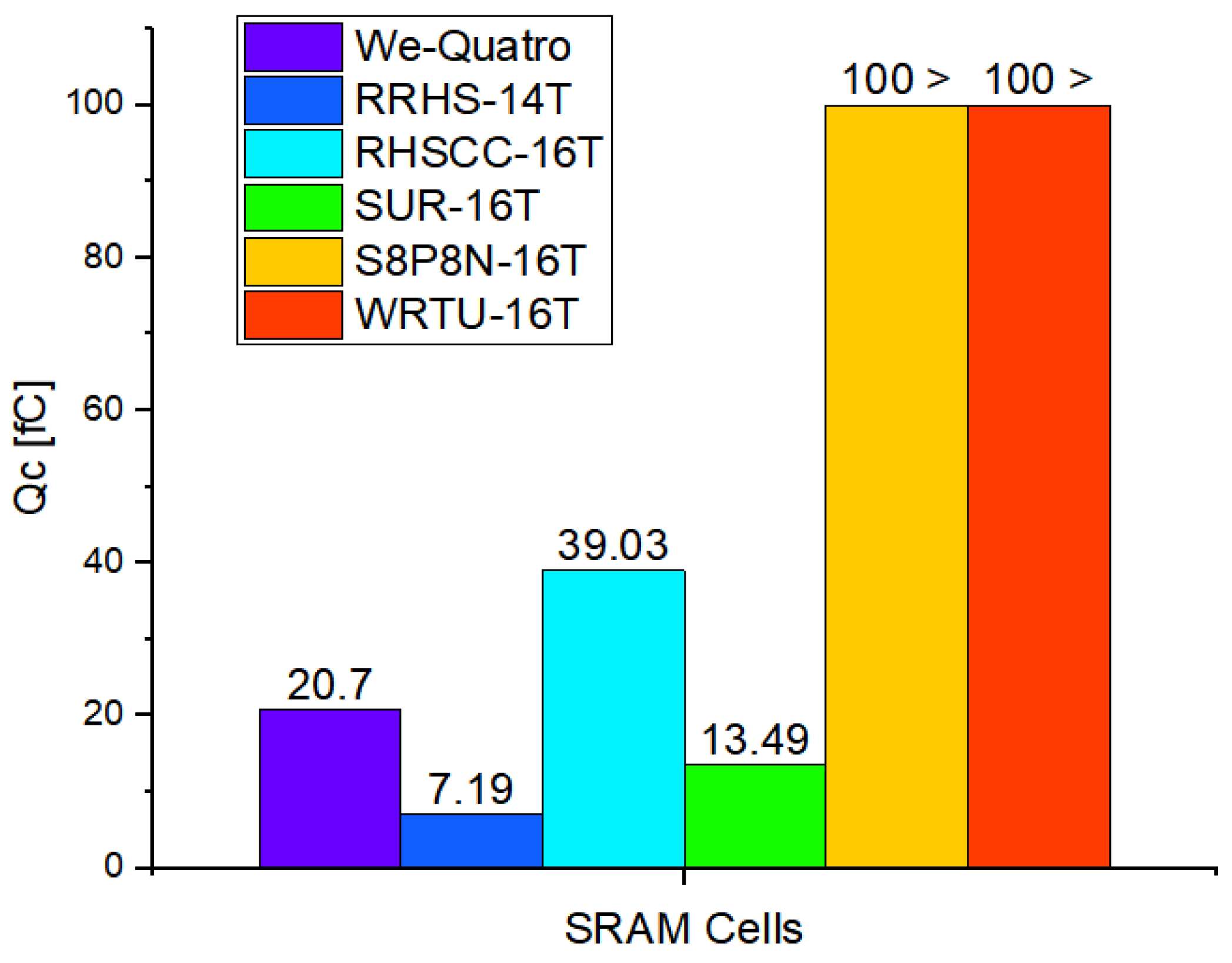

3.6. Soft Error Robustness Analysis

3.7. Area

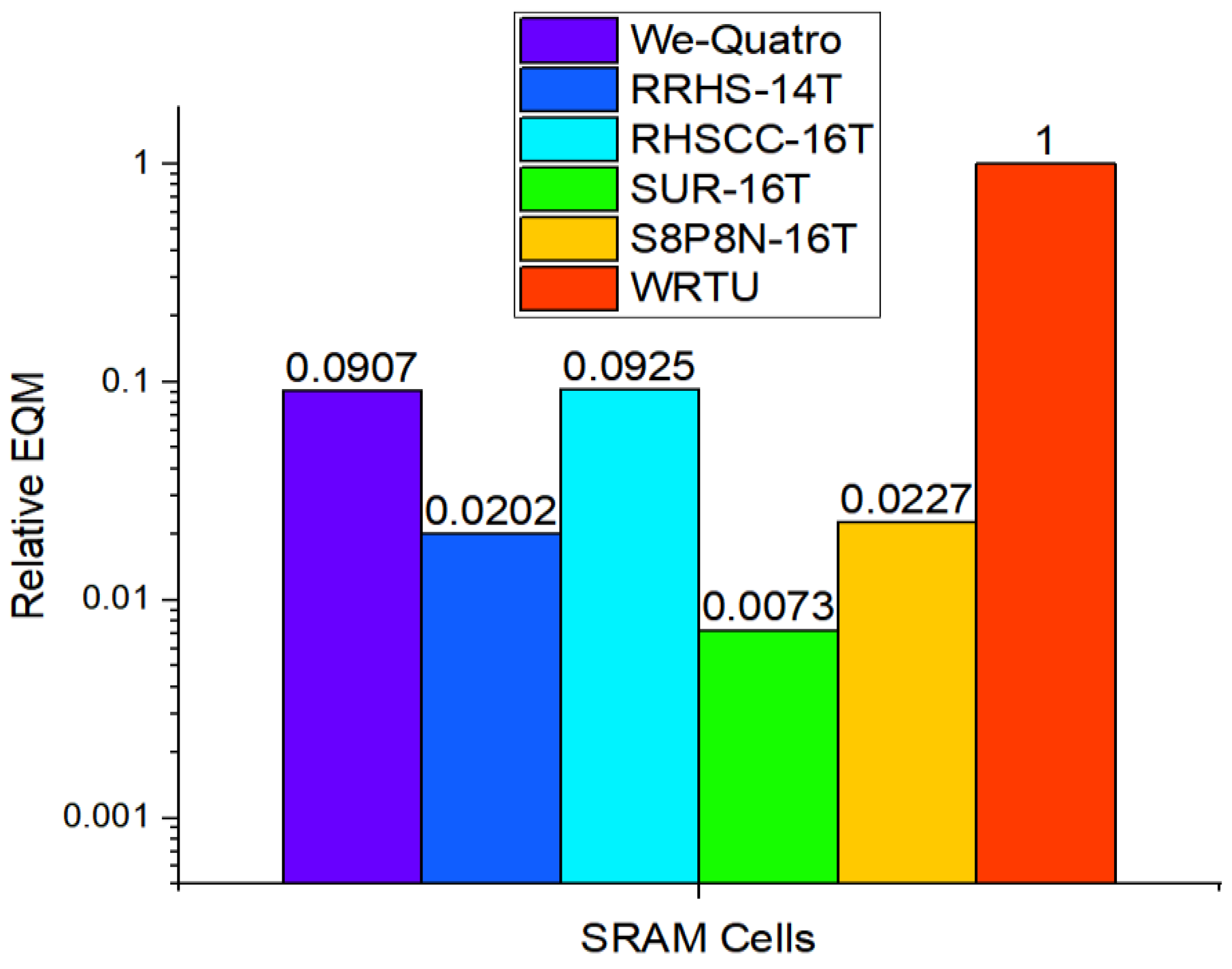

3.8. Electrical Quality Metric

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Kim, C.; Lee, D.; Na, J. A Comparison of Reliability and Resource Utilization of Radiation Fault Tolerance Mechanisms in Spaceborne Electronic Systems. Aerospace 2025, 12, 152. [Google Scholar] [CrossRef]

- Trang Dang, L.D.; Kim, J.S.; Chang, I.J. We-Quatro: Radiation-Hardened SRAM Cell With Parametric Process Variation Tolerance. IEEE Trans. Nucl. Sci. 2017, 64, 2489–2496. [Google Scholar] [CrossRef]

- Bai, N.; Wang, F.; Xu, Y.; Wang, S.; Wen, X. Reconfigurable Radiation-Hardened SRAM Cell Design for Different Radiation Environments. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2025, 1, 1. [Google Scholar] [CrossRef]

- Bharti, P.K.; Mekie, J. RHSCC-16T: Radiation Hardened Sextuple Cross Coupled Robust SRAM Design for Radiation Prone Environments. In Proceedings of the 2022 IEEE 40th International Conference on Computer Design (ICCD), Olympic Valley, CA, USA, 23–26 October 2022; pp. 17–24. [Google Scholar]

- Mukku, P.K.; Lorenzo, R. A Soft Error Upset Recovery SRAM Cell for Aerospace and Military Applications. In Proceedings of the TENCON 2023-2023 IEEE Region 10 Conference (TENCON), Chiang Mai, Thailand, 31 October 2023; pp. 744–749. [Google Scholar]

- Bai, N.; Xiao, X.; Xu, Y.; Wang, Y.; Wang, L.; Zhou, X. Soft-Error-Aware SRAM With Multinode Upset Tolerance for Aerospace Applications. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2024, 32, 128–136. [Google Scholar] [CrossRef]

- Yao, R.; Lv, H.; Zhang, Y.; Chen, X.; Zhang, Y.; Liu, X.; Bai, G. A High-Reliability 12T SRAM Radiation-Hardened Cell for Aerospace Applications. Micromachines 2023, 14, 1305. [Google Scholar] [CrossRef] [PubMed]

- Jiang, J.; Xu, Y.; Zhu, W.; Xiao, J.; Zou, S. Quadruple Cross-Coupled Latch-Based 10T and 12T SRAM Bit-Cell Designs for Highly Reliable Terrestrial Applications. IEEE Trans. Circuits Syst. Regul. Pap. 2019, 66, 967–977. [Google Scholar] [CrossRef]

- Kim, K.; Oh, T.W.; Jung, S.-O. Bitline Charge Sharing Suppressed Bitline and Cell Supply Collapse Assists for Energy-Efficient 6T SRAM. IEEE Access 2021, 9, 57393–57403. [Google Scholar] [CrossRef]

- Grossar, E.; Stucchi, M.; Maex, K.; Dehaene, W. Read Stability and Write-Ability Analysis of SRAM Cells for Nanometer Technologies. IEEE J. Solid-State Circuits 2006, 41, 2577–2588. [Google Scholar] [CrossRef]

- Alorda, B.; Carmona, C.; Torrens, G.; Bota, S. An Affordable Experimental Technique for SRAM Write Margin Characterization for Nanometer CMOS Technologies. Microelectron. Reliab. 2016, 65, 280–288. [Google Scholar] [CrossRef]

- Liu, C.; Liu, H.; Yang, J. A Novel Low-Power and Soft Error Recovery 10T SRAM Cell. Micromachines 2023, 14, 845. [Google Scholar] [CrossRef] [PubMed]

- Jahinuzzaman, S.M.; Sharifkhani, M.; Sachdev, M. An Analytical Model for Soft Error Critical Charge of Nanometric SRAMs. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2009, 17, 1187–1195. [Google Scholar] [CrossRef]

- Thirugnanam, S.; Soong, L.W.; Prabhu, C.M.; Singh, A.K. Energy-Efficient and Variability-Resilient 11T SRAM Design Using Data-Aware Read–Write Assist (DARWA) Technique for Low-Power Applications. Sensors 2023, 23, 5095. [Google Scholar] [CrossRef] [PubMed]

| SRAMs | Qc (fC) | RAT (ps) | RSNM (mV) | WAT (ps) | WWTV (mV) | HPWR (nW) |

|---|---|---|---|---|---|---|

| We-Quatro [2] | 20.70 | 34.16 | 284 | 32.15 | 178.53 | 99.29 |

| RRHS-14T [3] | 7.19 | 186.39 | 300 | 20.87 | 291.32 | 75.52 |

| RHSCC-16T [4] | 39.03 | 36.68 | 285 | 35.90 | 145.84 | 125.56 |

| SUR-16T [5] | 13.49 | 101.12 | 223 | 93.78 | 64.43 | 26.51 |

| S8P8N-16T [6] | >100 | 149.64 | 78 | 35.61 | 143.84 | 87.57 |

| WRTU-16T | >100 | 52.95 | 119 | 13.39 | 366.13 | 57.93 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, S.-H.; Jo, S.-H. WRTU-16T: Write-Enhanced Low-Power Radiation-Tolerant SRAM for Space Applications. Appl. Sci. 2025, 15, 7295. https://doi.org/10.3390/app15137295

Lee S-H, Jo S-H. WRTU-16T: Write-Enhanced Low-Power Radiation-Tolerant SRAM for Space Applications. Applied Sciences. 2025; 15(13):7295. https://doi.org/10.3390/app15137295

Chicago/Turabian StyleLee, Seung-Hyun, and Sung-Hun Jo. 2025. "WRTU-16T: Write-Enhanced Low-Power Radiation-Tolerant SRAM for Space Applications" Applied Sciences 15, no. 13: 7295. https://doi.org/10.3390/app15137295

APA StyleLee, S.-H., & Jo, S.-H. (2025). WRTU-16T: Write-Enhanced Low-Power Radiation-Tolerant SRAM for Space Applications. Applied Sciences, 15(13), 7295. https://doi.org/10.3390/app15137295