Performance Analysis of Modular Multilevel Converter with NPC Sub-Modules in Photovoltaic Grid-Integration

Abstract

:1. Introduction

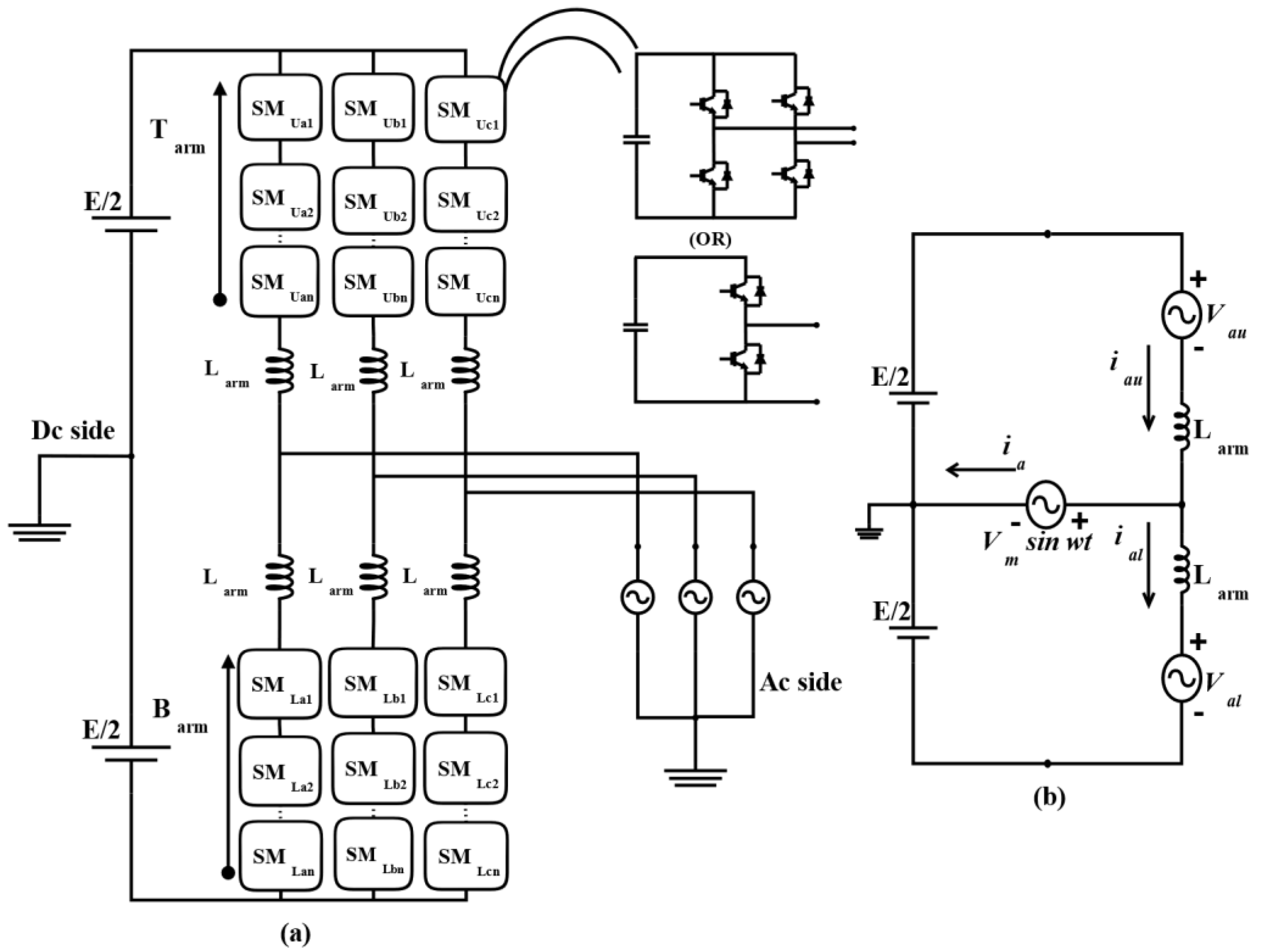

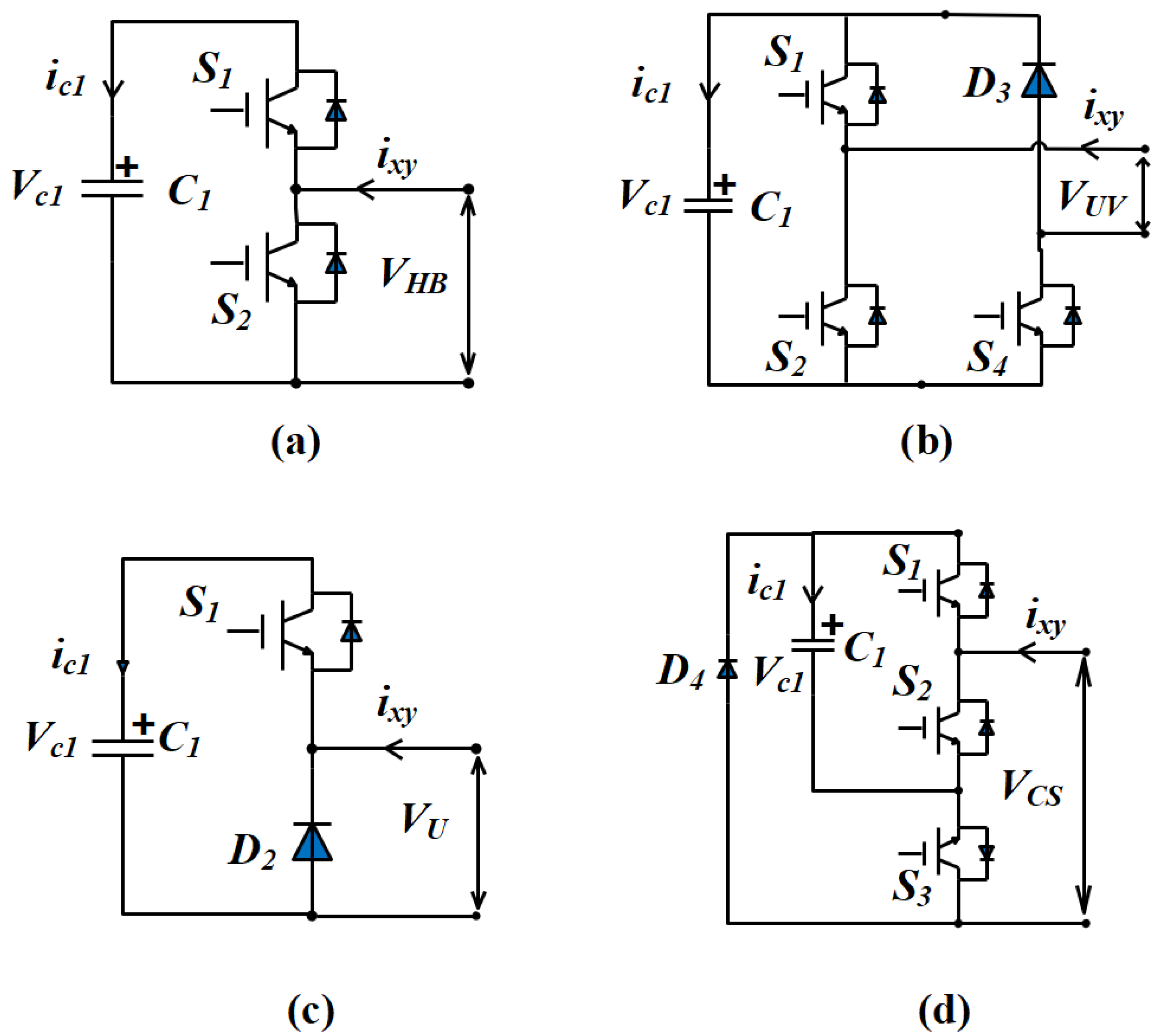

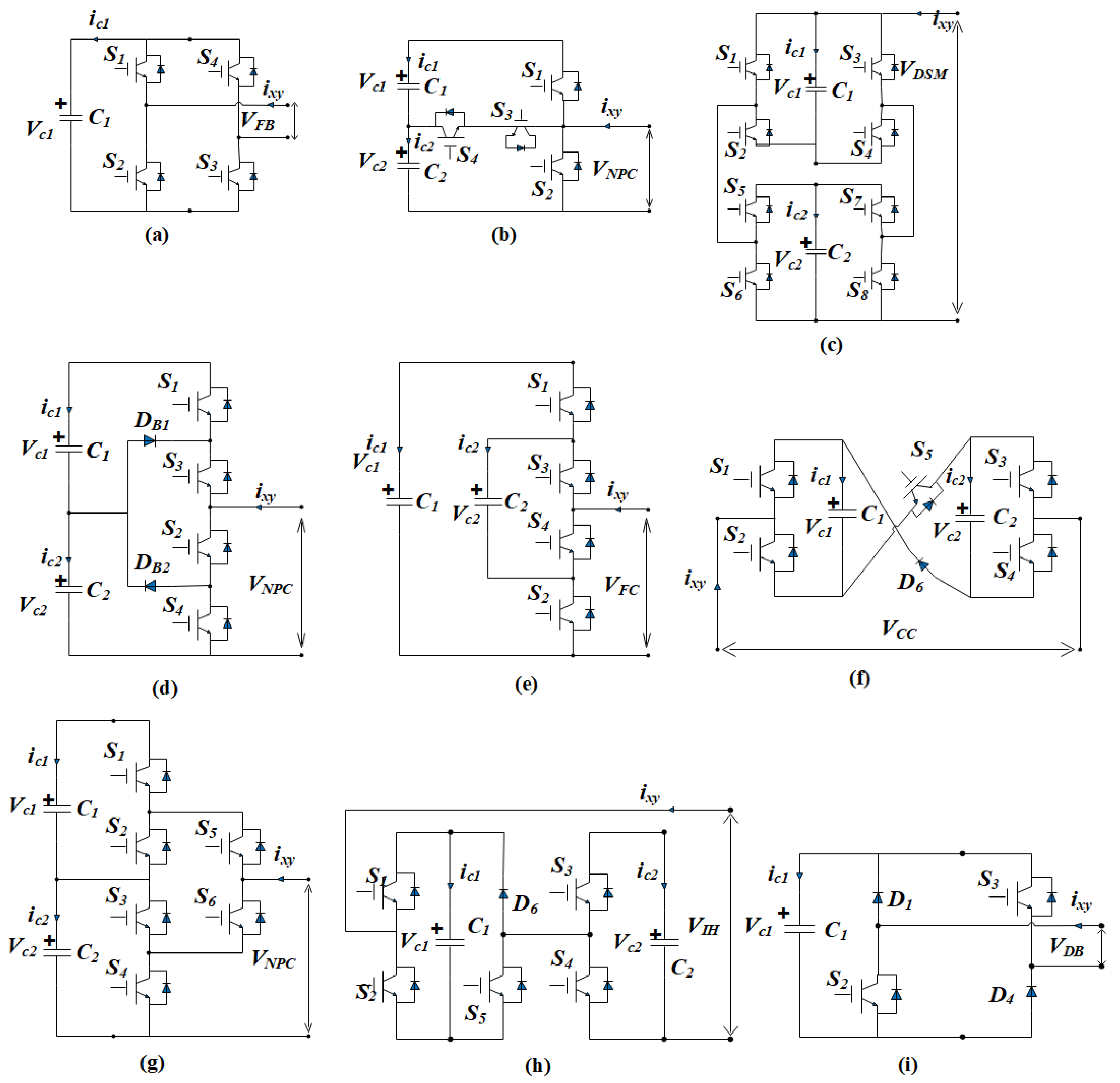

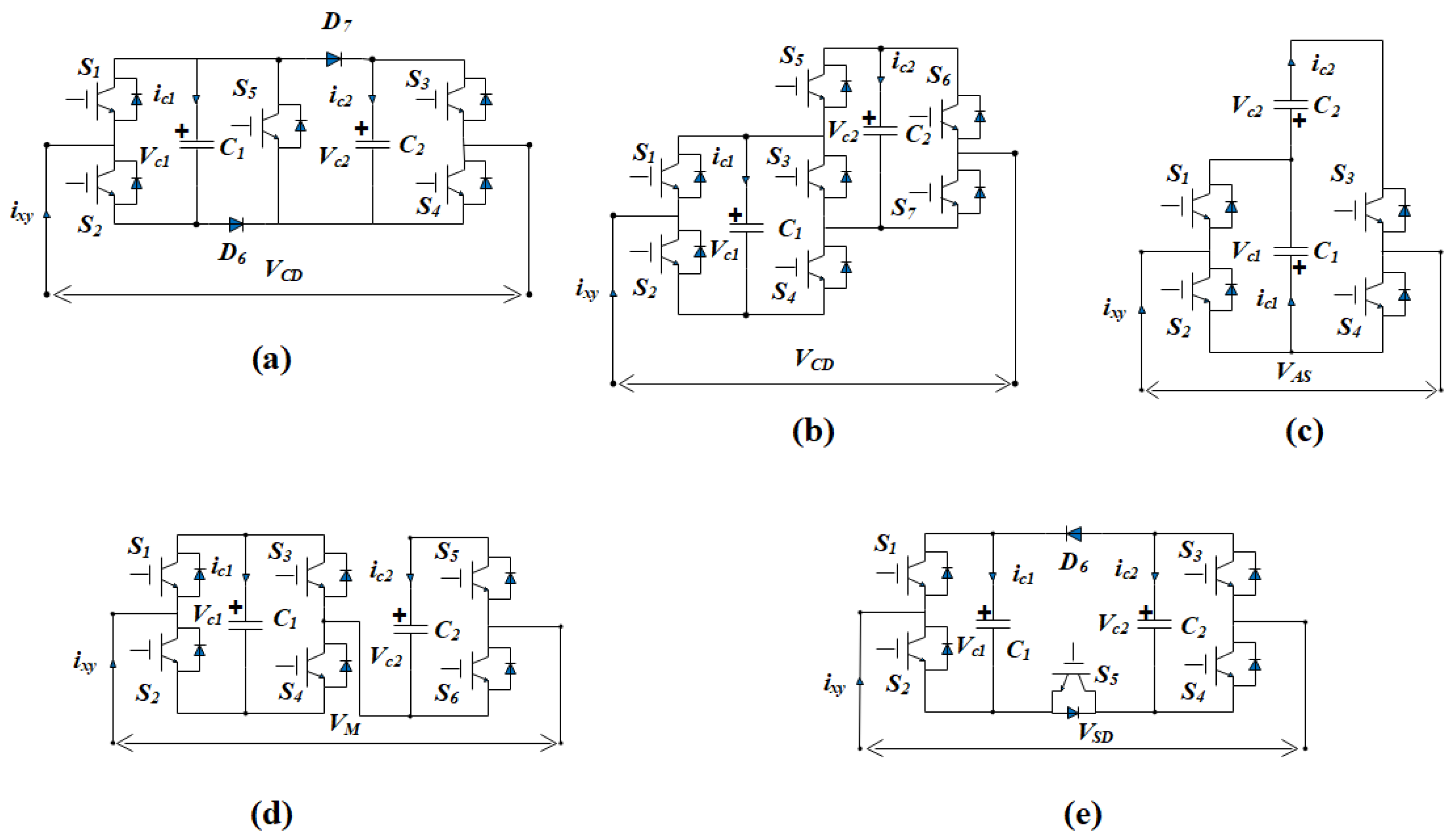

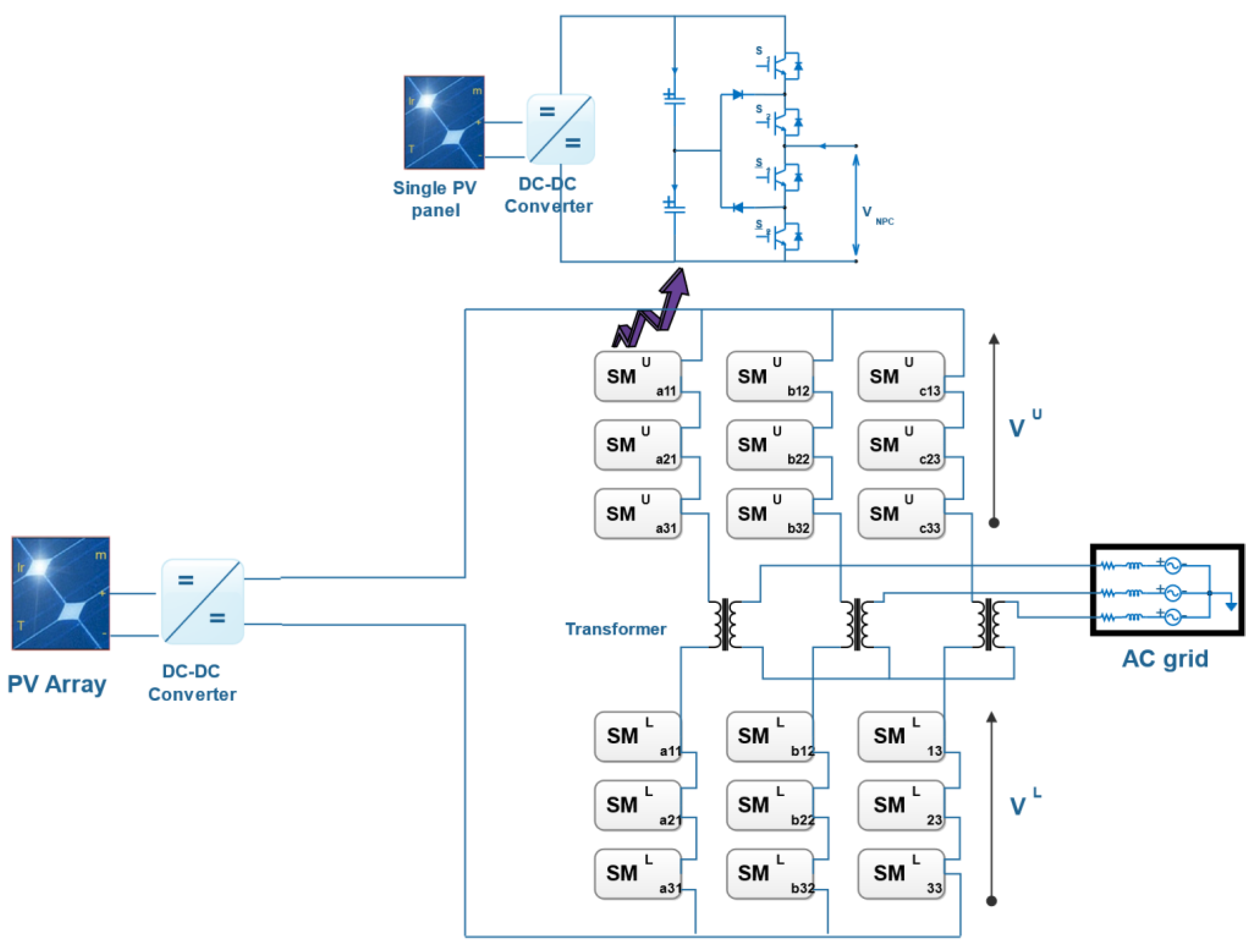

2. Modular Multilevel Converter and Sub Module Variants

3. Control Strategy of the Proposed MMC

4. Modulation Strategies

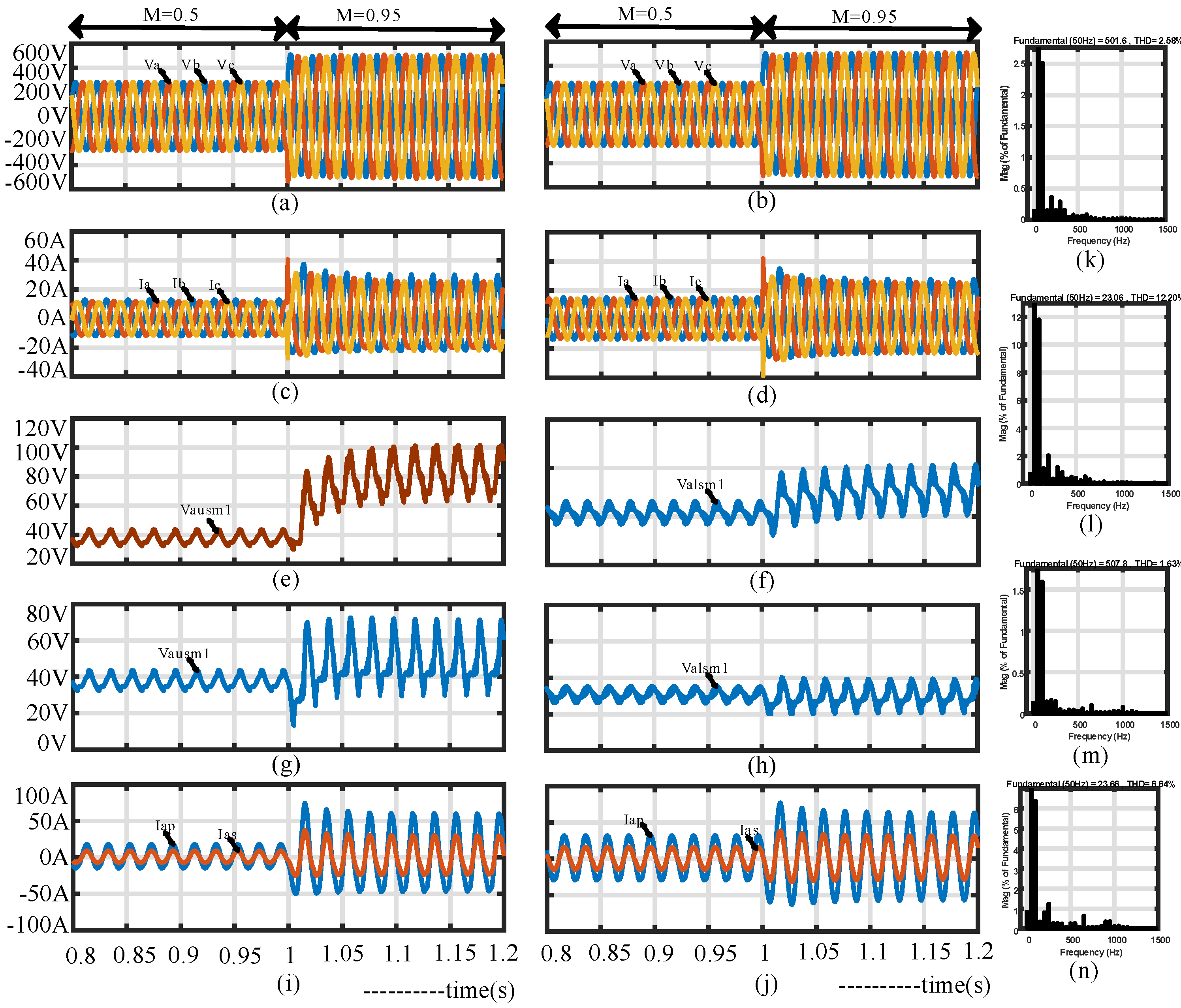

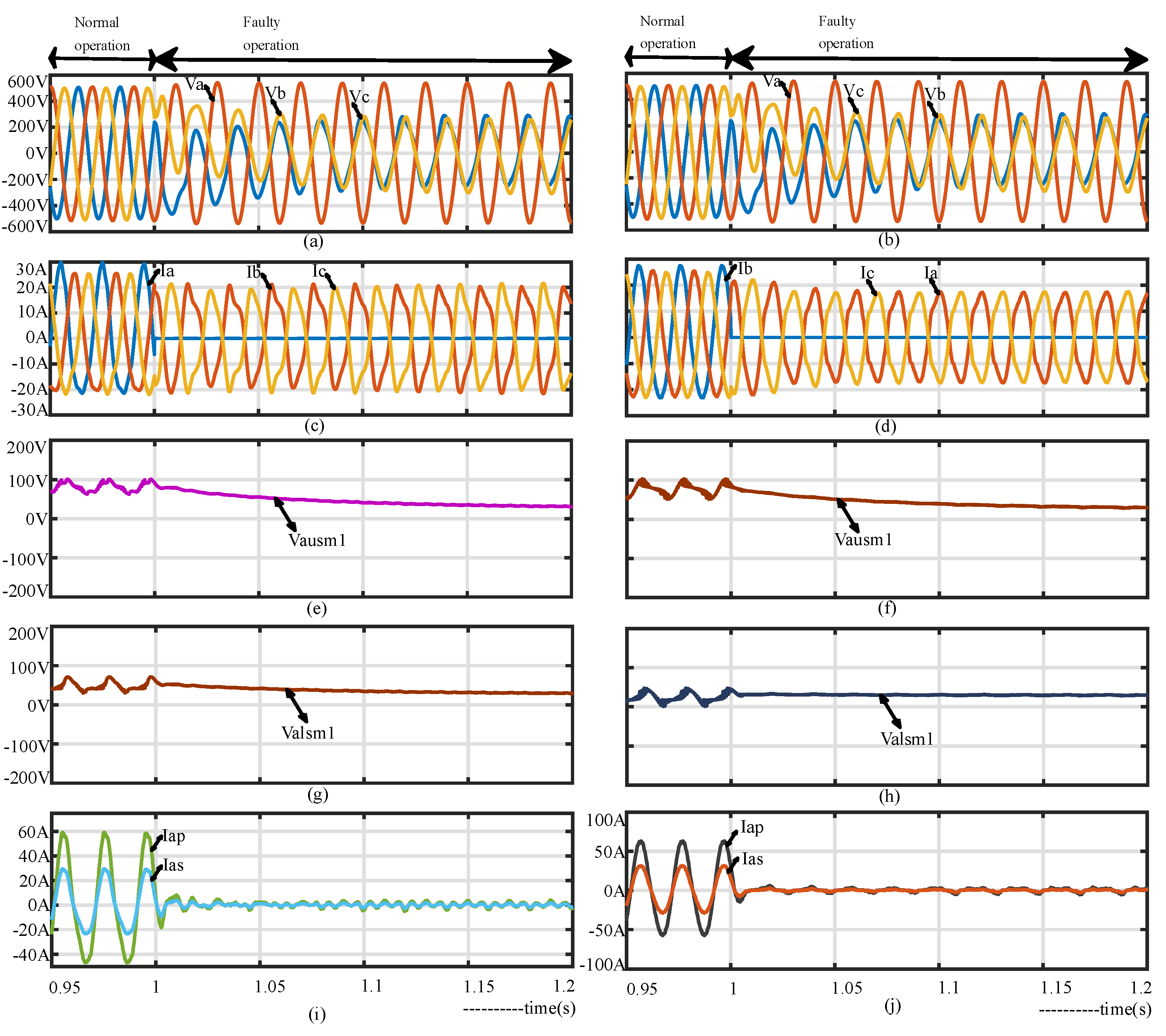

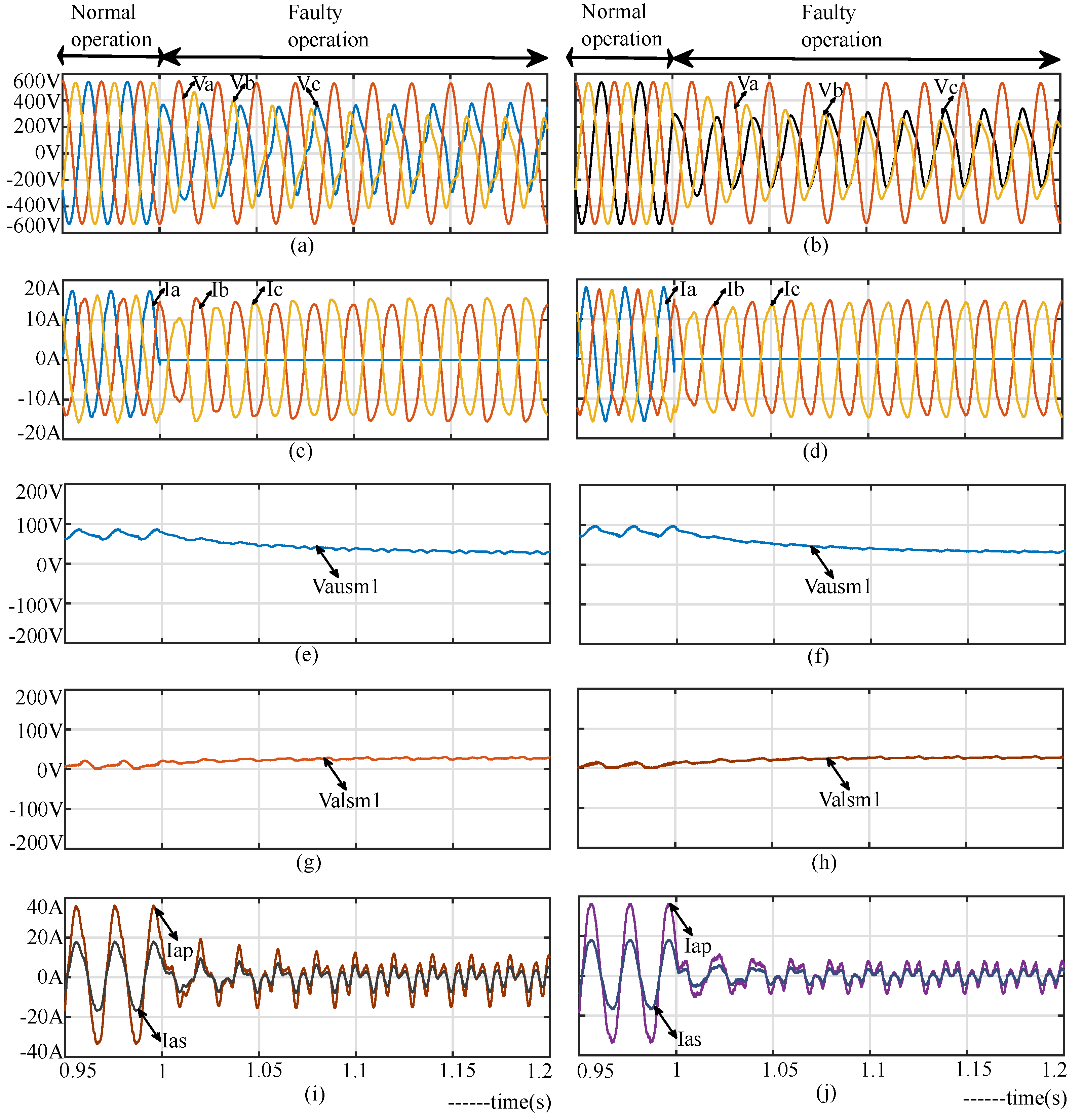

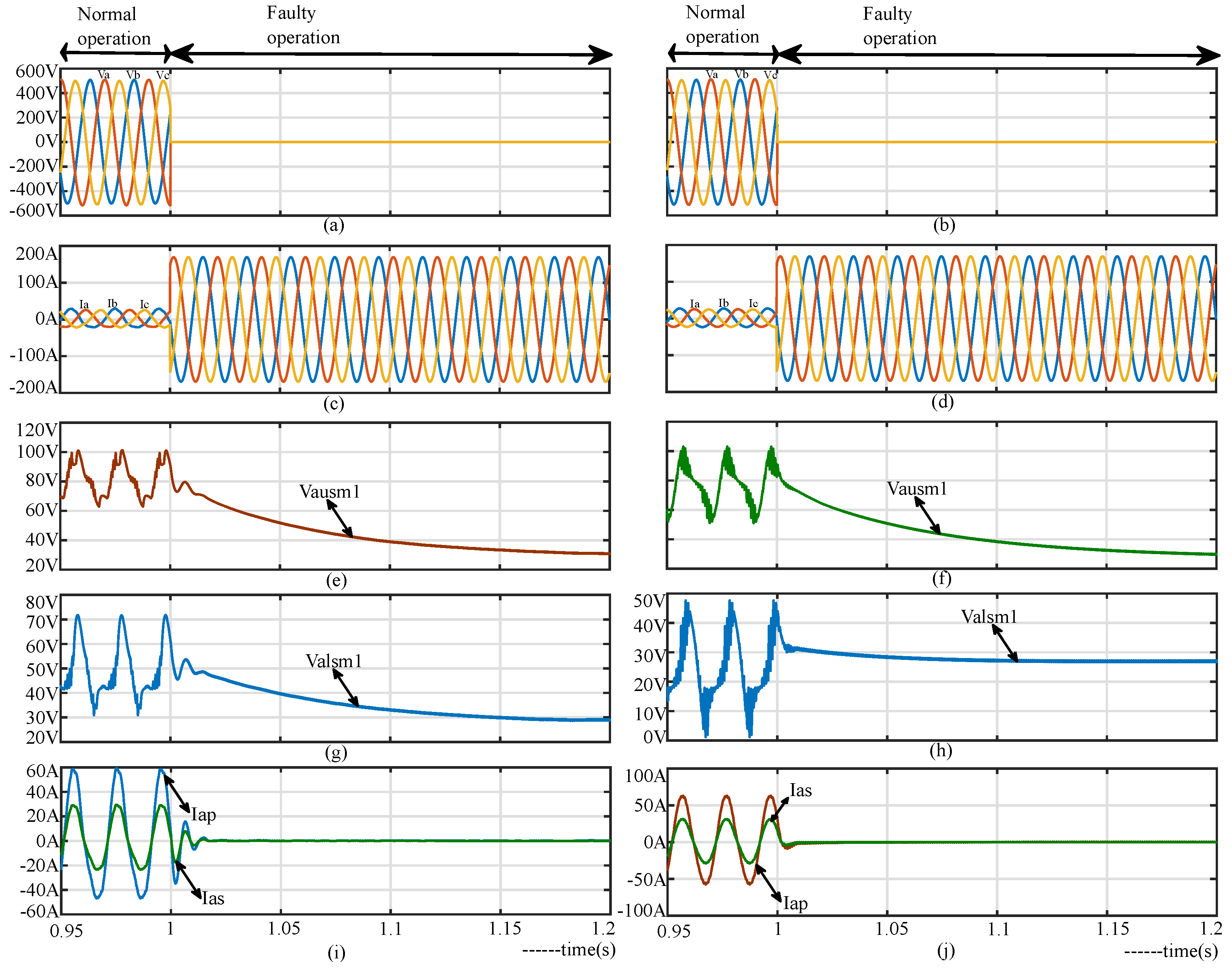

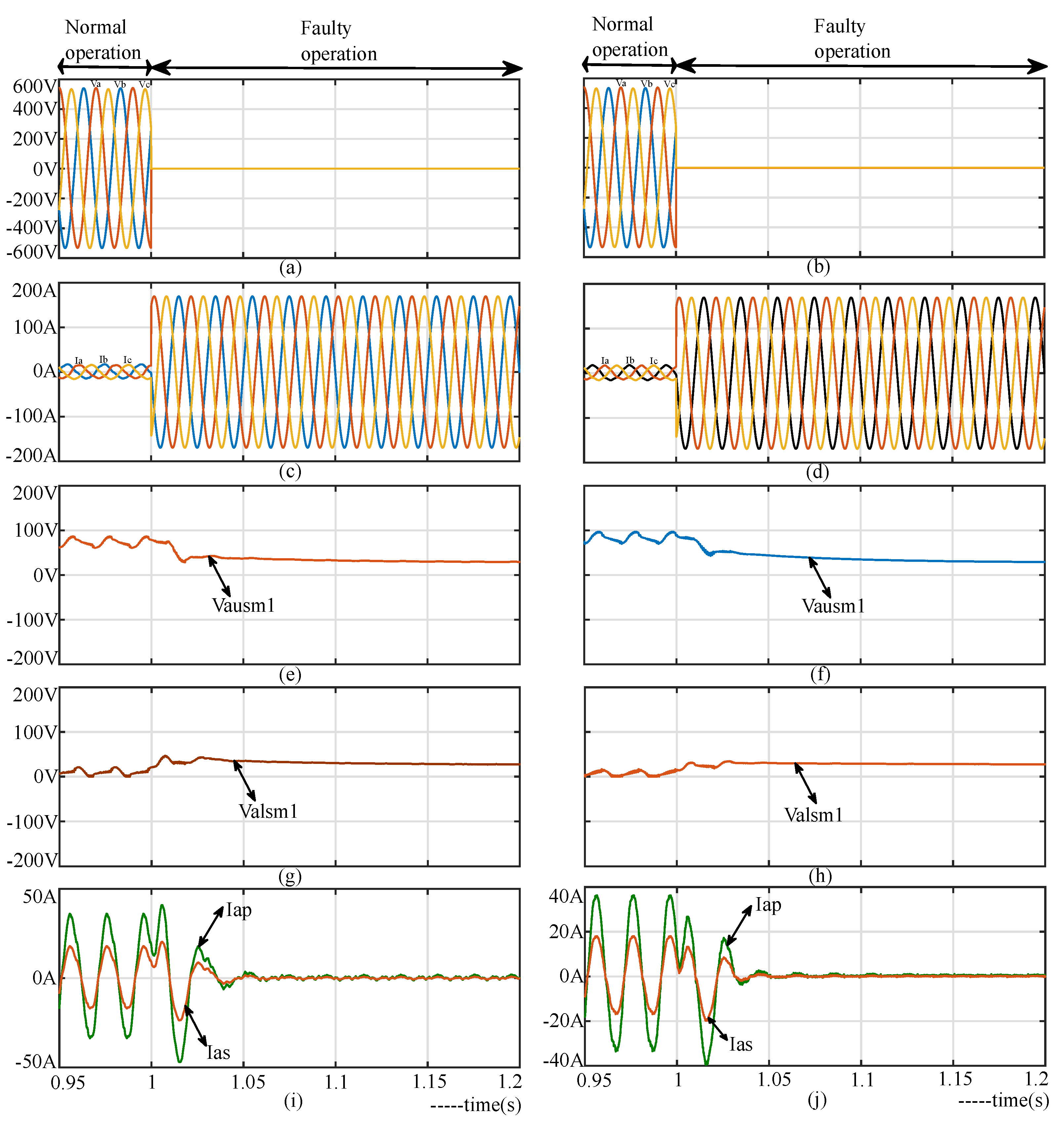

5. Results and Discussion

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Mei, J.; Xiao, B.; Shen, K.; Tolbert, L.M.; Zheng, J.Y. Modular multilevel inverter with new modulation method and its application to photovoltaic grid-connected generator. IEEE Trans. Power Electron. 2013, 28, 5063–5073. [Google Scholar] [CrossRef]

- Nademi, H.; Das, A.; Burgos, R.; Norum, L.E. A new circuit performance of modular multilevel inverter suitable for photovoltaic conversion plants. IEEE J. Emerg. Sel. Top. Power Electron. 2015, 4, 393–404. [Google Scholar] [CrossRef]

- Rojas, C.A.; Kouro, S.; Perez, M.A.; Echeverria, J. DC–DC MMC for HVDC grid interface of utility-scale photovoltaic conversion systems. IEEE Trans. Ind. Electron. 2017, 65, 352–362. [Google Scholar] [CrossRef]

- Wu, P.; Huang, W.; Tai, N. Novel grid connection interface for utility-scale PV power plants based on MMC. J. Eng. 2019, 2019, 2683–2686. [Google Scholar] [CrossRef]

- Bayat, H.; Yazdani, A. A power mismatch elimination strategy for an MMC-based photovoltaic system. IEEE Trans. Energy Convers. 2018, 33, 1519–1528. [Google Scholar] [CrossRef]

- Acharya, A.B.; Ricco, M.; Sera, D.; Teoderscu, R.; Norum, L.E. Performance analysis of medium-voltage grid integration of PV plant using modular multilevel converter. IEEE Trans. Energy Convers. 2019, 34, 1731–1740. [Google Scholar] [CrossRef]

- Basu, T.S.; Maiti, S. A hybrid modular multilevel converter for solar power integration. IEEE Trans. Ind. Appl. 2019, 55, 5166–5177. [Google Scholar] [CrossRef]

- Bayat, H.; Yazdani, A. A hybrid MMC-based photovoltaic and battery energy storage system. IEEE Power Energy Technol. Syst. J. 2019, 6, 32–40. [Google Scholar] [CrossRef]

- Verdugo, C.; Candela, J.I.; Blaabjerg, F.; Rodriguez, P. Three-phase isolated multi-modular converter in renewable energy distribution systems. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 8, 854–865. [Google Scholar] [CrossRef]

- Zhang, X.; Wang, M.; Zhao, T.; Mao, W.; Hu, Y.; Cao, R. Topological comparison and analysis of medium-voltage and high-power direct-linked PV inverter. CES Trans. Electr. Mach. Syst. 2019, 3, 327–334. [Google Scholar] [CrossRef]

- Solas, E.; Abad, G.; Barrena, J.A.; Aurtenetxea, S.; Carcar, A.; Zając, L. Modular multilevel converter with different submodule concepts—Part I: Capacitor voltage balancing method. IEEE Trans. Ind. Electron. 2012, 60, 4525–4535. [Google Scholar] [CrossRef]

- Solas, E.; Abad, G.; Barrena, J.A.; Aurtenetxea, S.; Carcar, A.; Zajac, L. Modular Multilevel Converter With Different Submodule Concepts—Part II: Experimental Validation and Comparison for HVDC Application. IEEE Trans. Ind. Electron. 2012, 60, 4536–4545. [Google Scholar] [CrossRef]

- Saad, H.; Dennetière, S.; Mahseredjian, J.; Delarue, P.; Guillaud, X.; Peralta, J.; Nguefeu, S. Modular multilevel converter models for electromagnetic transients. IEEE Trans. Power Deliv. 2013, 29, 1481–1489. [Google Scholar] [CrossRef]

- Dekka, A.; Wu, B.; Fuentes, R.L.; Perez, M.; Zargari, N.R. Evolution of topologies, modeling, control schemes, and applications of modular multilevel converters. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 1631–1656. [Google Scholar] [CrossRef]

- Jacobson, B.; Karlsson, P.; Asplund, G.; Harnefors, L.; Jonsson, T. VSC-HVDC Transmission with Cascaded Two-Level Converters. Proceeding of CIGRE SC B4 Session, Paris, France, 22 August 2010; pp. 1–8. [Google Scholar]

- Qin, J.; Saeedifard, M.; Rockhill, A.; Zhou, R. Hybrid design of modular multilevel converters for HVDC systems based on various submodule circuits. IEEE Trans. Power Deliv. 2014, 30, 385–394. [Google Scholar] [CrossRef]

- de Sousa, G.J.M.; Dias, A.D.S.; Alves, J.A.; Heldwein, M.L. June. In Modeling and control of a modular multilevel converter for medium voltage drives rectifier applications. In Proceedings of the 2015 IEEE 24th International Symposium on Industrial Electronics (ISIE), Buzios, Brazil, 3–5 June 2015; pp. 1080–1087. [Google Scholar]

- Xu, J.; Zhao, P.; Zhao, C. Reliability analysis and redundancy configuration of MMC with hybrid submodule topologies. IEEE Trans. Power Electron. 2015, 31, 2720–2729. [Google Scholar] [CrossRef]

- Perez, M.A.; Bernet, S.; Rodriguez, J.; Kouro, S.; Lizana, R. Circuit topologies, modeling, control schemes, and applications of modular multilevel converters. IEEE Trans. Power Electron. 2014, 30, 4–17. [Google Scholar] [CrossRef]

- Nami, A.; Liang, J.; Dijkhuizen, F.; Demetriades, G.D. Modular multilevel converters for HVDC applications: Review on converter cells and functionalities. IEEE Trans. Power Electron. 2014, 30, 18–36. [Google Scholar] [CrossRef]

- Debnath, S.; Qin, J.; Bahrani, B.; Saeedifard, M.; Barbosa, P. Operation, control, and applications of the modular multilevel converter: A review. IEEE Trans. Power Electron. 2014, 30, 37–53. [Google Scholar] [CrossRef]

- Soeiro, T.B.; Kolar, J.W. Novel 3-level hybrid neutral-point-clamped converter. In Proceedings of the IECON 2011-37th Annual Conference of the IEEE Industrial Electronics Society, Melbourne, VIC, Australia, 7–10 November 2011; pp. 4457–4462. [Google Scholar]

- Ilves, K.; Taffner, F.; Norrga, S.; Antonopoulos, A.; Harnefors, L.; Nee, H.P. A submodule implementation for parallel connection of capacitors in modular multilevel converters. IEEE Trans. Power Electron. 2014, 30, 3518–3527. [Google Scholar] [CrossRef]

- Yu, X.; Wei, Y.; Jiang, Q.; Xie, X.; Liu, Y.; Wang, K. A novel hybrid-arm bipolar MMC topology with DC fault ride-through capability. IEEE Trans. Power Deliv. 2016, 32, 1404–1413. [Google Scholar] [CrossRef]

- Mao, M.; Ding, Y.; Chang, L.; Hatziargyriou, N.D.; Chen, Q.; Tao, T.; Li, Y. Multi-objective power management for EV fleet with MMC-based integration into smart grid. IEEE Trans. Smart Grid 2017, 10, 1428–1439. [Google Scholar] [CrossRef]

- Zhang, J.; Zhao, C. The research of SM topology with DC fault tolerance in MMC-HVDC. IEEE Trans. Power Deliv. 2015, 30, 1561–1568. [Google Scholar] [CrossRef]

- Nami, A.; Wang, L.; Dijkhuizen, F.; Shukla, A. September. In Five level cross connected cell for cascaded converters. In Proceedings of the 2013 15th European conference on power electronics and applications (EPE), Lille, France, 2–6 September 2013; pp. 1–9. [Google Scholar]

- Abd Razak, A.B. Modulation Strategy for New Asymmetrical Multilevel Inverter Topology Using Nearest Dc Level. Ph.D. Thesis, Universiti Teknologi Malaysia, Skudai, Malaysia, 2019. [Google Scholar]

- Chaudhuri, T. Cross connected multilevel voltage source inverter topologies for medium voltage applications. Ph.D. Dissertation, EPFL, Lausanne, Switzerland, 2008. [Google Scholar]

| Sub-Module (SM) | NVL | Voltage Level | NS | MNSC | MBV | Bipolar | DC-Fault Handling |

|---|---|---|---|---|---|---|---|

| Two-Level SMs | |||||||

| HBSM | 2 | 0, +VC1 | 2 | 1 | VC1 | No | No |

| Unipolar SM | 2 | 0, +VC1 | 3 | 1 | VC1 | No | Yes |

| Unidirectional | 2 | 0, +VC1 | 1 | 1 | VC1 | No | No |

| CSSM | 2 | 0, +VC1 | 3 | 2 | VC1 | No | Yes |

| Three-Level SMs | |||||||

| FBSM | 3 | 0, +VC1, −VC1 | 4 | 2 | VC1 | Yes | Yes |

| TLFCSM | 3 | 0, +VC2, +(VC1 + VC2) | 4 | 2 | VC1 + VC2 | No | No |

| TLNPC-1 | 3 | 0, +VC2, +(VC1 + VC2) | 4 | 2 | VC1 + VC2 | No | No |

| TLNPC-2 | 3 | 0, +VC2, +(VC1 + VC2) | 6 | 2 | VC1 + VC2 | No | No |

| TLNPC-3 | 3 | 0, +VC2, +(VC1 + VC2) | 4 | 2 | VC1 + VC2 | No | No |

| DSM | 3 | 0, +VC2, +(VC1 + VC2) | 8 | 4 | VC1 + VC2 | No | Yes |

| TLCCSM | 3 | 0, +VC2, +(VC1 + VC2) | 5 | 3 | VC1 + VC2 | No | Yes |

| DBSM | 3 | 0, +VC1, −VC2 | 2 | 1 | VC1 | Yes | Yes |

| IHSM | 3 | 0, +VC1, +(VC1 + VC2) | 5 | 3 | VC1 + VC2 | No | Yes |

| Four-Level SMs | |||||||

| CDSM-1 | 4 | 0, +VC1, +(VC1 + VC2) | 5 | 3 | VC1 + VC2 | Yes | Yes |

| CDSM-2 | 4 | 0, +VC2, +(VC1 + VC2) | 7 | 3 | VC1 + VC2 | Yes | Yes |

| Asymmetrical | 4 | 0, +VC2, +(VC1 + VC2) | 4 | 2 | VC1 + VC2 | Yes | Yes |

| Mixed SM | 4 | 0, +VC2, +(VC1 + VC2) | 6 | 3 | VC1 + VC2 | Yes | Yes |

| SDSM | 4 | 0, +VC2, +(VC1 + VC2) | 5 | 3 | VC1 + VC2 | Yes | Yes |

| Five-Level SMs | |||||||

| FLCCSM | 5 | 0, +VC1, +VC2, ±(VC1 + VC2) | 6 | 3 | VC1 + VC2 | Yes | Yes |

| CCSM | 5 | 0, +VC1, +VC2, ±(VC1 + VC2) | 8 | 4 | VC1 + VC2 | Yes | Yes |

| PCSM | 5 | 0, +VC1, +VC2, ±(VC1 + VC2) | 8 | 4 | VC1 + VC2 | Yes | Yes |

| Number of Cells in Each Arm | 3 |

| Ac line inductor | 3 µH |

| Carrier frequency | 1 KHz |

| Transformer resistance | 74 m-ohm |

| Transformer inductor | 3.48 mH |

| Cell capacitance | 1000 µF |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mikkili, S.; Krishna, R.V.; Bonthagorla, P.K.; Senjyu, T. Performance Analysis of Modular Multilevel Converter with NPC Sub-Modules in Photovoltaic Grid-Integration. Appl. Sci. 2022, 12, 1219. https://doi.org/10.3390/app12031219

Mikkili S, Krishna RV, Bonthagorla PK, Senjyu T. Performance Analysis of Modular Multilevel Converter with NPC Sub-Modules in Photovoltaic Grid-Integration. Applied Sciences. 2022; 12(3):1219. https://doi.org/10.3390/app12031219

Chicago/Turabian StyleMikkili, Suresh, Raghu Vamsi Krishna, Praveen Kumar Bonthagorla, and Tomonobu Senjyu. 2022. "Performance Analysis of Modular Multilevel Converter with NPC Sub-Modules in Photovoltaic Grid-Integration" Applied Sciences 12, no. 3: 1219. https://doi.org/10.3390/app12031219

APA StyleMikkili, S., Krishna, R. V., Bonthagorla, P. K., & Senjyu, T. (2022). Performance Analysis of Modular Multilevel Converter with NPC Sub-Modules in Photovoltaic Grid-Integration. Applied Sciences, 12(3), 1219. https://doi.org/10.3390/app12031219