A Secondary Reconfigurable Inverter and Its Control Strategy

Abstract

Featured Application

Abstract

1. Introduction

2. Materials and Methods

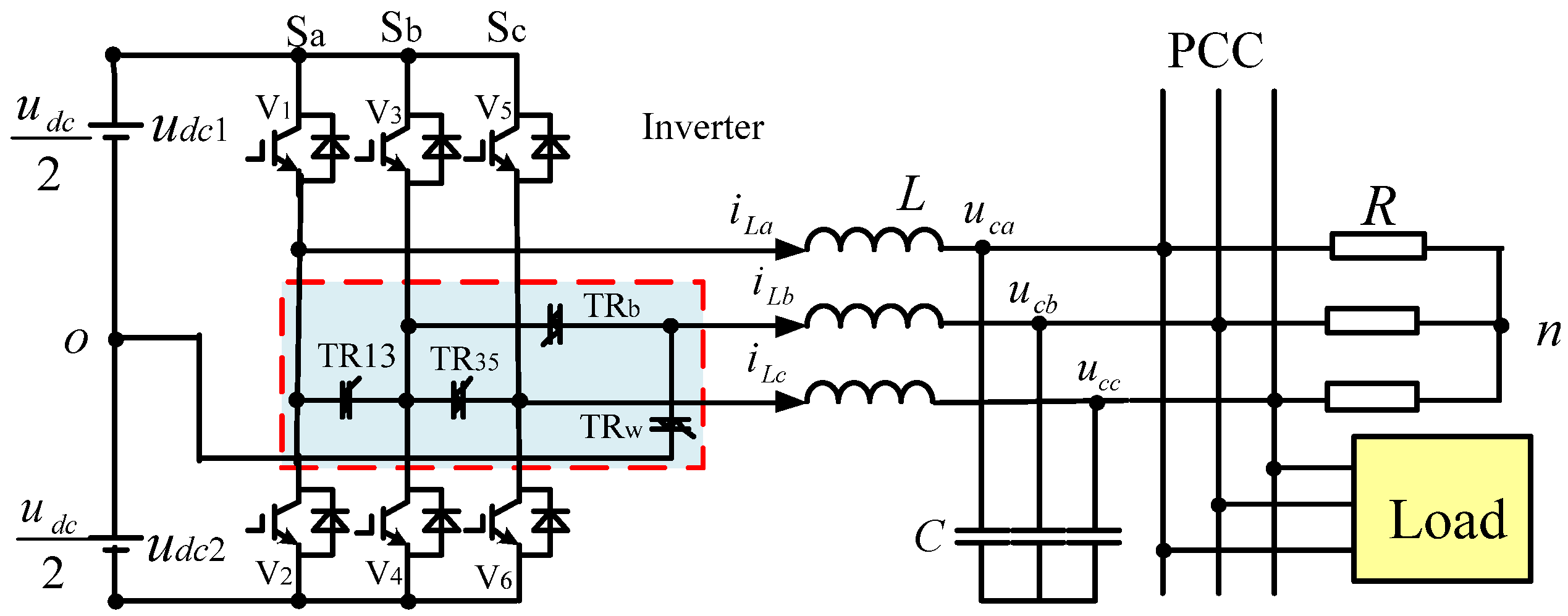

2.1. The Topology Structure of the Secondary Reconfigurable Inverter

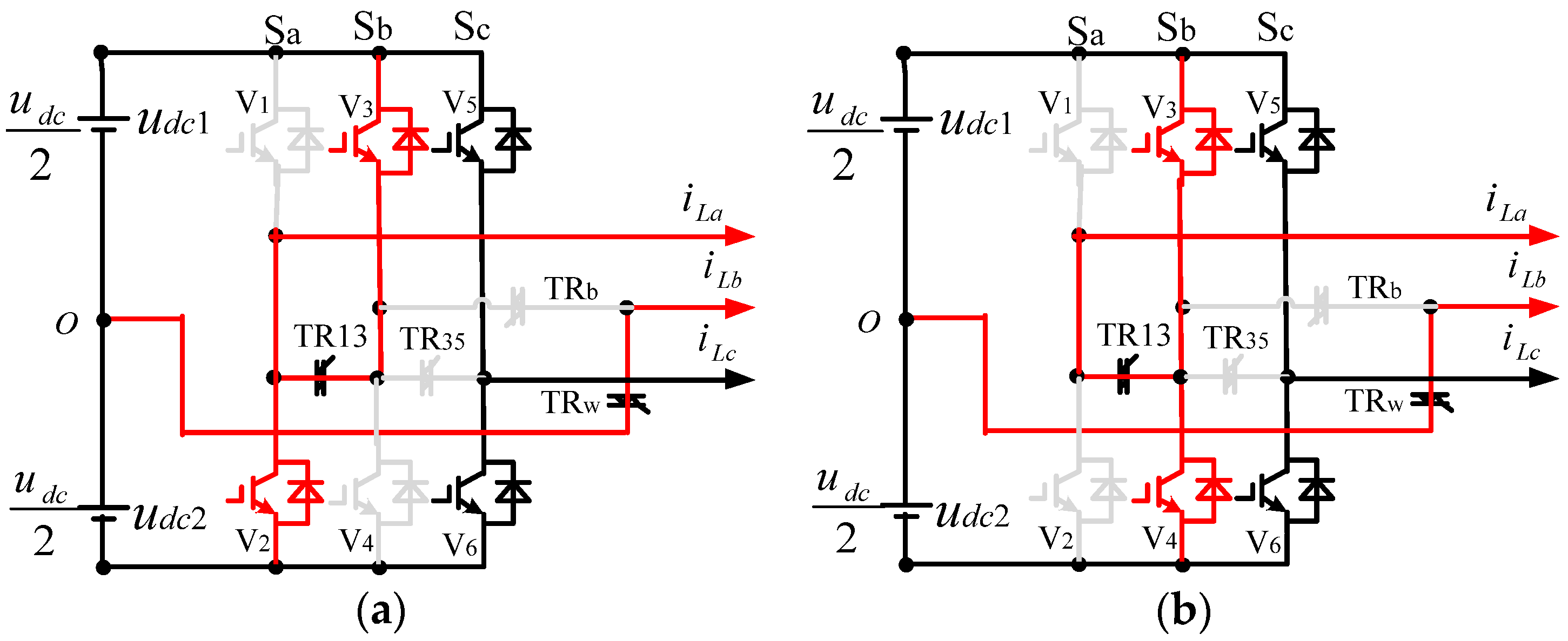

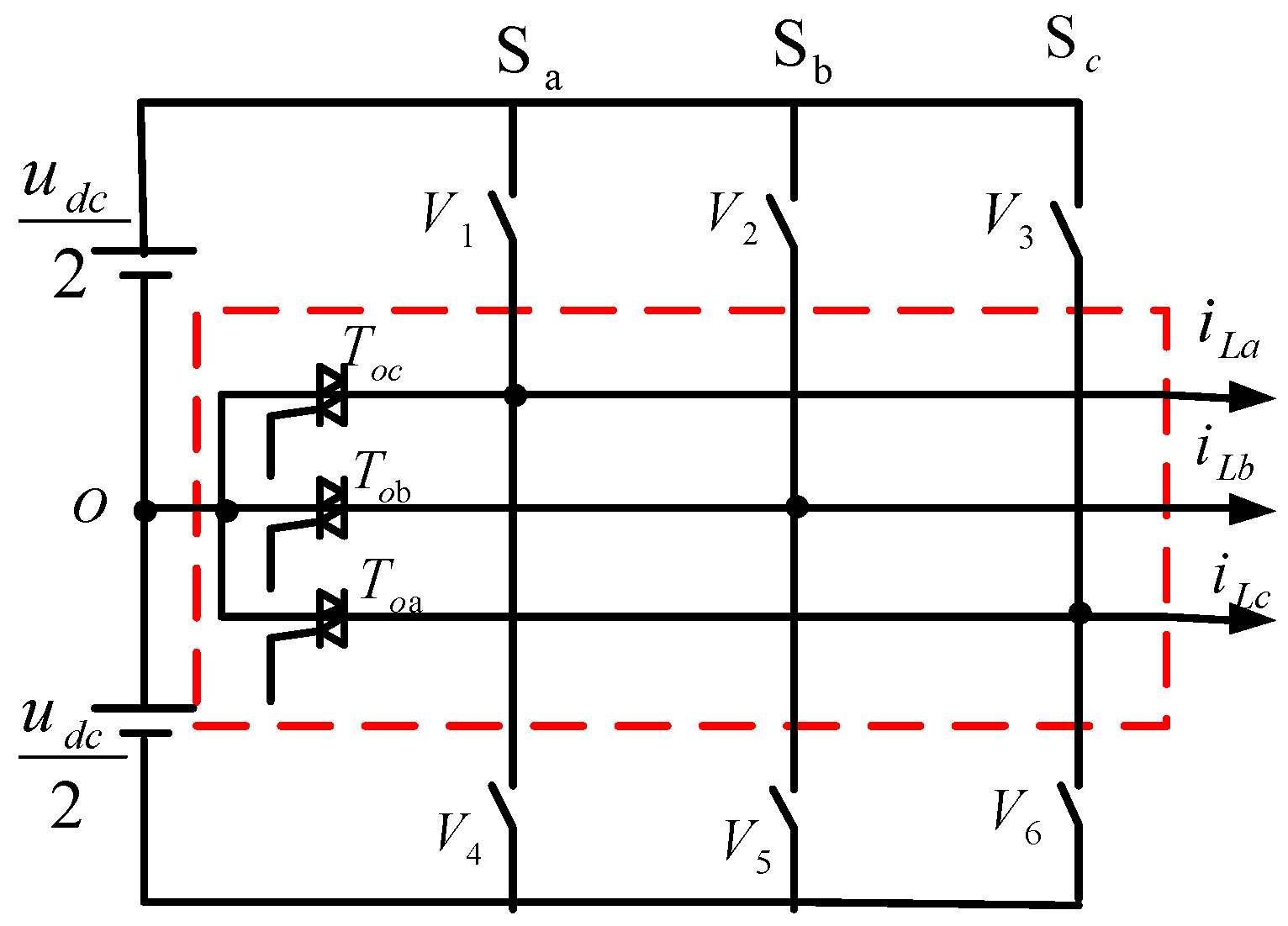

2.2. Analysis of the Fault Tolerant Inverter Operating Principle

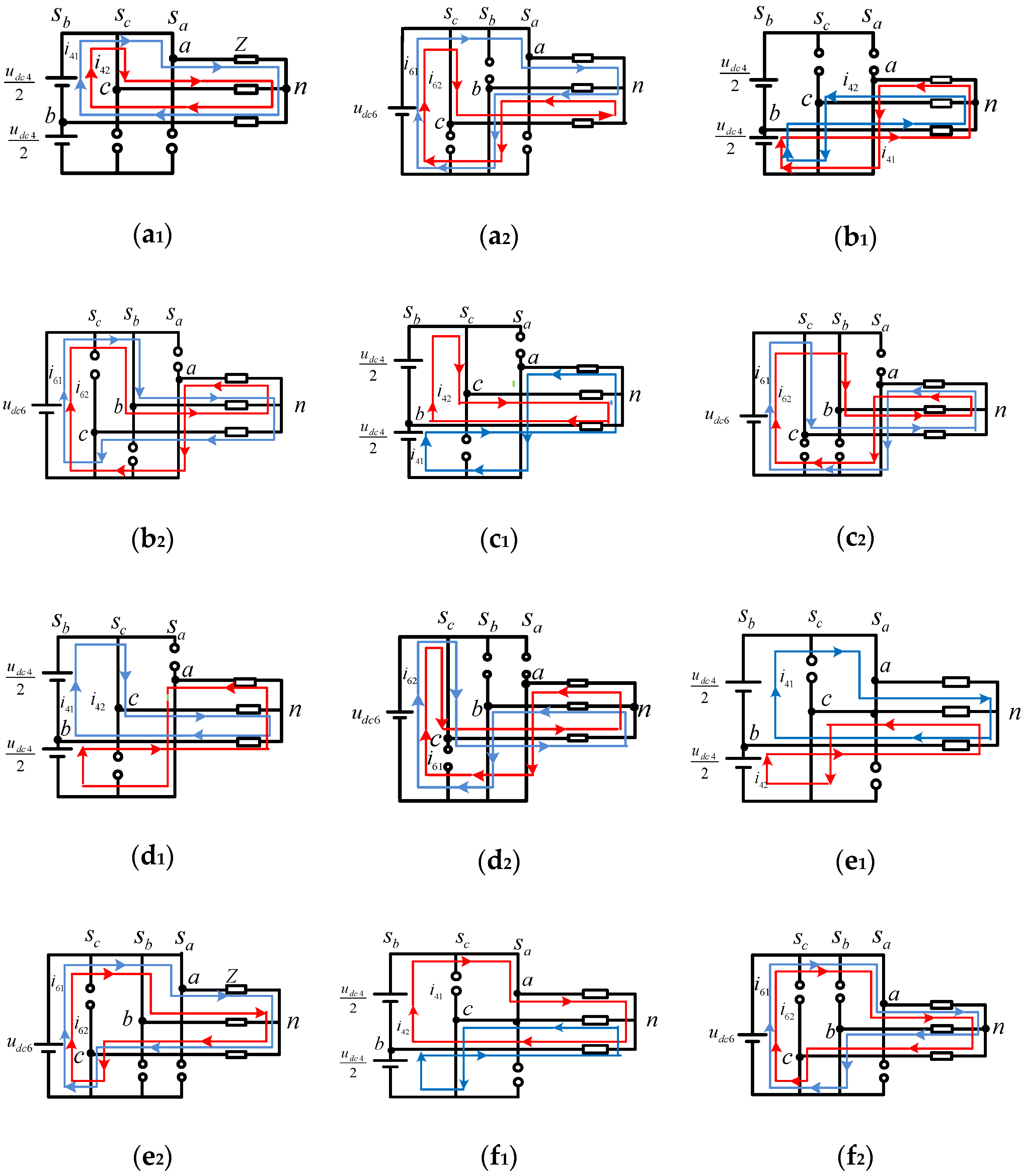

2.2.1. Analysis of the Switching Mode

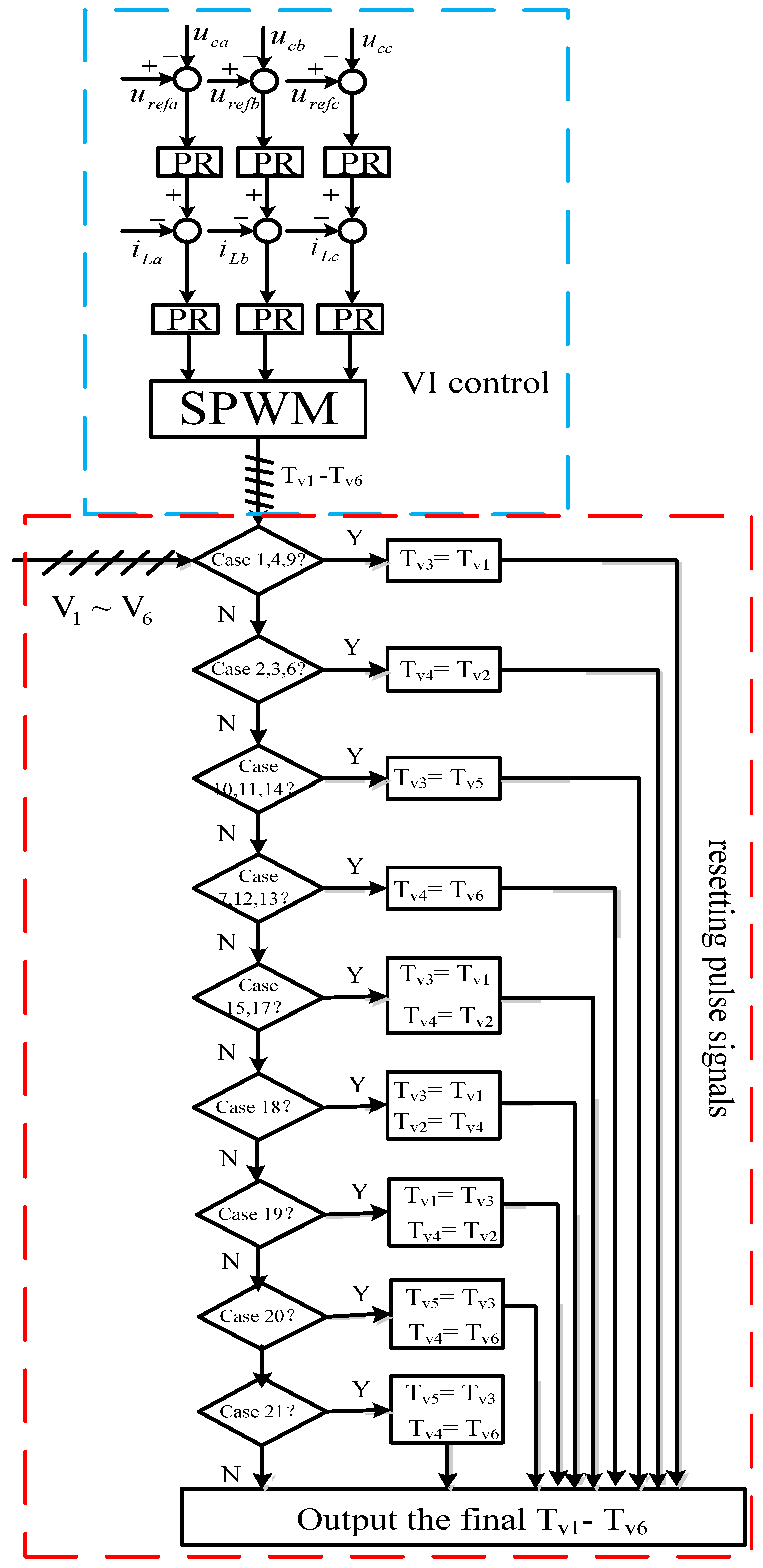

2.2.2. The Control Strategy for the Reconfigurable Inverter

3. Results and Discussion

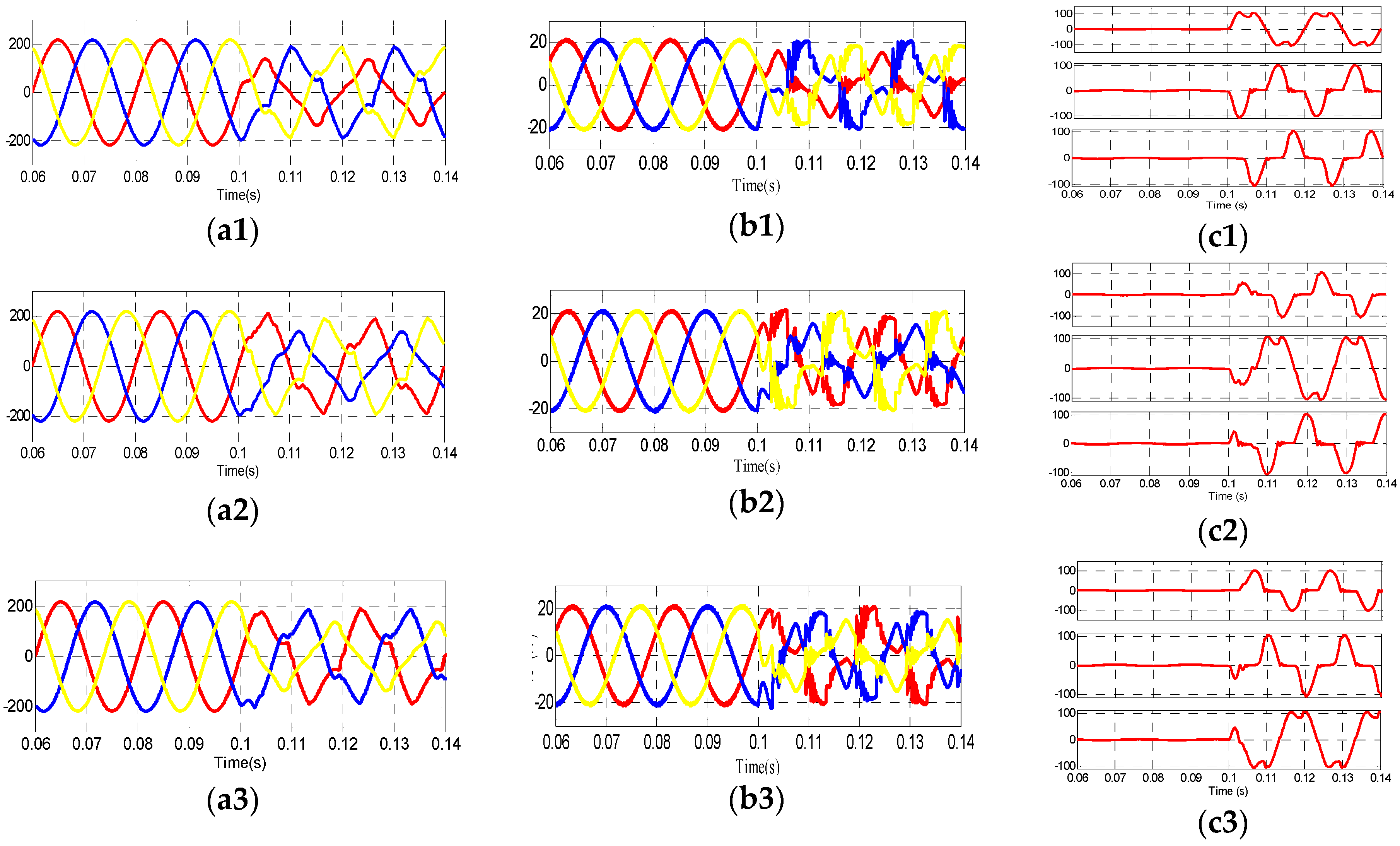

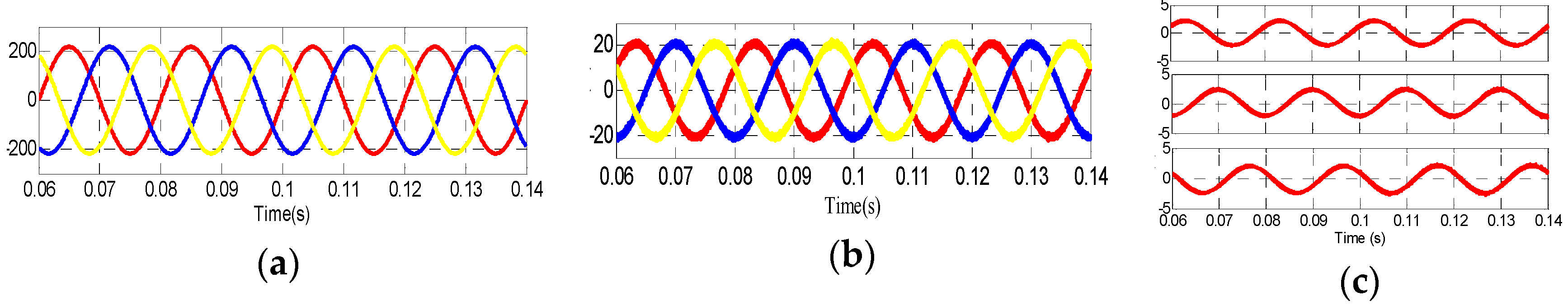

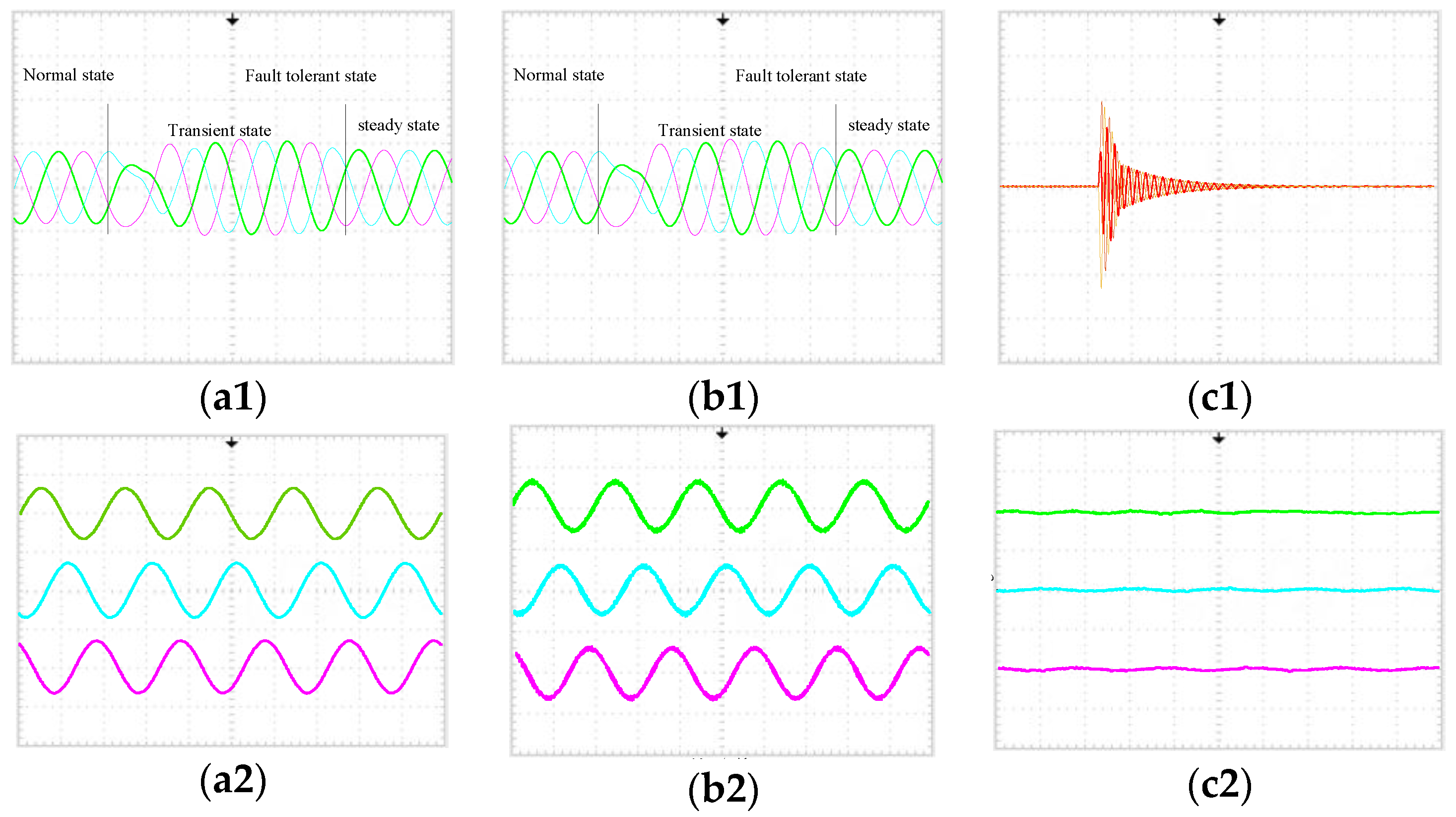

3.1. Simulation Results and Discussion

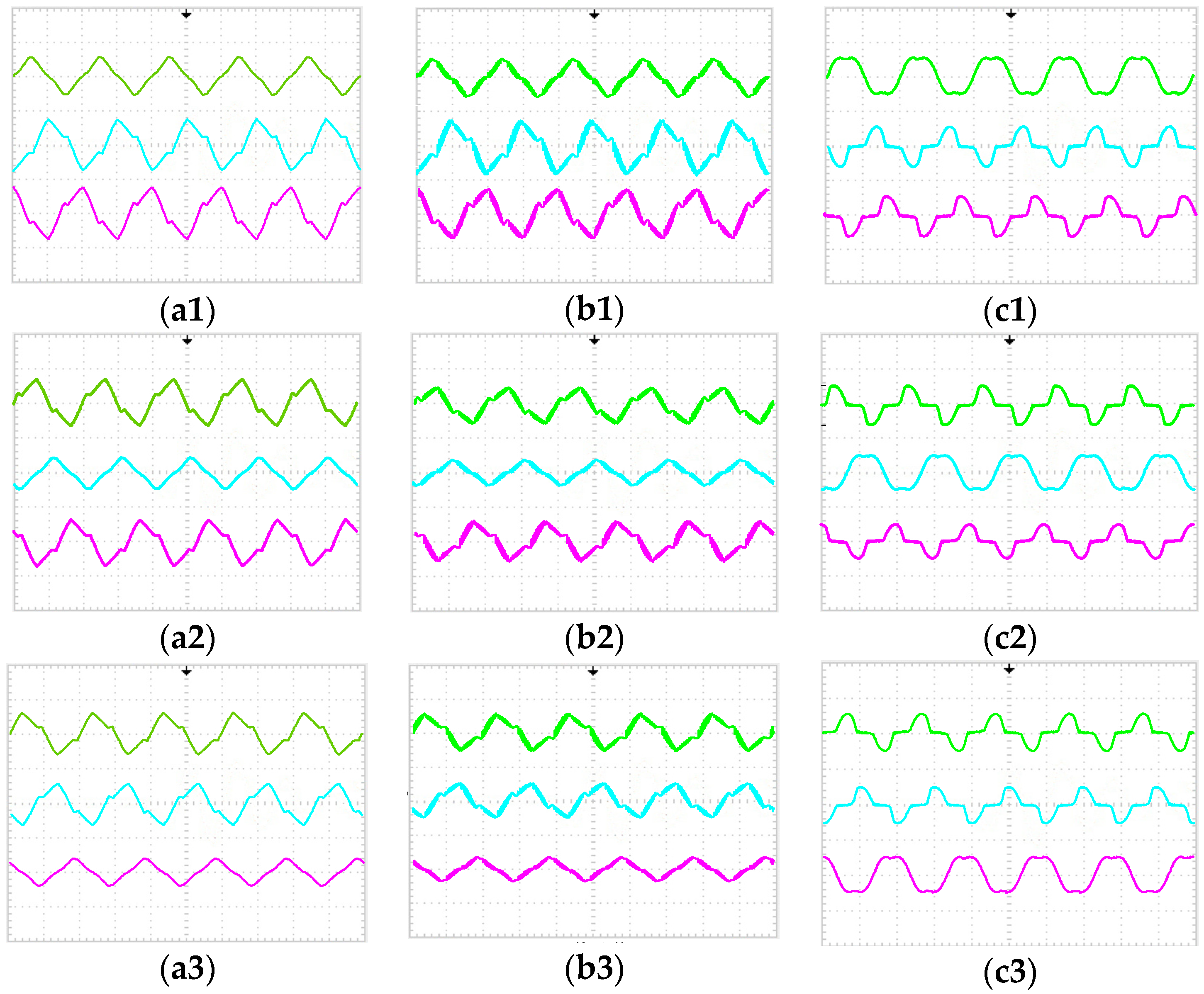

3.2. Experimental Results and Discussion

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Abronzini, U.; Attaianese, C.; D’Arpino, M.; Di Monaco, M.; Tomasso, G. Steady-State Dead-Time Compensation in VSI. IEEE Trans. Ind. Electron. 2016, 63, 5858–5866. [Google Scholar] [CrossRef]

- Mehdi, F.F.; Alireza, R.; Mohsen, G. Stability Analysis and Decentralized Control of Inverter-Based AC Microgrid. Prot. Control Mod. Power Syst. 2019, 4, 65–86. [Google Scholar]

- Ballestín-Fuertes, J.; Muñoz-Cruzado-Alba, J.; Sanz-Osorio, J.F.; Hernández-Callejo, L.; Alonso-Gómez, V.; Morales-Aragones, J.I.; Gallardo-Saavedra, S.; Martínez-Sacristan, O.; Moretón-Fernández, Á. Novel Utility-Scale Photovoltaic Plant Electroluminescence Maintenance Technique by Means of Bidirectional Power Inverter Controller. Appl. Sci. 2020, 10, 3084. [Google Scholar] [CrossRef]

- Soukaina, E.D.; Loubna, L.; Mustapha, A.L. Sliding Mode Approach Applied to Sensorless Direct Torque Control of Cage Asynchronous Motor Via Multi-Level Inverter. Prot. Control Mod. Power Syst. 2020, 5, 166–175. [Google Scholar]

- Zhang, W.; Xu, D.; Enjeti, P.; Li, H.; Hawke, J.T.; Krishnamoorthy, H.S. Survey on Fault-Tolerant Techniques for Power Electronic Converters. IEEE Trans. Power Electron. 2014, 29, 6319–6331. [Google Scholar] [CrossRef]

- Longchang, W.; Houlei, G.; Guibin, Z. Modeling Methodology and Fault Simulation of Distribution Networks Integrated with Inverter-Based DG. Prot. Control Mod. Power Syst. 2017, 2, 370–378. [Google Scholar]

- Chen, J.; Shang, Y.; Chen, A.; Xing, X. Fault-Tolerant Control Strategies for T-Type Three-Level Inverters Considering Neutral-Point Voltage Oscillations. IEEE Trans. Ind. Electron. 2019, 66, 2837–2846. [Google Scholar] [CrossRef]

- Lu, B.; Sharma, S. A Literature Review of IGBT Fault Diagnostic and Protection Methods for Power Inverters. IEEE Trans. Ind. Appl. 2009, 45, 1770–1777. [Google Scholar] [CrossRef]

- Karimi, S.; Gaillard, A.; Poure, P.; Saadate, S. FPGA-Based Real-Time Power Converter Failure Diagnosis for Wind Energy Conversion Systems. IEEE Trans. Ind. Electron. 2008, 55, 4299–4308. [Google Scholar] [CrossRef]

- Naidu, M.; Gopalakrishnan, S.; Nehl, T. Fault-Tolerant Permanent Magnet Motor Drive Topologies for Automotive X-By-Wire Systems. IEEE Trans. Ind. Appl. 2010, 46, 841–848. [Google Scholar] [CrossRef]

- Errabelli, R.R.; Mutschler, P. Fault-Tolerant Voltage Source Inverter for Permanent Magnet Drives. IEEE Trans. Power Electron. 2011, 27, 500–508. [Google Scholar] [CrossRef]

- De Lillo, L.; Empringham, L.; Wheeler, P.; Khwan-On, S.; Gerada, C.; Othman, M.; Huang, X. Multiphase Power Converter Drive for Fault-Tolerant Machine Development in Aerospace Applications. IEEE Trans. Ind. Electron. 2009, 57, 575–583. [Google Scholar] [CrossRef]

- Liu, G.; Xu, Z.; Xue, Y.; Tang, G. Optimized Control Strategy Based on Dynamic Redundancy for the Modular Multilevel Converter. IEEE Trans. Power Electron. 2014, 30, 339–348. [Google Scholar] [CrossRef]

- Blaabjerg, F.; Neacsu, D.; Pedersen, J. Adaptive SVM to compensate DC-link voltage ripple for four-switch three-phase voltage-source inverters. IEEE Trans. Power Electron. 1999, 14, 743–752. [Google Scholar] [CrossRef]

- Hu, S.; Liu, G.; Jin, N.; Guo, L. Constant-Frequency Model Predictive Direct Power Control for Fault-Tolerant Bidirectional Voltage-Source Converter with Balanced Capacitor Voltage. Energies 2018, 11, 2692. [Google Scholar] [CrossRef]

- Zhu, C.; Zeng, Z.; Zhao, R. Comprehensive Analysis and Reduction of Torque Ripples in Three-phase Four-switch Inverter-fed PMSM Drives Using Space Vector Pulse-width Modulation. IEEE Trans. Power Electron. 2016, 32, 1. [Google Scholar] [CrossRef]

- Li, W.; Xuan, S.; Gao, Q.; Luo, L. Investigation of a Four-Switch Four-Leg Inverter: Modulation, Control, and Application to an IPMSM Drive. IEEE Trans. Power Electron. 2018, 34, 5655–5666. [Google Scholar] [CrossRef]

- Zeng, Z.; Zheng, W.; Zhao, R.; Zhu, C.; Yuan, Q. Modeling, Modulation and Control of the Three-Phase Four-Switch PWM Rectifier under Balanced Voltage. IEEE Trans. Power Electron. 2015, 31, 1. [Google Scholar] [CrossRef]

- Zeng, Z.; Zheng, W.; Zhao, R. Space-Vector-Based Hybrid PWM Strategy for Reduced DC-Link Capacitor Current Stress in the Post-Fault Grid-Connected Three-Phase Rectifier. IEEE Trans. Ind. Electron. 2016, 63, 1. [Google Scholar] [CrossRef]

- Zeng, Z.; Zheng, W.; Zhao, R.; Zhu, C.; Yuan, Q. The Comprehensive Design and Optimization of the Post-Fault Grid-Connected Three-Phase PWM Rectifier. IEEE Trans. Ind. Electron. 2015, 63, 1629–1642. [Google Scholar] [CrossRef]

- Xia, C.; Li, Z.; Shi, T. A Control Strategy for Four-Switch Three-Phase Brushless DC Motor Using Single Current Sensor. IEEE Trans. Ind. Electron. 2009, 56, 2058–2066. [Google Scholar] [CrossRef]

- Klima, J. Analytical Investigation of an Induction Motor Fed from Four-Switch VSI with a New Space Vector Modulation Strategy. IEEE Trans. Energy Convers. 2006, 21, 832–838. [Google Scholar] [CrossRef]

- Kim, J.; Hong, J.; Nam, K. A Current Distortion Compensation Scheme for Four-Switch Inverters. IEEE Trans. Power Electron. 2009, 24, 1032–1040. [Google Scholar] [CrossRef]

- Wang, R.; Zhao, J.; Liu, Y. A Comprehensive Investigation of Four-Switch Three-Phase Voltage Source Inverter Based on Double Fourier Integral Analysis. IEEE Trans. Power Electron. 2011, 26, 2774–2787. [Google Scholar] [CrossRef]

- Correa, M.B.D.R.; Jacobina, C.B.; Da Silva, E.R.C.; Lima, A.M.N. A General PWM Strategy for Four-Switch Three-Phase Inverters. IEEE Trans. Power Electron. 2006, 21, 1618–1627. [Google Scholar] [CrossRef]

- Xia, C.; Wu, D.; Shi, T.; Chen, W. A Current Control Scheme of Brushless DC Motors Driven by Four-Switch Three-Phase Inverters. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 547–558. [Google Scholar] [CrossRef]

- Zaky, M.S.; Metwaly, M.K. A Performance Investigation of a Four-Switch Three-Phase Inverter-Fed IM Drives at Low Speeds Using Fuzzy Logic and PI Controllers. IEEE Trans. Power Electron. 2017, 32, 3741–3753. [Google Scholar] [CrossRef]

- Dasgupta, S.; Mohan, S.; Sahoo, S.K.; Panda, S.K. Application of Four-Switch-Based Three-Phase Grid-Connected Inverter to Connect Renewable Energy Source to a Generalized Unbalanced Microgrid System. IEEE Trans. Ind. Electron. 2012, 60, 1204–1215. [Google Scholar] [CrossRef]

- Tsang, K.-M.; Chan, W.-L. Single DC source three-phase multilevel inverter using reduced number of switches. IET Power Electron. 2014, 7, 775–783. [Google Scholar] [CrossRef]

- Jin, N.; Hu, S.; Gan, C.; Ling, Z. Finite States Model Predictive Control for Fault-Tolerant Operation of a Three-Phase Bidirectional AC/DC Converter Under Unbalanced Grid Voltages. IEEE Trans. Ind. Electron. 2018, 65, 819–829. [Google Scholar] [CrossRef]

- Ceballos, S.; Pou, J.; Zaragoza, J.; Robles, E.; Villate, J.L.; Martin, J.L. Fault-Tolerant Neutral-Point-Clamped Converter Solutions Based on Including a Fourth Resonant Leg. IEEE Trans. Ind. Electron. 2010, 58, 2293–2303. [Google Scholar] [CrossRef]

- Ceballos, S.; Pou, J.; Robles, E.; Gabiola, I.; Zaragoza, J.; Villate, J.; Boroyevich, D. Three-Level Converter Topologies With Switch Breakdown Fault-Tolerance Capability. IEEE Trans. Ind. Electron. 2008, 55, 982–995. [Google Scholar] [CrossRef]

- Correa, P.; Pacas, M.; Rodríguez, J. Modulation Strategies for Fault-Tolerant Operation of H-Bridge Multilevel Inverters. 2006 IEEE Int. Symp. Ind. Electron. 2006, 2, 1589–1594. [Google Scholar] [CrossRef]

- Liu, Y.; Li, D.; Jin, Y.; Wang, Q.; Song, W. Research on Unbalance Fault-Tolerant Control Strategy of Modular Multilevel Photovoltaic Grid-Connected Inverter. Energies 2018, 11, 1368. [Google Scholar] [CrossRef]

- Choi, U.-M.; Lee, K.-B.; Blaabjerg, F. Diagnosis and Tolerant Strategy of an Open-Switch Fault for T-Type Three-Level Inverter Systems. IEEE Trans. Ind. Appl. 2013, 50, 495–508. [Google Scholar] [CrossRef]

- Choi, U.-M.; Blaabjerg, F.; Lee, K.-B. Reliability Improvement of a T-Type Three-Level Inverter with Fault-Tolerant Control Strategy. IEEE Trans. Power Electron. 2014, 30, 2660–2673. [Google Scholar] [CrossRef]

- Zhou, D.; Li, Y.; Zhao, J.; Wu, F.; Luo, H. An Embedded Closed-Loop Fault-Tolerant Control Scheme for Nonredundant VSI-Fed Induction Motor Drives. IEEE Trans. Power Electron. 2016, 32, 3731–3740. [Google Scholar] [CrossRef]

- Zhang, W.; Xu, D.; Wang, H. Fault Analysis and Fault-Tolerant Design for Parallel Redundant Inverter Systems in Case of IGBT Short-Circuit Failures. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 2031–2041. [Google Scholar] [CrossRef]

| Case | First Fault | On | Reconfigured Phases | Second Fault | Reconfigured Phases | Switch Pulse Resetting |

|---|---|---|---|---|---|---|

| 0 | / | TRb | / | / | / | / |

| 1 | V1 | TRw and TR13 | Sa (V3, V2) Sb (C1, C2) | / | / | Tv3 = Tv1 |

| 2 | V1 | TRw and TR13 | / | V2 | Sa (V3, V4) Sb (C1, C2) | Tv4 = Tv2 |

| 3 | V2 | TRw and TR13 | Sa (V1, V4) Sb (C1, C2) | / | / | Tv4 = Tv2 |

| 4 | V2 | TRw and TR13 | / | V1 | Sa (V3, V4) Sb (C1, C2) | Tv3 = Tv1 |

| 5 | V3 | TRw | Sb (C1, C2) | / | / | / |

| 6 | V3 | TRw and TR13 | V2 | Sa (V1, V4) Sb (C1, C2) | Tv4 = Tv2 | |

| 7 | V3 | TRw and TR35 | / | V6 | Sc (V5, V4) Sb (C1, C2) | Tv4 = Tv6 |

| 8 | V4 | TRw | Sb (C1, C2) | / | / | / |

| 9 | V4 | TRw and TR13 | V1 | Sa (V3, V2) Sb (C1, C2) | Tv3 = Tv1 | |

| 10 | V4 | TRw and TR35 | V5 | Sc (V3, V6) Sb (C1, C2) | Tv3 = Tv5 | |

| 11 | V5 | TRw and TR35 | Sc (V3, V6) Sb (C1, C2) | / | / | Tv3 = Tv5 |

| 12 | V5 | TRw and TR35 | V4 | Sc (V3, V6) Sb (C1, C2) | Tv6 = Tv4 | |

| 13 | V6 | TRw and TR35 | Sc (V5, V4) Sb (C1, C2) | / | Tv4 = Tv6 | |

| 14 | V6 | TRw and TR35 | V3 | Sc (V5, V4) Sb (C1, C2) | Tv5 = Tv3 | |

| 15 | V1 and V2 | TRw and TR13 | Sa (V3, V4) Sb (C1, C2) | / | / | Tv3 = Tv1,Tv4 = Tv2 |

| 16 | V3 and V4 | TRw | Sb (C1, C2) | / | / | |

| 17 | V5 and V6 | TRw and TR35 | Sc (V3, V4) Sb (C1, C2) | / | / | Tv3 = Tv1,Tv4 = Tv2 |

| 18 | V1 and V4 | TRw and TR13 | Sa (V3, V2) Sb (C1, C2) | / | / | Tv3 = Tv1,Tv2 = Tv4 |

| 19 | V2 and V3 | TRw and TR13 | Sa (V1, V4) Sb (C1, C2) | / | / | Tv1 = Tv3,Tv4 = Tv2 |

| 20 | V3 and V6 | TRw and TR35 | Sc (V5, V4) Sb (C1, C2) | / | / | Tv5 = Tv3,Tv4 = Tv6 |

| 21 | V4 and V5 | TRw and TR35 | Sc (V3, V6) Sb (C1, C2) | / | / | Tv3 = Tv5,Tv6 = Tv4 |

| Case | Fault | On | Reconfigured Phases |

|---|---|---|---|

| 0 | / | / | / |

| 1 | V1 | Toc | Sa (C1, C2) |

| 2 | V4 | Toc | Sa (C1, C2) |

| 3 | V2 | Tob | Sb (C1, C2) |

| 4 | V5 | Tob | Sb (C1, C2) |

| 5 | V3 | Toa | Sc (C1, C2) |

| 6 | V6 | Toa | Sc (C1, C2) |

| 7 | V1 and V4 | Toc | Sa (C1, C2) |

| 8 | V2 and V5 | Tob | Sb (C1, C2) |

| 9 | V3 and V6 | Toa | Sc (C1, C2) |

| Main Parameters | Value |

|---|---|

| Reference voltage amplitude Um\V | 220 |

| Reference voltage frequency f\Hz | 50 |

| DC side voltage \V | 400/800 |

| IGBT switch frequency\kHz | 10 |

| Output side filter inductance L0\mH | 1.2 |

| Output side filter capacitance C0\µF | 4000 |

| Load resistance value RL\Ω | 12 |

| Load inductance value LL\mH | 1.4 |

| Kp of PR | 0.6 |

| KR of PR | 500 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, Y.; Xiang, P.; Chen, Y. A Secondary Reconfigurable Inverter and Its Control Strategy. Appl. Sci. 2020, 10, 7021. https://doi.org/10.3390/app10207021

Li Y, Xiang P, Chen Y. A Secondary Reconfigurable Inverter and Its Control Strategy. Applied Sciences. 2020; 10(20):7021. https://doi.org/10.3390/app10207021

Chicago/Turabian StyleLi, Yan, Peng Xiang, and Yandong Chen. 2020. "A Secondary Reconfigurable Inverter and Its Control Strategy" Applied Sciences 10, no. 20: 7021. https://doi.org/10.3390/app10207021

APA StyleLi, Y., Xiang, P., & Chen, Y. (2020). A Secondary Reconfigurable Inverter and Its Control Strategy. Applied Sciences, 10(20), 7021. https://doi.org/10.3390/app10207021