Artificial Intelligence: An Energy Efficiency Tool for Enhanced High performance computing

Abstract

1. Introduction

2. HPC Overview

2.1. What is HPC

2.2. Why HPC Is Important to Modern Communication

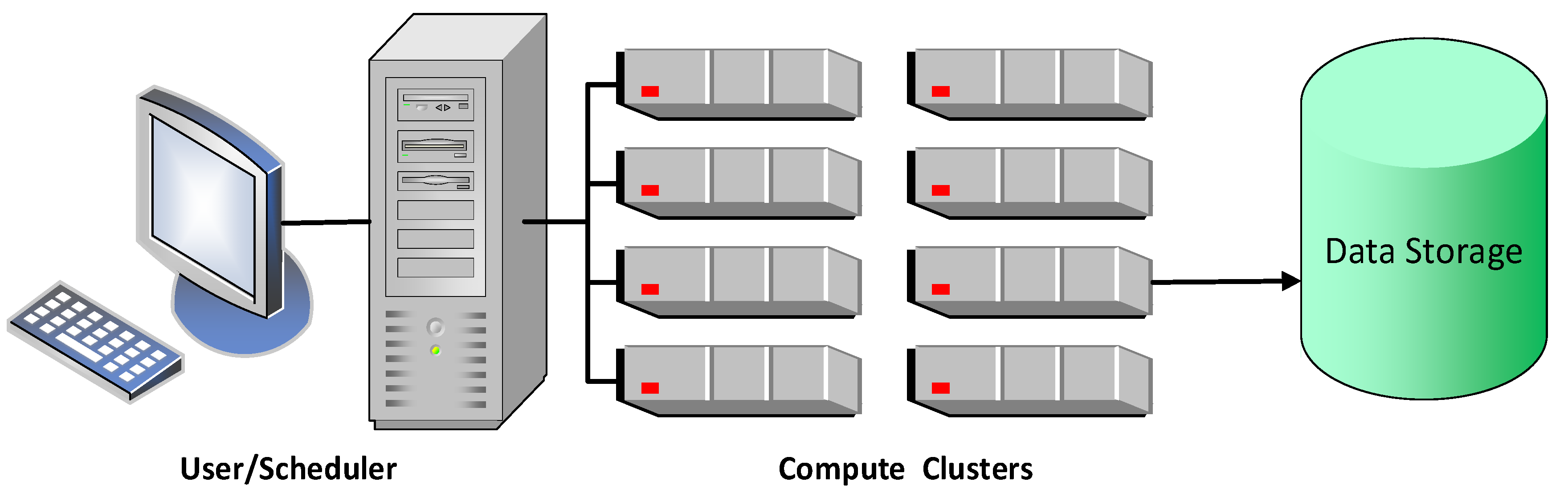

2.3. What Are the Operational Modalities of HPC

3. Comparative Studies

4. The Need for HPC Energy Efficiency in the Evolving 5G Networks

4.1. Discovering IoT Networks Needs in HPC

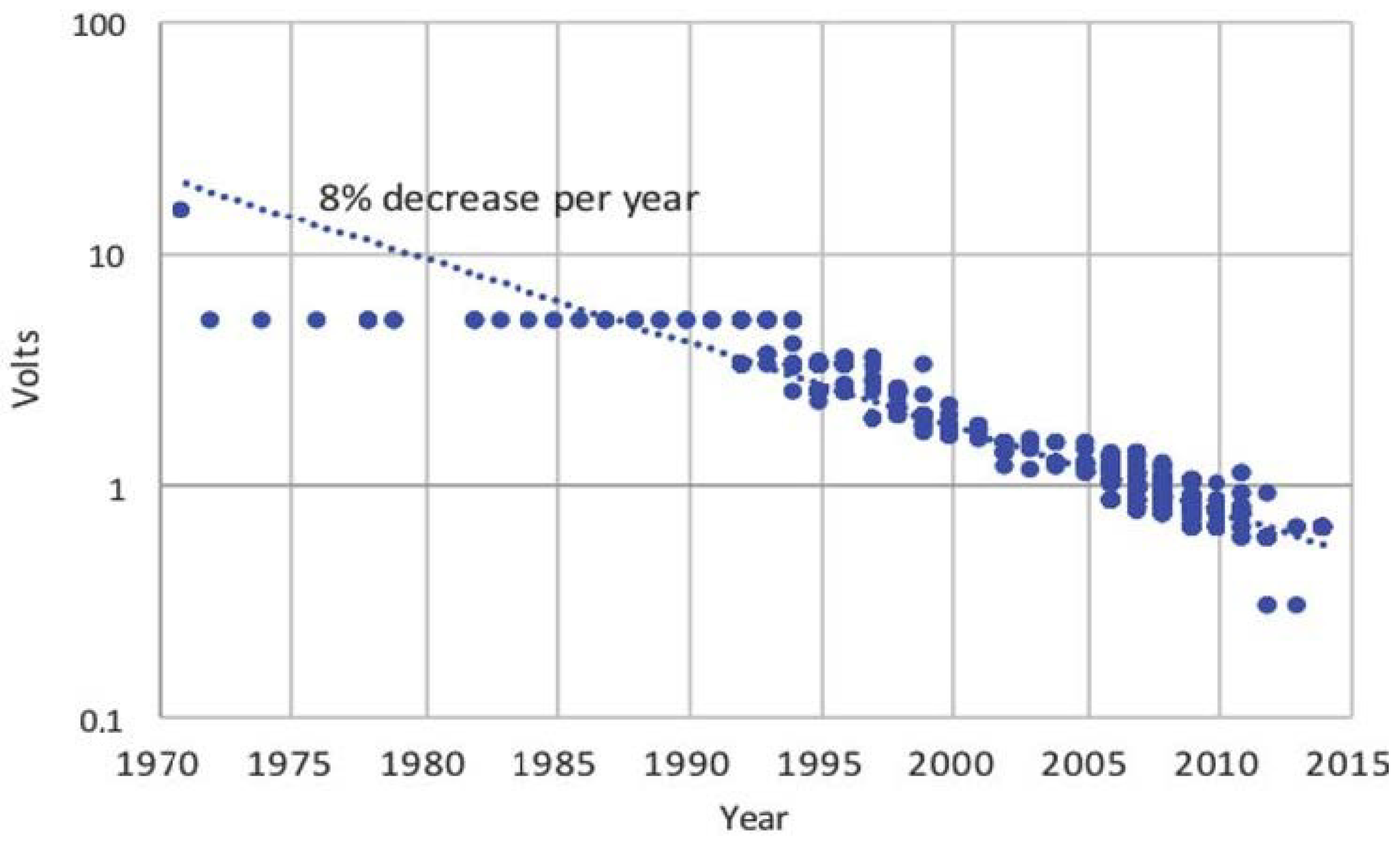

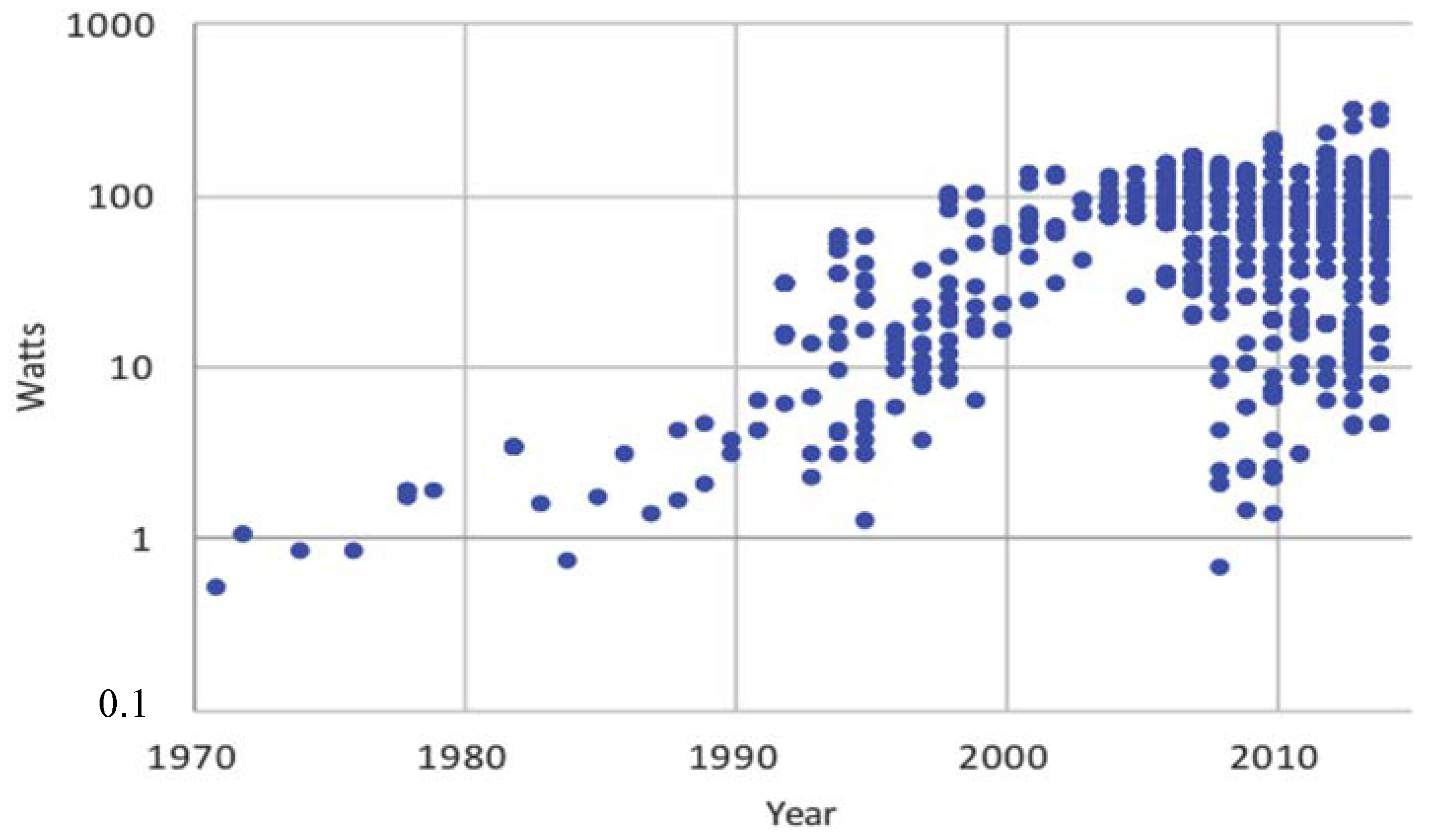

4.2. Energy Efficiency

4.3. HPC and Energy Efficiency

5. Artificial Intelligence: Overview

5.1. The Need for AI in HPC

5.2. AI Tools and Techniques

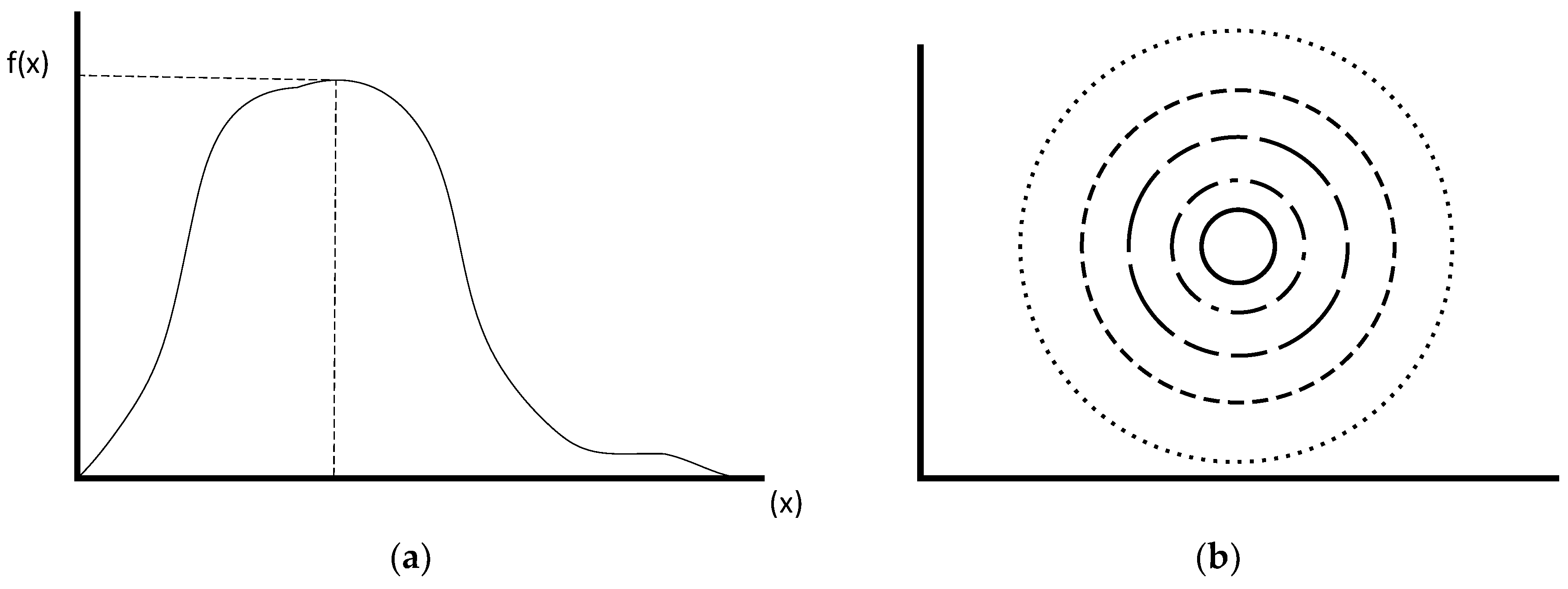

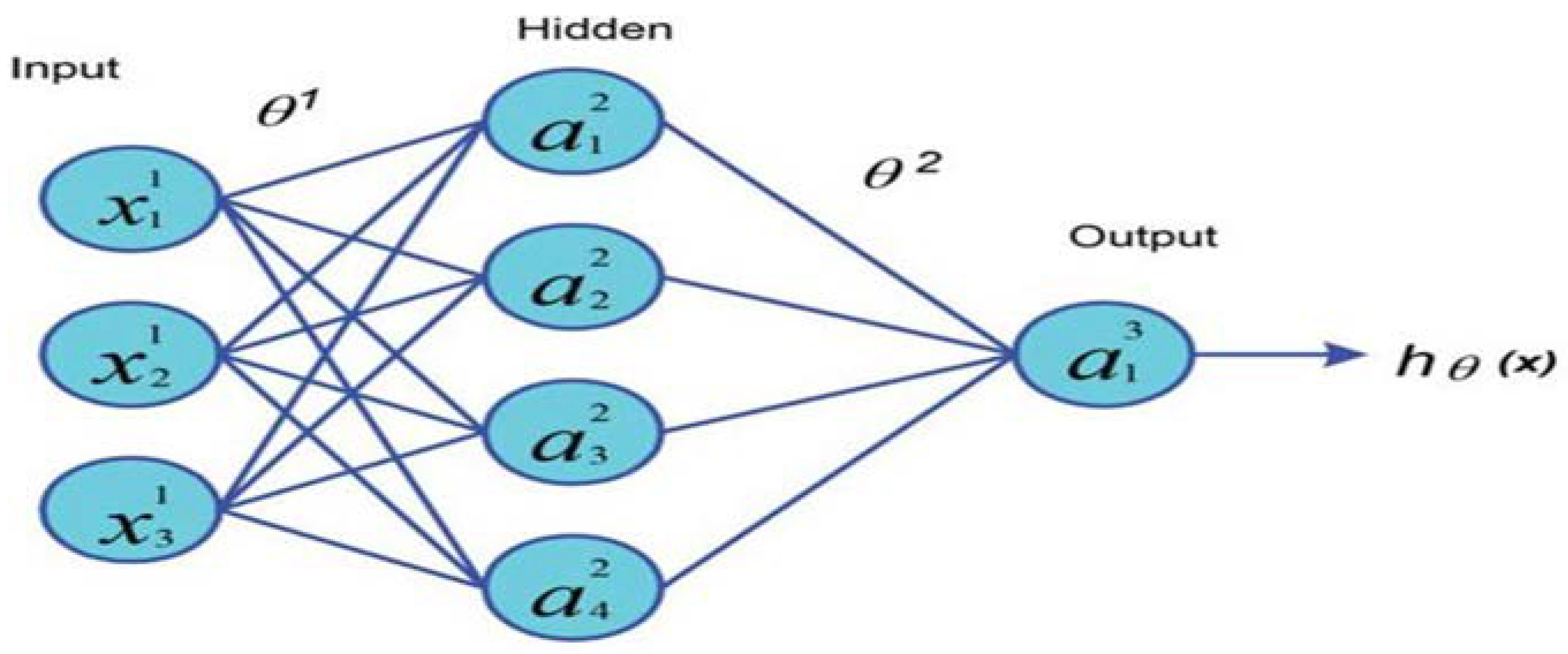

5.2.1. Artificial Neural Networks

5.2.2. Multi-Agent Systems

5.2.3. Reinforced Learning

6. Case Study: A Practical Application

6.1. Model Implementation

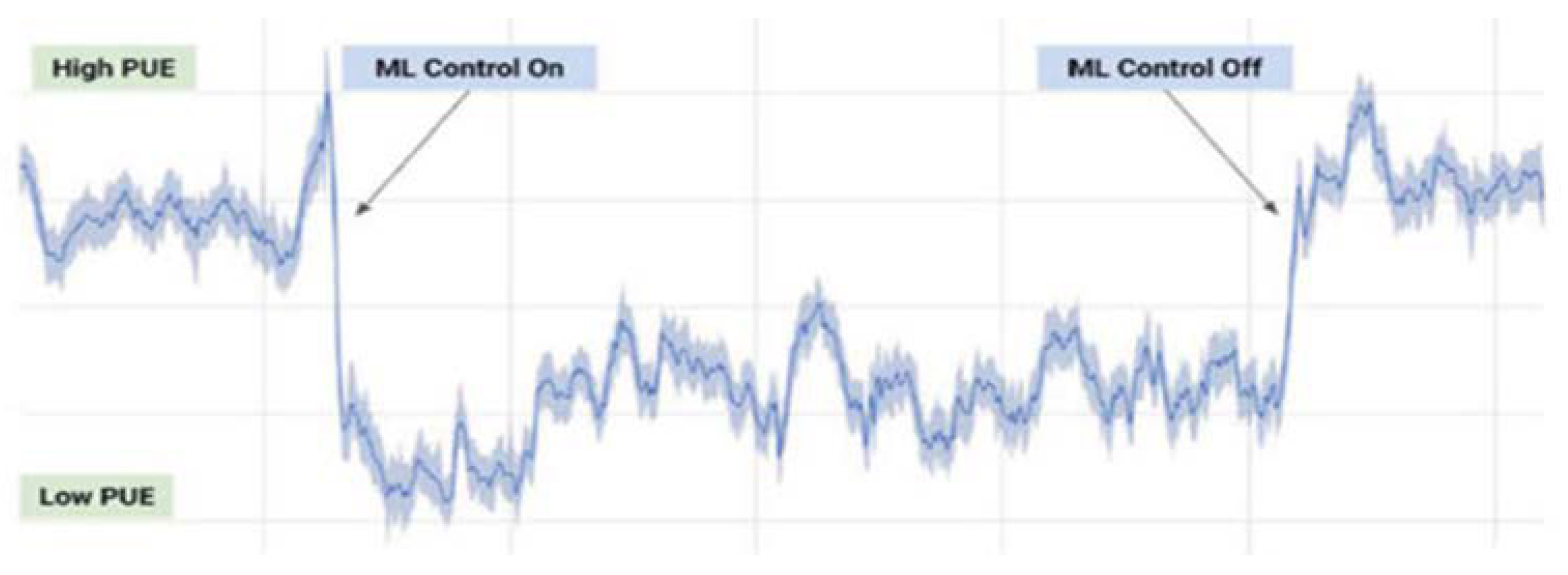

6.2. Benefits of Power Usage Effectiveness

- (1)

- Automatic performance warning, plant efficiency projections in real-time and troubleshooting using a contrast of actual vs. expected results under a set of conditions stated.

- (2)

- It helps operators of data centers to measure PUE sensitivity to operating parameters of the data center.

- (3)

- It helps operators to model Data Center operational conditions making no physical adjustments or changes. This approach emphasizing simulation enables operators to virtualize the Data Center and describe ideal plant configurations while minimizing the doubt concerning changes in plants.

6.3. Limitations

7. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Gill, S.S.; Tuli, S.; Xu, M.; Singh, I.; Singh, K.V.; Lindsay, D.; Tuli, S.; Smirnova, D.; Singh, M.; Jain, U.; et al. Transformative effects of IoT, Blockchain and Artificial Intelligence on cloud computing: Evolution, vision, trends and open challenges. Internet Things 2019, 8, 100118. [Google Scholar] [CrossRef]

- Tapscott, D.; Tapscott, A. Blockchain Revolution: How the Technology behind Bitcoin is Changing Money, Business, and the World; Penguin Publishing Group: London, UK, 2016. [Google Scholar]

- Martin, C.; Leurent, H. Technology and Innovation for the Future of Production: Accelerating Value Creation; World Economic Forum: Geneva, Switzerland, 2017. [Google Scholar]

- NetApp. What is High Performance Computing. Available online: http://www.netapp.com/us/info/what-is-high-performance-computing.aspx. (accessed on 23 April 2020).

- Henke, N.; Bughin, J.; Chui, M.; Manyika, J.; Saleh, T.; Wiseman, B.; Sethupathy, G. The age of analytics: Competing in a data-driven world. McKinsey Glob. Inst. 2016; 30, 1–28. [Google Scholar]

- Singh, M.K. Effective Big Data Management and Opportunities for Implementation; IGI Global: Hershey, PA, USA, 2016. [Google Scholar]

- Research and Markets. High Performance Computing (HPC) Market by Component, Infrastructure, Services, Price Band, HPC Applications, Deployment Types, Industry Verticals, and Regions. 2020–2025. Available online: https://www.researchandmarkets.com/reports/4896466/high-performance-computing-hpc-market-by (accessed on 23 April 2020).

- NVIDIA. Telecommunications Solutions for 5G Networks. Available online: https://www.nvidia.com/en-us/industries/telecommunications/ (accessed on 23 April 2020).

- Ezell, S.J.; Atkinson, R.D. The Vital Importance of High-Performance Computing to US Competitiveness; Information Technology and Innovation Foundation: Washington, WA, USA, 28 April 2016. [Google Scholar]

- PRACE. Supercomputers for All; The Next Frontier for High Performance Computing SPECIAL REPORT. 2013. Available online: https://prace-ri.eu/wp-content/uploads/SupercomputersForAll.pdf (accessed on 23 April 2020).

- Joseph, E.; Dekate, C.; Conway, S. Real-World Examples of Supercomputers Used For Economic and Societal Benefits: A Prelude to What the Exascale Era Can Provide (Special Study). 2014. Available online: https://www.hpcuserforum.com/downloads/HPCSuccessStories.pdf (accessed on 15 May 2020).

- Auweter, A.; Bode, A.; Brehm, M.; Huber, H.; Kranzlmüller, D. Principles of energy efficiency in high performance computing. In Proceedings of the International Conference on Information and Communication on Technology, Depok, Indonesia, 24–26 Junuary 2020; pp. 18–25. [Google Scholar]

- Halper, M. Supercomputing’s super energy needs, and what to do about them. Commun. ACM 2015, 9, 93–99. [Google Scholar]

- Flórez, E.; Pecero, J.E.; Emeras, J.; Barrios, C.J. Energy model for low-power cluster. In Proceedings of the 2017 17th IEEE/ACM International Symposium on Cluster, Cloud and Grid Computing (CCGRID), Madrid, Spain, 14 May 2017; pp. 1009–1016. [Google Scholar]

- Amruta, M.K.; Satish, M.T. Solar powered water quality monitoring system using wireless sensor network. In Proceedings of the 2013 International Mutli-Conference on Automation, Computing, Communication, Control and Compressed Sensing (iMac4s), Kerala, India, 22 March 2013; pp. 281–285. [Google Scholar]

- Enterprise, H.P. Improving the energy efficiency of modern supercomputers. In Hewlett Packard Enterprise Development LP; Springer: Cham, Switherland, 2017. [Google Scholar]

- González, A. Trends in Processor Architecture. In Harnessing Performance Variability in Embedded and High-Performance Many/Multi-Core Platforms; Springer: Berlin/Heidelberg, Germany, 2019; pp. 23–42. [Google Scholar]

- Czarnul, P.; Proficz, J.; Krzywaniak, A. Energy-Aware High-Performance Computing: Survey of State-of-the-Art Tools, Techniques, and Environments. Sci. Program. 2019, 19. [Google Scholar] [CrossRef]

- Matsuoka, S.; Endo, T.; Nukada, A.; Miura, S.; Nomura, A.; Sato, H.; Jitsumoto, H.; Drozd, A. Overview of TSUBAME3. 0 Green Cloud Supercomputer for Convergence of HPC AI and Big-Data. E-Sci. J. 2017, 16, 2–9. [Google Scholar]

- Alsharif, M.H.; Nordin, R.; Ismail, M. Survey of green radio communications networks: Techniques and recent advances. J. Comput. Netw. Commun. 2013, 2013, 13. [Google Scholar] [CrossRef]

- Letcher, C.W. Green Computing-Desktop Computer Power Management at the City of Tulsa; Oklahoma State University: Stillwater, Oklahoma, 2013. [Google Scholar]

- Yi, G.; Loia, V. High-performance computing systems and applications for AI. J. Supercomput. 2019, 75, 4248–4251. [Google Scholar] [CrossRef]

- Lu, C.-P. AI, native supercomputing and the revival of Moore's Law. APSIPA Trans. Signal Inf. Process. 2017, 6. [Google Scholar] [CrossRef]

- Rong, H.; Zhang, H.; Xiao, S.; Li, C.; Hu, C. Optimizing energy consumption for data centers. Renew. Sustain. Energy Rev. 2016, 58, 674–691. [Google Scholar] [CrossRef]

- Council, N.R. Getting up to Speed: The Future of Supercomputing; National Academies Press: Cambridge, MA, USA, 2005. [Google Scholar]

- Liao, X.-K.; Lu, K.; Yang, C.-Q.; Li, J.-W.; Yuan, Y.; Lai, M.-C.; Huang, L.-B.; Lu, P.-J.; Fang, J.-B.; Ren, J. Moving from exascale to zettascale computing: Challenges and techniques. Front. Inf. Technol. Electron. Eng. 2018, 19, 1236–1244. [Google Scholar] [CrossRef]

- Strande, S.M.; Cai, H.; Cooper, T.; Flammer, K.; Irving, C.; von Laszewski, G.; Majumdar, A.; Mishin, D.; Papadopoulos, P.; Pfeiffer, W. Comet: Tales from the long tail: Two years in and 10,000 users later. In Proceedings of the Practice and Experience in Advanced Research Computing 2017 on Sustainability, Success and Impact, New Orleans, LA, USA, 9–13 July 2017; pp. 1–7. [Google Scholar]

- Dayarathna, M.; Wen, Y.; Fan, R. Data center energy consumption modeling: A survey. IEEE Commun. Surv. Tutor. 2015, 18, 732–794. [Google Scholar] [CrossRef]

- Kant, K. Data center evolution: A tutorial on state of the art, issues, and challenges. Comput. Netw. 2009, 53, 2939–2965. [Google Scholar] [CrossRef]

- Bergamaschi, R.A.; Piga, L.; Rigo, S.; Azevedo, R.; Araújo, G. Data center power and performance optimization through global selection of p-states and utilization rates. Sustain. Comput. Inform. Syst. 2012, 2, 198–208. [Google Scholar] [CrossRef]

- Rizvandi, N.B.; Zomaya, A.Y. A Primarily Survey on Energy Efficiency in Cloud and Distributed Computing Systems. arXiv 2012, arXiv:1210.4690. [Google Scholar]

- Maiterth, M.; Koenig, G.; Pedretti, K.; Jana, S.; Bates, N.; Borghesi, A.; Montoya, D.; Bartolini, A.; Puzovic, M. Energy and Power Aware Job Scheduling and Resource Management: Global Survey—Initial Analysis. 2018. Available online: https://ieeexplore.ieee.org/abstract/document/8425478 (accessed on 24 April 2020).

- Zamani, R.; Afsahi, A.; Qian, Y.; Hamacher, C. A Feasibility Analysis of Power-Awareness and Energy Minimization in Modern Interconnects for High-Performance Computing. 2007. Available online: https://ieeexplore.ieee.org/abstract/document/4629224/ (accessed on 24 April 2020).

- Centre for Development of Advanced Computing (C-DAC) One-Day Symposium on Energy Efficiency Challenges for HPC Systems. Available online: https://www.cdac.in/index.aspx?id=pdf_Energy_Efficiency_Challenges_HPC_2019 (accessed on 24 April 2020).

- Gupta, G. The Benefits of Bringing Artificial Intelligence to High Performance Computing. 2019. Available online: https://high-performance-computing.cioreview.com/cxoinsight/the-benefits-of-bringing-artificial-intelligence-to-high-performance-computing-nid-26530-cid-84.html (accessed on 24 April 2020).

- Mei, X.; Wang, Q.; Chu, X. A survey and measurement study of GPU DVFS on energy conservation. Digit. Commun. Netw. 2017, 3, 89–100. [Google Scholar] [CrossRef]

- Johnsson, L.; Ahlin, D.; Wang, J. The SNIC/KTH PRACE Prototype: Achieving High Energy Efficiency with Commodity Technology without Acceleration. 2010. Available online: https://ieeexplore.ieee.org/abstract/document/5598259/ (accessed on 24 April 2020).

- Kan, E.Y.; Chan, W.K.; Tse, T. EClass: An execution classification approach to improving the energy-efficiency of software via machine learning. J. Syst. Softw. 2012, 85, 960–973. [Google Scholar] [CrossRef]

- Saravanan, K.P.; Carpenter, P.M.; Ramirez, A. Power/Performance Evaluation of Energy Efficient Ethernet (eee) for High Performance Computing. 2013. Available online: https://ieeexplore.ieee.org/abstract/document/6557171/ (accessed on 24 April 2020).

- Dally, B. Power, Programmability, and Granularity: The Challenges of Exascale Computing. Available online: https://ieeexplore.ieee.org/abstract/document/6139189/ (accessed on 24 April 2020).

- Reed, D.A.; Dongarra, J. Exascale computing and big data. Commun. ACM 2015, 58, 56–68. [Google Scholar] [CrossRef]

- Hussain, S.M.; Wahid, A.; Shah, M.A.; Akhunzada, A.; Arshad, S. Seven Pillars to Achieve Energy Efficiency in High Performance Computing and Big Data: An Application Perspective of Fog Computing; Springer: Cham, The Netherlands, 2019. [Google Scholar]

- Diouri, M.E.; Chetsa, G.L.T.; Glück, O.; Lefevre, L.; Pierson, J.-M.; Stolf, P.; Da Costa, G. Energy efficiency in high-performance computing with and without knowledge of applications and services. Int. J. High Perform. Comput. Appl. 2013, 27, 232–243. [Google Scholar] [CrossRef]

- Tan, L.; Song, S.L.; Wu, P.; Chen, Z.; Ge, R.; Kerbyson, D.J. Investigating the interplay between energy efficiency and resilience in high performance computing. In Proceedings of the 2015 IEEE International Parallel and Distributed Processing Symposium, Hyderabad, India, 25–29 May 2015; pp. 786–796. [Google Scholar]

- Wang, Z.; Srinivasan, R.S. A Review of Artificial Intelligence based Building Energy Prediction with a Focus on Ensemble Prediction Models. 2015. Available online: https://ieeexplore.ieee.org/abstract/document/7408504 (accessed on 24 April 2020).

- Dounis, A.I. Artificial intelligence for energy conservation in buildings. Adv. Build. Energy Res. 2010, 4, 267–299. [Google Scholar] [CrossRef]

- Jiang, Z.; Gao, W.; Wang, L.; Xiong, X.; Zhang, Y.; Wen, X.; Luo, C.; Ye, H.; Lu, X.; Zhang, Y. HPC AI500: A Benchmark Suite for HPC AI Systems. 2018. Available online: https://link.springer.com/chapter/10.1007/978-3-030-32813-9_2 (accessed on 24 April 2020).

- García Martín, E. Energy efficiency in machine learning: A position paper. In Proceedings of the 30th Annual Workshop of the Swedish Artificial Intelligence Society SAIS, Karlskrona, Sweden, 15–16 May 2017; pp. 68–72. [Google Scholar]

- IntelCorporation. Bringing AI Into Your Agency HPC Environment. Available online: https://www.govexec.com/media/intel_ai-hpc_eguide.pdf (accessed on 30 April 2020).

- Imes, C.; Hofmeyr, S.; Hofmann, H. Energy Efficiency in HPC with Machine Learning and Control Theory. 2017. Available online: https://sc17.supercomputing.org/SC17%20Archive/tech_poster/poster_files/post215s2-file3.pdf (accessed on 30 April 2020).

- Beloglazov, A.; Buyya, R.; Lee, Y.C.; Zomaya, A. A taxonomy and survey of energy-efficient data centers and cloud computing systems. In Advances in Computers; Elsevier: Amsterdam, The Netherlands, 2011; Volume 82, pp. 47–111. [Google Scholar]

- Vetter, J.S.; Mittal, S. Opportunities for nonvolatile memory systems in extreme-scale high-performance computing. Comput. Sci. Eng. 2015, 17, 73–82. [Google Scholar] [CrossRef]

- Freeh, V.W.; Lowenthal, D.K.; Pan, F.; Kappiah, N.; Springer, R.; Rountree, B.L.; Femal, M.E. Analyzing the energy-time trade-off in high-performance computing applications. IEEE Trans. Parallel Distrib. Syst. 2007, 18, 835–848. [Google Scholar] [CrossRef]

- Labasan, S. Energy-Efficient and Power-Constrained Techniques for Exascale Computing; Semanticscholar: Seattle, WA, USA, 2016. [Google Scholar]

- Wlotzka, M.; Heuveline, V. Energy-efficient multigrid smoothers and grid transfer operators on multi-core and GPU clusters. J. Parallel Distrib. Comput. 2017, 100, 181–192. [Google Scholar] [CrossRef]

- Graham, S.L.; Snir, M.; Patterson, C.A. Bolstering US Supercomputing. Issues Sci. Technol. 2005, 21, 28–32. [Google Scholar]

- Kelechi, A.H.; Alsharif, M.H.; Ramly, A.A.; Abdullah, N.F.; Nordin, R. The Four-C Framework for High Capacity Ultra-Low Latency in 5G Networks: A Review. Energies 2019, 12, 3449. [Google Scholar] [CrossRef]

- Alsharif, M.H.; Nordin, R. Evolution towards fifth generation (5G) wireless networks: Current trends and challenges in the deployment of millimetre wave, massive MIMO, and small cells. Telecommun. Syst. 2017, 64, 617–637. [Google Scholar] [CrossRef]

- Baldemair, R.; Dahlman, E.; Fodor, G.; Mildh, G.; Parkvall, S.; Selen, Y.; Tullberg, H.; Balachandran, K. Evolving wireless communications: Addressing the challenges and expectations of the future. IEEE Veh. Technol. Mag. 2013, 8, 24–30. [Google Scholar] [CrossRef]

- ITU-R. 5G —Fifth Generation of Mobile Technologies. Available online: https://www.itu.int/en/mediacentre/backgrounders/Pages/5G-fifth-generation-of-mobile-technologies.aspx. (accessed on 30 April 2020).

- Durisi, G.; Koch, T.; Popovski, P. Toward massive, ultrareliable, and low-latency wireless communication with short packets. Proc. IEEE 2016, 104, 1711–1726. [Google Scholar] [CrossRef]

- Morris, A. Scaling for 5G: From Data Centers to the Edge. Available online: https://www.hpcwire.com/solution_content/ibm/scaling-for-5g-from-data-centers-to-the-edge/ (accessed on 24 April 2020).

- Dahlman, E.; Mildh, G.; Parkvall, S.; Peisa, J.; Sachs, J.; Selén, Y. 5G radio access. Ericsson Rev. 2014, 6, 1–28. [Google Scholar]

- Fu, Y.; Wang, S.; Wang, C.-X.; Hong, X.; McLaughlin, S. Artificial intelligence to manage network traffic of 5G wireless networks. IEEE Netw. 2018, 32, 58–64. [Google Scholar] [CrossRef]

- Levis, B. Scaling HPC for 5G, AI, and Whatever’s Next. Available online: https://www.insight.tech/content/scaling-hpc-for-5g-ai-and-whatever-s-next (accessed on 25 April 2020).

- Al-Quzweeni, A.N.; Lawey, A.Q.; Elgorashi, T.E.; Elmirghani, J.M. Optimized energy aware 5G network function virtualization. IEEE Access 2019, 7, 44939–44958. [Google Scholar] [CrossRef]

- Alsharif, M.H.; Kelechi, A.H.; Albreem, M.A.; Chaudhry, A.C.; Zia, M.S.; Kim, S. Sixth Generation (6G) Wireless Networks: Vision, Research Activities, Challenges and Potential Solutions. Symmetry 2020, 12, 676. [Google Scholar] [CrossRef]

- Zhou, Y.; Li, N.; Li, H.; Zhang, Y. Regression cloud models and their applications in energy consumption of data center. J. Electr. Comput. Eng. 2015, 2015, 9. [Google Scholar] [CrossRef]

- Shoukourian, H.; Wilde, T.; Auweter, A.; Bode, A. Monitoring power data: A first step towards a unified energy efficiency evaluation toolset for HPC data centers. Environ. Model. Softw. 2014, 56, 13–26. [Google Scholar] [CrossRef]

- Chen, Y.-L.; Chang, M.-F.; Yu, C.-W.; Chen, X.-Z.; Liang, W.-Y. Learning-Directed Dynamic Voltage and Frequency Scaling Scheme with Adjustable Performance for Single-Core and Multi-Core Embedded and Mobile Systems. Sensors 2018, 18, 3068. [Google Scholar] [CrossRef]

- Trestian, R. Next-Generation Wireless Networks Meet Advanced Machine Learning Applications; IGI Global: Hershey, PA, USA, 2019. [Google Scholar]

- Alsharif, M.H.; Kelechi, A.H.; Yahya, K.; Chaudhry, S.A. Machine Learning Algorithms for Smart Data Analysis in Internet of Things Environment: Taxonomies and Research Trends. Symmetry 2020, 12, 88. [Google Scholar] [CrossRef]

- Osisanwo, F.; Akinsola, J.; Awodele, O.; Hinmikaiye, J.; Olakanmi, O.; Akinjobi, J. Supervised machine learning algorithms: Classification and comparison. Int. J. Comput. Trends Technol. (IJCTT) 2017, 48, 128–138. [Google Scholar]

- Wang, Z.; Srinivasan, R.S. A review of artificial intelligence based building energy use prediction: Contrasting the capabilities of single and ensemble prediction models. Renew. Sustain. Energy Rev. 2017, 75, 796–808. [Google Scholar] [CrossRef]

- Wang, T.; Xia, Y.; Muppala, J.; Hamdi, M. Achieving energy efficiency in data centers using an artificial intelligence abstraction model. IEEE Trans. Cloud Comput. 2015, 6, 612–624. [Google Scholar] [CrossRef]

- Chen, K.; Lin, G. Optimization of multiple-module thermoelectric coolers using artificial-intelligence techniques. Int. J. Energy Res. 2002, 26, 1269–1283. [Google Scholar] [CrossRef]

- Lee, J.; Stanley, M.; Spanias, A.; Tepedelenlioglu, C. Integrating machine learning in embedded sensor systems for Internet-of-Things applications. 2016. Available online: https://ieeexplore.ieee.org/abstract/document/7886051/ (accessed on 30 April 2020).

- Singh, A.; Thakur, N.; Sharma, A. A review of supervised machine learning algorithms. 2016. Available online: https://ieeexplore.ieee.org/abstract/document/7724478/ (accessed on 30 April 2020).

- Chen, S.H.; Jakeman, A.J.; Norton, J.P. Artificial intelligence techniques: An introduction to their use for modelling environmental systems. Math. Comput. Simul. 2008, 78, 379–400. [Google Scholar] [CrossRef]

- Belhaj, S.; Tagina, M. Modeling and prediction of the internet end-to-end delay using recurrent neural networks. J. Netw. 2009, 4, 528–535. [Google Scholar] [CrossRef]

- Buskirk, T.D.; Kirchner, A.; Eck, A.; Signorino, C.S. An introduction to machine learning methods for survey researchers. Surv. Pract. 2018, 11, 2718. [Google Scholar] [CrossRef]

- Rodvold, D.; McLeod, D.; Brandt, J.; Snow, P.; Murphy, G. Introduction to artificial neural networks for physicians: Taking the lid off the black box. Prostate 2001, 46, 39–44. [Google Scholar] [CrossRef]

- Jain, A.K.; Mao, J.; Mohiuddin, K.M. Artificial neural networks: A tutorial. Computer 1996, 29, 31–44. [Google Scholar] [CrossRef]

- Rycroft, M. Energy Management in Industry: Can AI Improve Energy Efficiency? Available online: https://www.ee.co.za/article/energy-management-in-industry-can-ai-improve-energy-efficiency.html (accessed on 25 April 2020).

- Sui, X.; Yang, Y.; Xu, X.; Zhang, S.; Zhang, L. The sampled-data consensus of multi-agent systems with probabilistic time-varying delays and packet losses. Phys. A Stat. Mech. Appl. 2018, 492, 1625–1641. [Google Scholar] [CrossRef]

- Luong, N.C.; Hoang, D.T.; Gong, S.; Niyato, D.; Wang, P.; Liang, Y.-C.; Kim, D.I. Applications of deep reinforcement learning in communications and networking: A survey. IEEE Commun. Surv. Tutor. 2019, 21, 3133–3174. [Google Scholar] [CrossRef]

- Li, J.; Gao, H.; Lv, T.; Lu, Y. Deep Reinforcement Learning based Computation Offloading and Resource Allocation for MEC. 2018. Available online: https://ieeexplore.ieee.org/abstract/document/8377343/ (accessed on 25 April 2020).

- Qiu, J.; Wu, Q.; Ding, G.; Xu, Y.; Feng, S. A survey of machine learning for big data processing. EURASIP J. Adv. Signal Process. 2016, 2016, 67. [Google Scholar] [CrossRef]

- Binsahaq, A.; Sheltami, T.R.; Salah, K. A survey on autonomic provisioning and management of QoS in SDN networks. IEEE Access 2019, 7, 73384–73435. [Google Scholar] [CrossRef]

- Gao, J. Machine Learning Applications for Data Center Optimization; Semanticscholar: Seattle, WA, USA, 2014. [Google Scholar]

- Evans, R.; Gao, J. Deepmind AI reduces Google data centre cooling bill by 40%. DeepMind Blog 2016, 20, 158. [Google Scholar]

- DeepMind, A. Reduces Google Data Centre Cooling Bill by 40%; Semanticscholar: Seattle, WA, USA, 2016. [Google Scholar]

| Reference | Objectives |

|---|---|

| Axel Auweter and Herbert Huber, 2011, [12] |

|

| Czarnul, Proficz, and Krzywaniak, 2019, [18] |

|

| Diouri et al., 2013, [43] |

|

| Florez, Pecero, Emeras, and Barrios, 2017, [14] |

|

| Hussain, Wahid, Shah, Akhunzada, and Arshad, 2018, [42] |

|

| Jiang et al., 2018, [47] |

|

| Johnsson, Ahlin, and Wang, 2010, [37] |

|

| Labasan, 2016, [54] |

|

| Lu, 2017, [23] |

|

| Saravanan, Carpenter, and Ramirez, 2013, [39] |

|

| Tan et al., 2015, [44] |

|

| Wang, Zeyu and M.E.Rinker, 2015, [45] |

|

| Wlotzka et al., 2017, [55] |

|

| Yi and Loia, 2019, [22] |

|

| Graham, Susan L. Snir, MarcPatterson, Cynthia A. 2005, [56] |

|

| X. Mei, Q. Wang, and X. Chu, 2017. [36] |

|

| E. Y. Y. Kan, W. K. Chan, and T. H. Tse 2012., [38] |

|

| PRACE,2013, [10]. |

|

| A. Beloglazov, R. Buyya, Y. C. Lee, and A. Zomaya, 2011. [51] |

|

| H. Rong, H. Zhang, S. Xiao, C. Li, and C. Hu, 2016, [24] |

|

| C. Imes, S. Hofmeyr, and H. Hofmann, 2017, [50] |

|

| J. S. Vetter and S. Mittal, 2015, [52] |

|

| V. W. Freeh et al., 2007, [53] |

|

| A. I. Dounis, 2010, [46] |

|

| Intel Corporation, [49] |

|

| E. Garcia, 2017, [48] |

|

| Advantages | Disadvantages | |

|---|---|---|

| Regression Algorithm | Model development is rapid and straightforward. Useful when the relationship to be modeled is not extremely complex and do not have a lot of data. | Applicable only if the solution is linear. In many real-life scenarios, it may not be the case. The algorithm assumes the input residuals (error) to be normally distributed but may not always be satisfied. |

| Classification | Straight forward implementation. New data can be added seamlessly. Robust against noisy training data. It has the capability to modeling complex classification problems by using many hidden neurons. Maintain the information that presents in the training data. | Does not work well with large dataset except using deep neural network. Sensitive to unbalanced training data. It is a supervised lazy learner. Requires huge memory usage cost |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kelechi, A.H.; Alsharif, M.H.; Bameyi, O.J.; Ezra, P.J.; Joseph, I.K.; Atayero, A.-A.; Geem, Z.W.; Hong, J. Artificial Intelligence: An Energy Efficiency Tool for Enhanced High performance computing. Symmetry 2020, 12, 1029. https://doi.org/10.3390/sym12061029

Kelechi AH, Alsharif MH, Bameyi OJ, Ezra PJ, Joseph IK, Atayero A-A, Geem ZW, Hong J. Artificial Intelligence: An Energy Efficiency Tool for Enhanced High performance computing. Symmetry. 2020; 12(6):1029. https://doi.org/10.3390/sym12061029

Chicago/Turabian StyleKelechi, Anabi Hilary, Mohammed H. Alsharif, Okpe Jonah Bameyi, Paul Joan Ezra, Iorshase Kator Joseph, Aaron-Anthony Atayero, Zong Woo Geem, and Junhee Hong. 2020. "Artificial Intelligence: An Energy Efficiency Tool for Enhanced High performance computing" Symmetry 12, no. 6: 1029. https://doi.org/10.3390/sym12061029

APA StyleKelechi, A. H., Alsharif, M. H., Bameyi, O. J., Ezra, P. J., Joseph, I. K., Atayero, A.-A., Geem, Z. W., & Hong, J. (2020). Artificial Intelligence: An Energy Efficiency Tool for Enhanced High performance computing. Symmetry, 12(6), 1029. https://doi.org/10.3390/sym12061029