Encapsulation of NEM Memory Switches for Monolithic-Three-Dimensional (M3D) CMOS–NEM Hybrid Circuits

Abstract

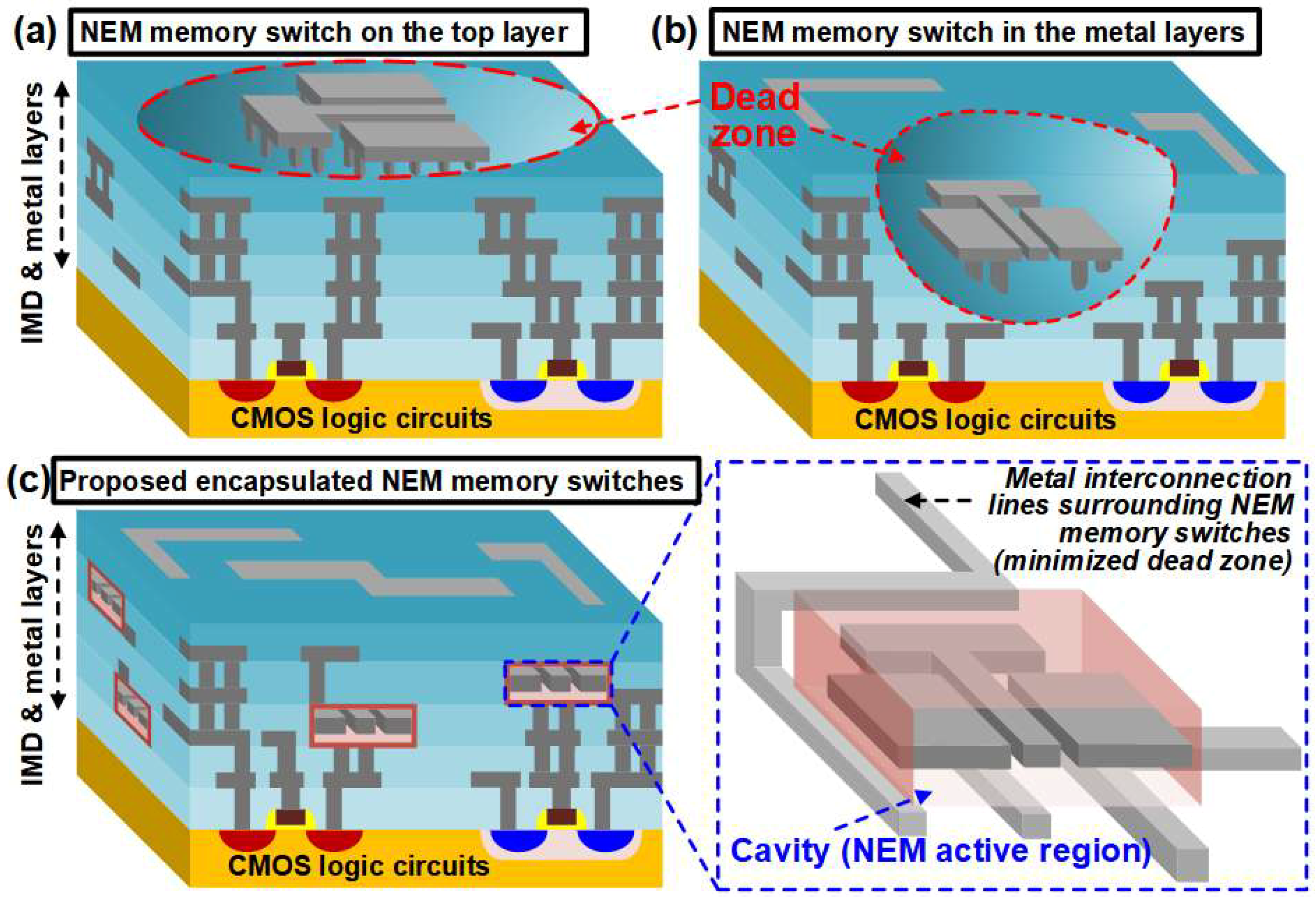

:1. Introduction

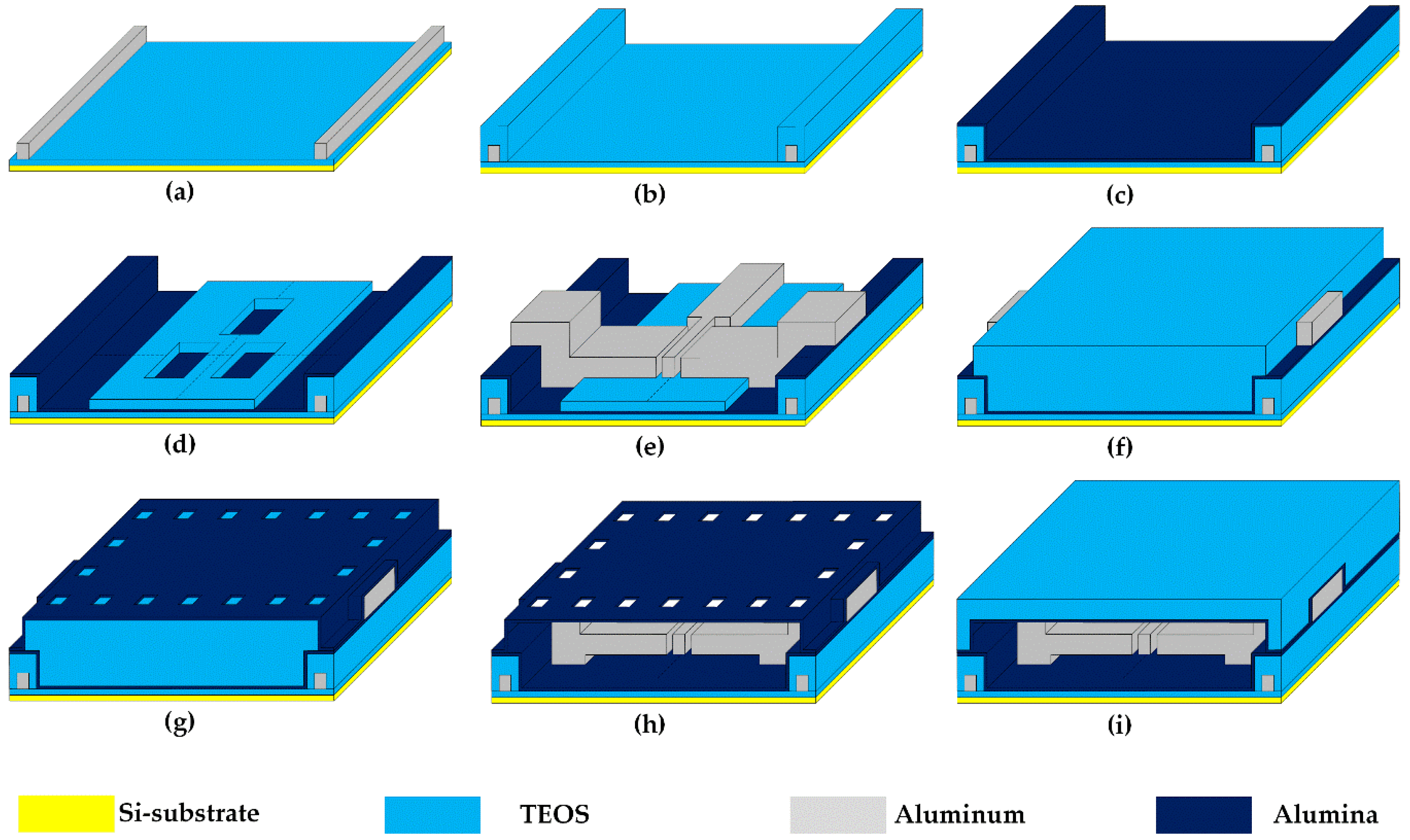

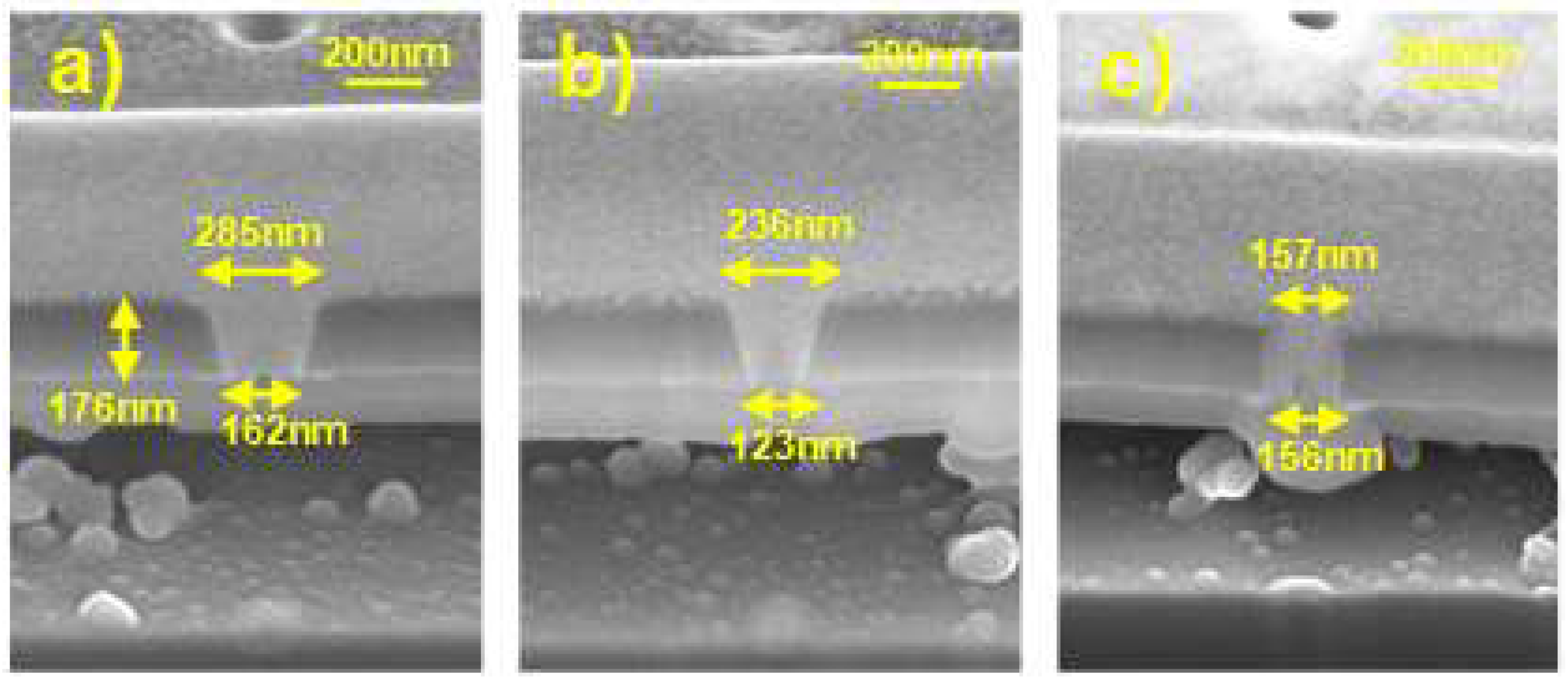

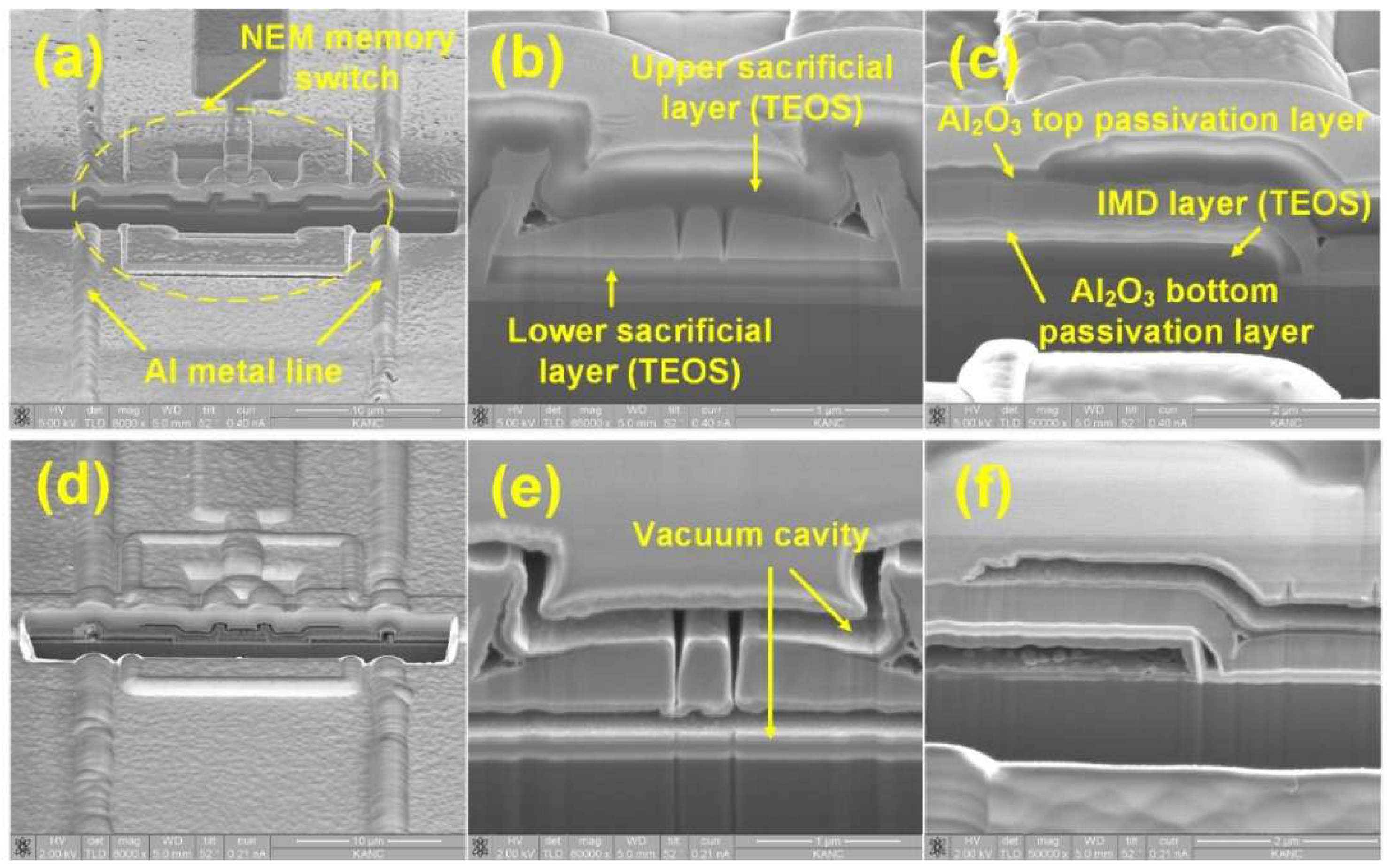

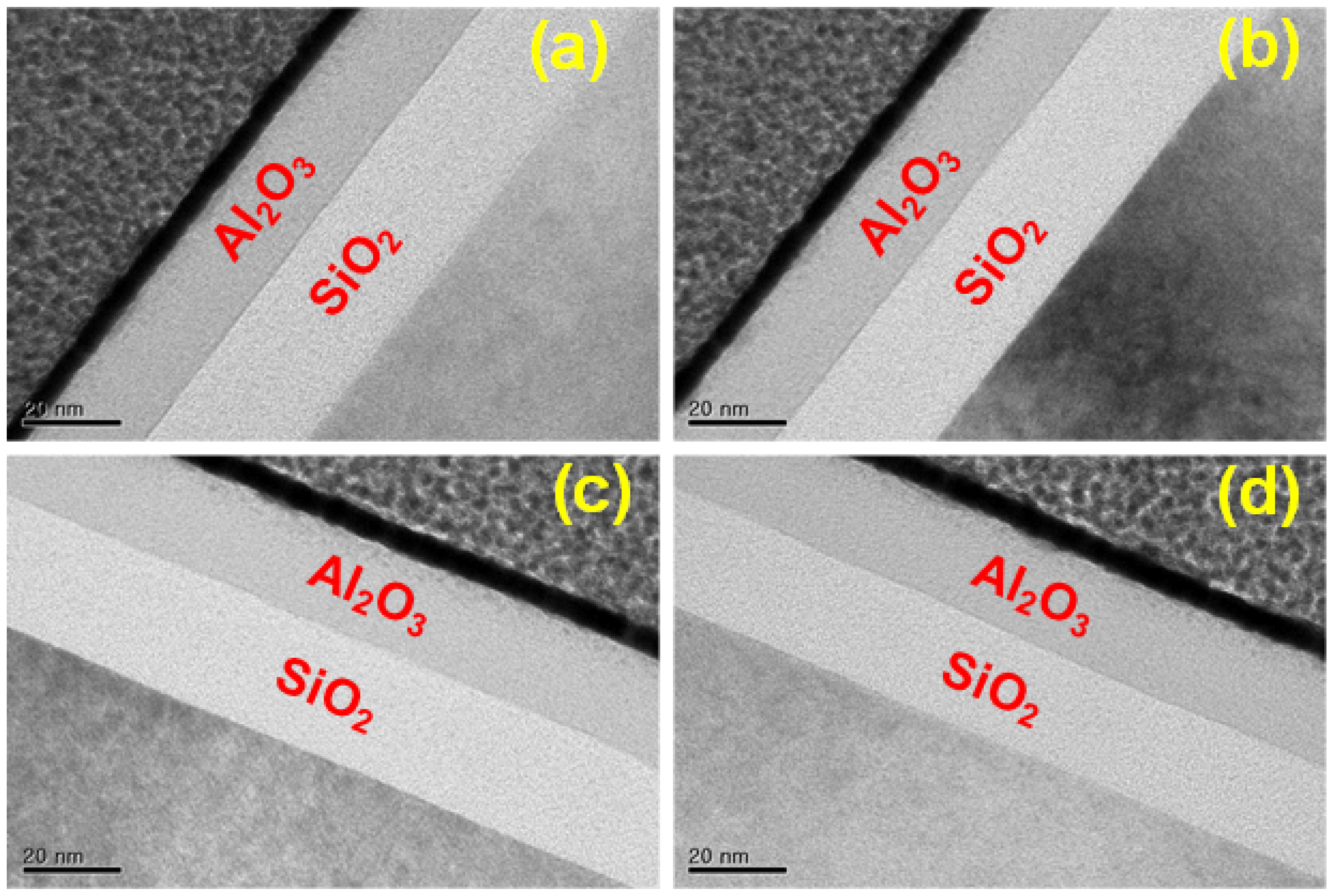

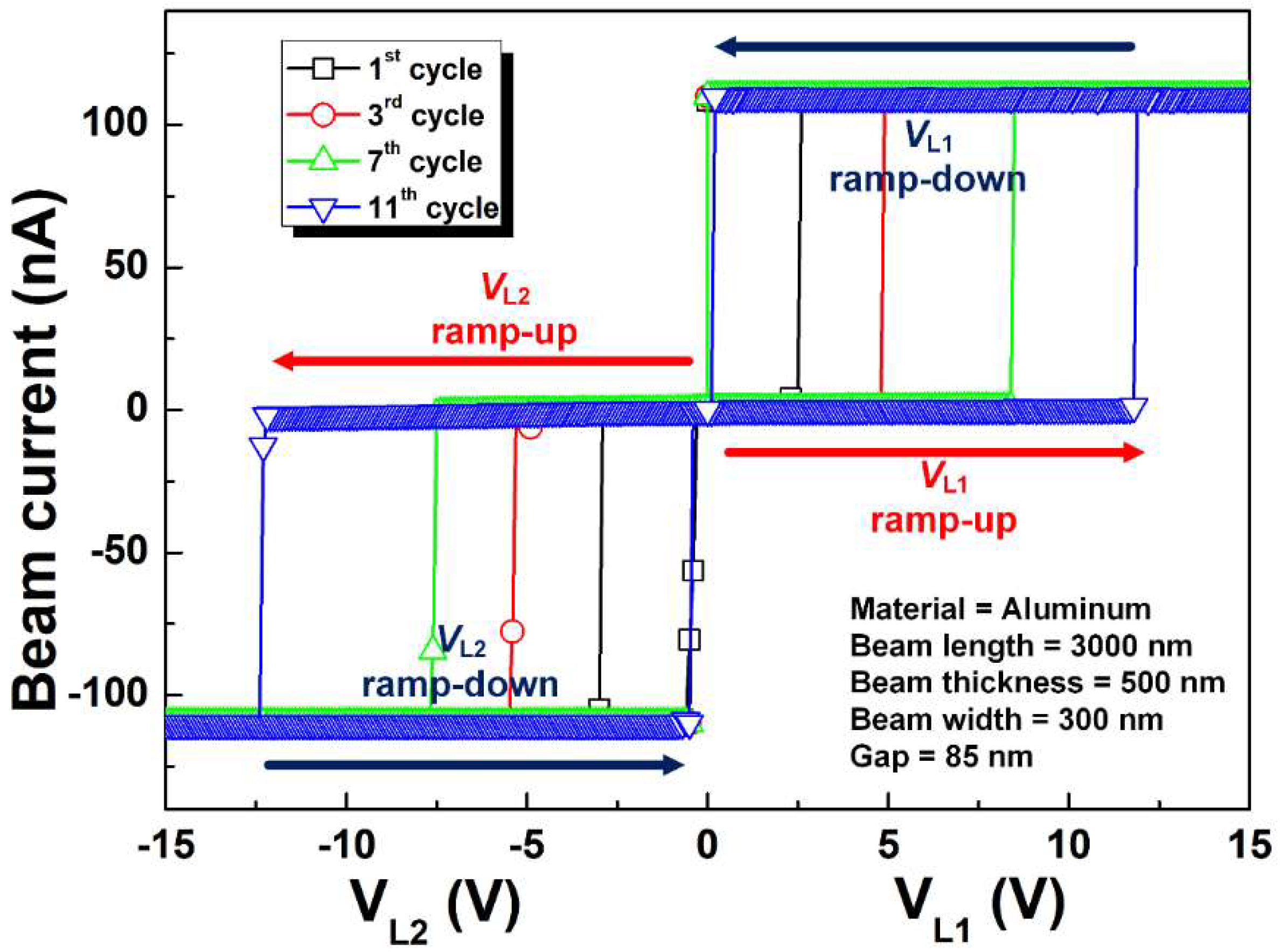

2. Encapsulation Process

3. Results and Discussion

4. Conclusions

Author Contributions

Acknowledgments

Conflicts of Interest

References

- Choi, W.Y.; Kim, Y.J. Three-Dimensional Integration of Complementary Metal-Oxide-Semiconductor-Nanoelectromechanical Hybrid Reconfigurable Circuits. IEEE Electron Device Lett. 2015, 36, 887–889. [Google Scholar] [CrossRef]

- Kwon, H.S.; Kim, S.K.; Choi, W.Y. Monolithic Three-Dimensional 65-nm CMOS-Nanoelectromechanical Reconfigurable Logic for Sub- 1.2-V Operation. IEEE Electron Device Lett. 2017, 38, 1317–1320. [Google Scholar] [CrossRef]

- Dong, C.; Chen, C.; Mitra, S.; Chen, D. Architecture and Performance Evaluation of 3D CMOS–NEM FPGA. In Proceedings of the System Level Interconnect Prediction Workshop (SLIP), San Diego, CA, USA, 5 June 2011; pp. 1–8. [Google Scholar]

- Chong, S.; Lee, B.G.; Parizi, K.B.; Provine, J.; Mitra, S.; Howe, R.T.; Wong, P. Integration of nanoelectromechanical (NEM) relays with silicon CMOS with functional CMOS–NEM circuit. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 5–7 December 2011; pp. 701–704. [Google Scholar]

- Muñoz-Gamarra, J.; Uranga, A.; Barniol, N. CMOS–NEMS Copper Switches Monolithically Integrated Using a 65nm CMOS Technology. Micromachines 2016, 7, 30. [Google Scholar] [CrossRef]

- Muñoz-Gamarra, J.; Alcaine, P.; Marigó, E.; Giner, J.; Uranga, A.; Esteve, J.; Barniol, N. Integration of NEMS resonators in a 65nm CMOS Technology. Microelectron. Eng. 2013, 110, 246–249. [Google Scholar] [CrossRef]

- Riverola, M.; Vidal-Alvarez, G.; Torres, F.; Barinol, N. 3-Terminal Tungsten CMOS–NEM Relay. In Proceedings of the Ph.D. Research in Microelectronics and Electronics (PRIME), Grenoble, France, 30 June–3 July 2014. [Google Scholar]

- Harrison, K.L.; Clary, W.A.; Provine, J.; Howe, R.T. Back-end-of-line compatible Poly-SiGe lateral nanoelectromechanical relays with multi-level interconnect. Microsyst. Technol. 2017, 23, 2125–2130. [Google Scholar] [CrossRef]

- Riverola, M.; Uranga, A.; Torres, F.; Barniol, N. Fabrication and characterization of a hammer-shaped CMOS/BEOL-embedded nanoelectromechanical (NEM) relay. Microelectron. Eng. 2018, 192, 44–51. [Google Scholar] [CrossRef]

- Magis, T.; Ballerand, S.; Comte, B.; Pollet, O. Deep Silicon Etch for Biology MEMS Fabrication: Review of Process Parameters Influence versus Chip Design. In Proceedings of the SPIE MOEMS-MEMS, San Francisco, CA, USA, 9 March 2013; p. 826120A. [Google Scholar]

- Witvrouw, A.; Bois, B.D.; Moor, P.D.; Verbist, A.; Hoof, C.V.; Bender, H.; Baert, C. Comparison between Wet HF Etching and Vapor HF Etching for Sacrificial Oxide removal. In Proceedings of the SPIE Micromachining and Microfabrication, Santa Clara, CA, USA, 25 August 2000; pp. 130–141. [Google Scholar]

- Williams, K.R.; Gupta, K.; Wasilik, M. Etch Rate for Micromachining Processing-Part Ⅱ. J. Micromech. Syst. 2003, 12, 761–778. [Google Scholar] [CrossRef]

- Bakke, T.; Schmidt, J.; Friedrichs, M.; Völker, B. Etch Stop Materials for release by vapor HF etching. In Proceedings of the MicroMechanics Europe Workshop (MME), Göteborg, Sweden, 29 January 2005; pp. 103–106. [Google Scholar]

- Winter, D.A.M.; Mulders, J.J.L. Redeposition Characteristics of Focus Ion Beam Milling for Nanofabricaiton. J. Vac. Sci. Technol. B 2007, 25, 2215–2218. [Google Scholar] [CrossRef]

- Choi, W.Y.; Osabe, T.; Liu, T.J.K. Nano-electro-mechanical nonvolatile memory (NEMory) cell design and scaling. IEEE Trans. Electron Devices 2008, 55, 3482–3488. [Google Scholar] [CrossRef]

- Soon, B.W.; Ng, E.J.; Qian, Y.; Singh, N.; Tsai, M.J.; Lee, C.K. A Bi-stable Nanoelectromechanical Nonvolatile memory based on van der Waals force. Appl. Phys. Lett. 2013, 103, 053122. [Google Scholar] [CrossRef]

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jo, H.C.; Choi, W.Y. Encapsulation of NEM Memory Switches for Monolithic-Three-Dimensional (M3D) CMOS–NEM Hybrid Circuits. Micromachines 2018, 9, 317. https://doi.org/10.3390/mi9070317

Jo HC, Choi WY. Encapsulation of NEM Memory Switches for Monolithic-Three-Dimensional (M3D) CMOS–NEM Hybrid Circuits. Micromachines. 2018; 9(7):317. https://doi.org/10.3390/mi9070317

Chicago/Turabian StyleJo, Hyun Chan, and Woo Young Choi. 2018. "Encapsulation of NEM Memory Switches for Monolithic-Three-Dimensional (M3D) CMOS–NEM Hybrid Circuits" Micromachines 9, no. 7: 317. https://doi.org/10.3390/mi9070317

APA StyleJo, H. C., & Choi, W. Y. (2018). Encapsulation of NEM Memory Switches for Monolithic-Three-Dimensional (M3D) CMOS–NEM Hybrid Circuits. Micromachines, 9(7), 317. https://doi.org/10.3390/mi9070317