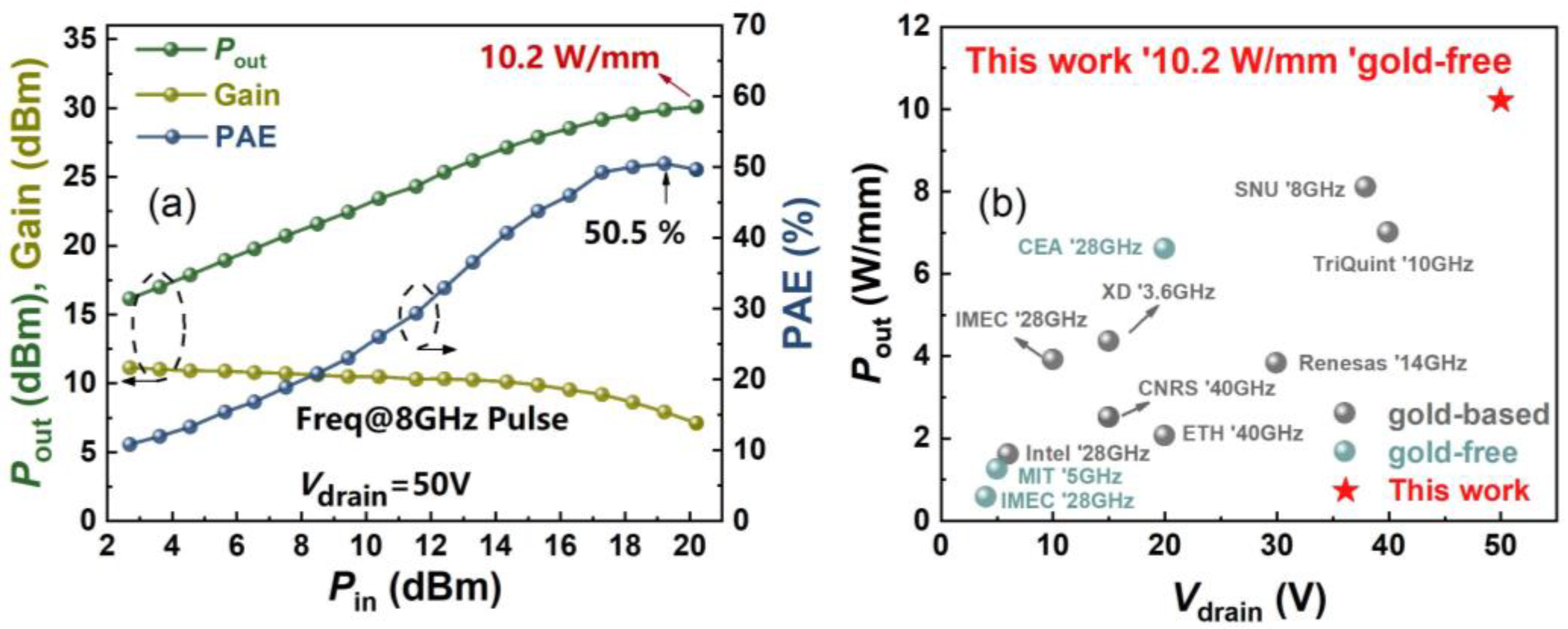

High Power Density X-Band GaN-on-Si HEMTs with 10.2 W/mm Used by Low Parasitic Gold-Free Ohmic Contact

Abstract

1. Introduction

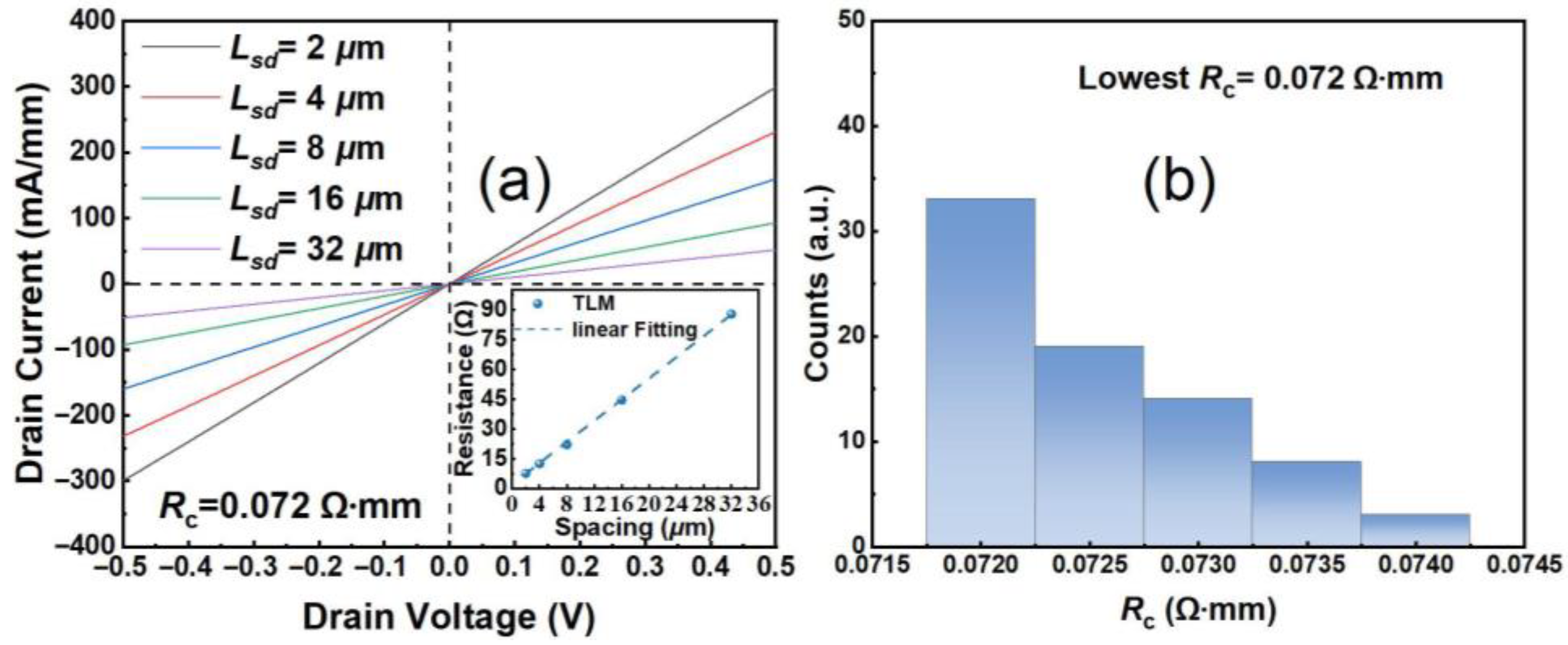

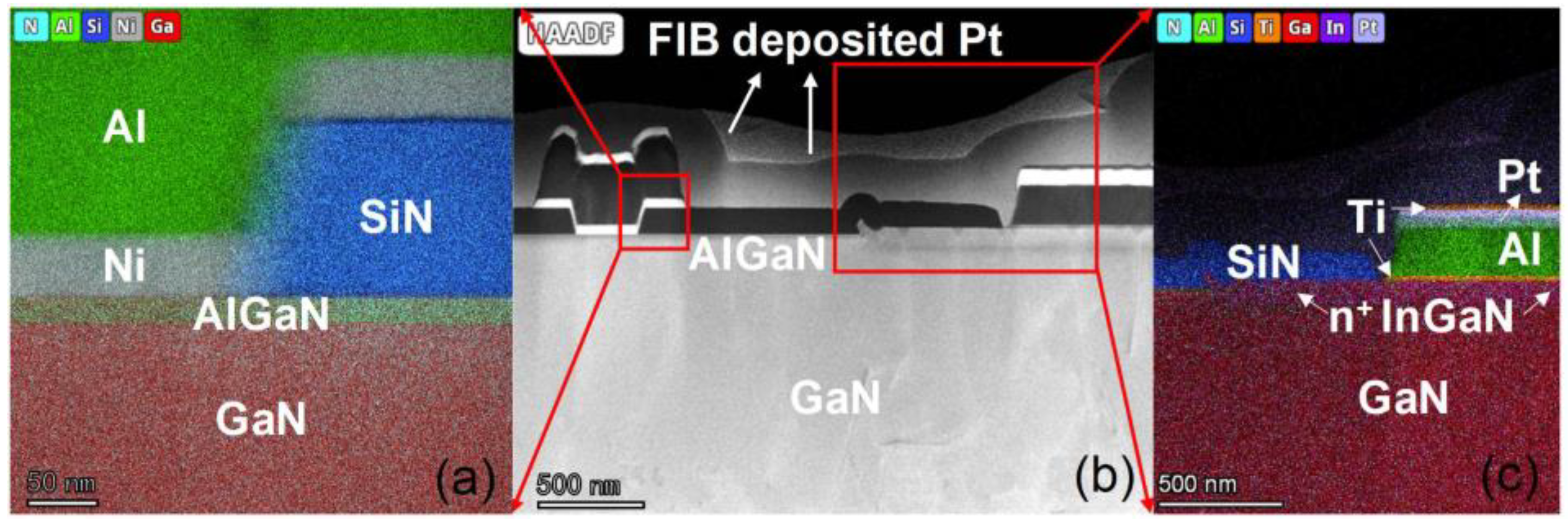

2. Material Growth and Device Fabrication

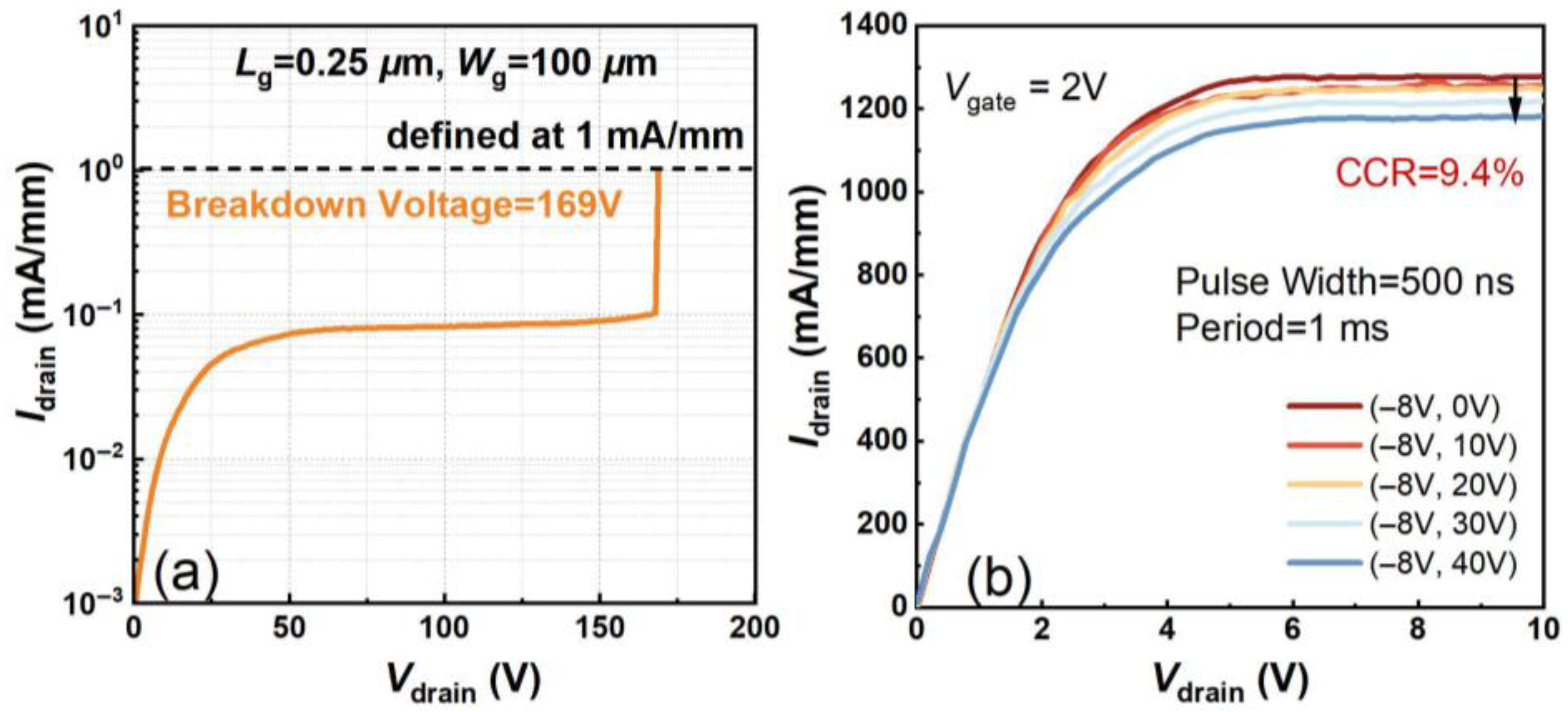

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Peralagu, U.; Alian, A.; Putcha, V.; Khaled, A.; Rodriguez, R.; Sibaja-Hernandez, A.; Chang, S.; Simoen, E.; Zhao, S.E.; De Jaeger, B.; et al. CMOS-compatible GaN-based devices on 200 mm-Si for RF applications: Integration and performance. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020; p. 17. [Google Scholar] [CrossRef]

- Then, H.W.; Huang, C.Y.; Krist, B.; Jun, K.; Lin, K.; Nidhi, N.; Michaelos, T.; Mueller, B.; Paul, R.; Peck, J.; et al. 3D heterogeneous integration of high performance high-K metal gate GaN NMOS and Si PMOS transistors on 300mm high-resistivity Si substrate for energy-efficient and compact power delivery, RF (5G and beyond) and SoC applications. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; p. 17. [Google Scholar] [CrossRef]

- Niranjan, S.; Rao, A.; Muralidharan, R.; Sen, P.; Nath, D.N. Performance Comparison of Au-Based and Au-Free AlGaN/GaN HEMT on Silicon. IEEE Trans. Electron Devices 2022, 69, 1014–1019. [Google Scholar] [CrossRef]

- Çakmak, H.; Öztürk, M.; Özbay, E.; Imer, B. Nonalloyed Ohmic Contacts in AlGaN/GaN HEMTs With MOCVD Regrowth of InGaN for Ka-Band Applications. IEEE Trans. Electron Devices 2021, 68, 1–5. [Google Scholar] [CrossRef]

- Morvan, E.; Gobil, Y.; Morisot, F.; Biscarat, J.; Charles, M.; Lugo, J.; Divay, A.; Medbouhi, M.; Charlet, I.; Delprato, J.; et al. 6.6 W/mm 200 mm CMOS compatible AlN/GaN/Si MIS-HEMT with in-situ SiN gate dielectric and low temperature ohmic contacts. In Proceedings of the 2023 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 9–13 December 2023; pp. 1–4. [Google Scholar] [CrossRef]

- Song, B.; Zhu, M.; Hu, Z.; Qi, M.; Nomoto, K.; Yan, X.; Cao, Y.; Jena, D.; Xing, H.G. Ultralow-Leakage AlGaN/GaN High Electron Mobility Transistors on Si With Non-Alloyed Regrown Ohmic Contacts. IEEE Electron Device Lett. 2016, 37, 16–19. [Google Scholar] [CrossRef]

- Qie, H.; Liu, J.; Li, Q.; Sun, Q.; Gao, H.; Sun, X.; Zhou, Y.; Yang, H. Selective area epitaxy of degenerate n-GaN for HEMT ohmic contact by MOCVD. Appl. Phys. Lett. 2022, 121, 212106. [Google Scholar] [CrossRef]

- Du, J.; Hou, B.; Yang, L.; Zhang, Y.; Zhu, Q.; Zhang, M.; Wu, M.; Huang, S.; Song, F.; Lu, H.; et al. High RF Performance E-Mode GaN-on-Si HEMTs With Pout of 5.32 W/mm Using High-Quality Ultrathin Buffer. IEEE Electron Device Lett. 2025, 46, 349–352. [Google Scholar] [CrossRef]

- Heinke, H.; Kirchner, V.; Einfeldt, S.; Hommel, D. X-ray diffraction analysis of the defect structure in epitaxial GaN. Appl. Phys. Lett. 2000, 77, 2145–2147. [Google Scholar] [CrossRef]

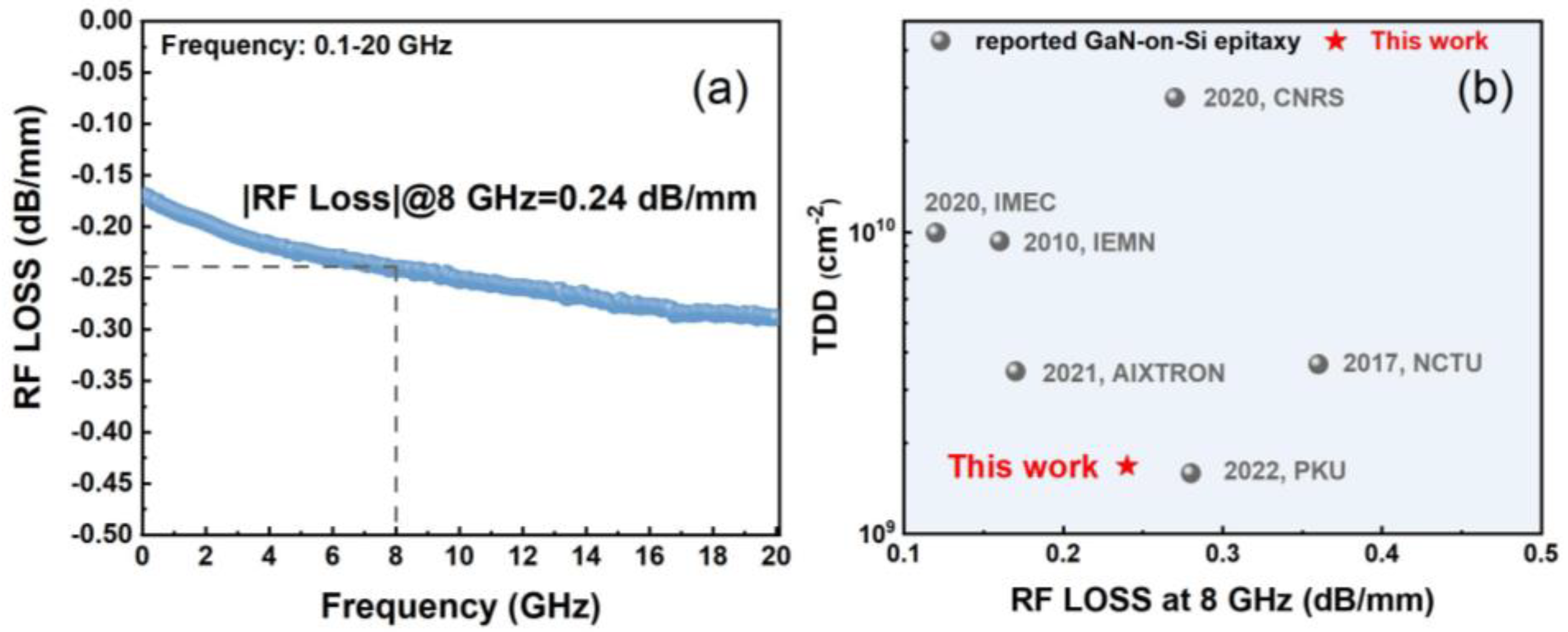

- Frayssinet, E.; Nguyen, L.; Lesecq, M.; Defance, N.; Barros, M.G.; Comyn, R.; Ngo, T.H.; Zielinski, M.; Portail, M.; Jaeger, J.-C.D.; et al. Metalorganic Chemical Vapor Phase Epitaxy Growth of Buffer Layers on 3C-SiC/Si (111) Templates for AlGaN/GaN High Electron Mobility Transistors with Low RF Losses. Phys. Status Solidi A 2020, 217, 1900760. [Google Scholar] [CrossRef]

- Chang, S.; Zhao, M.; Spampinato, V.; Franquet, A.; Chang, L. The influence of AlN nucleation layer on RF transmission loss of GaN buffer on high resistivity Si (111) substrate. Semicond. Sci. Technol. 2020, 35, 035029. [Google Scholar] [CrossRef]

- Lecourt, F.; Douvry, Y.; Defrance, N.; Hoel, V.; Cordier, Y.; DeJaeger, J.C. Analysis of AlGaN/GaN Epi-material on Resistive Si(111) Substrate for MMIC Applications in Millimeter Wave Range. In Proceedings of the 2010 5th European Microwave Integrated Circuits Conf. (EuMIC, 2010), Paris, France, 27–28 September 2010; p. 33. [Google Scholar]

- Mauder, C.; Hahn, H.; Marx, M.; Gao, Z.; Oligschlaeger, R.; Zweipfennig, T.; Nochlak, A.; Negra, R.; Kalisch, H.; Vescan, A.; et al. Investigation and reduction of RF loss induced by Al diffusion at the AlN/Si(111) interface in GaN-based HEMT buffer stacks. Semicond. Sci. Technol. 2021, 36, 075008. [Google Scholar] [CrossRef]

- Luong, T.T.; Lumbantoruan, F.; Chen, Y.-Y.; Ho, Y.-T.; Weng, Y.-C.; Lin, Y.-C.; Chang, S.; Chang, E.-Y. RF loss mechanisms in GaN-based high-electron-mobility-transistor on silicon: Role of an inversion channel at the AlN/Si interface. Phys. Status Solidi A 2017, 214, 1600944.1–1600944.7. [Google Scholar] [CrossRef]

- Ma, C.; Yang, X.; Shen, J.; Liu, D.; Cai, Z.; Chen, Z.; Tang, J.; Sang, L.; Xu, F.; Wang, X.; et al. Low RF loss and low dislocation density of GaN grown on high-resistivity Si substrates. Appl. Phys. Express 2022, 15, 31003.1–31003.4. [Google Scholar] [CrossRef]

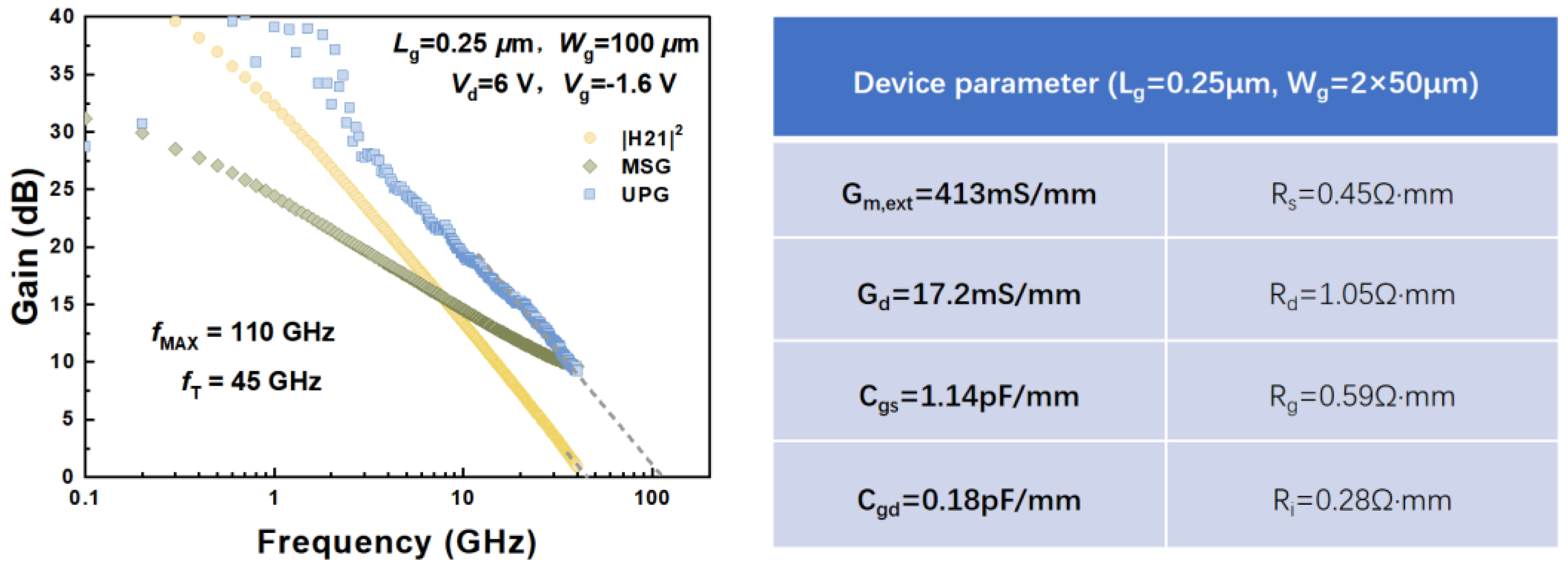

- Jarndal, A.; Kompa, G. A new small-signal modeling approach applied to GaN devices. IEEE Trans. Microwave Theory Tech. 2005, 53, 3440. [Google Scholar] [CrossRef]

- Lee, M.-S.; Kim, D.; Eom, S.; Cha, H.-Y.; Seo, K.-S. A Compact 30-W AlGaN/GaN HEMTs on Silicon Substrate With Output Power Density of 8.1 W/mm at 8 GHz. IEEE Electron Device Lett. 2014, 35, 995–997. [Google Scholar] [CrossRef]

- Dumka, D.C.; Lee, C.; Tserng, H.Q.; Saunier, P.; Kumar, M. AlGaN/GaN HEMTs on Si substrate with 7 W/mm output power density at 10 GHz. Electron. Lett. 2004, 40, 1023–1024. [Google Scholar] [CrossRef]

- Then, H.W.; Radosavljevic, M.; Jun, K.; Koirala, P.; Krist, B.; Talukdar, T.; Thomas, N.; Fischer, P. Gallium Nitride and Silicon Transistors on 300 mm Silicon Wafers Enabled by 3-D Monolithic Heterogeneous Integration. IEEE Trans. Electron Devices 2020, 67, 5306–5314. [Google Scholar] [CrossRef]

- Murase, Y.; Asano, K.; Takenaka, I.; Ando, Y.; Takahashi, H.; Sasaoka, C. T-Shaped Gate GaN HFETs on Si With Improved Breakdown Voltage and fMAX. IEEE Electron Device Lett. 2014, 35, 524–526. [Google Scholar] [CrossRef]

- Zhou, Y.; Zhu, J.; Zhang, B.; Wang, Q.; Qin, L.; Wei, L.; Li, M.; Chen, B.; Zhang, M.; Hao, Y.; et al. High RF Performance AlGaN/GaN HEMTs on 6-in Si Substrate for Low Voltage Applications. IEEE Electron Device Lett. 2025, 46, 549–552. [Google Scholar] [CrossRef]

- ElKashlan, R.; Khaled, A.; Yadav, S.; Yu, H.; Peralagu, U.; Alian, A.; Collaert, N.; Wambacq, P.; Parvais, B. mm-Wave GaN-on-Si HEMTs with a P SAT of 3.9 W/mm at 28 GHz. In Proceedings of the 2023 IEEE/MTT-S International Microwave Symposium-IMS 2023, San Diego, CA, USA, 11–16 June 2023; pp. 24–27. [Google Scholar]

- Medjdoub, F.; Zegaoui, M.; Grimbert, B.; Ducatteau, D.; Rolland, N.; Rolland, P.A. First Demonstration of High-Power GaN-on-Silicon Transistors at 40 GHz. IEEE Electron Device Lett. 2012, 33, 1168–1170. [Google Scholar] [CrossRef]

- Marti, D.; Tirelli, S.; Alt, A.R.; Roberts, J.; Bolognesi, C.R. 150-GHz Cutoff Frequencies and 2-W/mm Output Power at 40 GHz in a Millimeter-Wave AlGaN/GaN HEMT Technology on Silicon. IEEE Electron Device Lett. 2012, 33, 1372–1374. [Google Scholar] [CrossRef]

- Xie, H.; Liu, Z.; Hu, W.; Gao, Y.; Lee, K.E.; Guo, Y.-X.; Ng, G.I. CMOS-Compatible InAlN/GaN HEMTs on Silicon for RF Power Amplifiers in 5G Mobile SoCs. In Proceedings of the 2021 IEEE MTT-S International Microwave Workshop Series on Advanced Materials and Processes for RF and THz Applications (IMWS-AMP), Chongqing, China, 15–17 November 2021; pp. 397–399. [Google Scholar] [CrossRef]

- Parvais, B.; Alian, A.; Peralagu, U.; Rodriguez, R.; Yadav, S.; Khaled, A.; ElKashlan, R.Y.; Putcha, V.; Sibaja-Hernandez, A.; Zhao, M.; et al. GaN-on-Si mm-wave RF Devices Integrated in a 200mm CMOS Compatible 3-Level Cu BEOL. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020; pp. 8.1.1–8.1.4. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Du, J.; Lu, H.; Hou, B.; Yang, L.; Zhang, M.; Wu, M.; Chen, K.; Pan, T.; Chen, Y.; Liu, H.; et al. High Power Density X-Band GaN-on-Si HEMTs with 10.2 W/mm Used by Low Parasitic Gold-Free Ohmic Contact. Micromachines 2025, 16, 1067. https://doi.org/10.3390/mi16091067

Du J, Lu H, Hou B, Yang L, Zhang M, Wu M, Chen K, Pan T, Chen Y, Liu H, et al. High Power Density X-Band GaN-on-Si HEMTs with 10.2 W/mm Used by Low Parasitic Gold-Free Ohmic Contact. Micromachines. 2025; 16(9):1067. https://doi.org/10.3390/mi16091067

Chicago/Turabian StyleDu, Jiale, Hao Lu, Bin Hou, Ling Yang, Meng Zhang, Mei Wu, Kaiwen Chen, Tianqi Pan, Yifan Chen, Hailin Liu, and et al. 2025. "High Power Density X-Band GaN-on-Si HEMTs with 10.2 W/mm Used by Low Parasitic Gold-Free Ohmic Contact" Micromachines 16, no. 9: 1067. https://doi.org/10.3390/mi16091067

APA StyleDu, J., Lu, H., Hou, B., Yang, L., Zhang, M., Wu, M., Chen, K., Pan, T., Chen, Y., Liu, H., Chang, Q., Ma, X., & Hao, Y. (2025). High Power Density X-Band GaN-on-Si HEMTs with 10.2 W/mm Used by Low Parasitic Gold-Free Ohmic Contact. Micromachines, 16(9), 1067. https://doi.org/10.3390/mi16091067