Encapsulation Process and Dynamic Characterization of SiC Half-Bridge Power Module: Electro-Thermal Co-Design and Experimental Validation

Abstract

1. Introduction

- Higher switching frequencies: SiC modules can operate at frequencies significantly higher than IGBTs (typically <20 kHz for optimal IGBT performance vs. up to 100 kHz or MHz range for SiC). This enables the use of smaller, lighter passive components (inductors, capacitors, and transformers), substantially reducing system volume/weight and increasing power density [2].

- Lower switching losses: SiC exhibits switching losses approximately one order of magnitude lower than comparable IGBTs [3]. At identical switching frequencies, this translates to significantly higher system efficiency. Reduced switching losses also lower cooling requirements, allowing for smaller, lighter heat sinks and reduced thermal management costs.

- Superior high-temperature performance: SiC devices support significantly higher maximum junction temperatures (Tjs) than silicon devices (typically 175–200 °C+ for SiC vs. 150–175 °C for IGBTs). SiC modules can reliably operate at higher ambient temperatures, deliver increased power output under equivalent cooling conditions, exhibit superior high-temperature stability, and significantly reduce thermal management complexity and cost [4].

- Higher system efficiency and power density: SiC modules enable power conversion systems with higher overall efficiency, smaller size, reduced weight, and greater power density. This is critical for applications such as electric vehicles, renewable energy (PV inverters and wind converters), data center power supplies, industrial motor drives, and charging stations [5].

- Dynamic switching stress: The high switching speed of SiC devices induces significant voltage overshoot and electromagnetic interference (EMI) [6]. The switching transient process exhibits extremely high di/dt (current slew rate) and dv/dt (voltage slew rate), causing turn-off voltage spikes exceeding 30% of the bus voltage. This not only exacerbates EMI but also risks gate oscillations and potential device breakdown.

- Thermal management bottleneck: Under high power density operation, non-uniform thermal distribution within the module compromises system reliability. Current research predominantly focuses on static parameter testing of discrete SiC devices (e.g., using Rogowski coils for current sampling), leaving a significant gap in the co-analysis of static and dynamic behavior for half-bridge power modules. Therefore, this study employs double-pulse testing combined with multiphysics simulation to conduct an in-depth investigation into the switching characteristics and thermal behavior of SiC half-bridge power modules.

2. Hardware and Software Design of Double-Pulse Test Board for SiC Half-Bridge Power Module

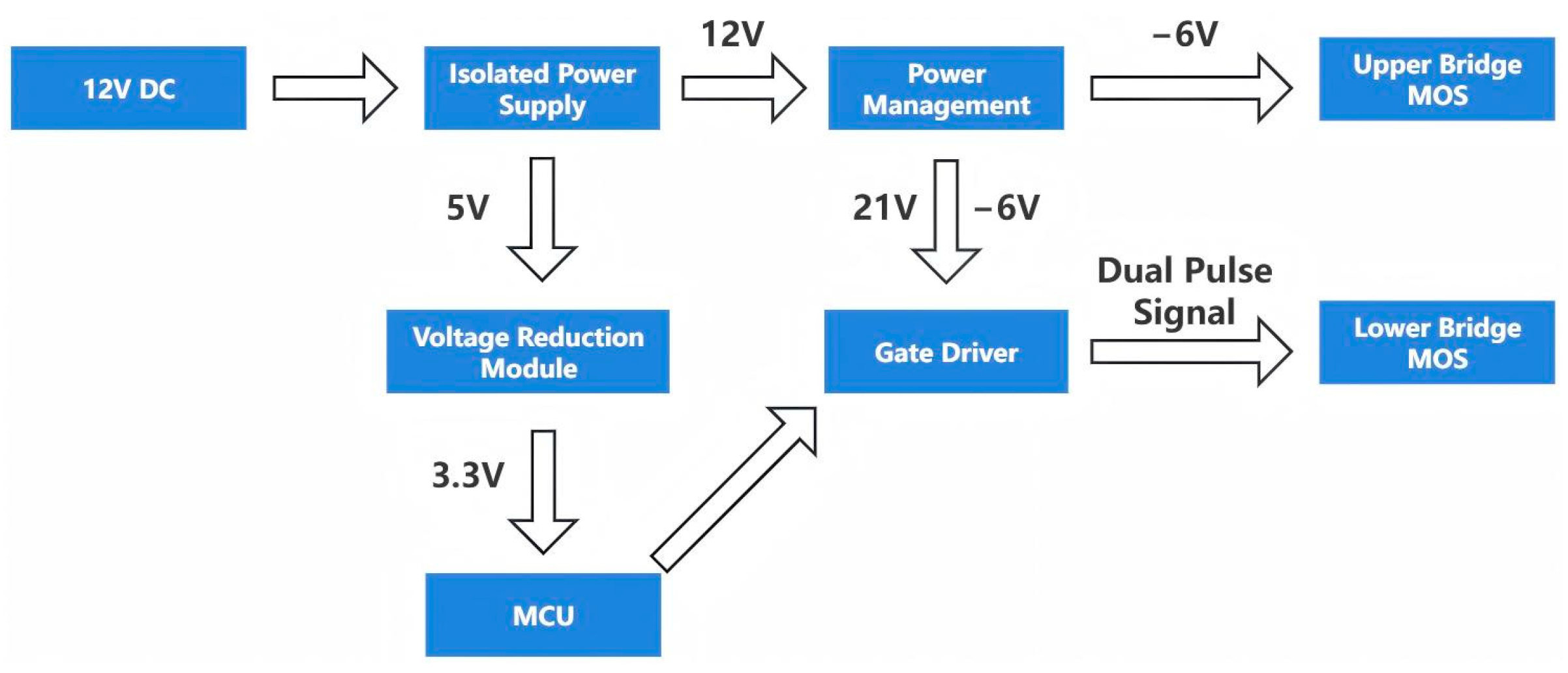

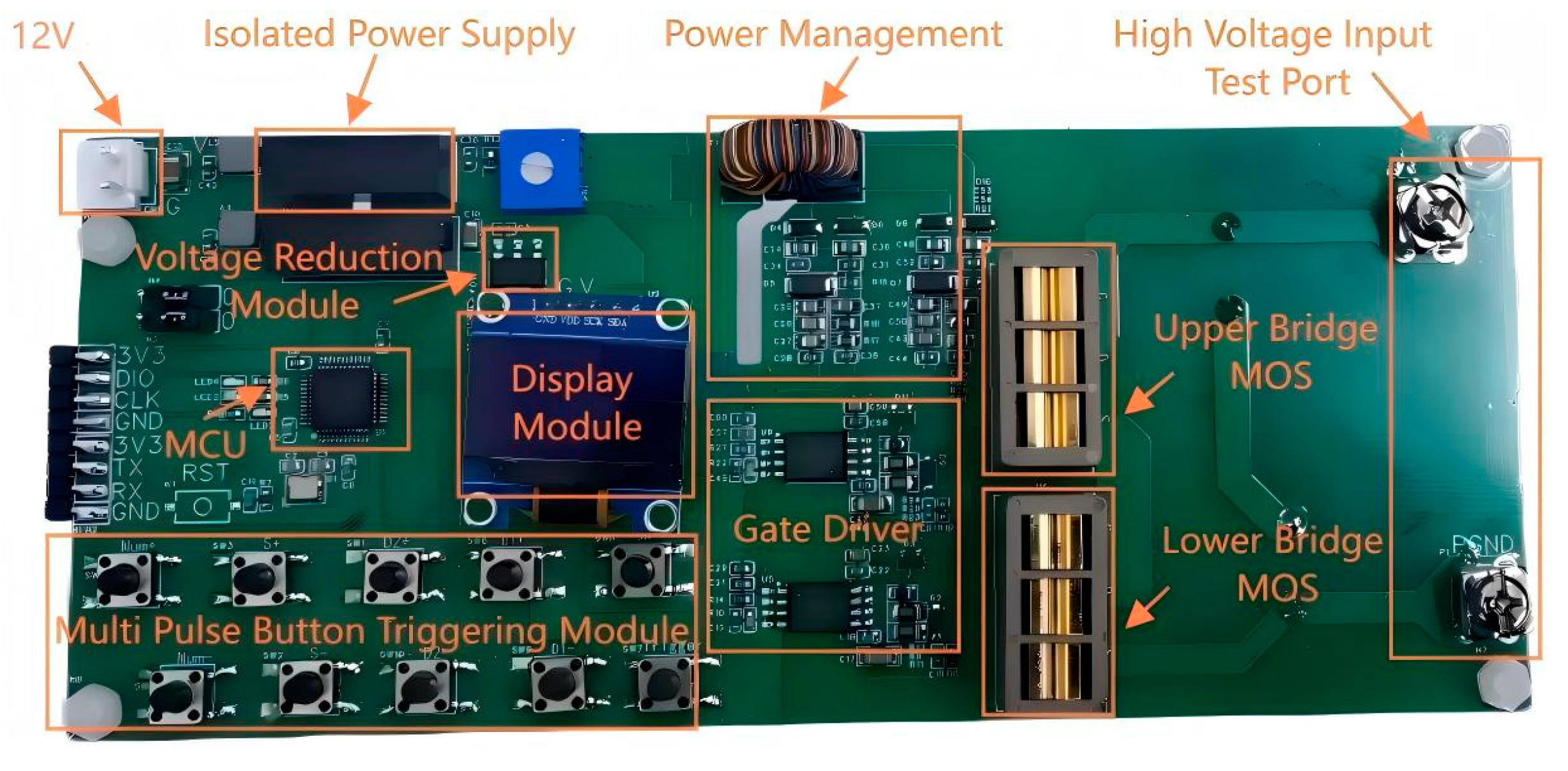

2.1. Hardware Design of Double-Pulse Test Board

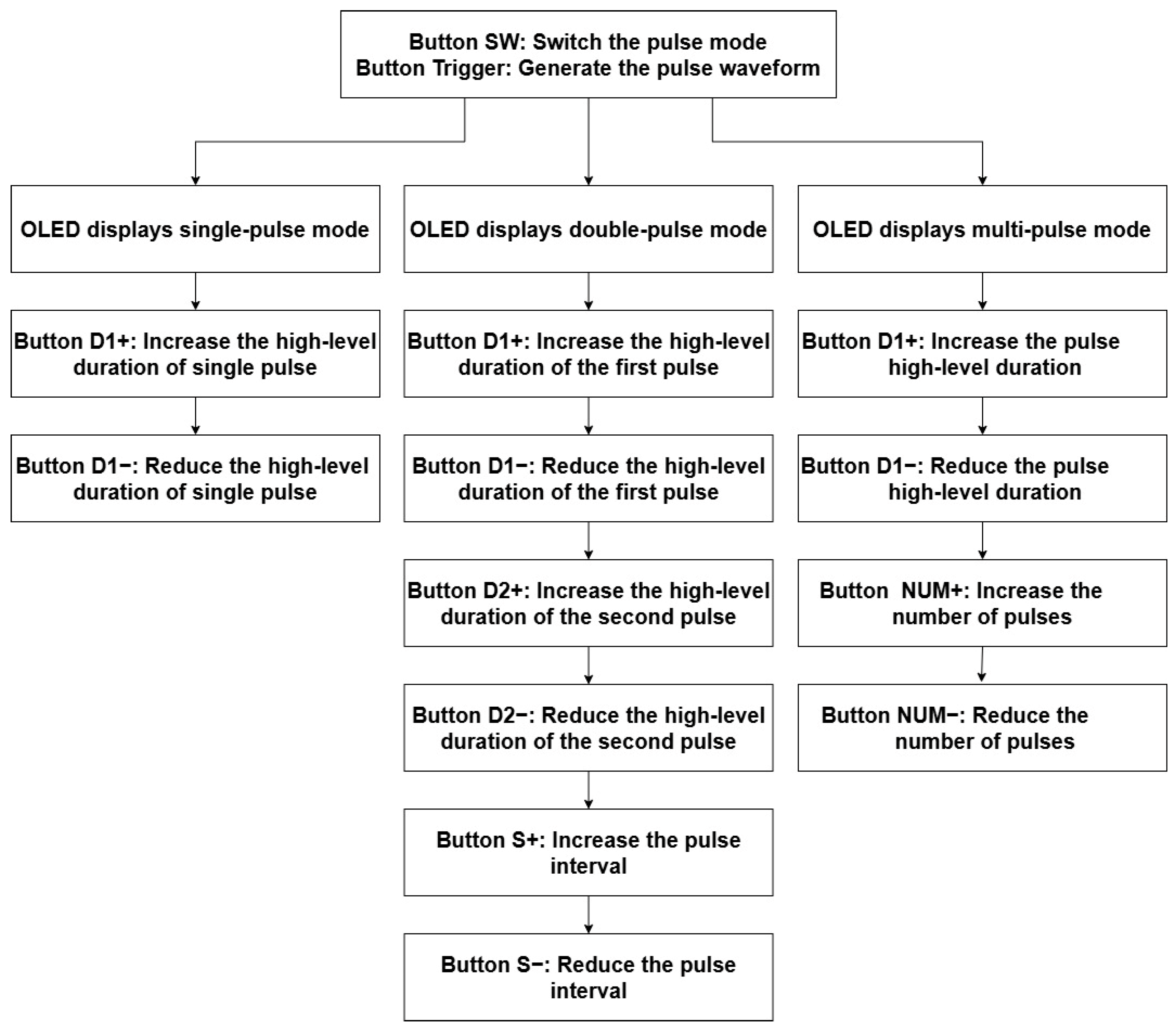

2.2. Software Program Design of Double-Pulse Test Board

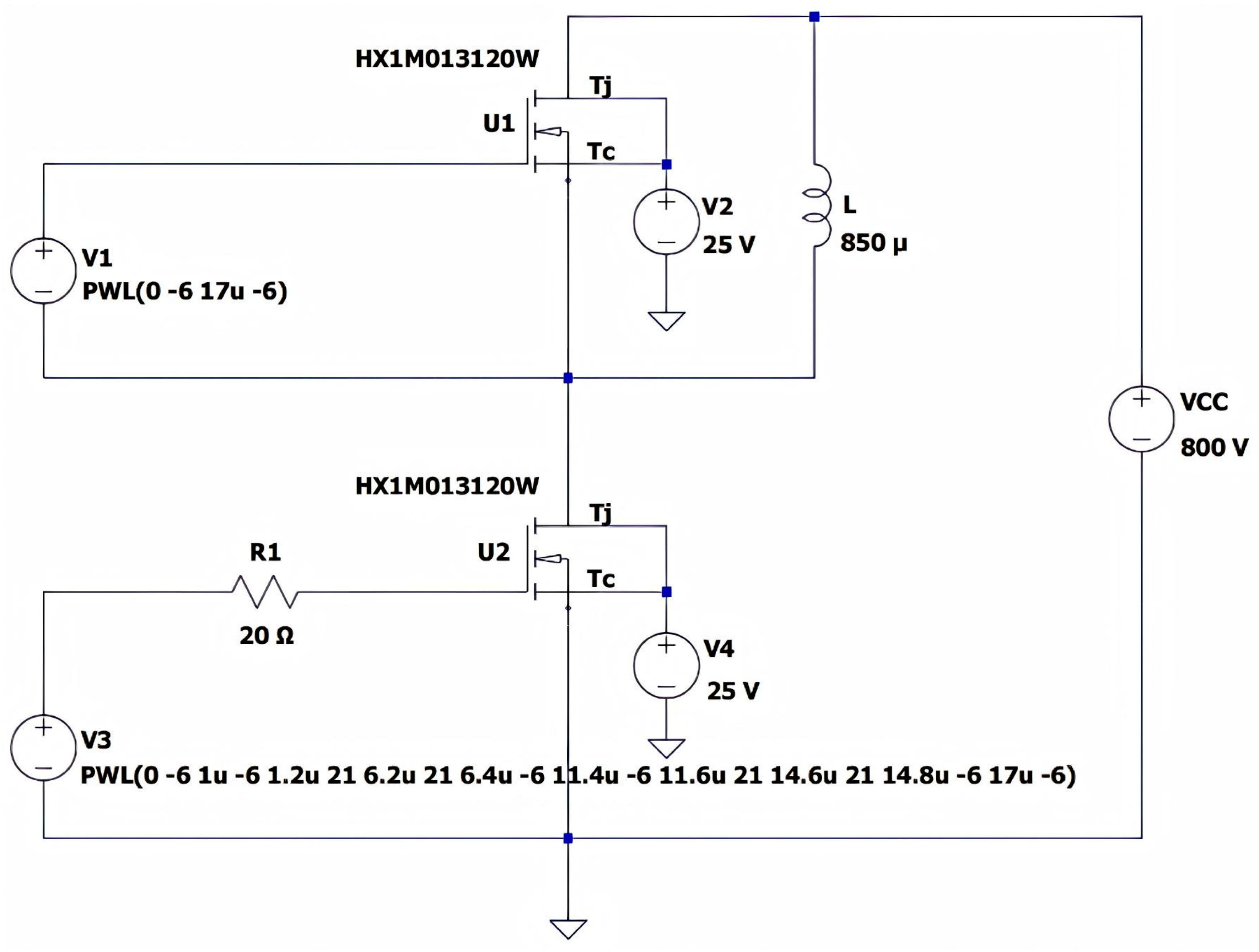

2.3. LTspice Simulation Analysis of Double-Pulse Test Circuit

- 1.

- The first pulse duration

- 2.

- The pulse interval

- 3.

- The second pulse duration

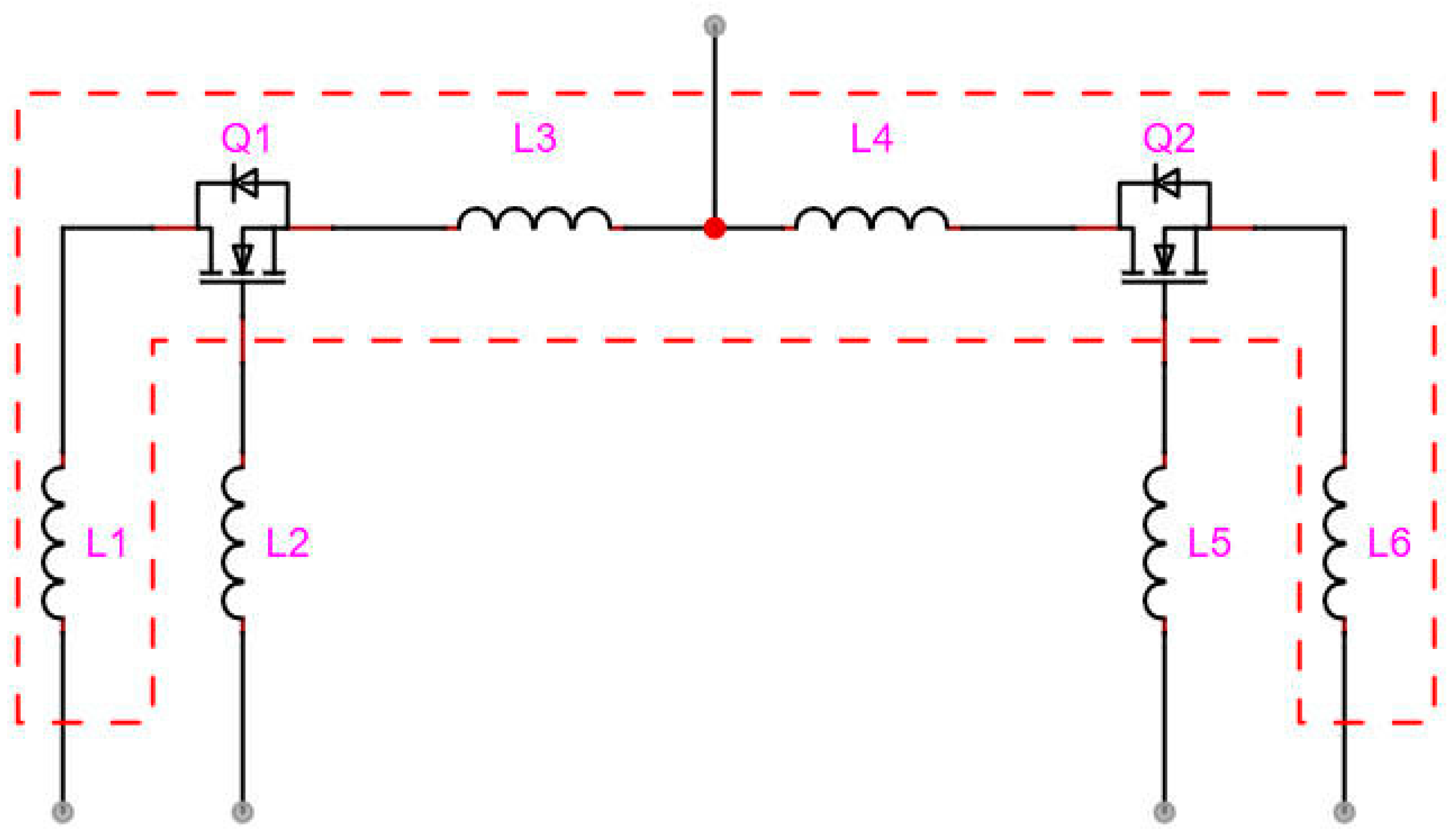

2.4. Q3D-Based Extraction of Parasitic Inductance in SiC Half-Bridge Modules

3. COMSOL Steady-State Thermal Simulation Analysis of SiC Half-Bridge Power Module

3.1. Construction of COMSOL Thermal Simulation Model

3.2. Thermal Field Boundary Condition Setting

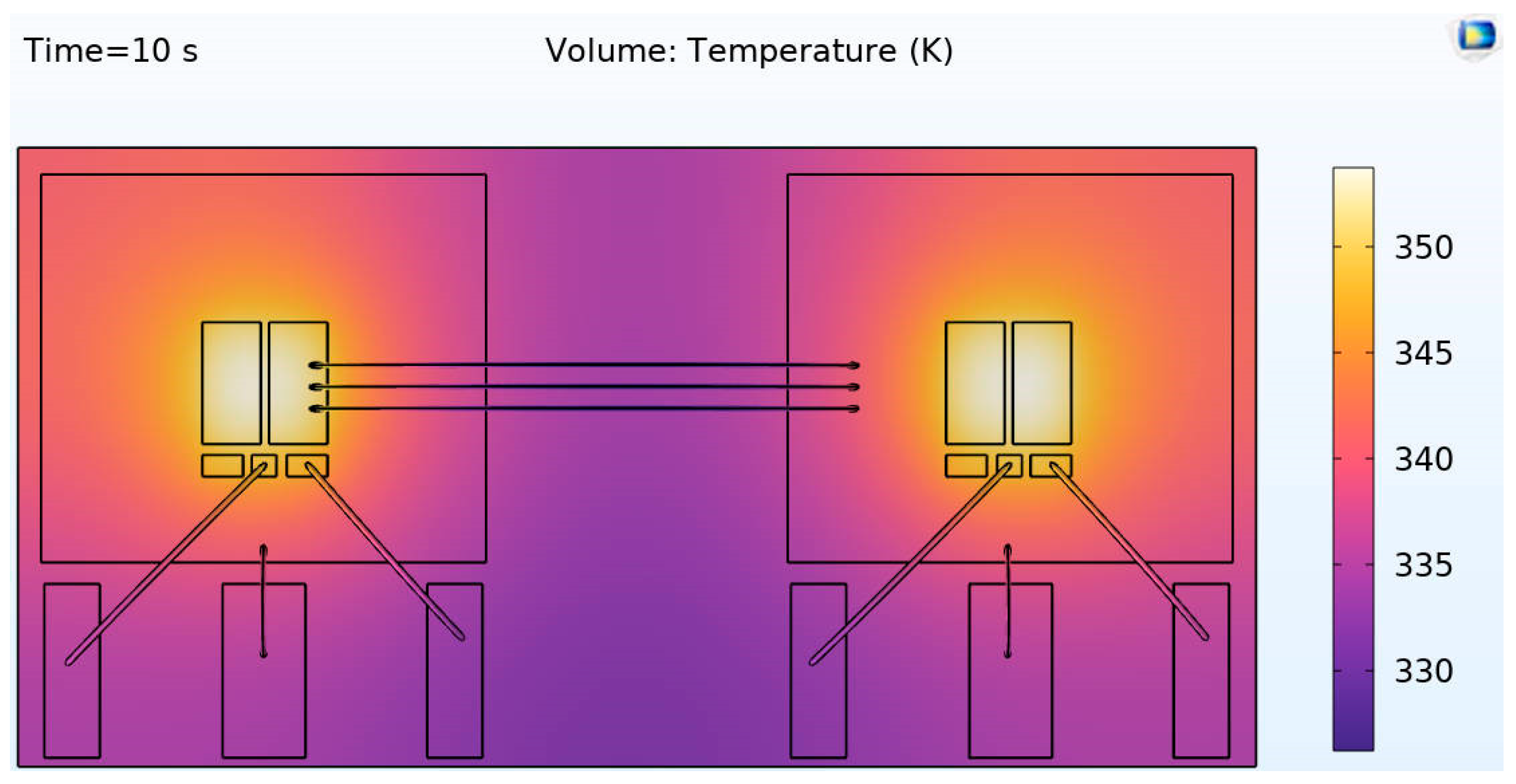

3.3. The Analysis of Thermal–Physical Field Simulation Results

4. Packaging Process Preparation Flow of the SiC Half-Bridge Power Module

4.1. Conductive Adhesive Sintering Experiment of SiC MOS Wafers

4.2. High-Temperature Baking Experiment

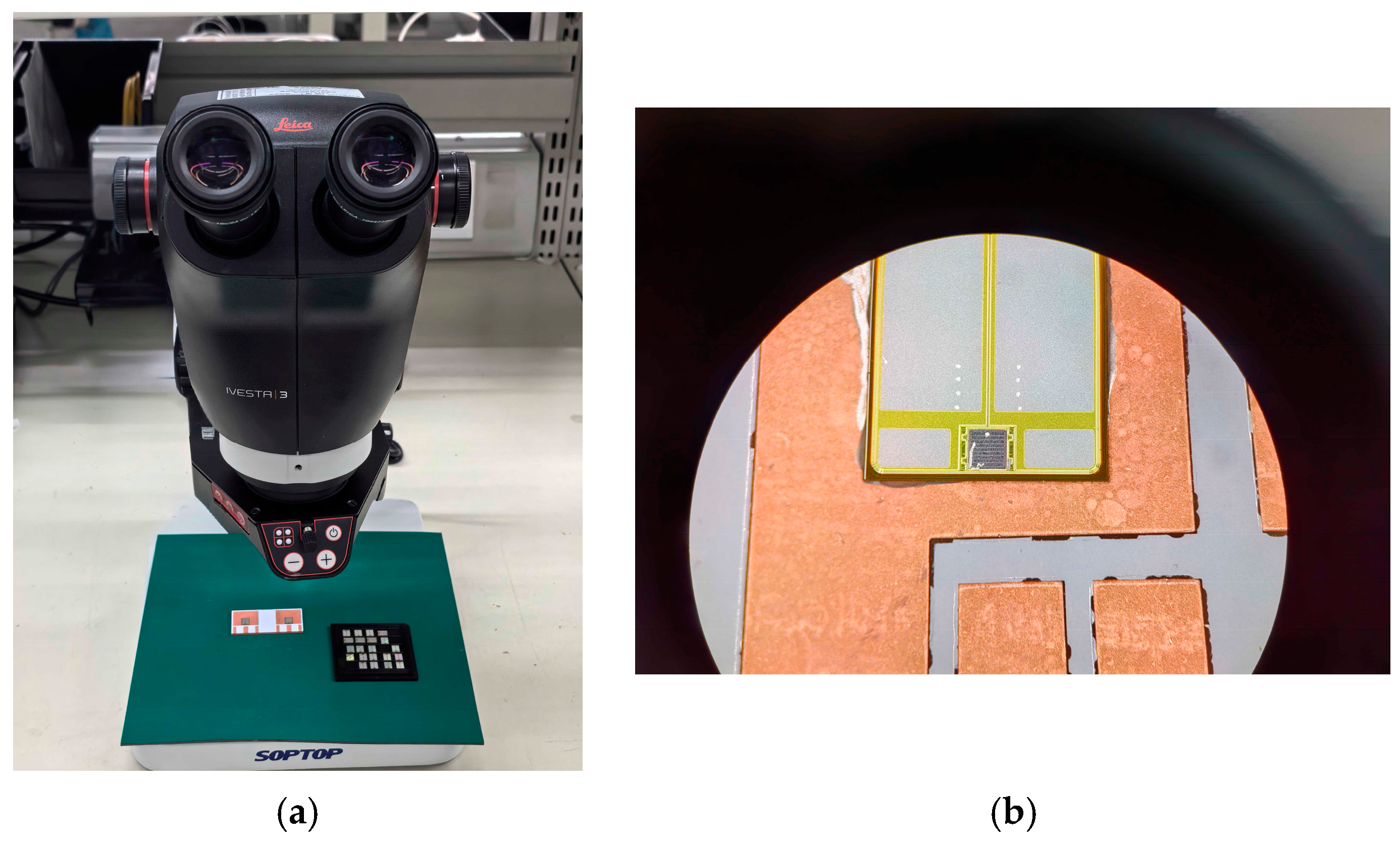

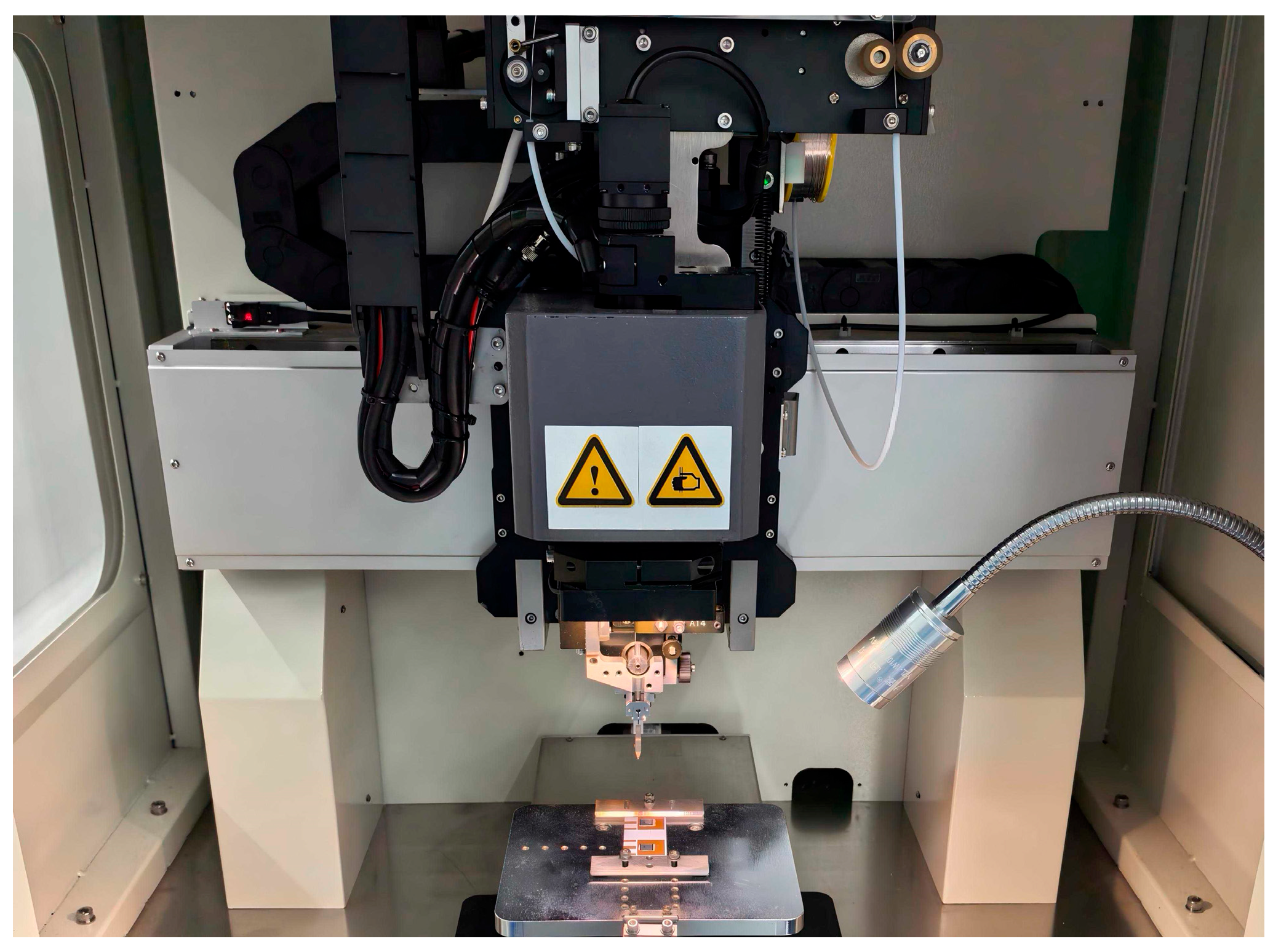

4.3. Aluminum Wire Bonding Experiment

5. Dynamic Characteristic Testing and Analysis of SiC Half-Bridge Power Module

5.1. Double-Pulse Test Experimental Platform

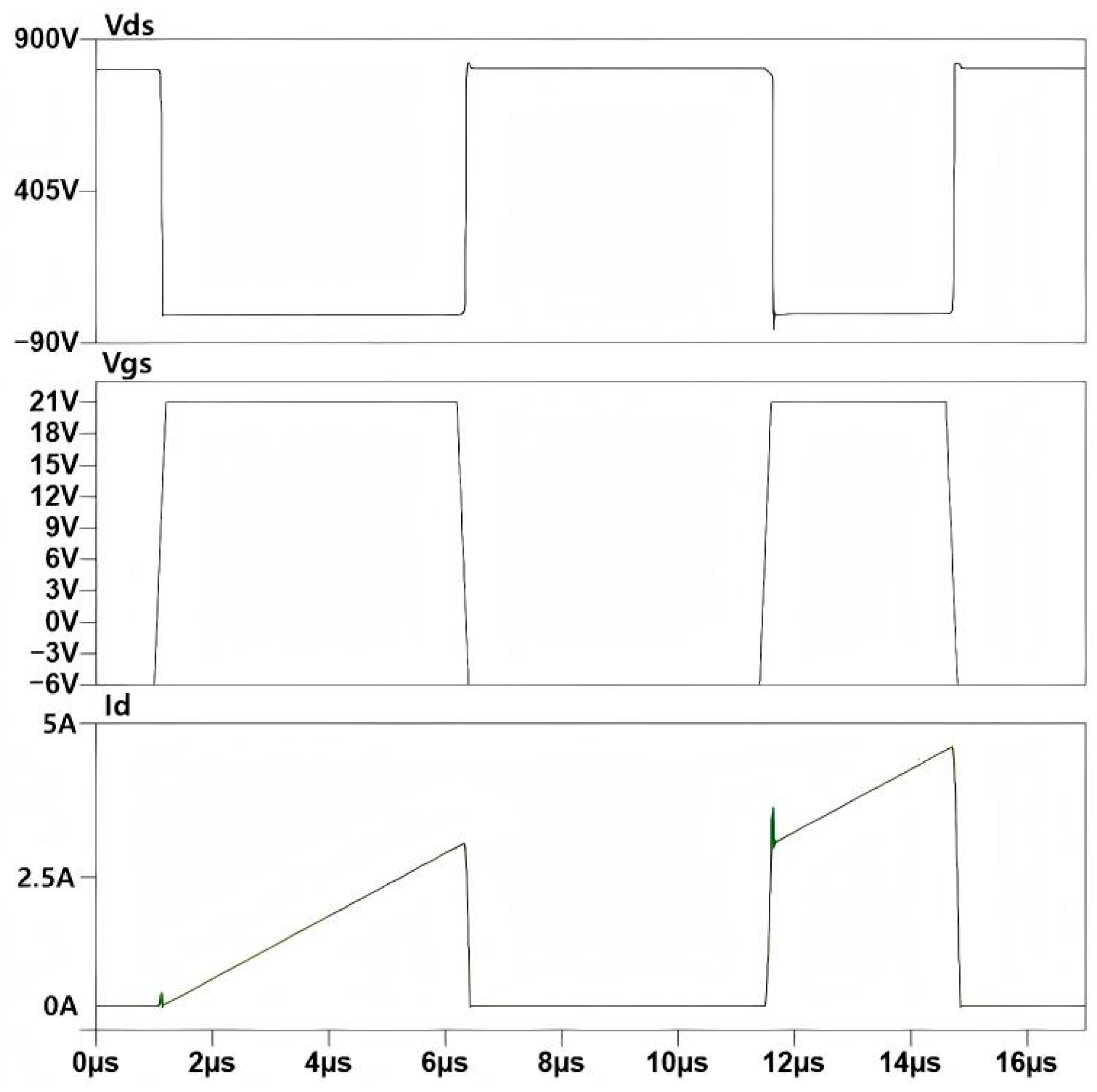

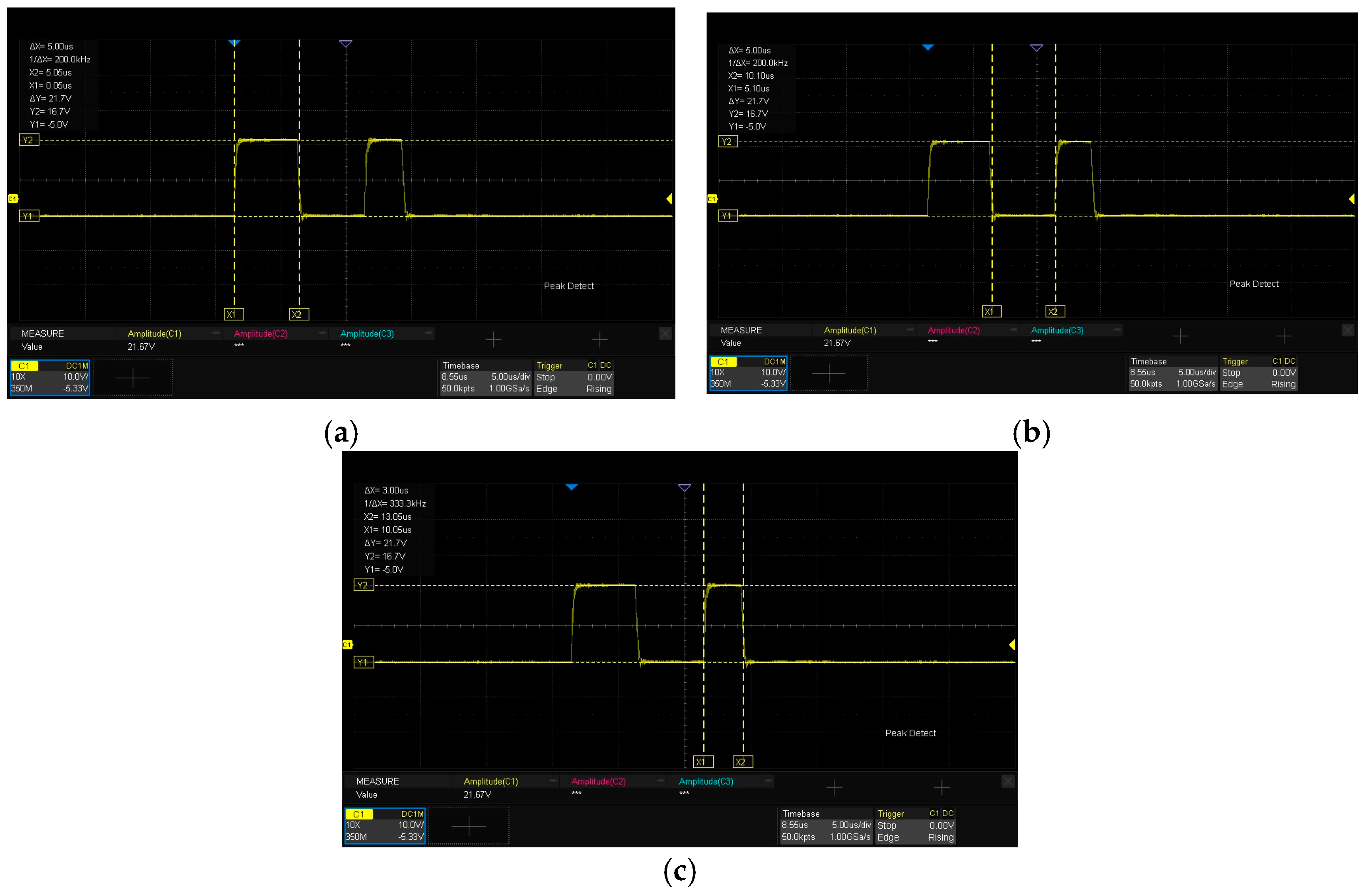

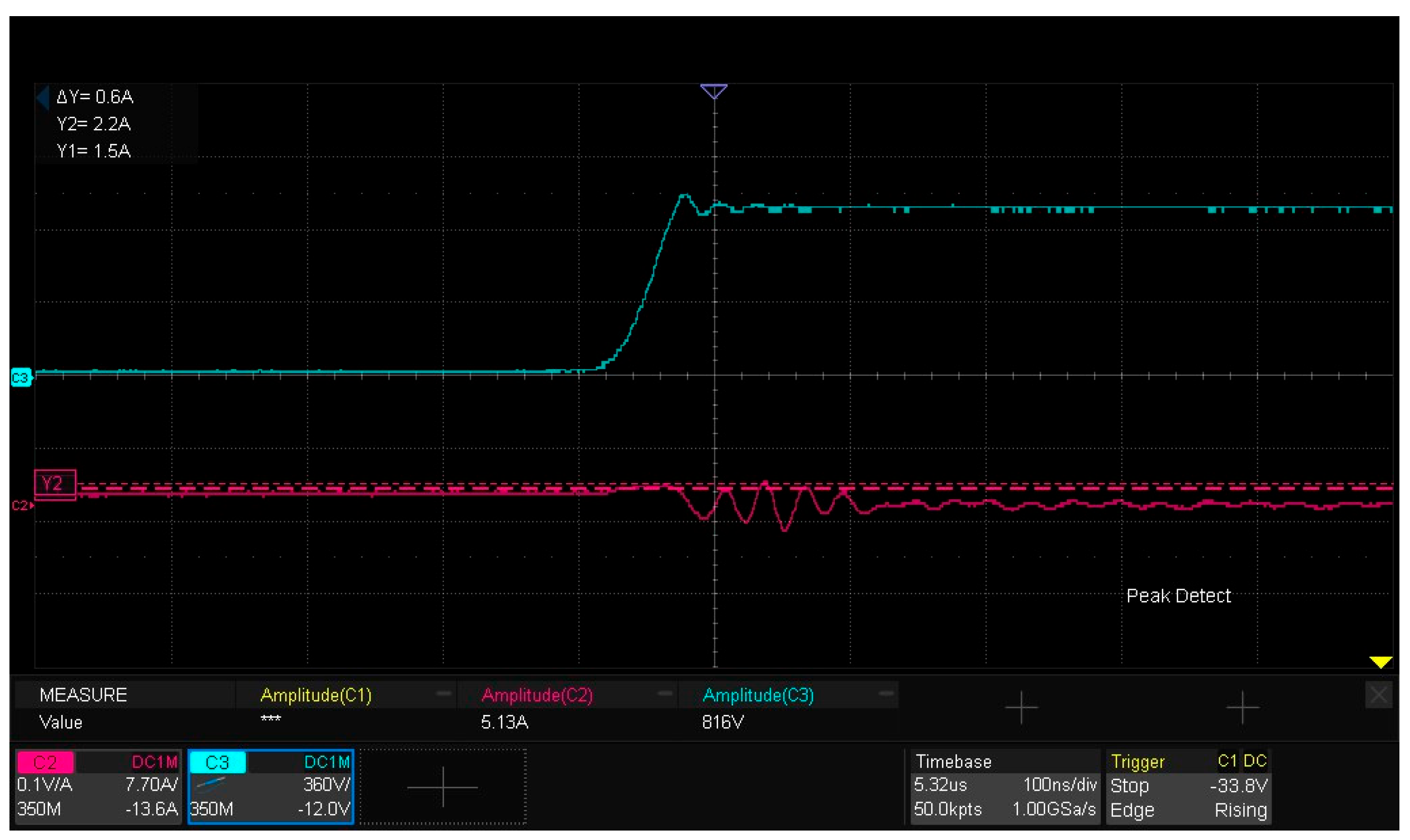

5.2. Waveform Analysis of Double-Pulse Test

5.3. Time Analysis of Double-Pulse Test

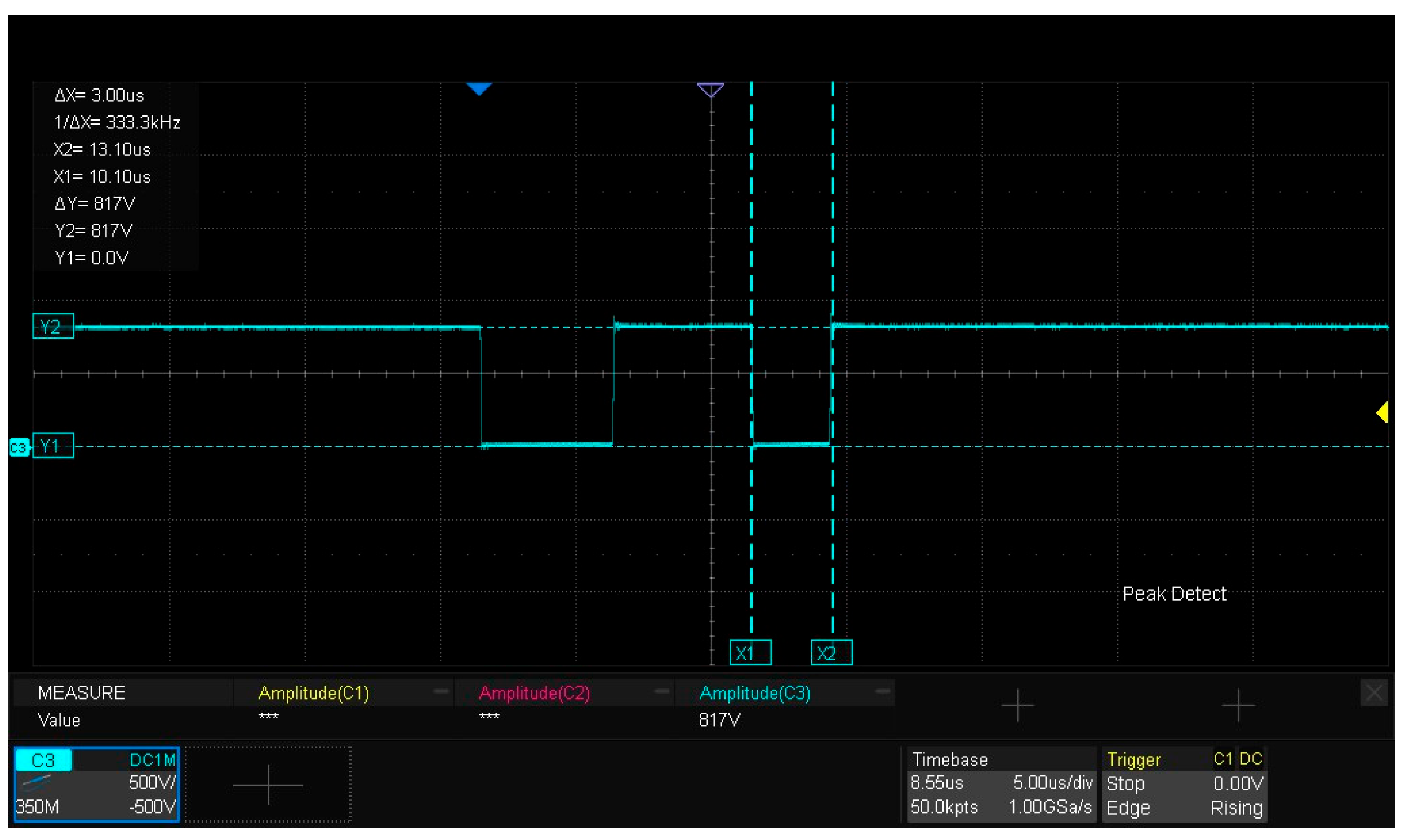

5.4. Waveform Analysis of Drain–Source Voltage of Lower-Bridge MOS

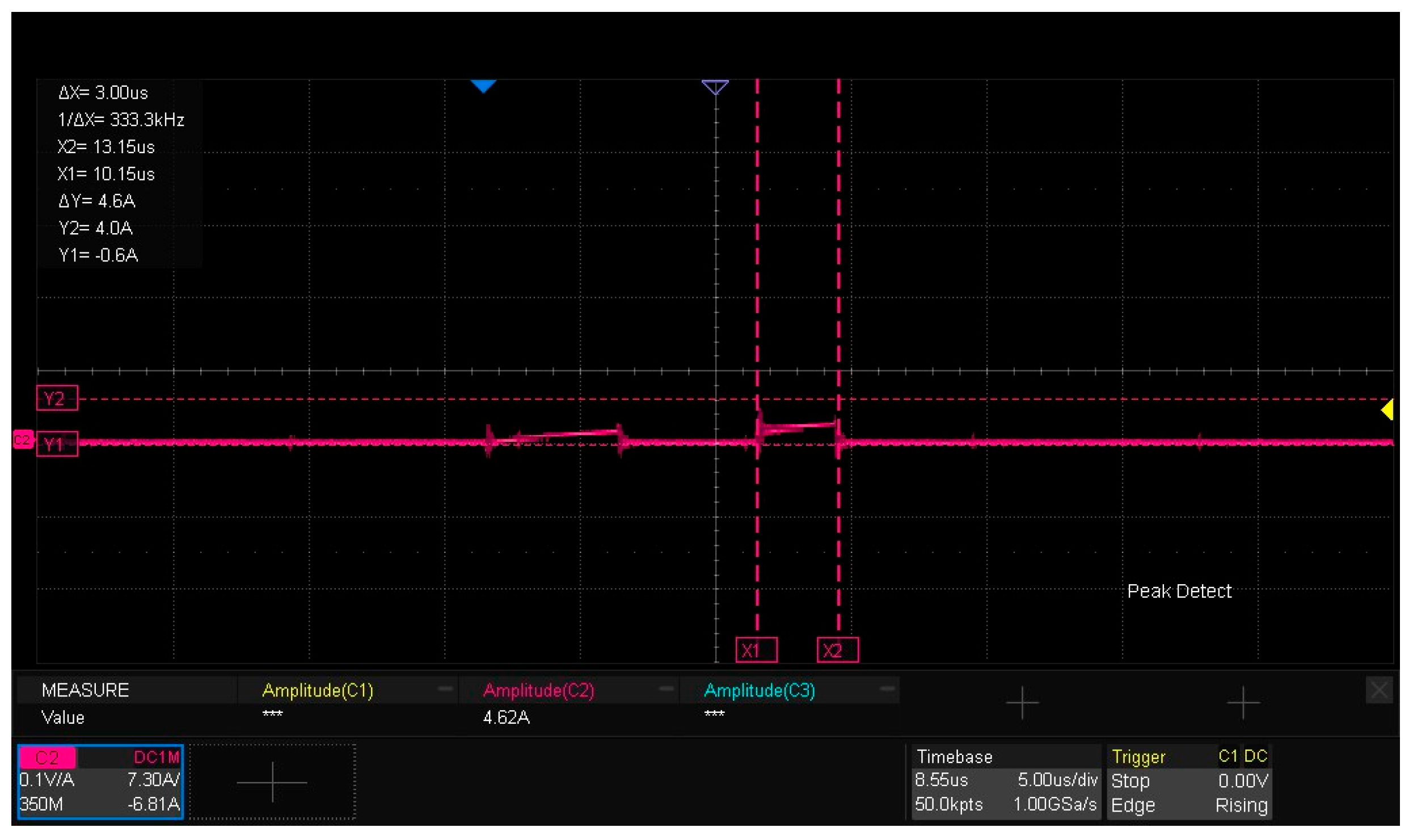

5.5. Waveform Analysis of Drain Current of Lower-Bridge MOS

5.6. Characterization of Turn-On and Turn-Off Waveforms

6. Conclusions

- Dynamic switching characterization: A multifunctional double-pulse test board was designed to quantitatively analyze the dynamic switching characteristics of the SiC half-bridge power module under an 800 V operating condition. Experimental validation confirmed that the packaged module successfully withstood the 800 V high-voltage test, with the measured drain current (4.62 A) exhibiting a deviation of <0.65% from the simulated value (4.65 A). This demonstrates the accuracy of the electro-thermal co-design approach.

- Thermal performance analysis: A COMSOL-based thermal simulation model was established to evaluate the temperature distribution of the module under a power loss of 117.6 W. The simulation revealed a junction temperature gradient of 55 °C, with localized hotspots concentrated at the SiC wafers. The maximum junction temperature (80 °C) remained significantly below the safety threshold (175 °C), validating the thermal reliability of the module.

- Packaging process optimization: Key packaging parameters were quantified for reliability enhancement, including conductive adhesive sintering (S820-F680, thermal conductivity: 39.3 W/(m·K)), high-temperature baking at 150 °C, aluminum wire bonding (15-mil wire diameter, ultrasonic power = 500 mW, and bonding force = 500 g), and microscopic examination (Leica IVesta 3, 55× magnification) which confirmed defect-free sintering and bonding interfaces.

- Frequency-dependent dynamic characteristics: Extraction of parasitic parameters for the power module was performed using ANSYS Q3D software, yielding a simulated inductance of 6 nH. Experimental validation via double-pulse testing measured the parasitic inductance at 8.3 nH. Both simulation and experimental results confirm the module’s relatively low parasitic parameters. Further evaluations across switching frequencies of 25 kHz to 200 kHz demonstrated a maximum temperature rise of 109 °C. This value remains below the 175 °C maximum junction temperature specified in the device datasheet, confirming operation within the permissible temperature range while maintaining low switching losses.

- Bandwidth constraints of probes, causing waveform distortion during fast SiC switching.

- Timing mismatches between voltage/current probes, inducing phase errors.

- Parasitic capacitances and inductances introducing extraneous energy components.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Jahdi, S.; Alatise, O.; Gonzalez, J.A.; Bonyadi, R.; Ran, L.; Mawby, P. Temperature and switching rate dependence of crosstalk in Si-IGBT and SiC power modules. IEEE Trans. Ind. Electron. 2015, 63, 849–863. [Google Scholar] [CrossRef]

- Zhang, M.; Ren, N.; Guo, Q.; Zhu, X.; Zhang, J.; Sheng, K. Modeling and analysis of vgs characteristics for upper-side and lower-side switches at turn-on transients for a 1200V/200A full-SiC power module. Micromachines 2019, 11, 5. [Google Scholar] [CrossRef] [PubMed]

- Lemmon, A.N.; Graves, R.C. Comprehensive characterization of 10-kV silicon carbide half-bridge modules. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 1462–1473. [Google Scholar] [CrossRef]

- Li, H.; Yu, R.; Zhong, Y.; Yao, R.; Liao, X.; Chen, X. Design of 400 V miniature DC solid state circuit breaker with SiC MOSFET. Micromachines 2019, 10, 314. [Google Scholar] [CrossRef] [PubMed]

- Cheng, H.C.; Jhu, W.Y.; Liu, Y.C.; Zheng, D.W.; Liu, Y.C.; Chang, T.C. Dynamic Performance Evaluation of Bidirectional Bridgeless Interleaved Totem-Pole Power Factor Correction Boost Converter. Micromachines 2025, 16, 223. [Google Scholar] [CrossRef] [PubMed]

- Matocha, K.; Banerjee, S.; Chatty, K. Advanced SiC Power MOSFETs Manufactured on 150 mm SiC Wafers. In Materials Science Forum; Trans Tech Publications Ltd.: Bäch, Switzerland, 2016; Volume 858, pp. 803–806. [Google Scholar]

- Cai, K.D.; Xiao, J.; Yang, Z.; Hu, R.H. Three-Level All-SiC High-Frequency High-Voltage Plasma Power Supply System. Energies 2025, 18, 1617. [Google Scholar] [CrossRef]

- Ni, Z.; Lyu, X.F.; Yadav, O.P.; Cao, D. Review of SiC MOSFET based three-phase inverter lifetime prediction. In Proceedings of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; pp. 1007–1014. [Google Scholar]

- Ceccarelli, L.; Bahman, A.S.; Iannuzzo, F. Impact of device aging in the compact electro-thermal modeling of SiC power MOSFETs. Microelectron. Reliab. 2019, 100, 113336. [Google Scholar] [CrossRef]

- Yang, Y.; Ge, Y.; Wang, Z.J.; Kang, Y. An automated electro-thermal-mechanical co-simulation methodology based on PSpice-MATLAB-COMSOL for SiC power module design. In Proceedings of the 2021 IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia), Wuhan, China, 25–27 August 2021; pp. 499–503. [Google Scholar]

- He, S.; Que, L.; Lv, J.; Ang, S.S. Silicon carbide power electronic module packaging. In Proceedings of the 2015 16th International Conference on Electronic Packaging Technology (ICEPT), Changsha, China, 11–14 August 2015; pp. 483–486. [Google Scholar]

- Zhang, Z.; Arriola, E.; Nicholas, C.; Lynch, J.; Yun, N.; Morgan, A. Package design and analysis of a 20-kV double-sided silicon carbide diode module with polymer nanocomposite field-grading coating. IEEE Trans. Compon. Packag. Manuf. Technol. 2024, 14, 776–783. [Google Scholar] [CrossRef]

- Loncarski, J.; Monopoli, V.G.; Leuzzi, R.; Ristic, L.; Cupertino, F. Analytical and simulation fair comparison of three level Si IGBT based NPC topologies and two level SiC MOSFET based topology for high speed drives. Energies 2019, 12, 4571. [Google Scholar] [CrossRef]

- Liu, S.; Cheng, X.; Zheng, L.; Sledziewski, T.; Erlbacher, T.; Sheng, L.; Yu, Y. Impact of the transition region between active area and edge termination on electrical performance of SiC MOSFET. Solid-State Electron. 2020, 171, 107873. [Google Scholar] [CrossRef]

- Peftitsis, D.; Rabkowski, J.; Nee, H.P. Self-powered gate driver for normally on silicon carbide junction field-effect transistors without external power supply. IEEE Trans. Power Electron. 2012, 28, 1488–1501. [Google Scholar] [CrossRef]

- Loncarski, J.; Monopoli, V.G.; Cascella, G.L.; Cupertino, F. SiC-mosfet and Si-igbt-based dc-dc interleaved converters for ev chargers: Approach for efficiency comparison with minimum switching losses based on complete parasitic modeling. Energies 2020, 13, 4585. [Google Scholar] [CrossRef]

- Ren, Y.; Yang, X.; Zhang, F.; Wang, L.; Wang, K.; Chen, W.; Zeng, X.; Pei, Y. Voltage suppression in wire-bond-based multichip phase-leg SiC MOSFET module using adjacent decoupling concept. IEEE Trans. Ind. Electron. 2017, 64, 8235–8246. [Google Scholar] [CrossRef]

- Alam, M.; Eberle, W.; Gautam, D.S.; Botting, C.; Dohmeier, N.; Musavi, F. A hybrid resonant pulse-width modulation bridgeless AC–DC power factor correction converter. IEEE Trans. Ind. Appl. 2016, 53, 1406–1415. [Google Scholar] [CrossRef]

- Zhang, B.F.; Xie, S.J.; Xu, J.M.; Qian, Q.; Zhang, Z.; Xu, K.S. A magnetic coupling based gate driver for crosstalk suppression of SiC MOSFETs. IEEE Trans. Ind. Electron. 2017, 64, 9052–9063. [Google Scholar] [CrossRef]

- Tala-Ighil, B.; Trolet, J.L.; Gualous, H.; Mary, P.; Lefebvre, S. Experimental and comparative study of gamma radiation effects on Si-IGBT and SiC-JFET. Microelectron. Reliab. 2015, 55, 1512–1516. [Google Scholar] [CrossRef]

- Yang, J.W.; Do, H.L. Soft-switching dual-flyback DC–DC converter with improved efficiency and reduced output ripple current. IEEE Trans. Ind. Electron. 2017, 64, 3587–3594. [Google Scholar] [CrossRef]

- Jiang, X.; Wang, J.; Chen, J.; Li, Z.; Zhai, D.; Yang, X.; Ji, B.; Shen, Z.J. Investigation on degradation of SiC MOSFET under surge current stress of body diode. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 8, 77–89. [Google Scholar] [CrossRef]

- Lu, J.; Wang, Y.; Li, X. Isolated high step-up DC–DC converter with integrated cascade structure. IET Power Electron. 2018, 11, 1143–1152. [Google Scholar] [CrossRef]

- Jain, P.; Das, B.P. Reducing the impact of local load variation on the DUT in a process detector using a supply controlled ring oscillator. IEEE Trans. Semicond. Manuf. 2019, 32, 605–612. [Google Scholar] [CrossRef]

- Yan, Q.; Yuan, X.; Geng, Y.; Charalambous, A.; Wu, X. Performance evaluation of split output converters with SiC MOSFETs and SiC Schottky diodes. IEEE Trans. Power Electron. 2016, 32, 406–422. [Google Scholar] [CrossRef]

- Górecki, P.; Górecki, K.; Rąbkowski, J. Switching energy losses characterization of discrete SiC power transistors-a new thermal approach. IEEE Trans. Instrum. Meas. 2025, 74, 1–11. [Google Scholar] [CrossRef]

- Baygildina, E.; Smirnova, L.; Murashko, K.; Juntunen, R.; Mityakov, A.; Kuisma, M.; Pyrhönen, O.; Peltoniemi, P.; Hynynen, K.; Mityakov, V.; et al. Application of a heat flux sensor in wind power electronics. Energies 2016, 9, 456. [Google Scholar] [CrossRef]

- Alavi, P.; Babaei, E.; Mohseni, P.; Marzang, V. Study and analysis of a DC–DC soft-switched buck converter. IET Power Electron. 2020, 13, 1456–1465. [Google Scholar] [CrossRef]

- Li, H.; Munk-Nielsen, S.; Bȩczkowski, S.; Wang, X. A novel DBC layout for current imbalance mitigation in SiC MOSFET multichip power modules. IEEE Trans. Power Electron. 2016, 31, 8042–8045. [Google Scholar] [CrossRef]

- Gelagaev, R.; Jacqmaer, P.; Driesen, J. A fast voltage clamp circuit for the accurate measurement of the dynamic on-resistance of power transistors. IEEE Trans. Ind. Electron. 2014, 62, 1241–1250. [Google Scholar] [CrossRef]

- Onambele, C.; Elsied, M.; Mpanda, M.A.; El, H.A. Multi-phase modular drive system: A case study in electrical aircraft applications. Energies 2017, 11, 5. [Google Scholar] [CrossRef]

- Islam, M.; Mekhilef, S.; Hasan, M. Single phase transformerless inverter topologies for grid-tied photovoltaic system: A review. Renew. Sustain. Energy Rev. 2015, 45, 69–86. [Google Scholar] [CrossRef]

- Ye, J.; Yang, K.; Ye, H.; Emadi, A. A fast electro-thermal model of traction inverters for electrified vehicles. IEEE Trans. Power Electron. 2016, 32, 3920–3934. [Google Scholar] [CrossRef]

- Matallana, A.; Robles, E.; Ibarra, E.; Andreu, J.; Delmonte, N.; Cova, P. A methodology to determine reliability issues in automotive SiC power modules combining 1D and 3D thermal simulations under driving cycle profiles. Microelectron. Reliab. 2019, 102, 113500. [Google Scholar] [CrossRef]

- Górecki, P.; Górecki, K.; Kisiel, R.; Brzozowski, E.; Bar, J.; Guziewicz, M. Investigations of an Influence of the Assembling Method of the Die to the Case on Thermal Parameters of IGBTs. IEEE Trans. Compon. Packag. Manuf. Technol. 2021, 11, 1988–1996. [Google Scholar] [CrossRef]

| Research Institutions | Research Status |

|---|---|

| North Dakota State University | Established an electro-thermal model to extract the temperature distribution of SiC modules, but failed to integrate practical process data (e.g., high-temperature baking), making it impossible to verify the model’s adaptability to high-temperature environments. |

| Aalborg University | Predicted SiC aging behavior using an electro-thermal co-simulation method, yet did not quantify the influence of sintering temperature/bonding parameters on the thermal model. |

| Huazhong University of Science and Technology | Explored an electro-thermal co-simulation method based on Pspice-MATLAB-COMSOL; however, it lacked practical process analysis experiments, making it difficult to evaluate the model’s robustness against process fluctuations. |

| University of Electronic Science and Technology of China | Investigated the design and experiments of packaging processes (e.g., substrate, wire bonding) for SiC power modules under high-temperature and high-voltage conditions, but did not perform thermal simulation analysis on module design, failing to predict the thermal distribution of power modules. |

| Virginia Polytechnic Institute and State University | In terms of packaging process design, it adopted lead-free bonding to minimize parasitic inductance. However, due to the lack of electrical simulation analysis on module design it was unable to predict its dynamic switching characteristics. |

| Parameters | Specifications |

|---|---|

| Test voltage | 800 V |

| Simulation time T | 17 μs |

| Load inductance L | 850 μH |

| MOS for upper and lower bridge arms | HX1M013120W |

| Parameters | Definition | Specifications (nH) | Impact |

|---|---|---|---|

| L1, L4 | Power loop inductance (drain path) | 1.8, 1.6 | Causing drain–source voltage oscillation or overshoot |

| L3, L6 | Power loop inductance (source path) | 1.2, 1.4 | Causing drain–source voltage oscillation or overshoot |

| L2, L5 | Gate–driver loop inductance | 2.1, 1.9 | Inducing gate-voltage oscillation |

| Structure | Length (mm) | Width (mm) | Height (mm) | Coordinates (mm) |

|---|---|---|---|---|

| Upper-arm SiC MOS wafer | 6.48 | 5.01 | 0.19 | (x = 10, y = 11) |

| Lower-arm SiC MOS wafer | 6.48 | 5.01 | 0.19 | (x = 35, y = 11) |

| Copper substrate | 45 | 22 | 1 | (x = 22.5, y = 11) |

| Material | Thermal ConductivityW/(m·K) | Density(kg/m3) | Heat Capacity at Constant Pressure [J/(kg·K)] |

|---|---|---|---|

| Cu | 400 | 8940 | 385 |

| SiC | 450 | 3210 | 700 |

| Alumina | 27 | 3900 | 900 |

| Parameters | Specifications |

|---|---|

| MOSFET wafer | HX1M013120W |

| Drain–source voltage | 800 V |

| Continuous maximum drain current | 10 A |

| On-resistance () | 0.45 |

| Threshold voltage () | 15–25 V |

| Output capacitance () | 70 pF |

| Operating junction and storage temperature range | −55~+175 |

| Parameters | Specifications |

|---|---|

| RMS (root mean square) current () | 100 A |

| Drain on-resistance () | 23 mΩ |

| Conduction duty cycle () | 0.5 |

| Turn-on loss and turn-off loss () | 105 |

| Switching frequency () | 25 kHz |

| Parameters | Specifications |

|---|---|

| Test voltage | 800 V |

| Load inductance | 850 uH |

| Gate-drive voltage of upper bridge | −6 V |

| Gate-drive voltage of lower bridge | 21 V |

| Half-bridge SiC power module | HX1M013120W (Macrocore Semiconductor (Shenzhen, China)) |

| High-voltage DC power supply | JingRi DP1200 (JingRi Technology Co., Ltd. (Hangzhou, China)) |

| Low-voltage DC power supply | Siglent SPD3303C (Siglent Technologies Co., Ltd. (Shenzhen, China)) |

| Oscilloscope | Siglent SDS2074X (Siglent Technologies Co., Ltd. (Shenzhen, China)) |

| High-voltage differential probe | Siglent DPB5150A (Siglent Technologies Co., Ltd. (Shenzhen, China)) |

| Rogowski coil | Micsig RCP600XS (Micsig Technologies Co., Ltd. (Shenzhen, China)) |

| Frequency (kHz) | Turn-On Loss (μJ) | Turn-Off Loss (μJ) | Peak Temperature (°C) |

|---|---|---|---|

| 25 | 65 | 42 | 85 |

| 100 | 261 | 165 | 93 |

| 150 | 370 | 245 | 102 |

| 200 | 450 | 310 | 109 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cai, K.; Xiao, J.; Su, X.; Tang, Q.; Deng, H. Encapsulation Process and Dynamic Characterization of SiC Half-Bridge Power Module: Electro-Thermal Co-Design and Experimental Validation. Micromachines 2025, 16, 824. https://doi.org/10.3390/mi16070824

Cai K, Xiao J, Su X, Tang Q, Deng H. Encapsulation Process and Dynamic Characterization of SiC Half-Bridge Power Module: Electro-Thermal Co-Design and Experimental Validation. Micromachines. 2025; 16(7):824. https://doi.org/10.3390/mi16070824

Chicago/Turabian StyleCai, Kaida, Jing Xiao, Xingwei Su, Qiuhui Tang, and Huayuan Deng. 2025. "Encapsulation Process and Dynamic Characterization of SiC Half-Bridge Power Module: Electro-Thermal Co-Design and Experimental Validation" Micromachines 16, no. 7: 824. https://doi.org/10.3390/mi16070824

APA StyleCai, K., Xiao, J., Su, X., Tang, Q., & Deng, H. (2025). Encapsulation Process and Dynamic Characterization of SiC Half-Bridge Power Module: Electro-Thermal Co-Design and Experimental Validation. Micromachines, 16(7), 824. https://doi.org/10.3390/mi16070824