Abstract

In this study, we report a low ohmic contact resistance process on a 650 V E-mode p-GaN gate HEMT structure. An amorphous silicon (a-Si) assisted layer was inserted in between the ohmic contact and GaN. The fabricated device exhibits a lower contact resistance of about 0.6 Ω-mm after annealing at 550 °C. In addition, the threshold voltage shifting of the device was reduced from −0.85 V to −0.74 V after applying a high gate bias stress at 150 °C for 10−2 s. The measured time to failure (TTF) of the device shows that a low thermal budget process can improve the device’s reliability. A 100-fold improvement in HTGB TTF was clearly demonstrated. The study shows a viable method for CMOS-compatible GaN power device fabrication.

1. Introduction

GaN is a wide bandgap (3.4 eV) semiconductor material with excellent physical properties, such as a high breakdown field (>3.5 MV/cm), high thermal stability, and high saturation electron velocity (~107 cm/s) [1,2,3]. AlGaN/GaN-based high electron mobility transistors (HEMTs) have proven to be outstanding modern power devices with low on-resistance, low gate charge, and high breakdown voltage. The p-GaN gate GaN HEMTs are ideally suited for use as enhancement-mode (E-mode) transistors because of their excellent threshold voltage (VTH) control capabilities and require a positive VTH above 1.5 V to turn on the device [4,5,6]. However, VTH instabilities of p-GaN gate GaN HEMTs have been reported and discussed [7,8,9]. The VTH shift is due to several complex reasons, including acceptor-like traps in p-GaN [10,11], p-GaN gate sidewall leakage [12,13,14], low Schottky barrier heights [10], etc. Therefore, the study of VTH instability of GaN-based HEMTs has been the subject of many research reports [15,16,17,18,19,20]. To ensure the safe operation of the power device, the negative VTH drop must be improved. High-temperature gate bias (HTGB) is one of the most suitable methods for assessing device reliability at high temperatures [21].

In this study, we performed the source/drain (S/D) resistive annealing process at various annealing temperatures to observe the threshold voltage instability associated with thermal budget. Typically, the thermal budget of S/D annealing takes place at the highest process temperature, except for GaN epitaxy. Therefore, the threshold voltage instability of GaN-based HEMTs with respect to the thermal budget of S/D annealing is discussed, as there is no previous study on this topic. Based on the study, we found that the negative threshold voltage drop is strongly related to the annealing temperature. In addition, the new ohmic S/D contact process used not only maintains a low contact resistance (0.6 Ω-mm), but also reduces the annealing temperature to 550 °C. The shift in VTH was reduced to −0.74 V after 10−2 s of gate stress at 150 °C. The time to failure (TTF) of the device exhibits an improvement of 100 times, thus indicating the improvement in device reliability. Hence, the study suggests that the instability of the threshold voltage could be improved by employing the low heat budget process.

2. Device Structure and Fabrication

The fabrication starts by growing the undoped GaN epilayer on a 6-inch low-resistance Si (111) substrate using a low-pressure organic chemical vapor deposition system (MOCVD). The epilayer growth started with AlN/AlGaN buffer layers, followed by an unintentionally carbon-doped (UID) GaN buffer layer. Following the buffer layers, a 300 nm undoped GaN channel layer, 12 nm Al0.16Ga0.84N barrier layer, and a 90 nm p-GaN were grown. Mg is used as a p-type dopant for p-GaN layer with a concentration of about 5 × 1019 cm−3. The Mg dopant was activated in situ with metal-organic chemical vapor deposition (MOCVD) after the epilayers had grown. The wafer bow warp was controlled under ±35 μm. The total epilayer thickness is approximately 4.8 μm.

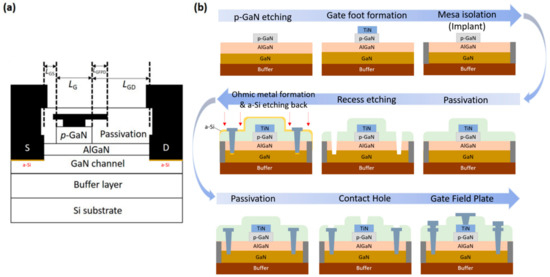

For device fabrication, the 6-inch Si wafer was diced into 1.2 × 1.2 cm2 small pieces. The gate-first device fabrication process was initiated by etching the p-GaN gate using fluorine-based gas andwell etched-stop at the AlGaN barrier layer. A surface roughness of about 1 nm is measured at the AlGaN access region. After etching, the gate metal (TiN) was deposited and patterned on p-GaN corresponding to the AlN/Al2O3 passivation grown by atomic layer deposition (ALD) [22]. Ar-implantation is used to perform the mesa isolation process. Next, a 200 nm SiNx layer was deposited by plasma-enhanced chemical vapor deposition (PECVD) to serve as the second passivation layer. The S/D region was defined using photolithography and etched accordingly. The top passivation/AlGaN stacking layers were fully removed using dry etching, followed by a 2 nm over-etching in the GaN channel layer. In this study, two types of processes are used: Process A (Sample A-1 to Sample A-4) is without an amorphous-Si (a-Si) assisted layer, while Process B (Sample B-1) has an a-Si assisted layer. For Samples A-1 to A-4, the S/D metal layer stack (Ti/Al/Ti with dimensions 25/500/5 nm) was grown by a lift-off process. For Sample B-1, a 1 nm a-Si-assisted layer was included, which is grown by AMAT CENTURA SYSTEM 5200 PECVD prior to the ohmic metal deposition.

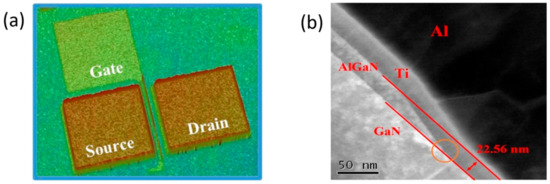

To find an optimal thermal budget for device reliability, Sample A-series are studied under various S/D annealing temperatures ranging from 550 °C to 700 °C. Finally, the fabrication is concluded by growing the gate field plate, S/D metal pads, and SiO2 passivation. The length of the p-GaN is 2 μm with a 0.5 μm enclosure of TiN gate metal. The dimensions of LGS/LGD/LGFPD/WG are 3/15/3/100 μm, respectively. Transmission line measurement (TLM) is used to extract the contact resistance of the device. The schematic device structure is shown in Figure 1a, and the device schematic process flow in Figure 1b. The optical 3D surface profiler and the TEM of the fabricated device is shown in Figure 2. A part of the GaN epitaxial layer of the S/D recess is also etched so that the two-dimensional electron gas on the side wall can directly contact the metal structure, as indicated by the orange circle in the Figure 2b. The list of fabricated samples along with the corresponding annealing conditions are tabulated in Table 1.

Figure 1.

(a) Schematic cross-section of the GaN-based HEMT device structure. (b) Device process flow.

Figure 2.

(a) Three-dimensional surface profiler. (b) TEM image of the fabricated device.

Table 1.

Summary of sample list and the corresponding etching depth, a-Si thickness, S/D metal stack, and annealing temperature.

3. Results and Discussion

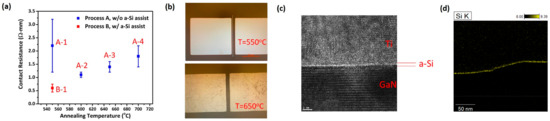

Figure 3a shows the relationship between contact resistance and annealing temperature for the two different process schemes (Process A and Process B). The highest contact resistance was observed at an annealing temperature of 550 °C (Sample A-1) which might be due to insufficient metal for alloying. As the annealing temperature increases to 600 °C (Sample A-2), the contact resistance was reduced to 1.1 ± 0.1 Ω-mm and gradually increases as the annealing temperature rises. The increase in contact resistance can be attributed to the boiling of Al after 650 °C, as shown in Figure 3b. As seen from the optical microscopy images of Sample A-1 (annealing temperature of 550 °C) and Sample A-3 (annealing temperature of 650 °C), the surface of Sample A-3 became worse due to the boiling of Al on the S/D metal surface at 650 °C. In Sample B-1, where a-Si-assisted layer was inserted at the interface between the S/D metal and GaN, the lowest contact resistance up to 0.6 ± 0.2 Ω-mm with a low annealing temperature (550 °C) was exhibited (Figure 3a). To investigate the interface quality of Sample B-1, the high-resolution transmission electron microscopy (HR-TEM) is used. Figure 3c shows the HR-TEM image of a 1 nm a-Si-assisted layer in between S/D metal and GaN of Sample B-1. Furthermore, to observe the composition of the a-Si-assisted layer, energy-dispersive X-ray spectroscopy (EDS) in TEM was carried out. The image of an a-Si-assisted layer deposited at the interface of Ti/GaN after the EDS mapping of the Si signal by TEM is shown in Figure 3d.

Figure 3.

(a) Contact resistance as a function of annealing temperature. (b) The optical microscopy images of Sample A-1 and Sample A-3, Al boiling can be observed. (c) The HR-TEM image of the interface between Ti/GaN corresponds to a 1 nm a-Si-assisted layer of Sample B-1. (d) The EDS mapping of Si signal by TEM, the inset shows the corresponding TEM image.

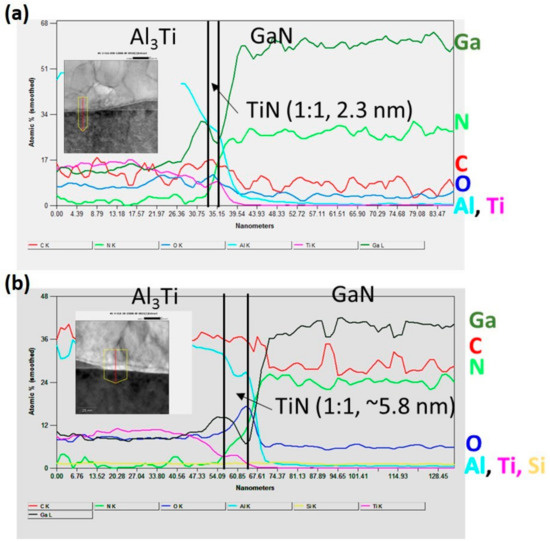

To analyze the improvement in the contact resistance, the EDS line scan from top S/D metal to GaN for Sample A-2 and Sample B-1 was compared. The respective EDS line scan for Sample A-2 and Sample B-1 is shown in Figure 4a,b, respectively. In the alloyed region, Al3Ti phase was observed at the top of alloyed S/D metal and the formation of TiN layer is observed at the interface for both samples. However, the thickness of the interfacial TiN of Sample B-1 is more than that of Sample A-2. According to [22], the formation of TiN occurs when Ti reacts with GaN. Many nitrogen vacancies (VN) were produced near the interface between Ti and GaN after thermal alloying. The shift in Fermi level to the energy level of nitrogen vacancy towards the Fermi level pinning at 0.5 eV below the edge of the conduction band was reported by Lin et al. [23]. The sharp band bending of GaN gives rise to the probability of electron tunneling, and as a result electrons are being transported from GaN to Ti as free carriers. Thus, from images in Figure 4, we concluded that a thin a-Si assisted layer promised a thicker TiN interfacial layer. In addition, the presence of a thicker Ti layer at the top contributes to the reduction in contact resistance. The excess amount of Ti obstructs the reaction between TiN and Al, leading to lower contact resistance.

Figure 4.

EDS line-scan analysis in the red arrow direction of TEM images for (a) Sample A-2 without an a-Si assisted layer and (b) Sample B-1 with a 1 nm a-Si-assisted layer. The corresponding TEM images were shown in the inset.

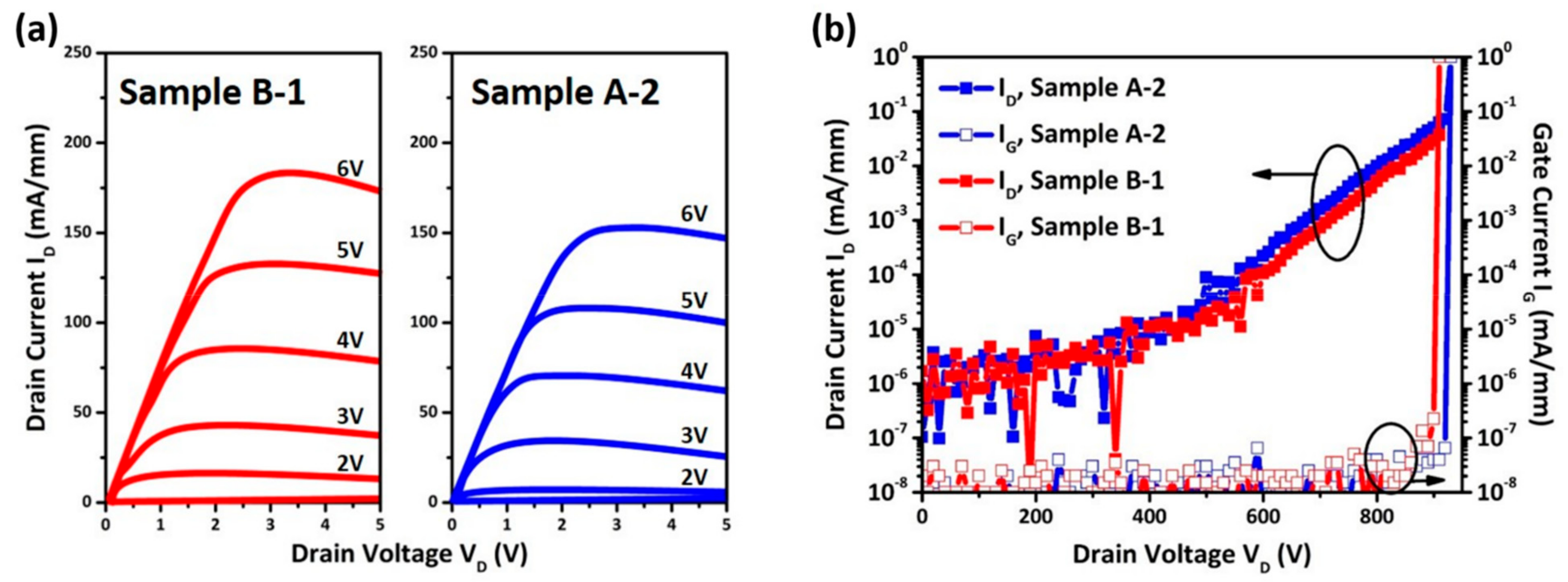

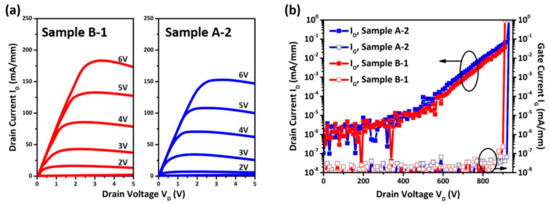

Figure 5a,b show the measured transfer ID-VD characteristics and off-state leakage current characteristics of fabricated HEMTs. As shown in Figure 5b, the excellent off-state leakage current characteristics were obtained within a high drain voltage ranging up to 800 V with an off-state drain current less than 5 × 10−8 A/mm at VDS value of 650 V. The BV curves for both processes show a compatible result which indicates that there is no side effect by inserting an a-Si-assisted layer in the ohmic contact process. The on-resistance of the device can be ascribed as the summation of contact resistance (RC), source resistance (RS), drain resistance (RD), and channel resistance (RChannel). The on-resistance (Ron) of the fabricated device was calculated when VG = 6 V and VD = 1 V from ID-VD curves. The measured values of series resistances of fabricated GaN HEMT is tabulated in Table 2. The Ron shows an improvement from 14.4 Ω-mm (Sample A-2) to 13.0 Ω-mm (Sample B-1), and the corresponding 2 RC reduces from 2.2 to 1.2 Ω-mm by introducing the a-Si assisted layer. The reduction in RD + RS and Rchannel in Sample B-1 was from the 2DEG-RS reduction from 530 to 510 ohm/sq.

Figure 5.

(a) The transfer I-V characteristics of Sample B-1 and Sample A-2 under VD = 10. (b) Off-state leakage current characteristics.

Table 2.

Measured value of series resistances of fabricated GaN HEMT.

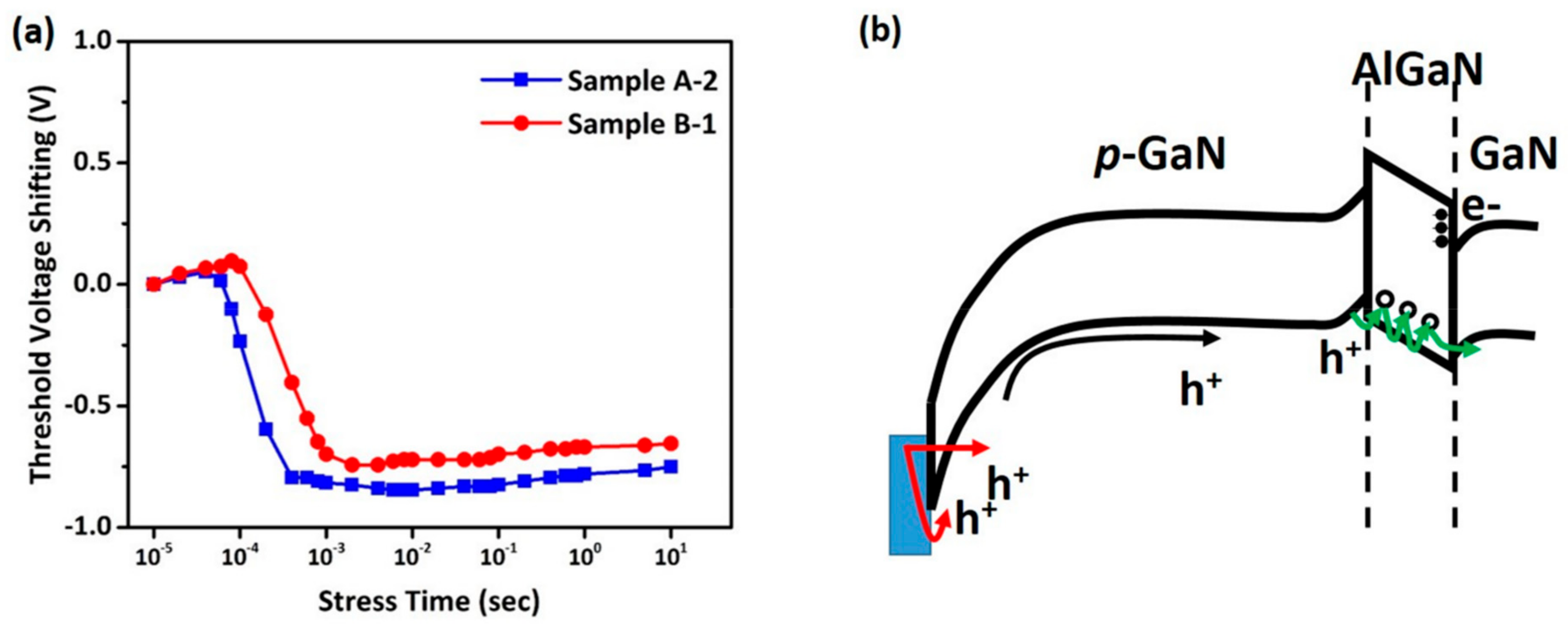

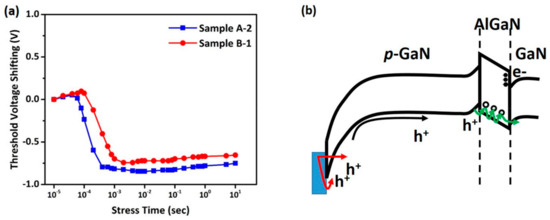

HTGB measurement was performed to compare the thermal budget effect from S/D ohmic metallization process. Both samples, Sample A-2 and Sample B-1, were kept under stress with a high gate forward bias of 7 V at T = 150 °C for 1 ksec while the Drain bias and substrate bias are kept at 0 V. During the measurement, both devices exhibit a VTH shift in subthreshold characteristics; the shifting of VTH with respect to stress time is shown in Figure 6a. The VTH shift was observed at 10−2 s, where Sample B-1 is −0.74 V and Sample A-2 is −0.85 V. Sample B-1 exhibits a lower VTH negative shifting than Sample A-2, which was correlated to the thermal budget consideration. The VTH shifting can be attributed to the hole accumulation in the two-dimensional hole gas (2DHG) and hole depletion across the p-GaN/AlGaN/GaN as a p-i-n diode. In a p-i-n diode structure, the hole supply is limited by either tunneling through or thermionic emission (TE) across the Schottky barrier of gate metal/p-GaN. The uniform hole emission over the reverse-biased Schottky diode leads to an increase in the 2DHG density, and consequently the threshold voltage shifting is corresponded to the 2DHG density [14]. Additionally, the out-diffusion of Mg could be the result of p-GaN thermal activation or S/D ohmic metallization annealing. The Mg acceptor-like states in the AlGaN band structure allows the hole trap-assist-tunneling (TAT) by the trapping/de-trapping process, leading to a negative threshold voltage shifting and a serious gate leakage [24], as shown by the green arrow in Figure 6b. Furthermore, as the gate voltage increased the p-GaN potential, holes were injected across the AlGaN barrier into the GaN layer, leaving behind a partially depleted p-GaN layer. Simultaneously, the hole-electron recombination between 2DHG and 2DEG will occur, leading to a positive threshold shift, which is expected to take place after a long stressing time. Tang et al. reported the generation of GaN band-edge ultraviolet (UV) emission when injected holes recombine with 2DEG electrons in the GaN channel layer [25]. This phenomenon can be considered as the reason for positive threshold voltage shifting at 101 s stress time. The positive shifting of both samples is observed to be about ~90 mV from 10−2 s to 101 s stress time.

Figure 6.

(a) Experimental threshold voltage shifting versus accumulated stress time for Sample A-2 and Sample B-1. (b) The energy band diagram of the Schottky metal/p-GaN/AlGaN/GaN gate stack at VG = 6 V with different threshold voltage shifting mechanisms. The red arrow indicates the holes across the Schottky barrier height, the green arrow shows the out-diffusion of Mg as an acceptor-like trap level in AlGaN.

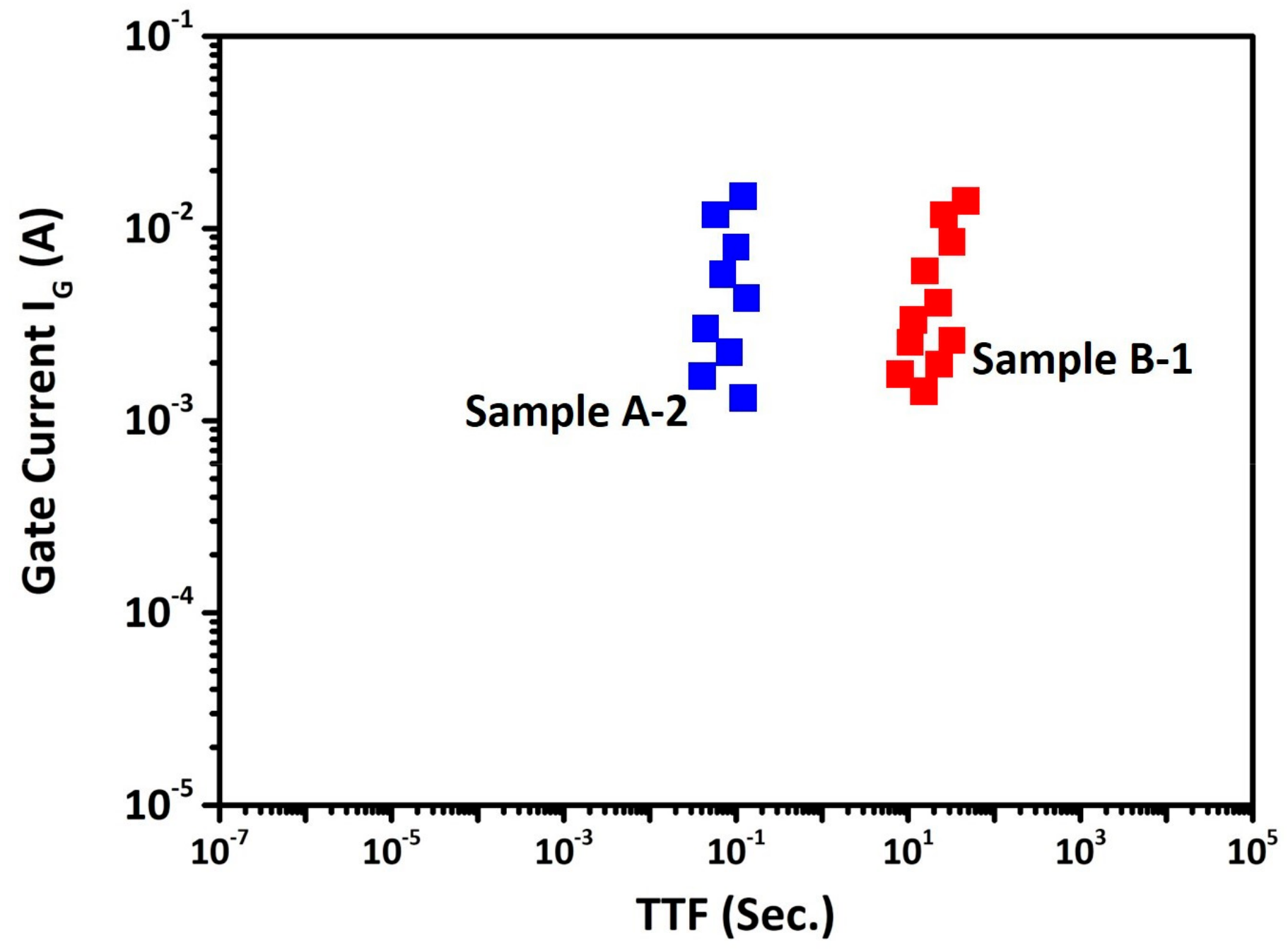

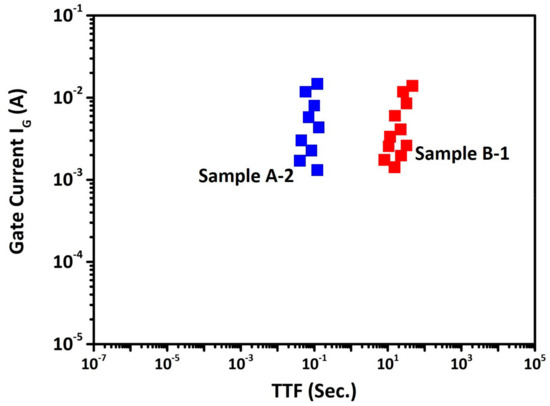

The correlation between gate current and time to failure (TTF) during HTGB at VG = 10 V for Sample A-2 and Sample B-1 is shown in Figure 7. As seen in the figure, the TTF of Sample A-2 is shorter than Sample B-1; this can be attributed to the higher amount of hole injection from Schottky metal through the p-GaN and GaN channel layer [26]. The result shows that a higher thermal budget leads to hole re-activation during S/D metallization. Thus, a higher annealing temperature reactivates the hole doping concentration. Additionally, the sheet resistance of Sample A-2 is lower than Sample B-1 which also suggests the re-activation under S/D metallization. The out-diffused [Mg] into AlGaN served as an acceptor-like trap as well as a negative charge. The re-activation of out-diffused [Mg] enables the removal of negative charges so that the 2DEG-RS can be reduced by a higher annealing temperature. However, post-implantation annealing results in GaN surface decomposition thus limiting the annealing temperature, which results in insufficient activation [26]. Defect assisted due to Mg diffusion results in redistributions of Mg atoms into the deeper region [27].

Figure 7.

Correlation between gate current and time to failure (TTF) for the device under an HTGB at VG = 10 V, T = 150 °C.

Stoffels et al. observed the relationship between TTF and hole doping concentration [28]; a higher hole doping concentration and a higher amount of holes injected into p-GaN results in increased gate leakage and poor TTF. Stoffels et al. also reported that enhancing the barrier height of p-GaN/AlGaN/GaN p-i-n diode improves the TTF degradation [14]. Sample B-1 with a lower thermal budget at S/D metallization was able to reduce the TiN/p-GaN alloying temperature, or hole re-activation. In addition, the TTF is improved by 100 times for the lower thermal budget process than that of the higher thermal budget process sample under HTGB testing.

4. Conclusions

In summary, we have demonstrated that low contact resistance can be fabricated by using an a-Si-assisted-process scheme. The implementation of an a-Si-assisted scheme not only enhanced contact resistance but also maintained a low annealing temperature. The threshold voltage instability of the device at a high gate stress is also improved by the low thermal budget process. The lower thermal budget process with an a-Si-assisted layer showed an improvement in VTH shifting from −0.85 V to −0.74 V after a 10−2 s gate stress at 150 °C. In addition, the lower thermal budget enhanced the TiN/p-GaN alloying and eliminated hole activation from S/D metallization annealing. Furthermore, the TTF of HTGB at gate bias of 10 V at 150 °C was improved by 100 times, thus achieving a significant improvement in the lifetime of the device.

Author Contributions

Data analysis and structure designing, C.L., A.-C.L. and J.T.; fabrication, N.-J.Y., M.-H.K., W.-H.H. and C.-H.S.; writing—review and editing, C.L. and J.T.; supervision, H.-C.K. and J.-M.S.; project administration, J.T. and H.-C.K. All authors have read and agreed to the published version of the manuscript.

Funding

This work is supported by the Ministry of Science and Technology, Taiwan (110-2124-M-A49-003-, 108-2221-E-009-113-MY3).

Data Availability Statement

The authors confirm that the data supporting the findings of this study are available within the article.

Acknowledgments

The authors would like to thank the Taiwan Semiconductor Research Institute (TSRI) and the Nano Facility Center of National Chiao Tung University for their support. The epi-wafers were supported by J. I. Chyi and Y. M. Shin of National Central University. The process was supported by H. C. Chiu of Chang Gung University.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Dora, Y.; Chakraborty, A.; Mccarthy, L.; Keller, S.; DenBaars, S.; Mishra, U.K. High breakdown voltage achieved on AlGaN/GaN HEMTs with integrated slant field plates. IEEE Electron Device Lett. 2006, 27, 713–715. [Google Scholar] [CrossRef]

- Uemoto, Y.; Hikita, M.; Ueno, H.; Matsuo, H.; Ishida, H.; Yanagihara, M.; Ueda, T.; Tanaka, T.; Ueda, D. Gate injection transistor (GIT)—A normally-off AlGaN/GaN power transistor using conductivity modulation. IEEE Trans. Electron Devices 2007, 54, 3393–3399. [Google Scholar] [CrossRef]

- Kuzuhara, M.; Tokuda, H. Low-loss and high-voltage III-nitride transistors for power switching applications. IEEE Trans. Electron Devices 2014, 62, 405–413. [Google Scholar] [CrossRef]

- He, J.; Tang, G.; Chen, K.J. VTH Instability of p-GaN Gate HEMTs Under Static and Dynamic Gate Stress. IEEE Electron Device Lett. 2018, 39, 1576–1579. [Google Scholar] [CrossRef]

- Lee, F.; Su, L.-Y.; Wang, C.-H.; Wu, Y.-R.; Huang, J. Impact of gate metal on the performance of p-GaN/AlGaN/GaN high electron mobility transistors. IEEE Electron Device Lett. 2015, 36, 232–234. [Google Scholar] [CrossRef]

- Jiang, H.; Lyu, Q.; Zhu, R.; Xiang, P.; Cheng, K.; Lau, K.M. 1300 V normally-OFF p-GaN gate HEMTs on Si with high ON-state drain current. IEEE Trans. Electron Devices 2020, 68, 653–657. [Google Scholar] [CrossRef]

- Tang, X.; Li, B.; Moghadam, H.A.; Tanner, P.; Han, J.; Dimitrijev, S. Mechanism of Threshold Voltage Shift in p-GaN Gate AlGaN/GaN Transistors. IEEE Electron Device Lett. 2018, 39, 1145–1148. [Google Scholar] [CrossRef]

- Sayadi, L.; Iannaccone, G.; Sicre, S.; Häberlen, O.; Curatola, G. Threshold voltage instability in p-GaN gate AlGaN/GaN HFETs. IEEE Trans. Electron Devices 2018, 65, 2454–2460. [Google Scholar] [CrossRef]

- Shi, Y.; Zhou, Q.; Cheng, Q.; Wei, P.; Zhu, L.; Wei, D.; Zhang, A.; Chen, W.; Zhang, B. Carrier Transport Mechanisms Underlying the Bidirectional VTH Shift in p-GaN Gate HEMTs Under Forward Gate Stress. IEEE Trans. Electron Devices 2018, 66, 876–882. [Google Scholar] [CrossRef]

- Del Alamo, J.A.; Lee, E.S. Stability and reliability of lateral GaN power field-effect transistors. IEEE Trans. Electron Devices 2019, 66, 4578–4590. [Google Scholar] [CrossRef]

- Wang, H.; Wei, J.; Xie, R.; Liu, C.; Tang, G.; Chen, K.J. Maximizing the performance of 650-V p-GaN gate HEMTs: Dynamic RON characterization and circuit design considerations. IEEE Trans. Power Electron. 2016, 32, 5539–5549. [Google Scholar] [CrossRef]

- Tajalli, A.; Canato, E.; Nardo, A.; Meneghini, M.; Stockman, A.; Moens, P.; Zanoni, E.; Meneghesso, G. Impact of sidewall etching on the dynamic performance of GaN-on-Si E-mode transistors. Microelectron. Reliab. 2018, 88, 572–576. [Google Scholar] [CrossRef]

- Wang, R.; Lei, J.-M.; Guo, H.; Li, R.; Chen, D.-J.; Lu, H.; Zhang, R.; Zheng, Y.-D. VT Shift and Recovery Mechanisms of p-GaN Gate HEMTs Under DC/AC Gate Stress Investigated by Fast Sweeping Characterization. IEEE Electron Device Lett. 2021, 42, 1508–1511. [Google Scholar] [CrossRef]

- Stockman, A.; Canato, E.; Meneghini, M.; Meneghesso, G.; Moens, P.; Bakeroot, B.; Reliability, M. Schottky gate induced threshold voltage instabilities in p-GaN gate AlGaN/GaN HEMTs. IEEE Trans. Device Mater. Reliab. 2021, 21, 169–175. [Google Scholar] [CrossRef]

- Tallarico, A.N.; Stoffels, S.; Posthuma, N.; Magnone, P.; Marcon, D.; Decoutere, S.; Sangiorgi, E.; Fiegna, C. PBTI in GaN-HEMTs with p-Type Gate: Role of the Aluminum Content on ΔVTH and Underlying Degradation Mechanisms. IEEE Trans. Electron Devices 2017, 65, 38–44. [Google Scholar] [CrossRef]

- Ruzzarin, M.; Meneghini, M.; Barbato, A.; Padovan, V.; Haeberlen, O.; Silvestri, M.; Detzel, T.; Meneghesso, G.; Zanoni, E. Degradation mechanisms of GaN HEMTs with p-type gate under forward gate bias overstress. IEEE Trans. Electron Devices 2018, 65, 2778–2783. [Google Scholar] [CrossRef]

- Tallarico, A.N.; Stoffels, S.; Posthuma, N.; Decoutere, S.; Sangiorgi, E.; Fiegna, C. Threshold voltage instability in GaN HEMTs with p-type gate: Mg doping compensation. IEEE Electron Device Lett. 2019, 40, 518–521. [Google Scholar] [CrossRef]

- Li, S.; He, Z.; Gao, R.; Chen, Y.; Chen, Y.; Liu, C.; Huang, Y.; Li, G. Time-dependent threshold voltage instability mechanisms of p-GaN gate AlGaN/GaN HEMTs under high reverse bias conditions. IEEE Trans. Electron Devices 2020, 68, 443–446. [Google Scholar] [CrossRef]

- Wu, H.; Fu, X.; Guo, J.; Wang, Y.; Liu, T.; Hu, S. Time-Resolved Threshold Voltage Instability of 650-V Schottky Type p-GaN Gate HEMT Under Temperature-Dependent Forward and Reverse Gate Bias Conditions. IEEE Trans. Electron Devices 2022, 69, 531–535. [Google Scholar] [CrossRef]

- Savadi, L.; Iannaccone, G.; Sicre, S.; Lavanza, S.; Fiori, G.; Haberlen, O.; Curatola, G. Charge injection in normally-off p-GaN gate AlGaN/GaN-on-Si HFETs. In Proceedings of the 2018 48th European Solid-State Device Research Conference (ESSDERC), Dresden, Germany, 3–6 September 2018; pp. 18–21. [Google Scholar]

- Chihani, O.; Theolier, L.; Deletage, J.-Y.; Woirgard, E.; Bensoussan, A.; Durier, A. Temperature and voltage effects on HTRB and HTGB stresses for AlGaN/GaN HEMTs. In Proceedings of the 2018 IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, USA, 11–15 March 2018; pp. P-RT.2-1–P-RT.2-6. [Google Scholar]

- Lu, C.; Davydov, A.; Josell, D.; Bendersky, L.A. Interfacial reactions of Ti/n-GaN contacts at elevated temperature. J. Appl. Phys. 2003, 94, 245–253. [Google Scholar] [CrossRef]

- Lin, Y.-S.; Wu, J.-Y.; Chan, C.-Y.; Hsu, S.S.; Huang, C.-F.; Lee, T.-C. Square-gate AlGaN/GaN HEMTs with improved trap-related characteristics. IEEE Trans. Electron Devices 2009, 56, 3207–3211. [Google Scholar] [CrossRef]

- Bakeroot, B.; Stockman, A.; Posthuma, N.; Stoffels, S.; Decoutere, S. Analytical Model for the Threshold Voltage of p-(Al) GaN High-Electron-Mobility Transistors. IEEE Trans. Electron Devices 2017, 65, 79–86. [Google Scholar] [CrossRef]

- Tang, X.; Li, B.; Zhang, J.; Li, H.; Han, J.; Nguyen, N.-T.; Dimitrijev, S.; Wang, J. Demonstration of Electron/Hole Injections in the Gate of p-GaN/AlGaN/GaN Power Transistors and Their Effect on Device Dynamic Performance. In Proceedings of the 2019 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD), Shanghai, China, 19–23 May 2019; pp. 415–418. [Google Scholar]

- Narita, T.; Yoshida, H.; Tomita, K.; Kataoka, K.; Sakurai, H.; Horita, M.; Bockowski, M.; Ikarashi, N.; Suda, J.; Kachi, T.; et al. Progress on and challenges of p-type formation for GaN power devices. J. Appl. Phys. 2020, 128, 090901. [Google Scholar] [CrossRef]

- Kachi, T.; Narita, T.; Sakurai, H.; Matys, M.; Kataoka, K.; Hirukawa, K.; Sumida, K.; Horita, M.; Ikarashi, N.; Sierakowski, K.; et al. Process engineering of GaN power devices via selective-area p-type doping with ion implantation and ultra-high-pressure annealing. J. Appl. Phys. 2022, 132, 130901. [Google Scholar] [CrossRef]

- Stoffels, S.; Bakeroot, B.; Wu, T.-L.; Marcon, D.; Posthuma, N.; Decoutere, S.; Tallarico, A.; Fiegna, C. Failure mode for p-GaN gates under forward gate stress with varying Mg concentration. In Proceedings of the 2017 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2–6 April 2017; pp. 4B-4.1–4B-4.9. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).