Bond Wire Damage Detection Method on Discrete MOSFETs Based on Two-Port Network Measurement

Abstract

:1. Introduction

2. Methodologies

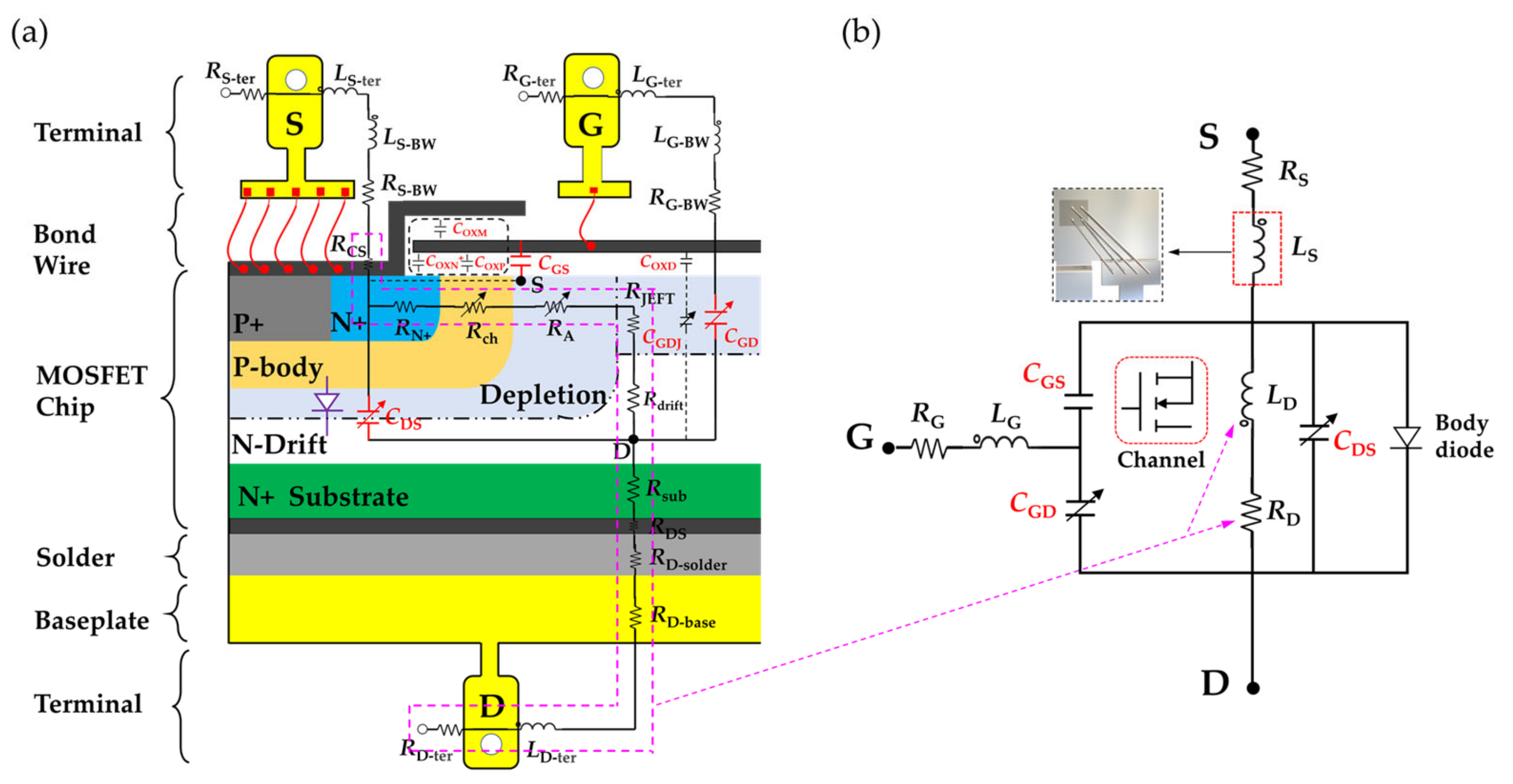

2.1. MOSFET Small-Signal Equivalent Circuit

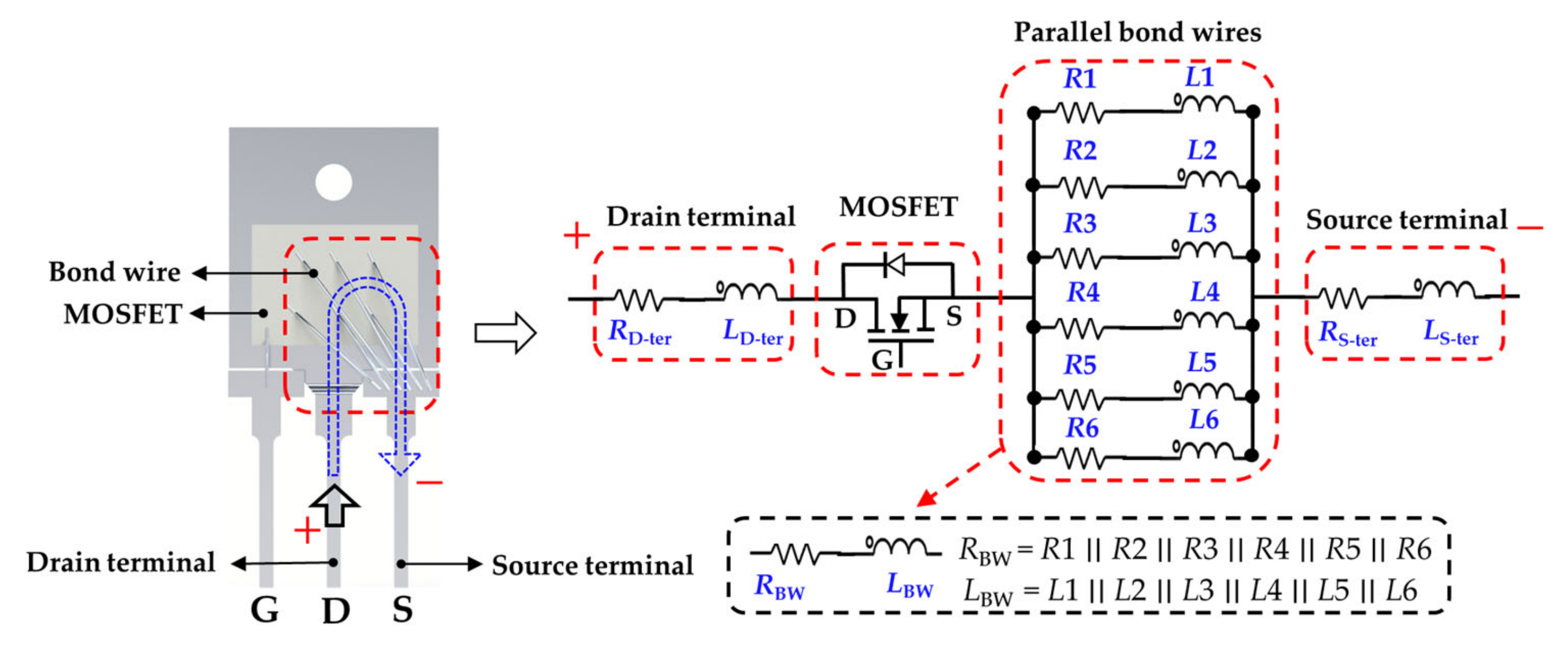

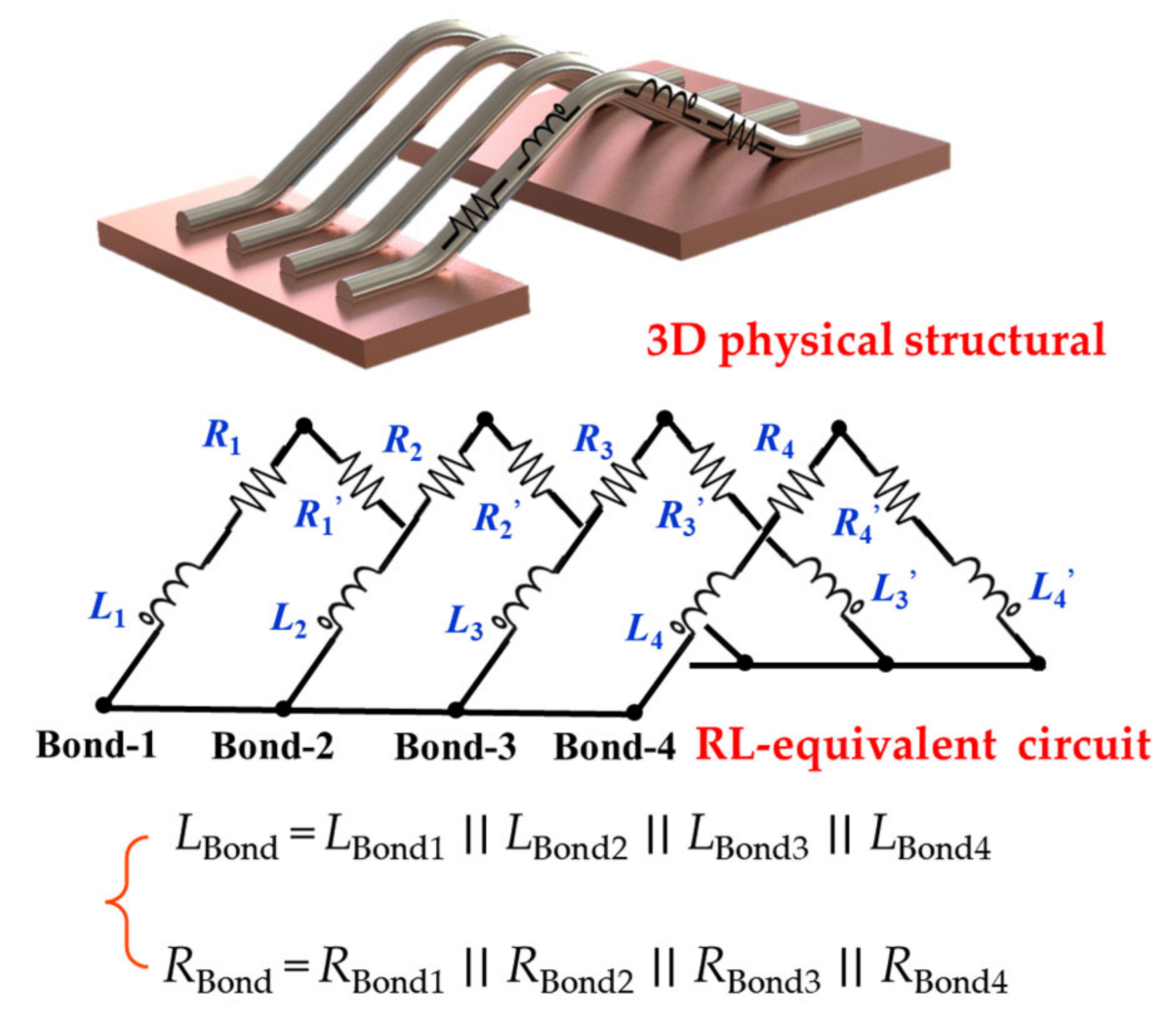

2.2. Bond Wire Parasitic Inductance

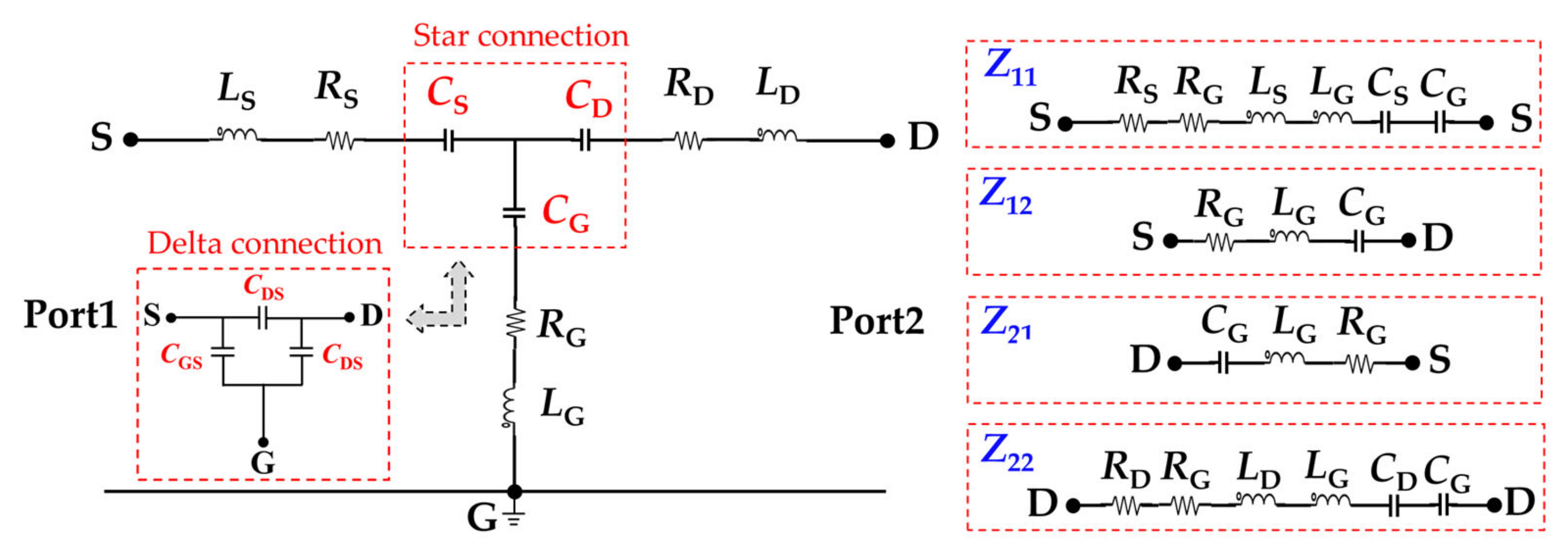

2.3. Two-Port Parasitic Inductance Extraction Approach

3. Experimental Results and Discussion

3.1. Validation Parasitic Inductance Extraction Approach for MOSFET

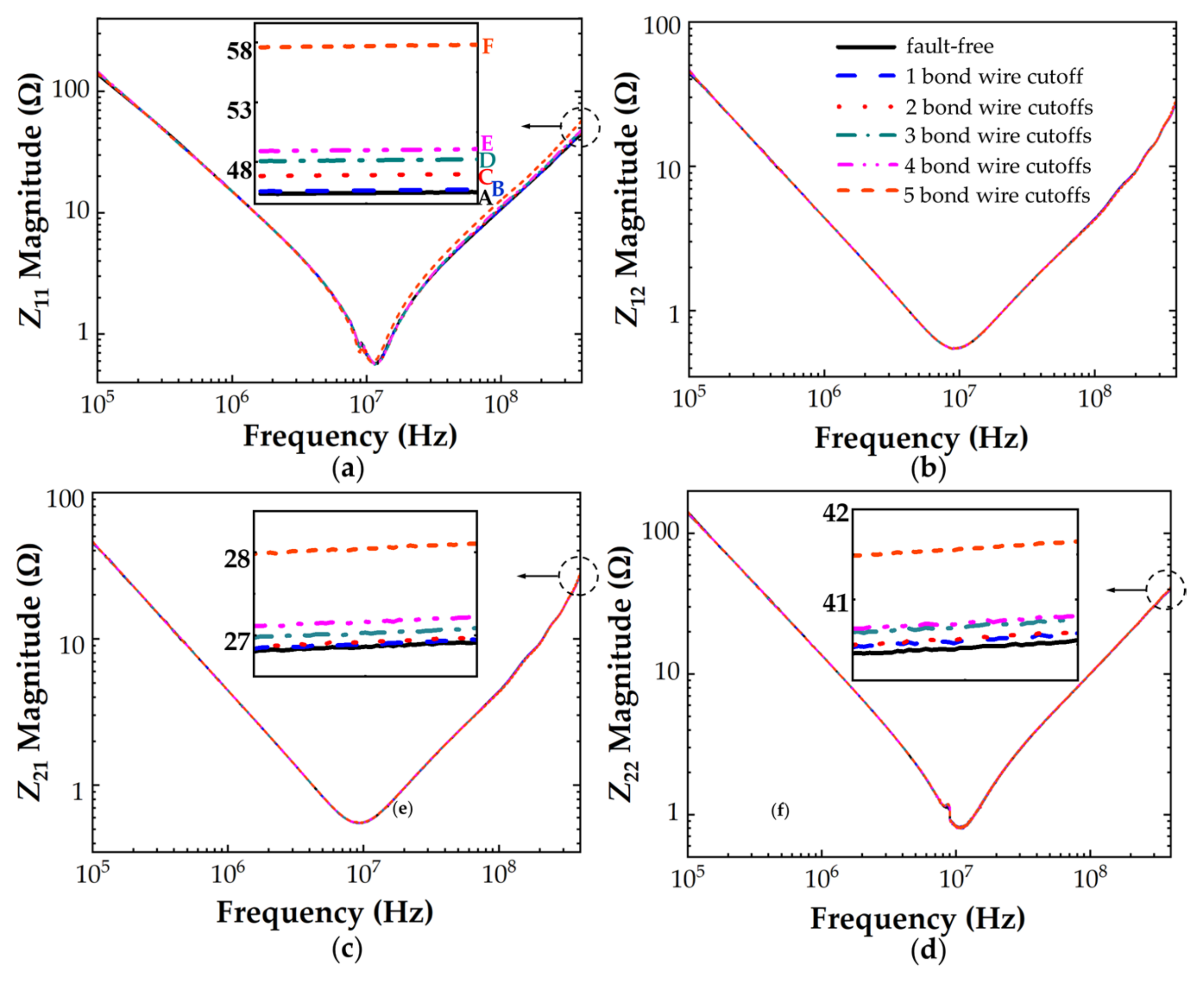

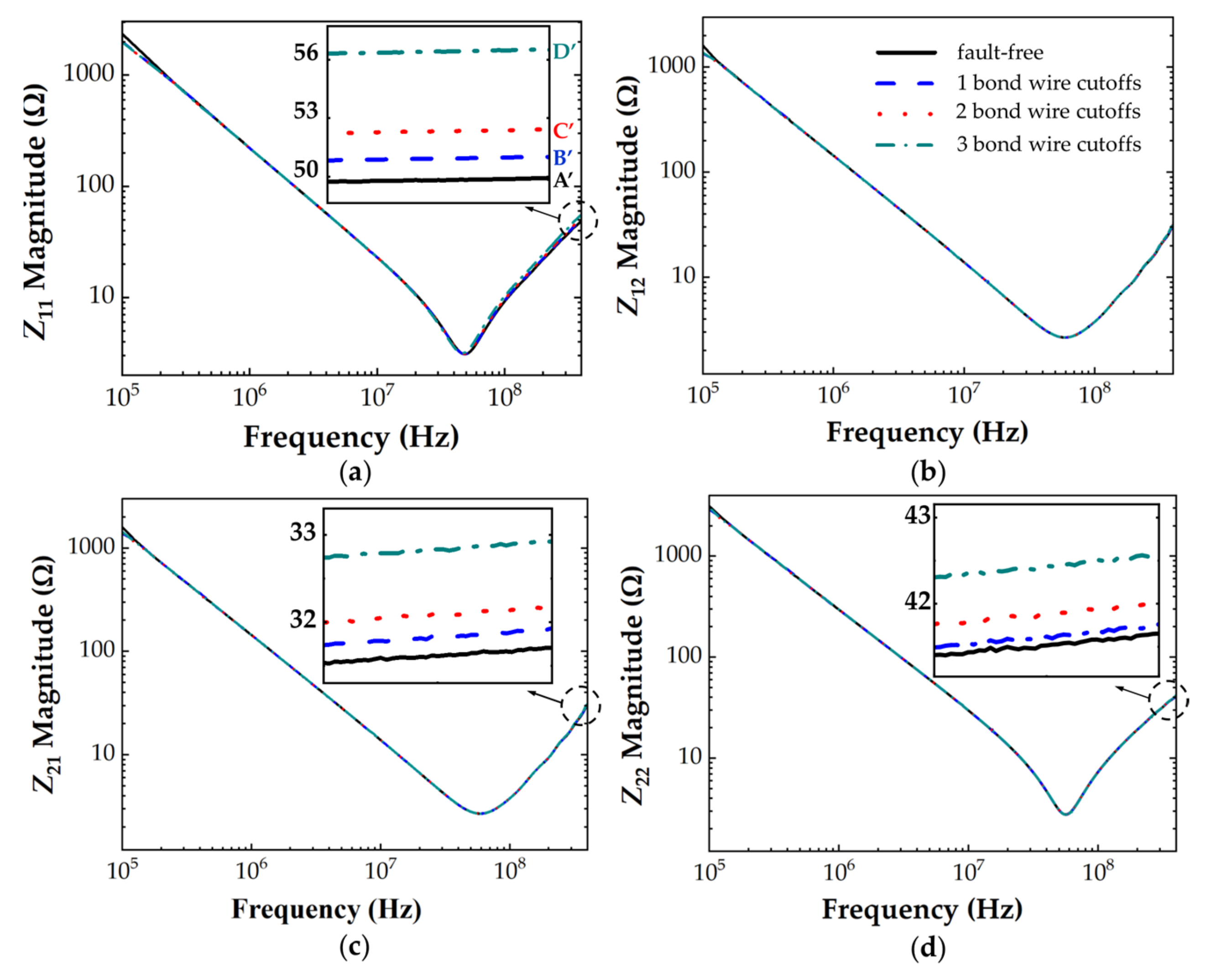

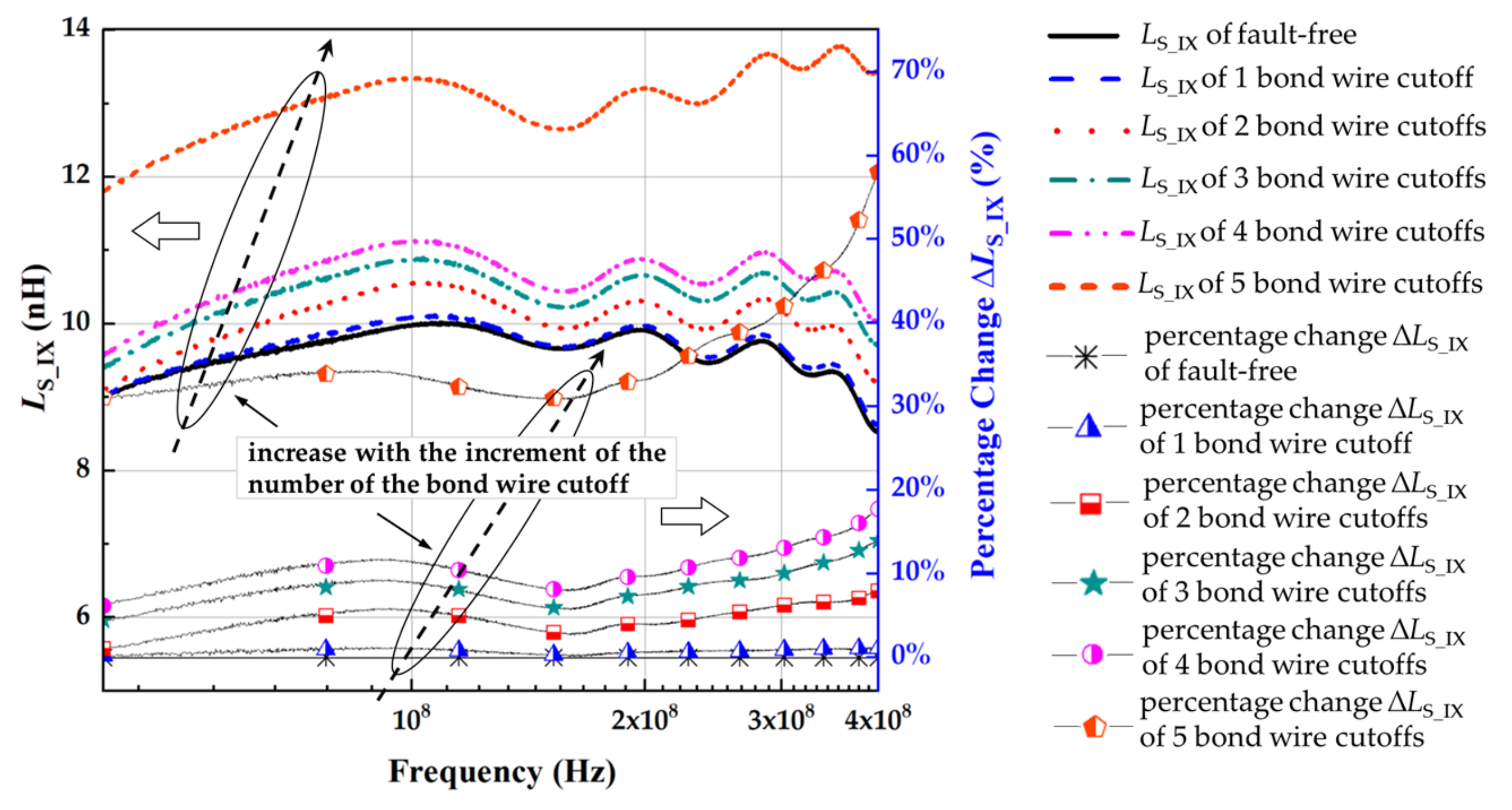

3.2. Analysis of Parasitic Inductance with Bond Wire Fault

3.3. Bond Wire Experimental Results

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

Appendix A

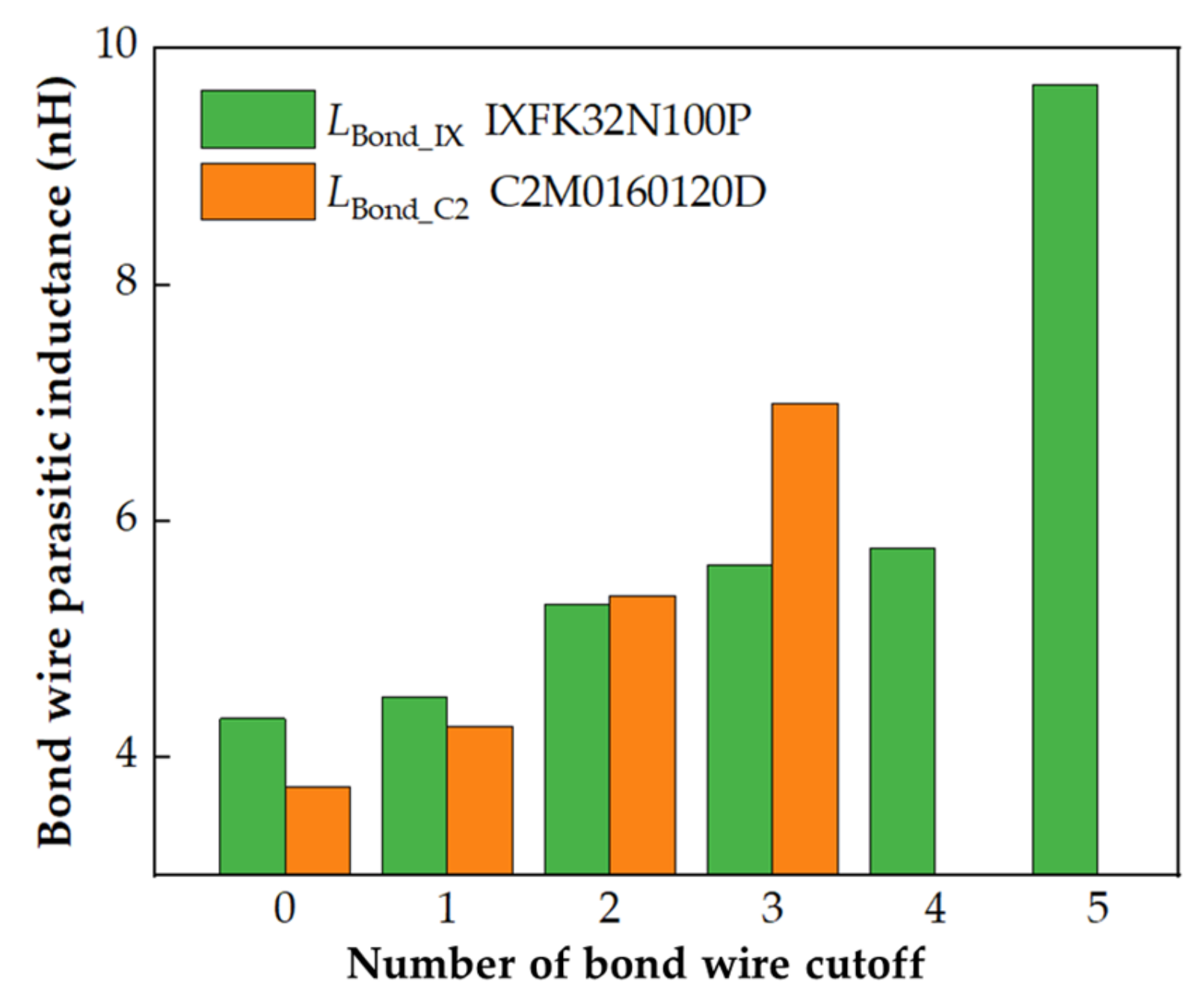

| Bond Wire No. | 1 | 2 | 3 | 4 | 5 | 6 | LBond_No. nH | |

|---|---|---|---|---|---|---|---|---|

| Si MOSFET IXFK32N100P | 1 | / | ||||||

| 2 | ||||||||

| 3 | / | 12.72 | 4.98 | 3.51 | 2.58 | 23.79 | ||

| 4 | 4.98 | 14.19 | 3.76 | 3.57 | 26.5 | |||

| 5 | 3.51 | 3.76 | 7.22 | 3.22 | 17.71 | |||

| 6 | 2.58 | 3.57 | 3.22 | 9.7 | 19.07 | |||

| LBond_IX | 5.30 | |||||||

| SiC MOSFET C2M0160120D | 1 | / | ||||||

| 2 | ||||||||

| 3 | / | 6.78 | 3.84 | 10.63 | ||||

| 4 | 3.84 | 7.00 | 10.84 | |||||

| LBond_C2 | 5.37 | |||||||

| Bond Wire No. | 1 | 2 | 3 | 4 | 5 | 6 | LBond_No. nH | |

|---|---|---|---|---|---|---|---|---|

| Si MOSFET IXFK32N100P | 1 | / | ||||||

| 2 | ||||||||

| 3 | ||||||||

| 4 | / | 14.19 | 3.76 | 3.57 | 21.52 | |||

| 5 | 3.76 | 7.22 | 3.22 | 14.2 | ||||

| 6 | 3.57 | 3.22 | 9.7 | 16.49 | ||||

| LBond_IX | 5.63 | |||||||

| SiC MOSFET C2M0160120D | 1 | / | ||||||

| 2 | ||||||||

| 3 | ||||||||

| 4 | / | 7.00 | 7.00 | |||||

| LBond_C2 | 7.00 | |||||||

| Bond Wire No. | 1 | 2 | 3 | 4 | 5 | 6 | LBond_No. | |

|---|---|---|---|---|---|---|---|---|

| Si MOSFET IXFK32N100P | 1 | / | ||||||

| 2 | ||||||||

| 3 | ||||||||

| 4 | ||||||||

| 5 | / | 7.22 | 3.22 | 10.44 | ||||

| 6 | 3.22 | 9.7 | 12.92 | |||||

| LBond_IX | 5.77 | |||||||

| Bond Wire No. | 1 | 2 | 3 | 4 | 5 | 6 | LBond_No. | |

|---|---|---|---|---|---|---|---|---|

| Si MOSFET IXFK32N100P | 1 | / | ||||||

| 2 | ||||||||

| 3 | ||||||||

| 4 | ||||||||

| 5 | / | |||||||

| 6 | 9.7 | 9.7 | ||||||

| LBond_IX | 9.7 | |||||||

References

- Oh, H.; Han, B.; Mccluskey, P.; Han, C.; Youn, B.D. Physics-of-failure, condition monitoring, and prognostics of insulated gate bipolar transistor modules: A review. IEEE Trans. Power Electron. 2015, 30, 2413–2426. [Google Scholar] [CrossRef]

- Fischer, K.; Pelka, K.; Bartschat, A.; Tegtmeier, B.; Wenske, J. Reliability of power converters in wind turbines: Exploratory analysis of failure and operating data from a worldwide turbine fleet. IEEE Trans. Power Electron. 2019, 34, 6332–6344. [Google Scholar] [CrossRef]

- Yang, S.; Bryant, A.; Mawby, P.; Xiang, D.W.; Ran, L.; Tavner, P. An industry-based survey of reliability in power electronic converters. IEEE Trans. Ind. Appl. 2011, 47, 1441–1451. [Google Scholar] [CrossRef]

- Rodriguez, M.A.; Claudio, A.; Theilliol, D.; Vela, L.G. A new fault detection technique for IGBT based on gate voltage monitoring. In Proceedings of the 2007 IEEE 38th Annual Power Electronics Specialists Conference, Orlando, FL, USA, 17–21 June 2007; IEEE: Manhattan, NY, USA, 2007. [Google Scholar]

- Yang, Y.Y.; Zhang, P.J. A novel bond wire fault detection method for IGBT modules based on turn-on gate voltage overshoot. IEEE Trans. Power Electron. 2021, 36, 7501–7512. [Google Scholar] [CrossRef]

- Gonzalez-Hernando, F.; San-Sebastian, J.; Garcia-Bediaga, A.; Arias, M.; Iannuzzo, F.; Blaabjerg, F. Wear-out condition monitoring of IGBT and MOSFET power modules in inverter operation. IEEE Trans. Ind. Appl. 2019, 55, 6184–6192. [Google Scholar] [CrossRef]

- Wang, C.; He, Y.; Jiang, Y.; Li, L. An anti-Interference online monitoring method for IGBT bond wire aging. Electronics 2021, 10, 1449. [Google Scholar] [CrossRef]

- Du, M.; Xin, J.; Wang, H.; Ouyang, Z. Aging diagnosis of bond wire using on-state drain-source voltage separation for SiC MOSFET. IEEE Trans. Device Mat. Rel. 2021, 21, 41–47. [Google Scholar] [CrossRef]

- Oukaour, A.; Tala-Ighil, B.; Pouderoux, B.; Tounsi, M.; Bouarroudj-Berkani, M.; Lefebvre, S.; Boudart, B. Ageing defect detection on IGBT power modules by artificial training methods based on pattern recognition. Microelectron. Rel. 2011, 51, 386–391. [Google Scholar] [CrossRef]

- Dusmez, S.; Ali, S.H.; Heydarzadeh, M.; Kamath, A.S.; Duran, H.; Akin, B. Aging precursor identification and lifetime estimation for thermally aged discrete package silicon power switches. IEEE Trans. Ind. Appl. 2017, 53, 251–260. [Google Scholar] [CrossRef]

- Zhou, S.Q.; Zhou, L.W.; Sun, P.J. Monitoring potential defects in an IGBT module based on dynamic changes of the gate current. IEEE Trans. Power Electron. 2013, 28, 1479–1487. [Google Scholar] [CrossRef]

- Sun, P.; Gong, C.; Du, X.; Luo, Q.M.; Wang, H.B.; Zhou, L.W. Online condition monitoring for both IGBT module and DC-Link capacitor of power converter based on short-circuit current simultaneously. IEEE Trans. Ind. Electron. 2017, 64, 3662–3671. [Google Scholar] [CrossRef]

- Xu, Z.X.; Xu, F.; Wang, F. Junction temperature measurement of IGBTs using short-circuit current as a temperature-sensitive electrical parameter for converter prototype evaluation. IEEE Trans. Ind. Electron. 2015, 62, 3419–3429. [Google Scholar] [CrossRef]

- Eleffendi, M.A.; Johnson, C.M. Evaluation of on-state voltage VCE(ON) and threshold voltage Vth for real-time health monitoring of IGBT power modules. In Proceedings of the 2015 17th European Conference on Power Electronics and Applications, Geneva, Switzerland, 8–10 September 2015; IEEE: Manhattan, NY, USA, 2015. [Google Scholar]

- Sun, P.J.; Gong, C.; Du, X.; Peng, Y.Z.; Wang, B.; Zhou, L.W. Condition monitoring IGBT module bond wires fatigue using short-circuit current identification. IEEE Trans. Power Electron. 2017, 32, 3777–3786. [Google Scholar] [CrossRef]

- Yang, Y.Y.; Zhang, P.J. In situ insulated gate bipolar transistor junction temperature estimation method via a bond wire degradation independent parameter Turn-OFF Vce overshoot. IEEE Trans. Ind. Electron. 2021, 68, 10118–10129. [Google Scholar] [CrossRef]

- Górecki, K.; Górecki, P.; Zarebski, J. Measurements of parameters of the thermal model of the IGBT module. IEEE Trans. Instrum. Meas. 2019, 68, 4864–4875. [Google Scholar] [CrossRef]

- Halick, M.; Sathik, M.; Kandasamy, K.; Jet, T.K.; Sundarajan, P. Online computation of IGBT on-state resistance for off-shelf three-phase two-level power converter systems. Microelectron. Rel. 2016, 64, 379–386. [Google Scholar] [CrossRef]

- Liu, J.C.; Zhang, G.G.; Chen, Q.; Qi, L.; Geng, Y.S.; Wang, J.H. In situ condition monitoring of IGBTs based on the miller plateau duration. IEEE Trans. Power Electron. 2019, 34, 769–782. [Google Scholar] [CrossRef]

- Ji, B.; Song, X.G.; Cao, W.P.; Pickert, V.; Hu, Y.H.; Mackersie, J.W.; Pierce, G. In-situ diagnostics and prognostics of solder fatigue in IGBT modules for electric vehicle drives. IEEE Trans. Power Electron. 2015, 30, 1535–1543. [Google Scholar]

- Li, K.J.; Tian, G.Y.; Cheng, L.; Yin, A.J.; Cao, W.P.; Crichton, S. State detection of bond wires in IGBT modules using eddy current pulsed thermography. IEEE Trans. Power Electron. 2014, 29, 5000–5009. [Google Scholar] [CrossRef] [Green Version]

- Baker, N.; Dupont, L.; Munk-Nielsen, S.; Iannuzzo, F.; Liserre, M. IR camera validation of IGBT junction temperature measurement via peak gate current. IEEE Trans. Power Electron. 2017, 32, 3099–3111. [Google Scholar] [CrossRef] [Green Version]

- Zhang, J.; Du, X.; Yu, Y.Y.; Zheng, S.; Sun, P.J.; Tai, H.M. Thermal parameter monitoring of IGBT module using case temperature. IEEE Trans. Power Electron. 2019, 34, 7942–7956. [Google Scholar] [CrossRef]

- Dreher, P.; Schmidt, R.; Vetter, A.; Heppb, J.; Karl, A.; Brabec, C.J. Non-destructive imaging of defects in Ag-sinter die attach layers–A comparative study including X-ray, scanning acoustic microscopy and thermography. Microelectron. Rel. 2018, 88–90, 365–370. [Google Scholar] [CrossRef]

- Feng, W.W.; Meng, Q.F.; Xie, Y.B.; Fan, H. Wire bonding quality monitoring via refining process of electrical signal from ultrasonic generator. Mech. Syst. Signal Process. 2011, 25, 884–900. [Google Scholar] [CrossRef]

- Hanif, A.; Azad, A.N.M.W.; Khan, F. Detection of bond wire lift off in IGBT power modules using ultrasound resonators. In Proceedings of the 2020 IEEE Applied Power Electronics Conference and Exposition, New Orleans, LA, USA, 15–19 March 2020. [Google Scholar]

- Paul, C.R. Inductance: Loop and Partial; John Wiley & Sons: Hoboken, NJ, USA, 2010; pp. 195–245. [Google Scholar]

- Liu, T.J.; Feng, Y.J.; Ning, R.T.; Wong, T.T.Y.; Shen, Z.J. Extracting parasitic inductances of IGBT power modules with two-port S−parameter measurement. In Proceedings of the 2017 IEEE Transportation Electrification Conference and Expo, Chicago, IL, USA, 22–24 June 2017; IEEE: Manhattan, NY, USA, 2017. [Google Scholar]

- Liu, T.J.; Wong, T.T.Y.; Shen, Z.J. A new characterization technique for extracting parasitic inductances of SiC power MOSFETs in discrete and module packages based on two-port S−parameters measurement. IEEE Trans. Power Electron. 2018, 33, 9819–9833. [Google Scholar] [CrossRef]

- Gugliandolo, G.; Marinković, Z.; Campobello, G.; Crupi, G.; Donato, N. On the performance evaluation of commercial SAW resonators by means of a direct and reliable equivalent-circuit extraction. Micromachines 2021, 12, 303. [Google Scholar] [CrossRef]

- Williams, D.F.; Corson, P.; Sharma, J.; Krishnaswamy, H.; Tai, W.; George, Z.; Ricketts, D.; Watson, P.; Dacquay, E.; Voinigescu, S.P. Calibration-kit design for millimeter-wave silicon integrated circuits. IEEE Trans. Microw. Theory Techol. 2013, 61, 2685–2694. [Google Scholar] [CrossRef]

| Bond Wire No. | 1 | 2 | 3 | 4 | 5 | 6 | |

|---|---|---|---|---|---|---|---|

| IXFK32N100P | l (mm) | 13.54 | 8.76 | 14.16 | 15.50 | 8.94 | 11.35 |

| d (mm) | 0.279 | ||||||

| C2M0160120D | l (mm) | 5.78 | 5.90 | 7.85 | 8.00 | ||

| d (mm) | 0.178 | ||||||

| Bond Wire No. | 1 | 2 | 3 | 4 | 5 | 6 | LBond_No. nH | |

|---|---|---|---|---|---|---|---|---|

| Si MOSFET IXFK32N100P | 1 | 12.04 | 3.4 | 4.66 | 3.76 | 2.16 | 2.08 | 28.1 |

| 2 | 3.40 | 7.04 | 3.66 | 3.40 | 2.39 | 1.86 | 21.75 | |

| 3 | 4.66 | 3.66 | 12.72 | 4.98 | 3.51 | 2.58 | 32.11 | |

| 4 | 3.76 | 3.4 | 4.98 | 14.19 | 3.76 | 3.57 | 33.66 | |

| 5 | 2.16 | 2.39 | 3.51 | 3.76 | 7.22 | 3.22 | 22.26 | |

| 6 | 2.08 | 1.86 | 2.58 | 3.57 | 3.22 | 9.7 | 23.01 | |

| LBond_IX | 4.33 | |||||||

| SiC MOSFET C2M0160120D | 1 | 5.63 | 3.11 | 3.11 | 1.85 | 13.70 | ||

| 2 | 3.11 | 5.83 | 3.24 | 2.40 | 14.59 | |||

| 3 | 3.11 | 3.24 | 6.78 | 3.84 | 16.99 | |||

| 4 | 1.85 | 2.40 | 3.84 | 7.00 | 15.08 | |||

| LBond_C2 | 3.75 | |||||||

| Bond Wire No. | 1 | 2 | 3 | 4 | 5 | 6 | LBond_No. nH | |

|---|---|---|---|---|---|---|---|---|

| Si MOSFET IXFK32N100P | 1 | / | ||||||

| 2 | / | 7.04 | 3.66 | 3.4 | 2.39 | 1.86 | 18.35 | |

| 3 | 3.66 | 12.72 | 4.98 | 3.51 | 2.58 | 27.45 | ||

| 4 | 3.4 | 4.98 | 14.19 | 3.76 | 3.57 | 29.9 | ||

| 5 | 2.39 | 3.51 | 3.76 | 7.22 | 3.22 | 20.1 | ||

| 6 | 1.86 | 2.58 | 3.57 | 3.22 | 9.7 | 20.93 | ||

| LBond_IX | 4.51 | |||||||

| SiC MOSFET C2M0160120D | 1 | / | ||||||

| 2 | / | 5.83 | 3.24 | 2.40 | 11.47 | |||

| 3 | 3.24 | 6.78 | 3.84 | 13.87 | ||||

| 4 | 2.40 | 3.84 | 7.00 | 13.24 | ||||

| LBond_C2 | 4.26 | |||||||

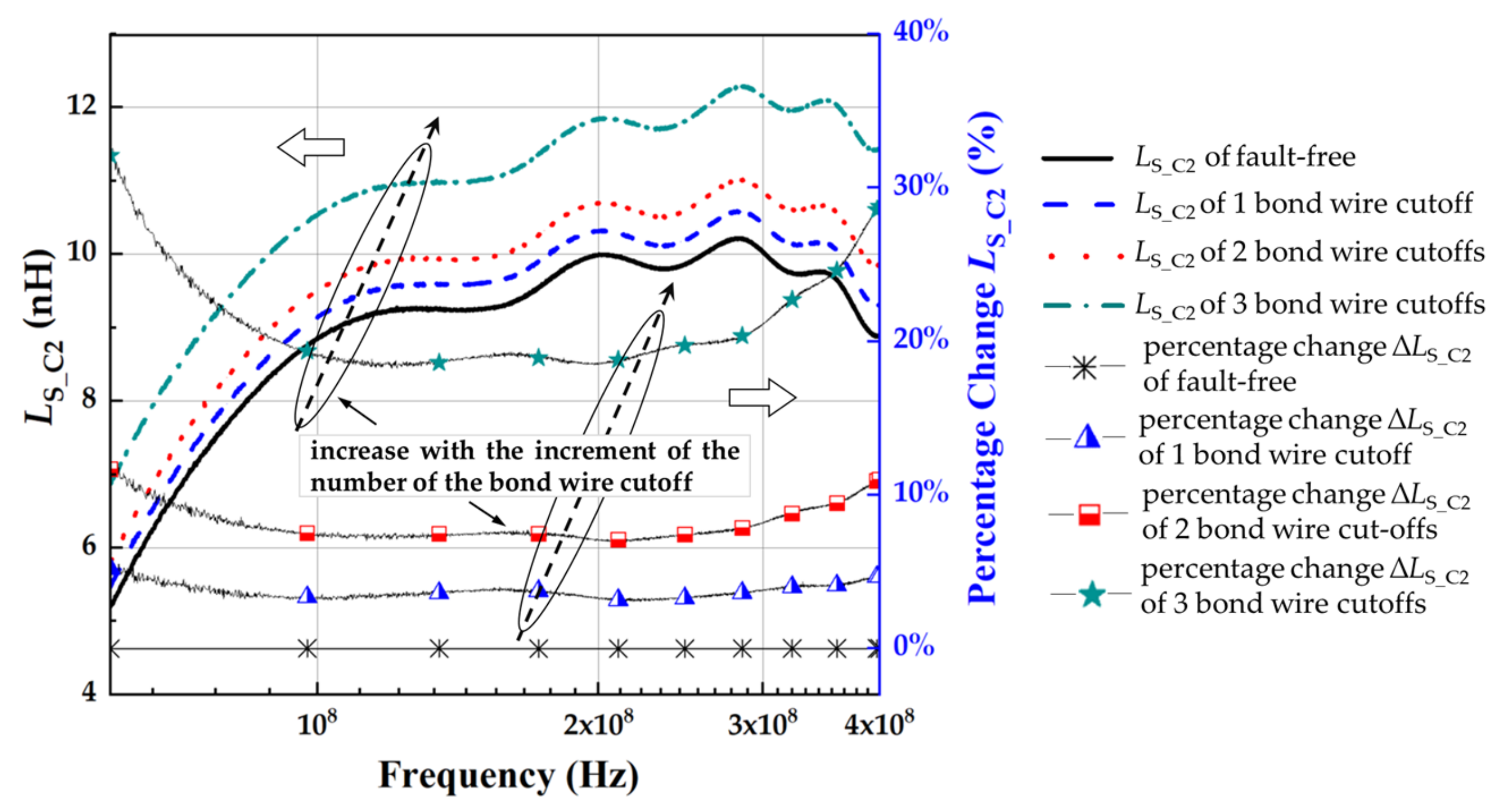

| Bond Wire Cutoff Model | Si MOSFET | SiC MOSFET | ||||||

|---|---|---|---|---|---|---|---|---|

| 400 MHz | fSRF | 400 MHz | fSRF | |||||

| LS nH | Percentage Change % | RS Ω | Percentage Change % | LS nH | Percentage Change % | RS Ω | Percentage Change % | |

| 0 | 8.52 | 0 | 0.012 | 0 | 8.88 | 0 | 0.401 | 0 |

| 1 | 8.62 | 1.12 | 0.014 | 16.67% | 9.30 | 4.71 | 0.406 | 1.25% |

| 2 | 9.20 | 7.96 | 0.013 | 8.33% | 9.85 | 10.97 | 0.418 | 4.24% |

| 3 | 9.71 | 13.98 | 0.014 | −8.33% | 11.43 | 28.79 | 0.470 | 17.21% |

| 4 | 10.03 | 17.75 | 0.006 | −50.00% | ||||

| 5 | 13.46 | 58.02 | 0.029 | 141.67% | ||||

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yun, M.; Cai, M.; Yang, D.; Yang, Y.; Xiao, J.; Zhang, G. Bond Wire Damage Detection Method on Discrete MOSFETs Based on Two-Port Network Measurement. Micromachines 2022, 13, 1075. https://doi.org/10.3390/mi13071075

Yun M, Cai M, Yang D, Yang Y, Xiao J, Zhang G. Bond Wire Damage Detection Method on Discrete MOSFETs Based on Two-Port Network Measurement. Micromachines. 2022; 13(7):1075. https://doi.org/10.3390/mi13071075

Chicago/Turabian StyleYun, Minghui, Miao Cai, Daoguo Yang, Yiren Yang, Jing Xiao, and Guoqi Zhang. 2022. "Bond Wire Damage Detection Method on Discrete MOSFETs Based on Two-Port Network Measurement" Micromachines 13, no. 7: 1075. https://doi.org/10.3390/mi13071075

APA StyleYun, M., Cai, M., Yang, D., Yang, Y., Xiao, J., & Zhang, G. (2022). Bond Wire Damage Detection Method on Discrete MOSFETs Based on Two-Port Network Measurement. Micromachines, 13(7), 1075. https://doi.org/10.3390/mi13071075