Reduced Etch Lag and High Aspect Ratios by Deep Reactive Ion Etching (DRIE)

Abstract

1. Introduction

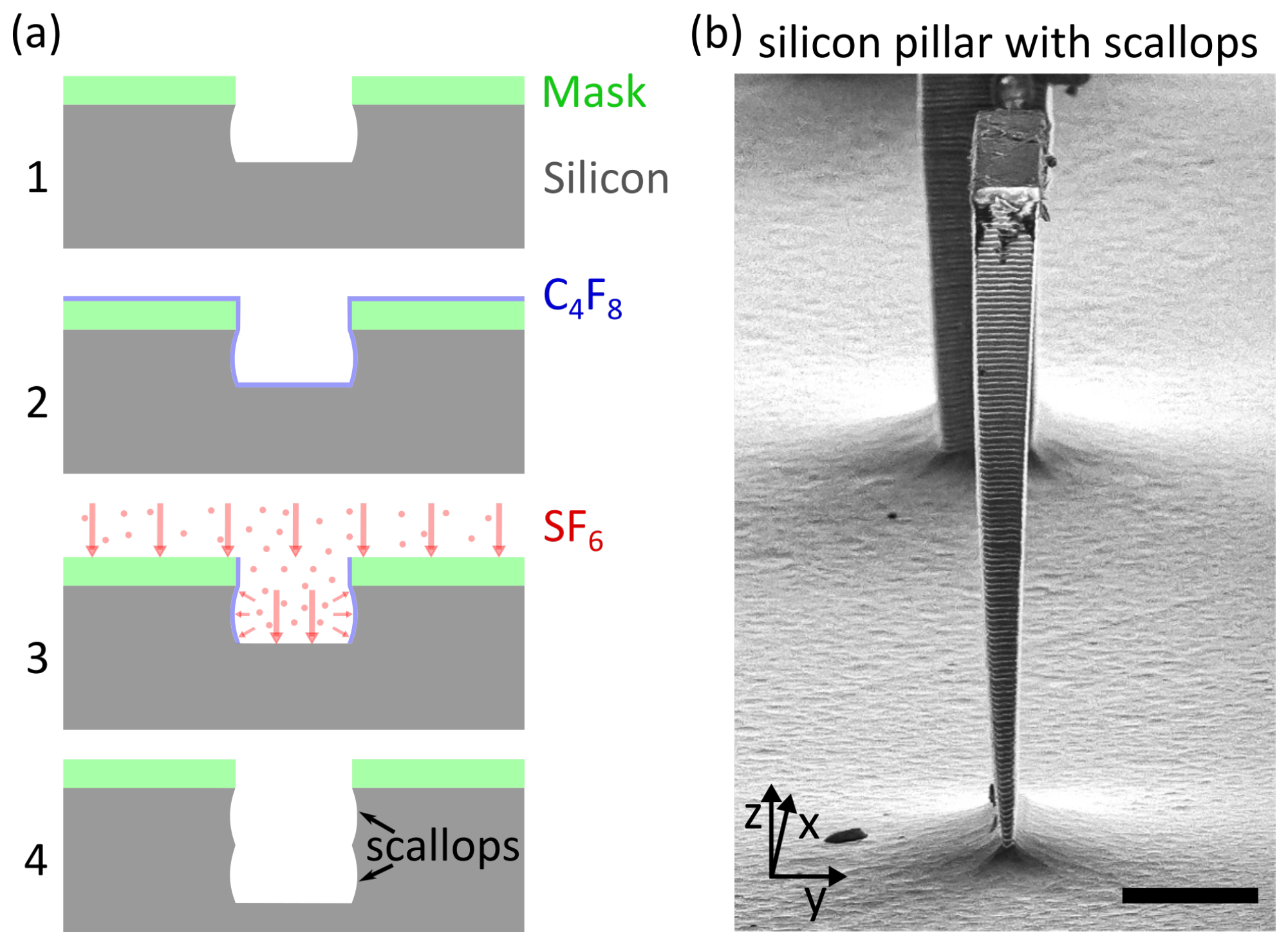

2. Materials and Methods

3. Results & Discussion

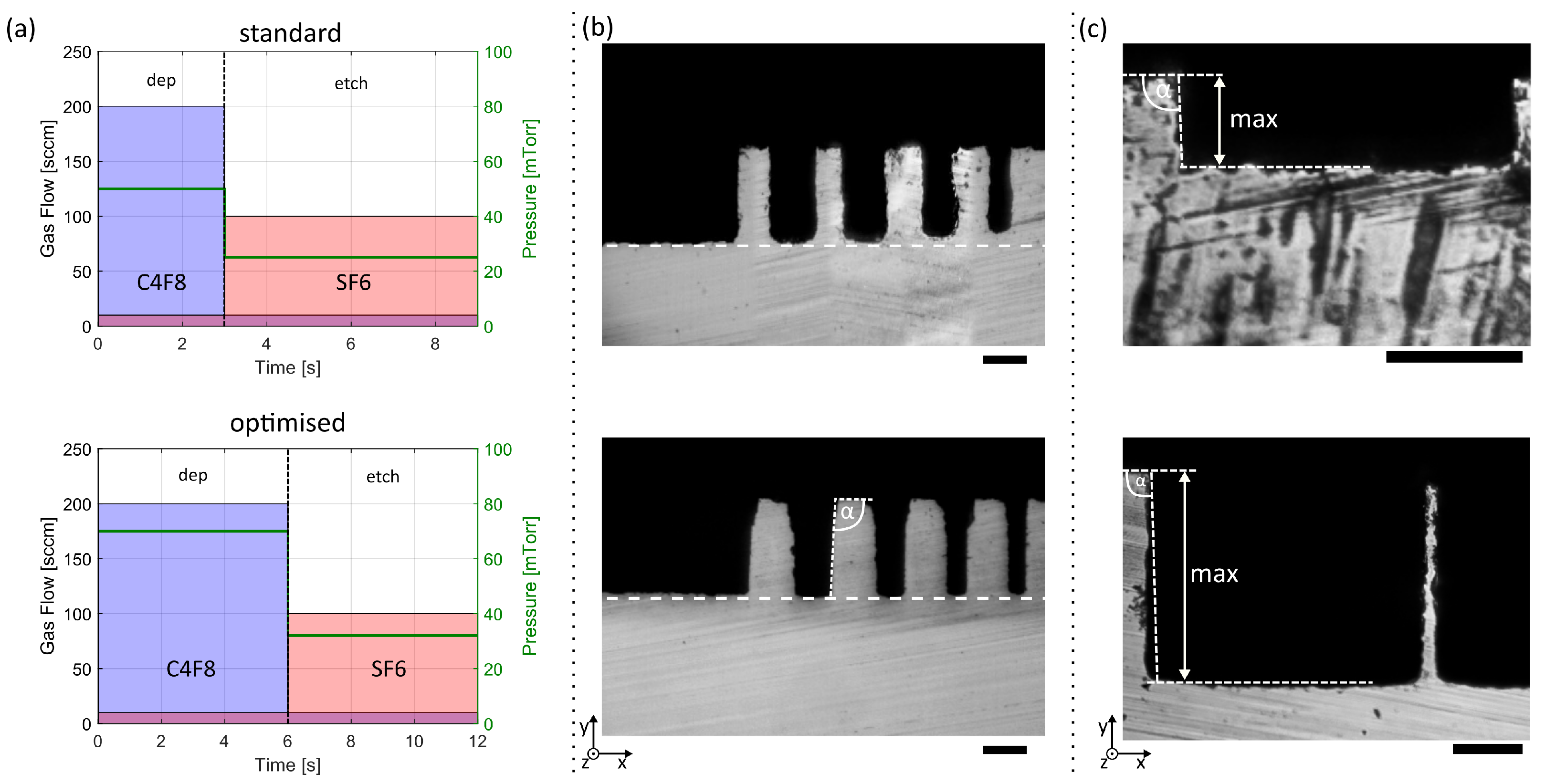

3.1. Bosch Process Optimisation for Reduced RIE Lag

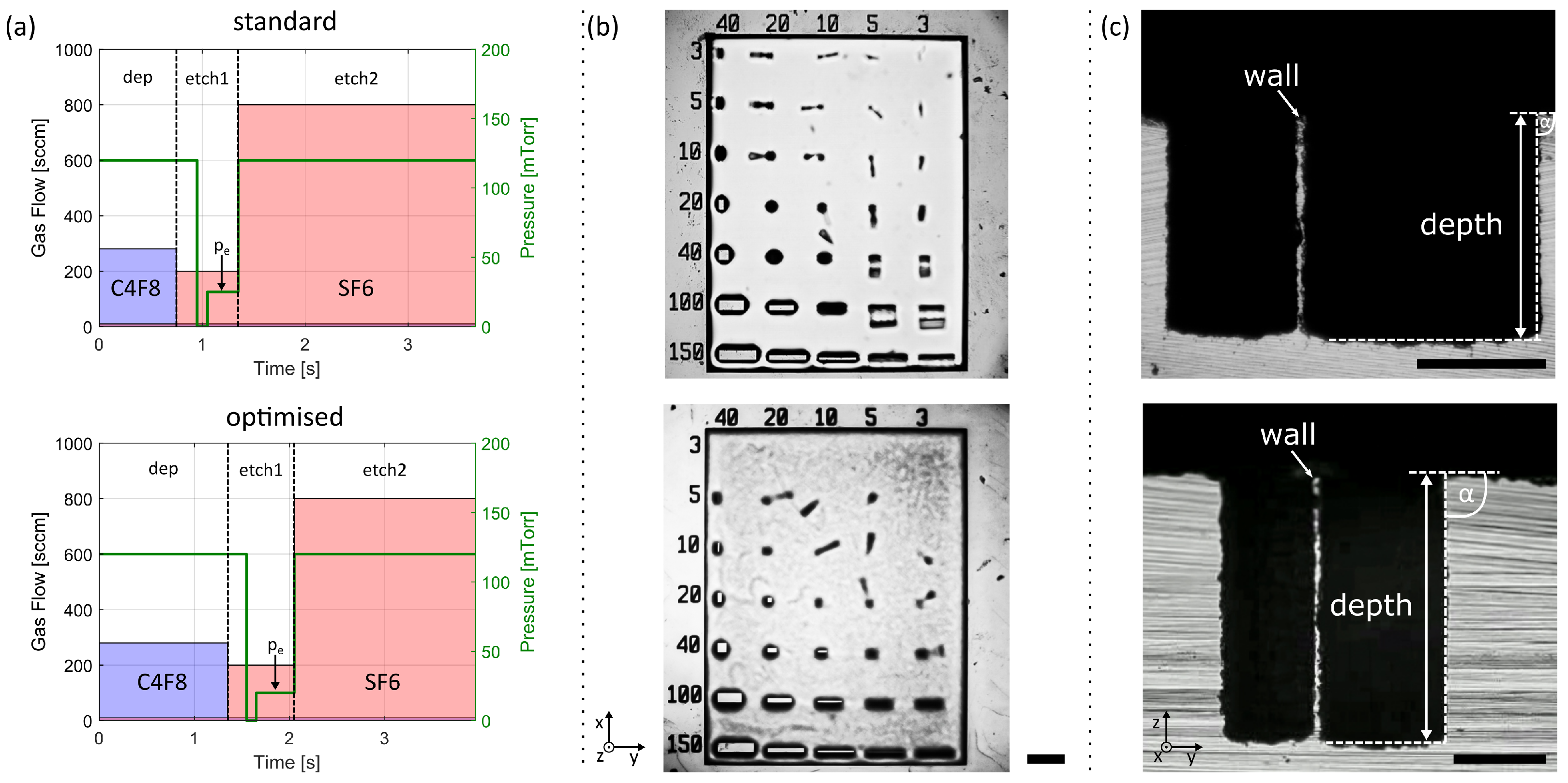

3.2. High Rate Process Optimisation for Deep Etch

4. Conclusions

Supplementary Materials

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Abbreviations

| ICP | inductively coupled plasma |

| DRIE | deep reactive ion etching |

| RIE | reactive ion etching |

| PR | photoresist |

| HMDS | hexamethyldisilazane |

References

- Grayson, A.; Shawgo, R.; Johnson, A.; Flynn, N.; Li, Y.; Cima, M.; Langer, R. A BioMEMS Review: MEMS Technology for Physiologically Integrated Devices. Proc. IEEE 2004, 92, 6–21. [Google Scholar] [CrossRef]

- Whitesides, G.M. The origins and the future of microfluidics. Nature 2006, 442, 368–373. [Google Scholar] [CrossRef] [PubMed]

- Dittrich, P.S.; Tachikawa, K.; Manz, A. Micro Total Analysis Systems. Latest Advancements and Trends. Anal. Chem. 2006, 78, 3887–3908. [Google Scholar] [CrossRef] [PubMed]

- Wu, B.; Kumar, A.; Pamarthy, S. High aspect ratio silicon etch: A review. J. Appl. Phys. 2010, 108, 051101. [Google Scholar] [CrossRef]

- Laermer, F.; Schilp, A. Method of Anisotropically Etching Silicon. U.S. Patent 5501893, 26 March 1996. [Google Scholar]

- Laermer, F.; Urban, A. MEMS at Bosch—Si plasma etch success story, history, applications, and products. Plasma Process. Polym. 2019, 16, 1800207. [Google Scholar] [CrossRef]

- Laermer, F.; Franssila, S.; Sainiemi, L.; Kolari, K. Deep reactive ion etching. In Handbook of Silicon Based MEMS Materials and Technologies; Elsevier: Amsterdam, The Netherlands, 2020; pp. 417–446. [Google Scholar] [CrossRef]

- Chen, S.C.; Lin, Y.C.; Wu, J.C.; Horng, L.; Cheng, C.H. Parameter optimization for an ICP deep silicon etching system. Microsyst. Technol. 2007, 13, 465–474. [Google Scholar] [CrossRef]

- Chung, C.K. Geometrical pattern effect on silicon deep etching by an inductively coupled plasma system. J. Micromech. Microeng. 2004, 14, 656–662. [Google Scholar] [CrossRef]

- Lai, S.L.; Johnson, D.; Westerman, R. Aspect ratio dependent etching lag reduction in deep silicon etch processes. J. Vac. Sci. Technol. A Vac. Surf. Film. 2006, 24, 1283–1288. [Google Scholar] [CrossRef]

- Fu, L.; Miao, J.; Li, X.; Lin, R. Study of deep silicon etching for micro-gyroscope fabrication. Appl. Surf. Sci. 2001, 177, 78–84. [Google Scholar] [CrossRef]

- Laermer, F.; Urban, A. Challenges, developments and applications of silicon deep reactive ion etching. Microelectron. Eng. 2003, 677–68, 349–355. [Google Scholar] [CrossRef]

- Abdolvand, R.; Ayazi, F. An advanced reactive ion etching process for very high aspect-ratio sub-micron wide trenches in silicon. Sens. Actuators A Phys. 2008, 144, 109–116. [Google Scholar] [CrossRef]

- Parasuraman, J.; Summanwar, A.; Marty, F.; Basset, P.; Angelescu, D.E.; Bourouina, T. Deep reactive ion etching of sub-micrometer trenches with ultra high aspect ratio. Microelectron. Eng. 2014, 113, 35–39. [Google Scholar] [CrossRef]

- Morton, K.J.; Nieberg, G.; Bai, S.; Chou, S.Y. Wafer-scale patterning of sub-40 nm diameter and high aspect ratio (>50:1) silicon pillar arrays by nanoimprint and etching. Nanotechnology 2008, 19, 345301. [Google Scholar] [CrossRef]

- Owen, K.J.; VanDerElzen, B.; Peterson, R.L.; Najafi, K. High aspect ratio deep silicon etching. In Proceedings of the 2012 IEEE 25th International Conference on Micro Electro Mechanical Systems (MEMS), Paris, France, 29 January–2 February 2012; pp. 251–254. [Google Scholar] [CrossRef]

- Blauw, M.A.; Zijlstra, T.; van der Drift, E. Balancing the etching and passivation in time-multiplexed deep dry etching of silicon. J. Vac. Sci. Technol. B Microelectron. Nanometer Struct. 2001, 19, 2930. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gerlt, M.S.; Läubli, N.F.; Manser, M.; Nelson, B.J.; Dual, J. Reduced Etch Lag and High Aspect Ratios by Deep Reactive Ion Etching (DRIE). Micromachines 2021, 12, 542. https://doi.org/10.3390/mi12050542

Gerlt MS, Läubli NF, Manser M, Nelson BJ, Dual J. Reduced Etch Lag and High Aspect Ratios by Deep Reactive Ion Etching (DRIE). Micromachines. 2021; 12(5):542. https://doi.org/10.3390/mi12050542

Chicago/Turabian StyleGerlt, Michael S., Nino F. Läubli, Michel Manser, Bradley J. Nelson, and Jürg Dual. 2021. "Reduced Etch Lag and High Aspect Ratios by Deep Reactive Ion Etching (DRIE)" Micromachines 12, no. 5: 542. https://doi.org/10.3390/mi12050542

APA StyleGerlt, M. S., Läubli, N. F., Manser, M., Nelson, B. J., & Dual, J. (2021). Reduced Etch Lag and High Aspect Ratios by Deep Reactive Ion Etching (DRIE). Micromachines, 12(5), 542. https://doi.org/10.3390/mi12050542