High Thermal Dissipation of Normally off p-GaN Gate AlGaN/GaN HEMTs on 6-Inch N-Doped Low-Resistivity SiC Substrate

Abstract

:1. Introduction

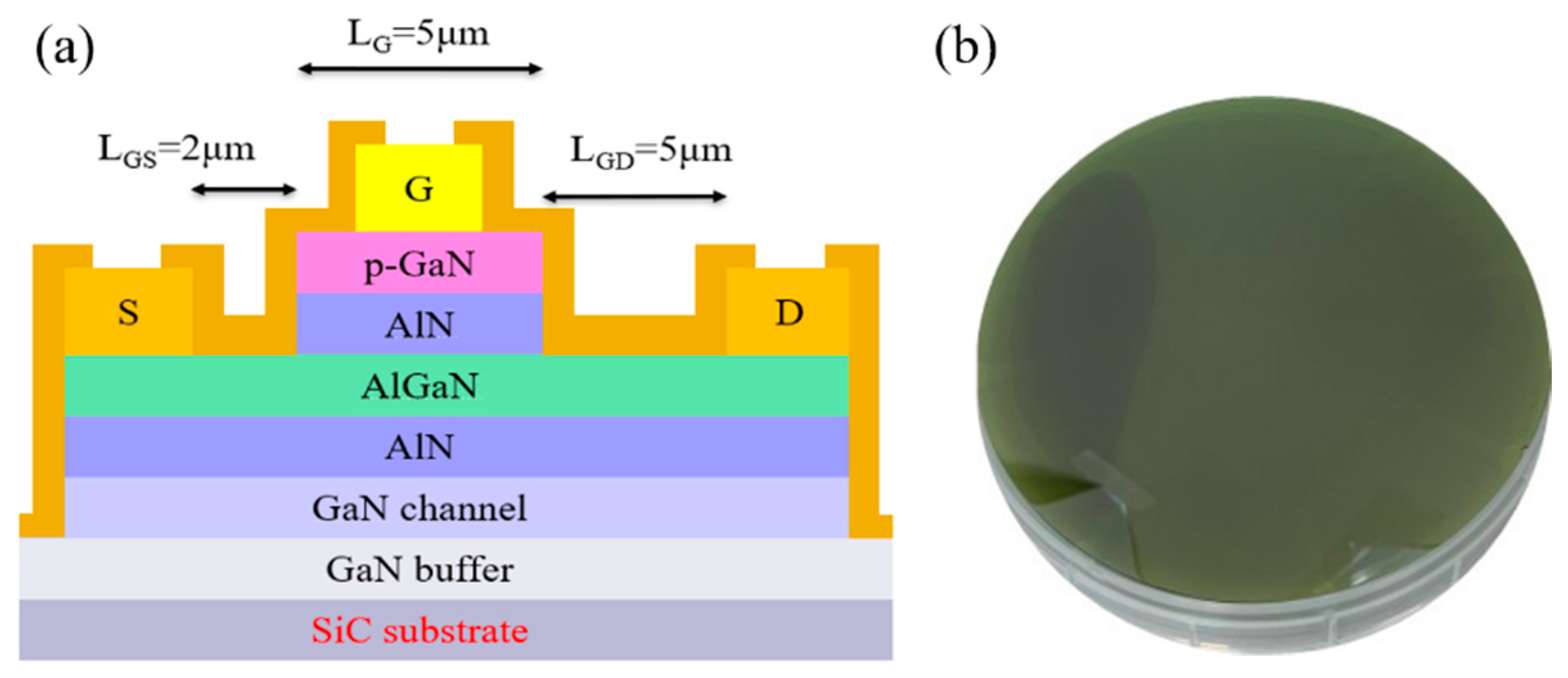

2. Experimental Procedures

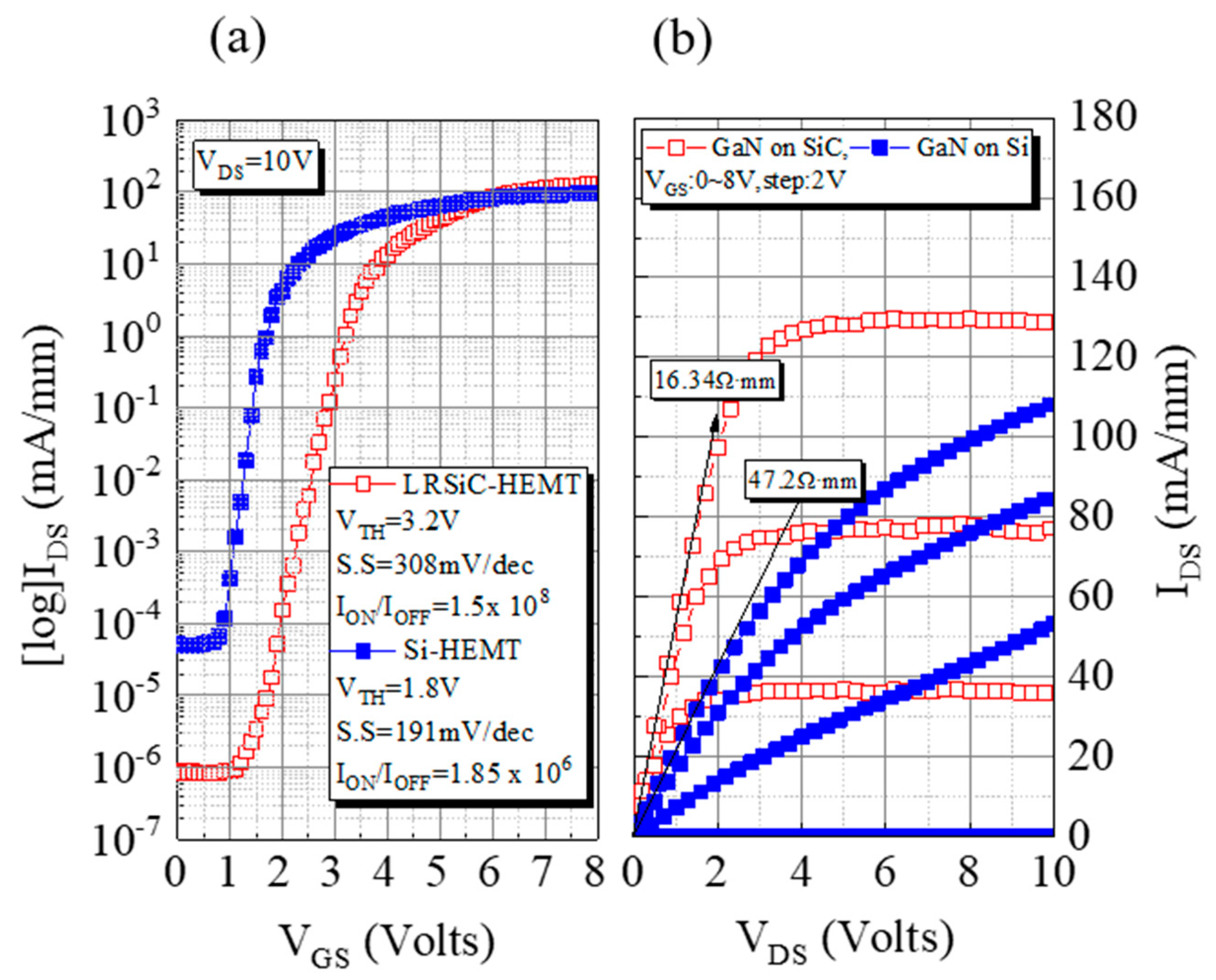

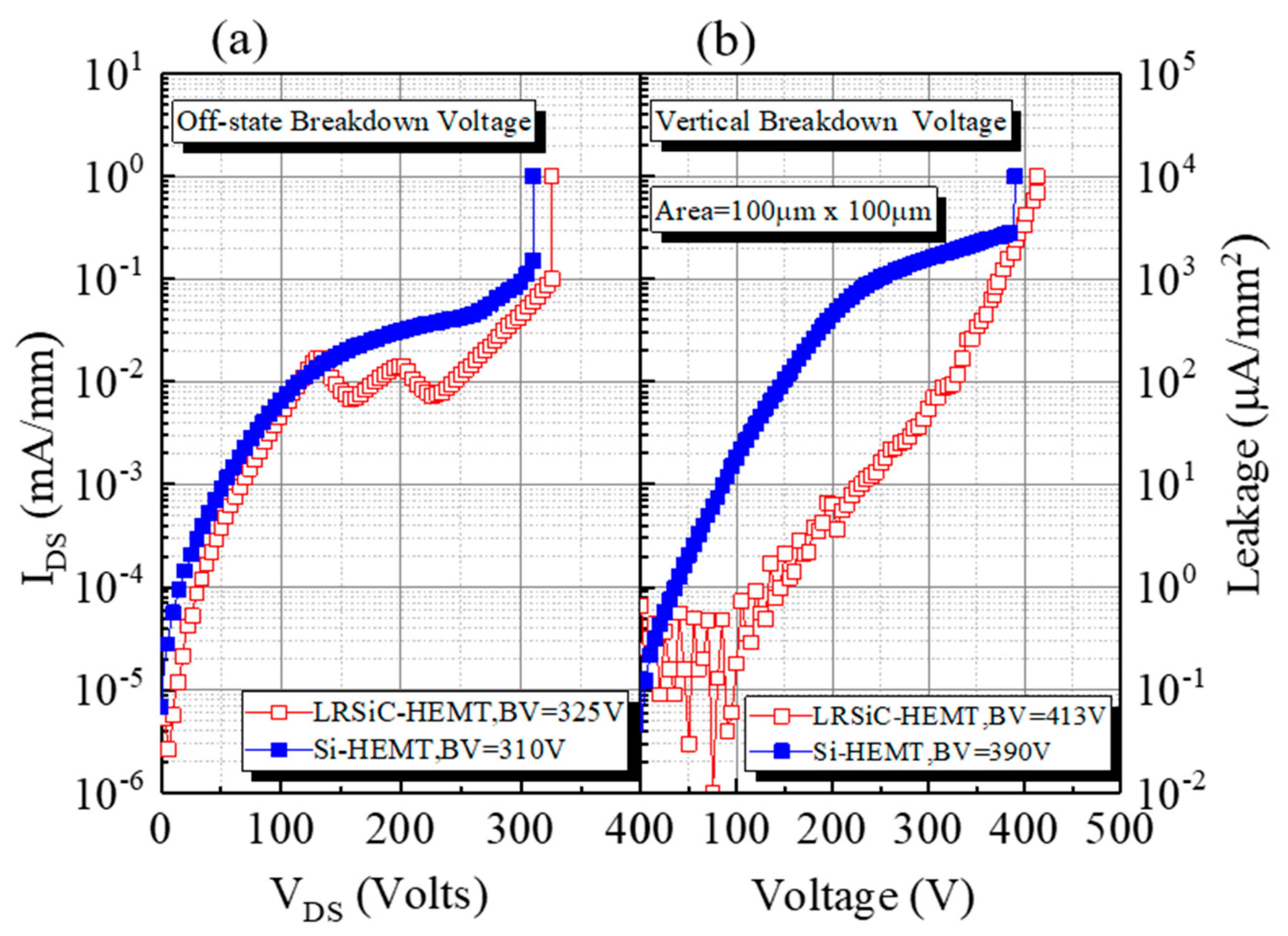

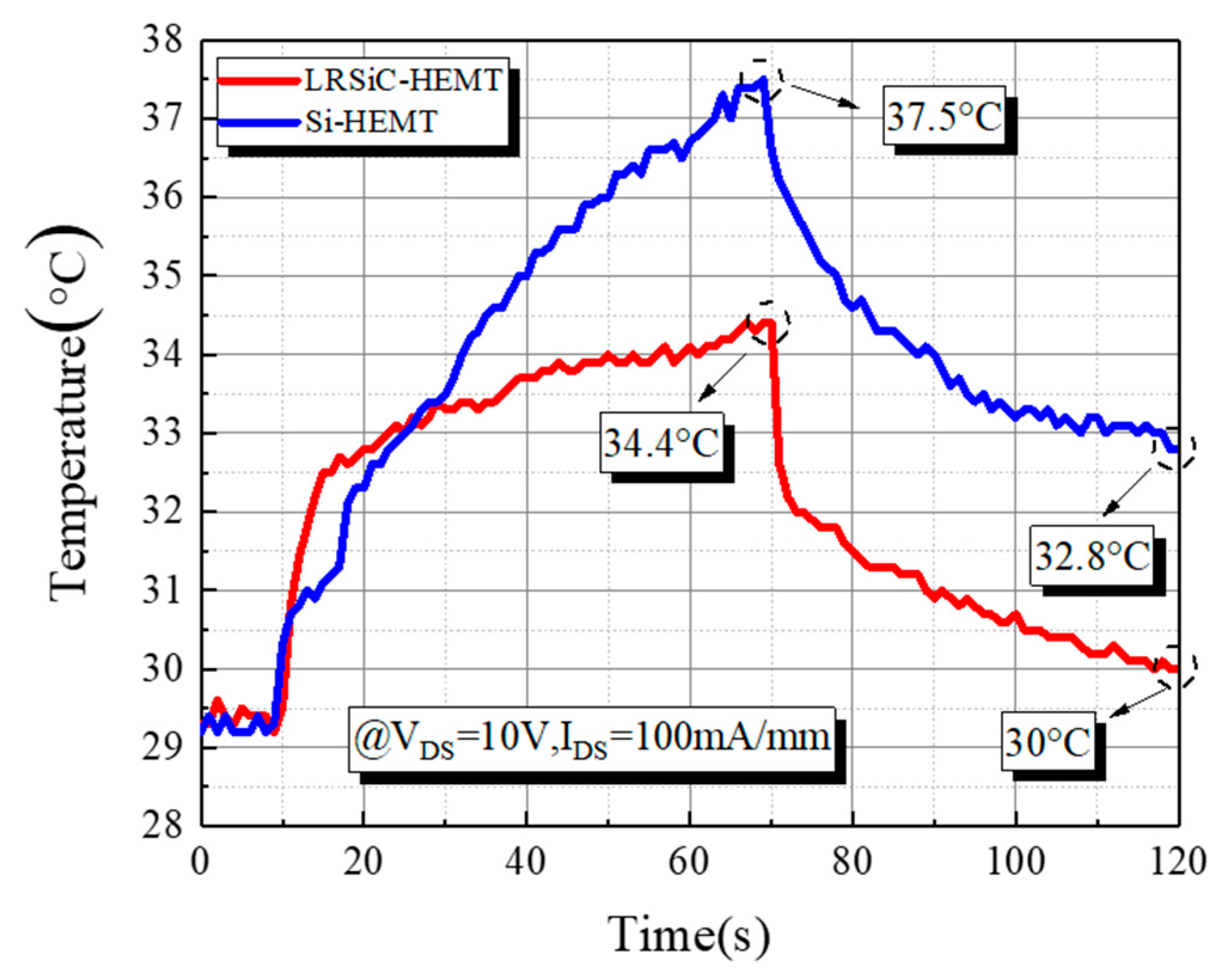

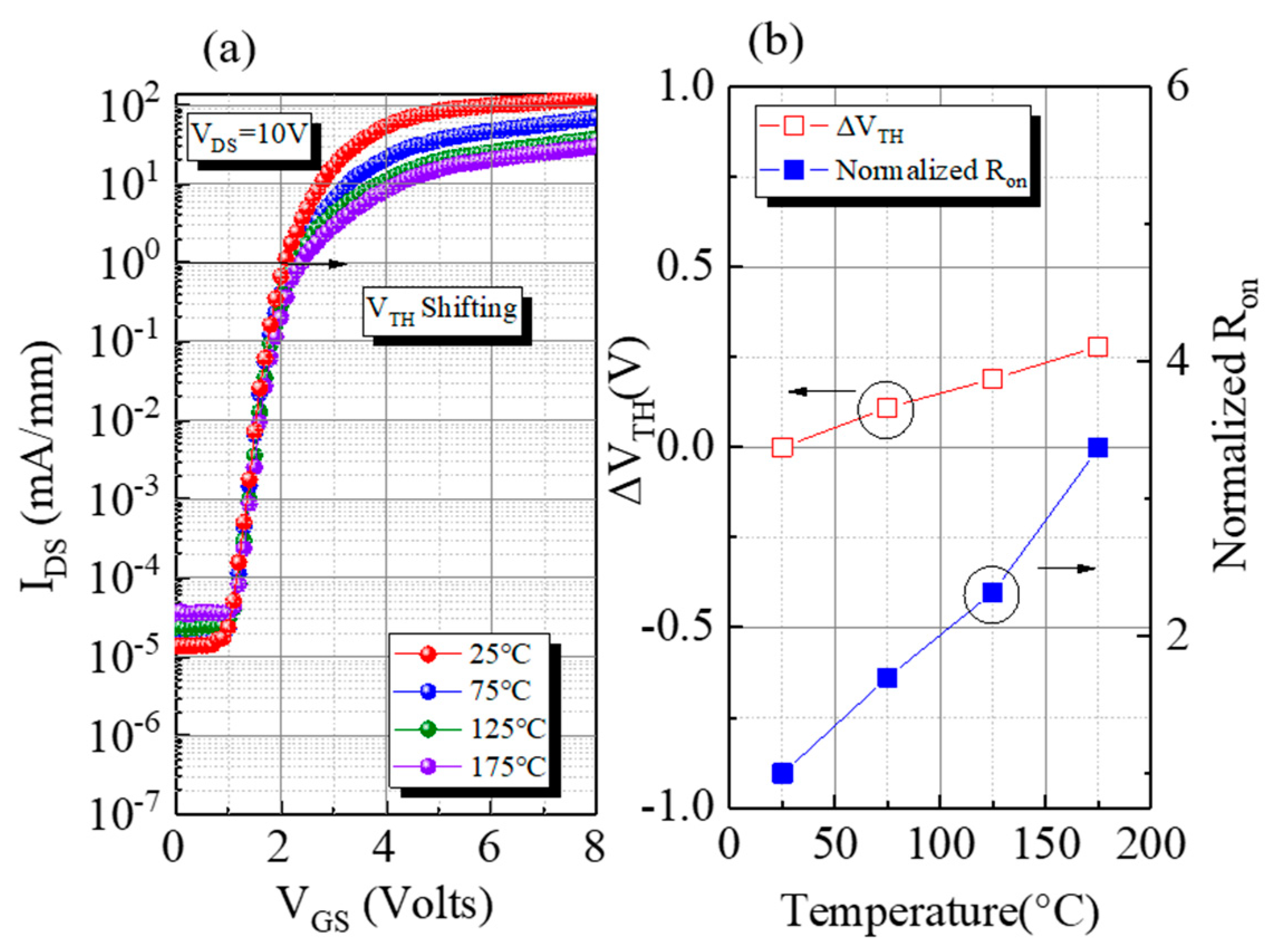

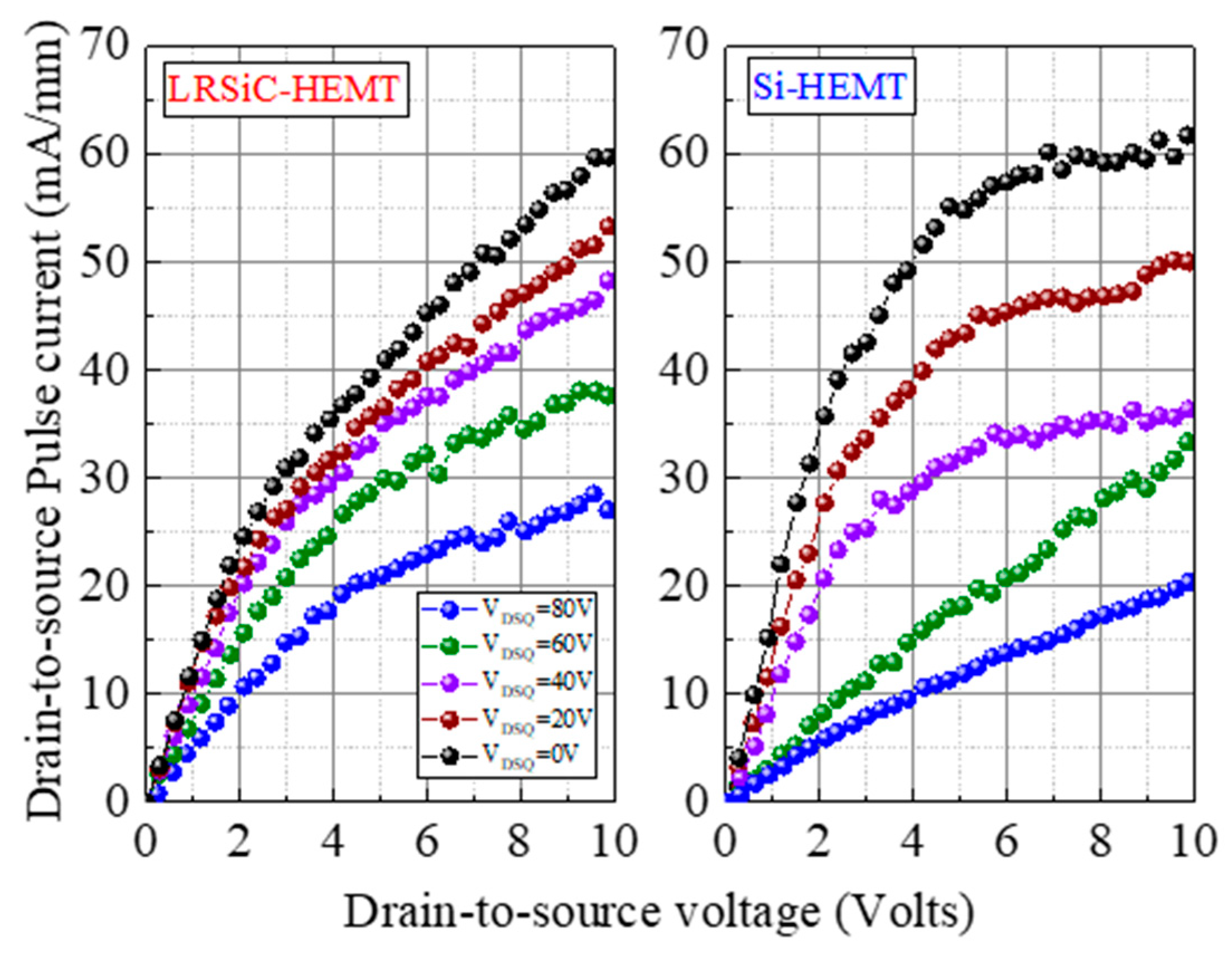

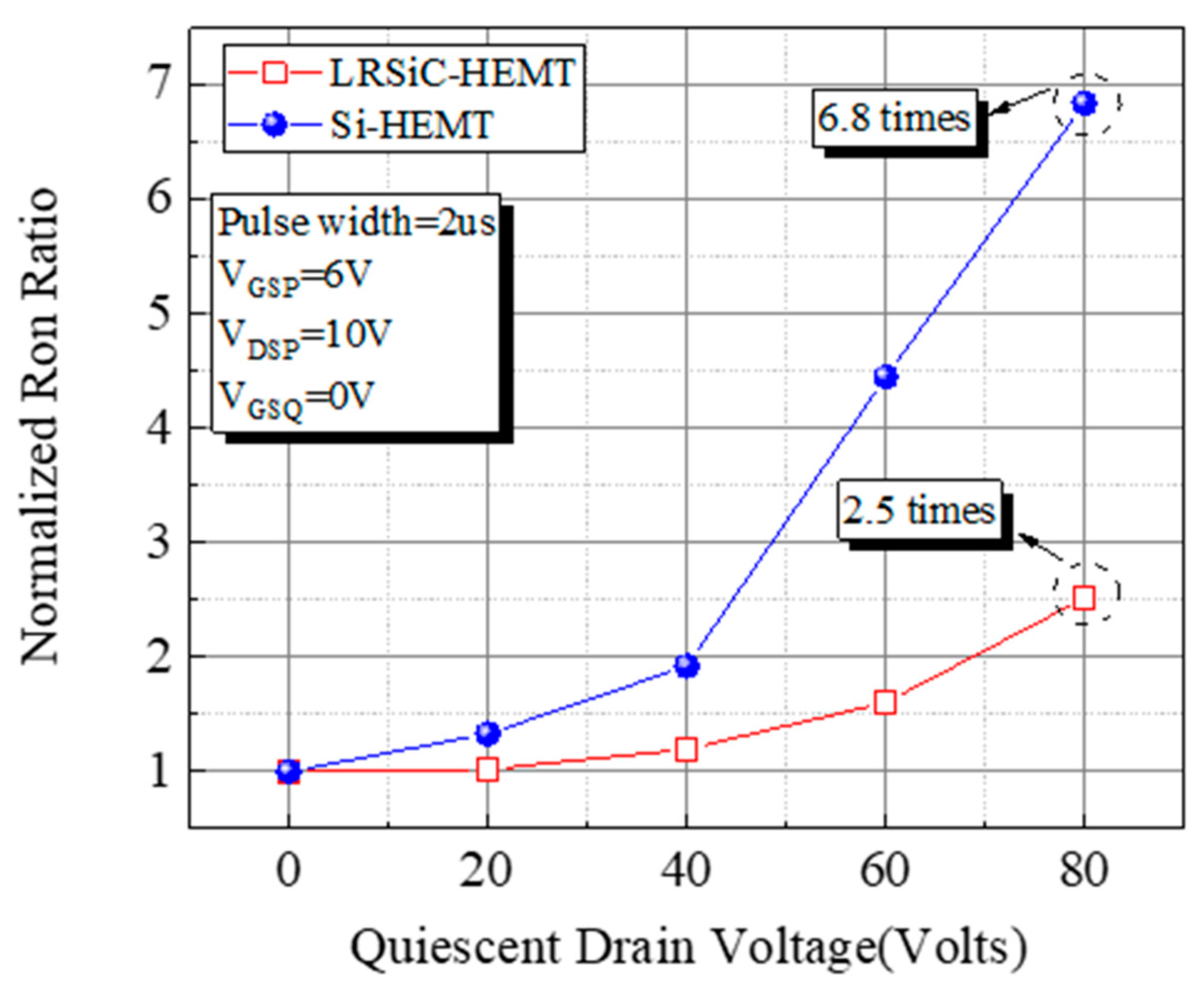

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Khan, M.A.; Chen, Q.; Sun, C.J.; Yang, J.W.; Blasingame, M.; Shur, M.S.; Park, H. Enhancement and depletion mode GaN/AlGaN heterostructure field effect transistors. Appl. Phys. Lett. 1996, 68, 514–516. [Google Scholar] [CrossRef]

- Chen, W.; Wong, K.-Y.; Chen, K.J. Monolithic integration of lateral field-effect rectifier with normally-off HEMT for GaN-onSi switch-mode power supply converters. In Proceedings of the IEEE IEDM, San Francisco, CA, USA, 15–17 December 2008; pp. 1–4. [Google Scholar]

- Cai, Y.; Zhou, Y.; Chen, K.J.; Lau, K.M. Highperformance enhancement-mode AlGaN/GaN HEMTs using fluoridebased plasma treatment. IEEE Electron. Device Lett. 2005, 26, 435–437. [Google Scholar] [CrossRef]

- Ohmaki, Y.; Tanimoto, M.; Akamatsu, S.; Mukai, T. Enhancementmode AlGaN/AlN/GaN high electron mobility transistor with low ON-state resistance and high breakdown voltage. Jpn. J. Appl. Phys. 2006, 45, 42–45. [Google Scholar] [CrossRef]

- Oka, T.; Nozawa, T. AlGaN/GaN recessed MIS-gate HFET with high-threshold-voltage normally-off operation for power electronics applications. IEEE Electron. Device Lett. 2008, 29, 668–670. [Google Scholar] [CrossRef]

- Kim, K.-W.; Jung, S.-D.; Kim, D.-S.; Kang, H.-S.; Im, K.-S.; Oh, J.-J.; Ha, J.-B.; Shin, J.-K.; Lee, J.-H. Effects of TMAH treatment on device performance of normally off Al2O3/GaN MOSFET. IEEE Electron. Device Lett. 2011, 32, 1376–1378. [Google Scholar] [CrossRef]

- Uemoto, Y.; Hikita, M.; Ueno, H.; Matsuo, H.; Ishida, H.; Yanagihara, M.; Ueda, T.; Tanaka, T.; Ueda, D. Gate injection transistor (GIT) normally-off AlGaN/GaN power transistor using conductivity modulation. IEEE Trans. Electron. Devices 2007, 54, 3393–3399. [Google Scholar] [CrossRef]

- Meneghini, M.; de Santi, C.; Ueda, T.; Tanaka, T.; Ueda, D.; Zanoni, E.; Meneghesso, G. Time- and field-dependent trapping in GaN-based enhancement-mode transistors with p-gate. IEEE Electron. Device Lett. 2012, 33, 375–377. [Google Scholar] [CrossRef]

- Hilt, O.; Knauer, A.; Brunner, F.; Bahat-Treidel, E.; Wurfl, J. Normallyoff AlGaN/GaN HFET with p-type GaN gate and AlGaN buffer. In Proceedings of the ISPSD, Hiroshima, Japan, 6–10 June 2010; pp. 347–350. [Google Scholar]

- Fleury, C. High temperature performances of normally-off p-GaN gate AlGaN/GaN HEMTs on SiC and Si substrates for power applications. Microelectron. Reliab. 2015, 55, 1687–1691. [Google Scholar] [CrossRef]

- Wang, C. E-Mode p-n Junction/AlGaN/GaN (PNJ) HEMTs. IEEE Electron. Device Lett. 2020, 41, 545–548. [Google Scholar] [CrossRef]

- Hwang, I.; Kim, J.; Chong, S.; Choi, H.S.; Hwang, S.K.; Oh, J.; Shin, J.K.; Chung, U.I. Impact of channel hot electrons on current collapse in AlGaN/GaN HEMTs. IEEE Electron. Device Lett. 2013, 34, 1494–1496. [Google Scholar] [CrossRef]

| Reference Price | Resistivity (Ω·cm) | |

|---|---|---|

| LRSiC (6 inch) | USD1000 | 0.015~0.025 |

| HRSiC (6 inch) | USD3000 | >1E5 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Huang, Y.-C.; Chiu, H.-C.; Kao, H.-L.; Wang, H.-C.; Liu, C.-H.; Huang, C.-R.; Chen, S.-W. High Thermal Dissipation of Normally off p-GaN Gate AlGaN/GaN HEMTs on 6-Inch N-Doped Low-Resistivity SiC Substrate. Micromachines 2021, 12, 509. https://doi.org/10.3390/mi12050509

Huang Y-C, Chiu H-C, Kao H-L, Wang H-C, Liu C-H, Huang C-R, Chen S-W. High Thermal Dissipation of Normally off p-GaN Gate AlGaN/GaN HEMTs on 6-Inch N-Doped Low-Resistivity SiC Substrate. Micromachines. 2021; 12(5):509. https://doi.org/10.3390/mi12050509

Chicago/Turabian StyleHuang, Yu-Chun, Hsien-Chin Chiu, Hsuan-Ling Kao, Hsiang-Chun Wang, Chia-Hao Liu, Chong-Rong Huang, and Si-Wen Chen. 2021. "High Thermal Dissipation of Normally off p-GaN Gate AlGaN/GaN HEMTs on 6-Inch N-Doped Low-Resistivity SiC Substrate" Micromachines 12, no. 5: 509. https://doi.org/10.3390/mi12050509

APA StyleHuang, Y.-C., Chiu, H.-C., Kao, H.-L., Wang, H.-C., Liu, C.-H., Huang, C.-R., & Chen, S.-W. (2021). High Thermal Dissipation of Normally off p-GaN Gate AlGaN/GaN HEMTs on 6-Inch N-Doped Low-Resistivity SiC Substrate. Micromachines, 12(5), 509. https://doi.org/10.3390/mi12050509