Investigation of Recessed Gate AlGaN/GaN MIS-HEMTs with Double AlGaN Barrier Designs toward an Enhancement-Mode Characteristic

Abstract

1. Introduction

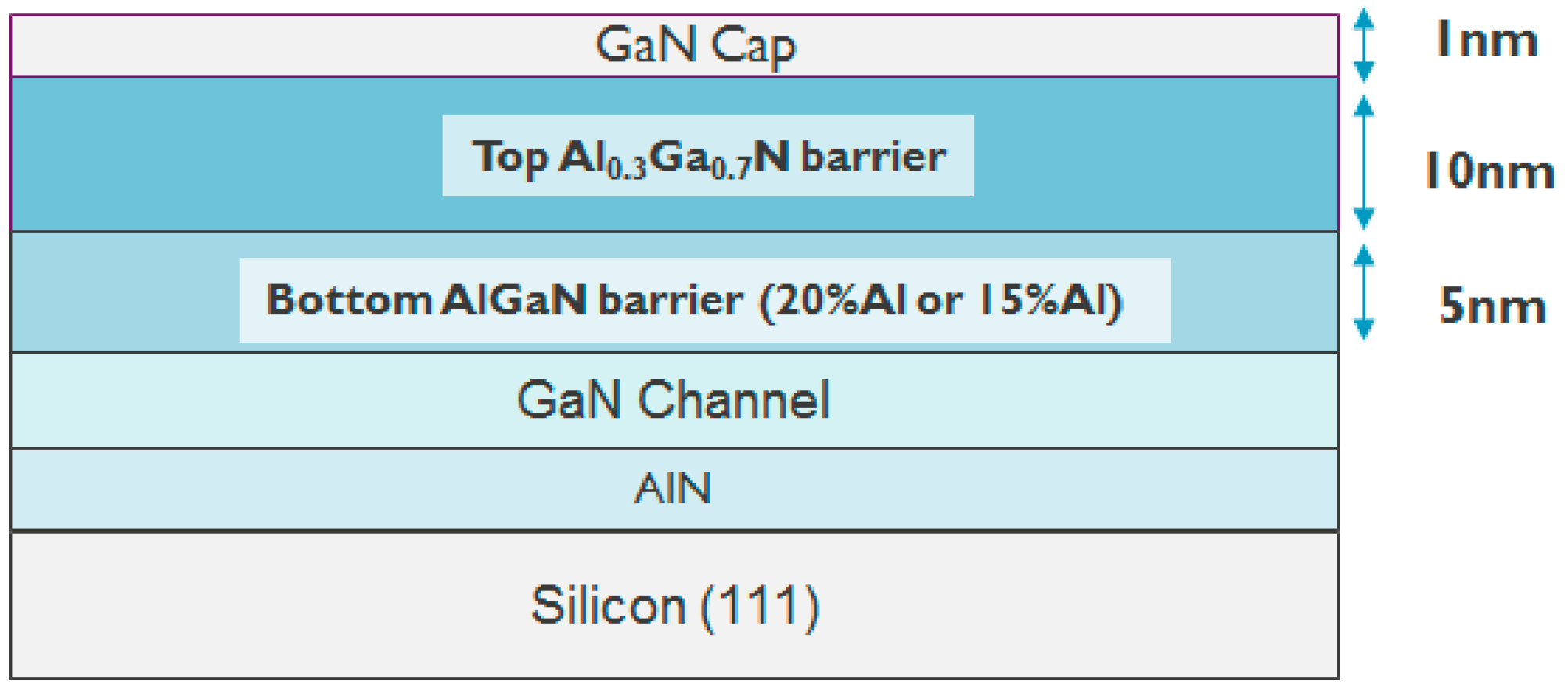

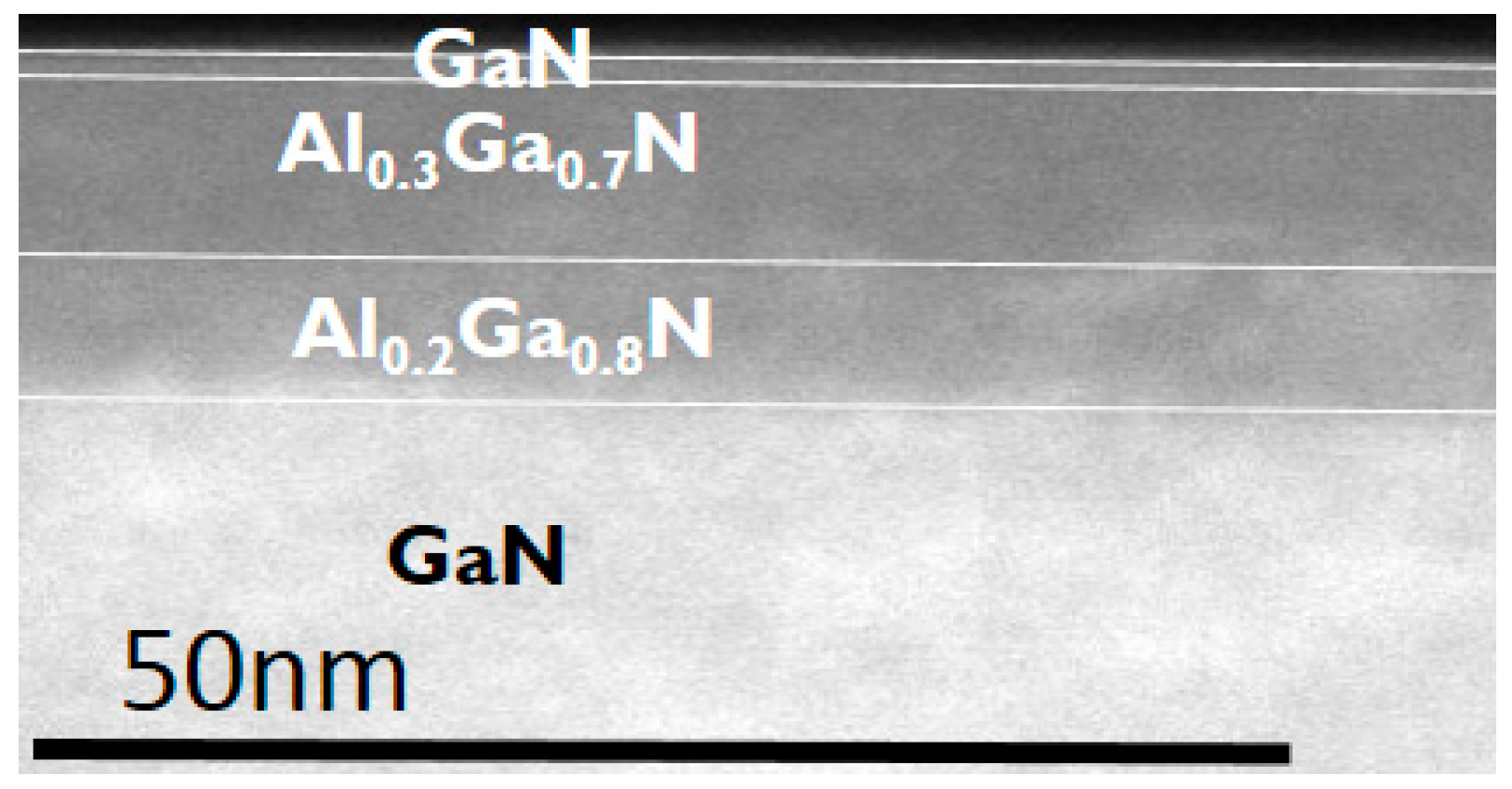

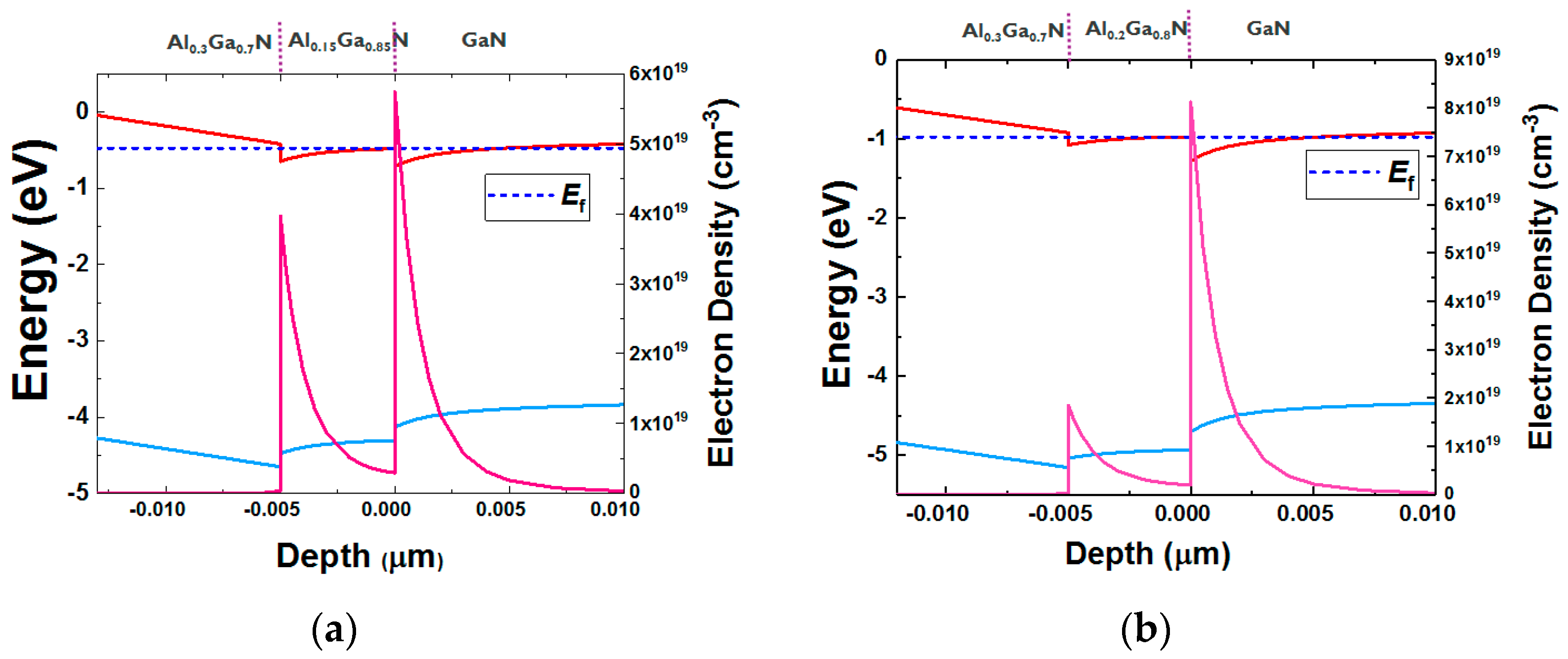

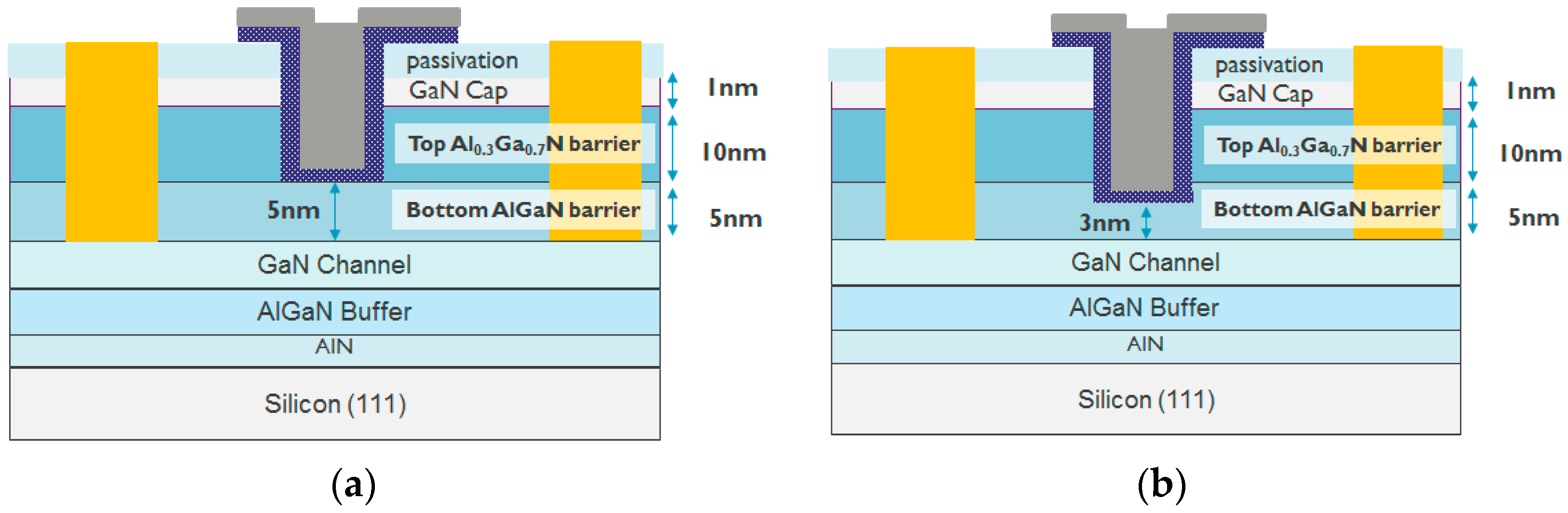

2. Device Fabrications

3. Results

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Amano, H.; Baines, Y.; Beam, E.; Borga, M.; Bouchet, T.; Chalker, P.R.; Charles, M.; Chen, K.J.; Chowdhury, N.; Chu, R.; et al. The 2018 GaN power electronics roadmap. J. Phys. D Appl. Phys. 2018, 51, 1–48. [Google Scholar] [CrossRef]

- Chen, K.J.; Häberlen, O.; Lidow, A.; Tsai, C.L.; Ueda, T.; Uemoto, Y.; Wu, Y. GaN-on-Si power technology: Devices and applications. IEEE Trans. Electron Devices 2017, 64, 779–795. [Google Scholar] [CrossRef]

- Van Hove, M.; Boulay, S.; Bahl, S.R.; Stoffels, S.; Kang, X.; Wellekens, D.; Geens, K.; Delabie, A.; Decoutere, S. CMOS Process-Compatible High-Power Low-Leakage AlGaN/GaN MISHEMT on Silicon. IEEE Electron Device Lett. 2012, 33, 667–669. [Google Scholar] [CrossRef]

- Moens, P.; Liu, C.; Banerjee, A.; Vanmeerbeek, P.; Coppens, P.; Ziad, H.; Constant, A.; Li, Z.; de Vleeschouwer, H.; RoigGuitart, J.; et al. An Industrial Process for 650 V Rated GaN-on-Si Power Devices Using in-Situ SiN as a Gate Dielectric. In Proceedings of the International Symposium on Power Semiconductor Devices and ICs (ISPSD), Waikoloa, HI, USA, 15–19 June 2014; pp. 374–377. [Google Scholar] [CrossRef]

- Hua, M.; Zhang, Z.; Wei, J.; Lei, J.; Tang, G.; Fu, K.; Cai, Y.; Zhang, B.; Chen, K.J. Integration of LPCVD-SiNx Gate Dielectric with Recessed-Gate E-Mode GaN MIS-FETs: Toward High Performance, High Stability and Long TDDB Lifetime. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 10.4.1–10.4.4. [Google Scholar] [CrossRef]

- Wu, T.-L.; Marcon, D.; de Jaeger, B.; van Hove, M.; Bakeroot, B.; Lin, D.; Stoffels, S.; Kang, X.; Roelofs, R.; Groeseneken, G.; et al. The Impact of the Gate Dielectric Quality in Developing Au-Free D-Mode and E-Mode Recessed Gate AlGaN/GaN Transistors on a 200 mm Si Substrate. In Proceedings of the International Symposium on Power Smicond Devices and ICs (ISPSD), Hong Kong, China, 10–14 May 2015; pp. 225–228. [Google Scholar] [CrossRef]

- De Jaeger, B.; van Hove, M.; Wellekens, D.; Kang, X.; Liang, H.; Mannaert, G.; Geens, K.; Decoutere, S. Au-Free CMOS-Compatible AlGaN/GaN HEMT Processing on 200 mm Si Substrates. In Proceedings of the 2012 24th International Symposium on Power Semiconductor Devices and ICs, Bruges, Belgium, 3–7 June 2012; pp. 49–52. [Google Scholar] [CrossRef]

- Wu, T.-L.; Marcon, D.; You, S.; Posthuma, N.; Bakeroot, B.; Stoffels, S.; van Hove, M.; Groeseneken, G.; Decoutere, S. Forward bias gate breakdown mechanism in enhancement-mode p-GaN gate AlGaN/GaN high-electron mobility transistors. IEEE Electron Device Lett. 2015, 36, 1001–1003. [Google Scholar] [CrossRef]

- Cai, Y.; Zhou, Y.; Chen, K.J.; Lau, K.M. High-performance enhancement-mode AlGaN/GaN HEMTs using fluoride-based plasma treatment. IEEE Electron Device Lett. 2005, 26, 435–437. [Google Scholar] [CrossRef]

- Huang, W.; Khan, T.; Chow, T.P. Enhancement-mode n-channel GaN MOSFETs on p and n-GaN/sapphire substrates. IEEE Electron Device Lett. 2006, 27, 796–798. [Google Scholar] [CrossRef]

- Lu, B.; Saadat, O.I.; Palacios, T. High-performance integrated dual-gate AlGaN/GaN enhancement-mode transistor. IEEE Electron Device Lett. 2010, 31, 990–992. [Google Scholar] [CrossRef]

- Wang, R.; Wu, Y.; Chen, K.J. Gain improvement of enhancement-mode AlGaN/GaN high-electron-mobility transistors using dual-gate architecture. Jpn. J. Appl. Phys. 2013, 47, 2820. [Google Scholar] [CrossRef]

- Sheng, N.H.; Lee, C.P.; Chen, R.T.; Miller, D.L.; Lee, S.J. Multiple-Channel GaAs/AlGaAs High Electron Mobility Transistors. IEEE Electron Device Lett. 1985, 6, 307–310. [Google Scholar] [CrossRef]

- Gaska, R.; Shur, M.S.; Fjeldly, T.A.; Bykhovski, A.D. Two-channel AlGaN/GaN heterostructure field effect transistor for high power applications. J. Appl. Phys. 1999, 85, 3009–3011. [Google Scholar] [CrossRef]

- Chu, R.; Zhou, Y.; Liu, J.; Wang, D.; Chen, K.J.; Lau, K.M. AlGaN-GaN Double-Channel HEMTs. IEEE Trans. Electron Devices 2005, 52, 438–446. [Google Scholar] [CrossRef]

- Palacios, T.; Chini, A.; Buttari, D.; Heikman, S.; Chakraborty, A.; Keller, S.; DenBaars, S.P.; Mishra, U.K. Use of Double-Channel Heterostructures to Improve the Access Resistance and Linearity in GaN-Based HEMTs. IEEE Trans. Electron Devices 2006, 53, 562–565. [Google Scholar] [CrossRef]

- Kamath, A.; Patil, T.; Adari, R.; Bhattacharya, I.; Ganguly, S.; Aldhaheri, R.W.; Hussain, M.A.; Saha, D. Double-Channel AlGaN/GaN High Electron Mobility Transistor with Back Barriers. IEEE Electron Device Lett. 2012, 33. [Google Scholar] [CrossRef]

- Xue, J.; Zhang, J.; Zhang, K.; Zhao, Y.; Zhang, L.; Ma, X.; Li, X.; Meng, F.; Hao, Y. Fabrication and characterization of InAlN/GaN-based double-channel high electron mobility transistors for electronic applications. J. Appl. Phys. 2012, 111, 114513. [Google Scholar] [CrossRef]

- Wei, J.; Liu, S.; Li, B.; Tang, X.; Lu, Y.; Liu, C.; Hua, M.; Zhang, Z.; Tang, G.; Chen, K.J. Enhancement-Mode GaN Double-Channel MOS-HEMT with Low On-Resistance and Robust Gate Recess. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 9.4.1–9.4.4. [Google Scholar] [CrossRef]

- Mizue, C.; Hori, Y.; Miczek, M.; Hashizume, T. Capacitance-Voltage Characteristics of Al2O3/AlGaN/GaN Structures and State Density Distribution at Al2O3/AlGaN Interface. Jpn. J. Appl. Phys. 2011, 50, 021001. [Google Scholar] [CrossRef]

- Wu, T.-L.; Marcon, D.; Ronchi, N.; Bakeroot, B.; You, S.; Stoffels, S.; van Hove, M.; Bisi, D.; Meneghini, M.; Groeseneken, G.; et al. Analysis of Slow De-trapping Phenomena after a Positive Gate Bias on AlGaN/GaN MIS-HEMTs with in-situ Si3N4/Al2O3 Bilayer Gate Dielectrics. Solid-State Electron. 2015, 103, 127–130. [Google Scholar] [CrossRef]

- Lagger, P.; Steinschifter, P.; Reiner, M.; Denifl, G.; Naumann, A.; Wilde, L.; Sundqvist, J.; Pogany, D.; Ostermaier, C. Role of the dielectric for the charging dynamics of the dielectric/barrier interface in AlGaN/GaN based metal-insulator-semiconductor structures under forward gate bias stress. Appl. Phys. Lett. 2014, 105, 033512. [Google Scholar] [CrossRef]

- Lee, J.-H.; Kim, J.-G.; Ju, J.-M.; Ahn, W.-H.; Kang, S.-H.; Lee, J.-H. AlInGaN/GaN double-channel FinFET with high on-current and negligible current collapse. Solid-State Electron. 2020, 164, 107678. [Google Scholar] [CrossRef]

- Deen, D.A.; Miller, R.A.; Osinsky, A.V.; Downey, B.P.; Storm, D.F.; Meyer, D.J.; Katzer, D.S.; Nepal, N. Polarization-mediated Debye-screening of surface potential fluctuations in dual-channel AlN/GaN high electron mobility transistors. Appl. Phys. Lett. 2016, 120, 235704. [Google Scholar] [CrossRef]

| Parameters | Top AlGaN Barrier | Bottom AlGaN Barrier |

| Thickness | 10 nm | 5 nm |

| Al% | 30% | 20% |

| 15% | ||

| Recessed depth | ||

| Remaining bottom AlGaN barrier under the gate region | – | 5 nm |

| 3 nm | ||

| Reference | Barrier designs | Ion/Ioff | SS (mV/dec) | VTH (V) @0.1mA/mm | 1nd gm (mS/mm) | 2nd gm (mS/mm) |

|---|---|---|---|---|---|---|

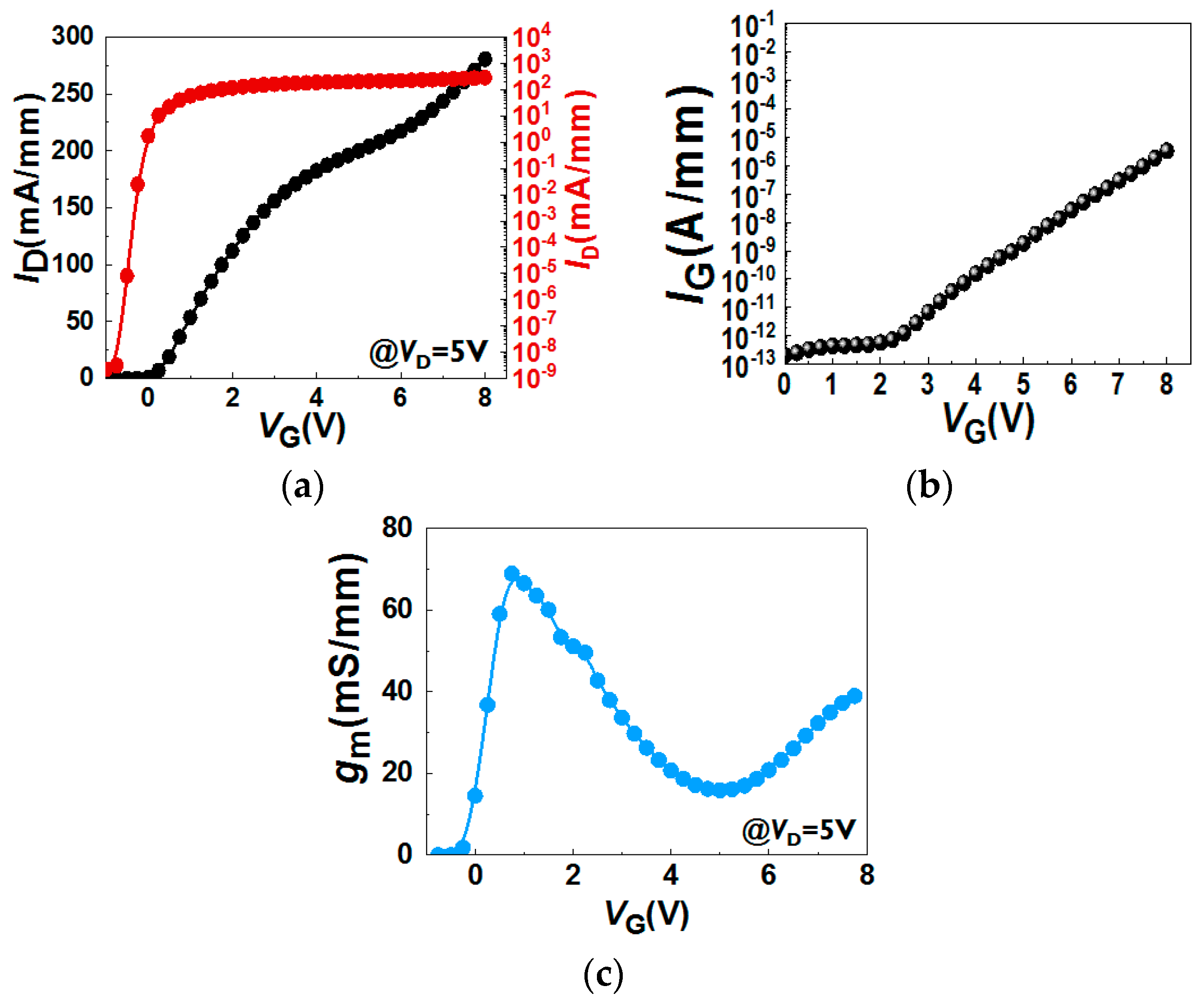

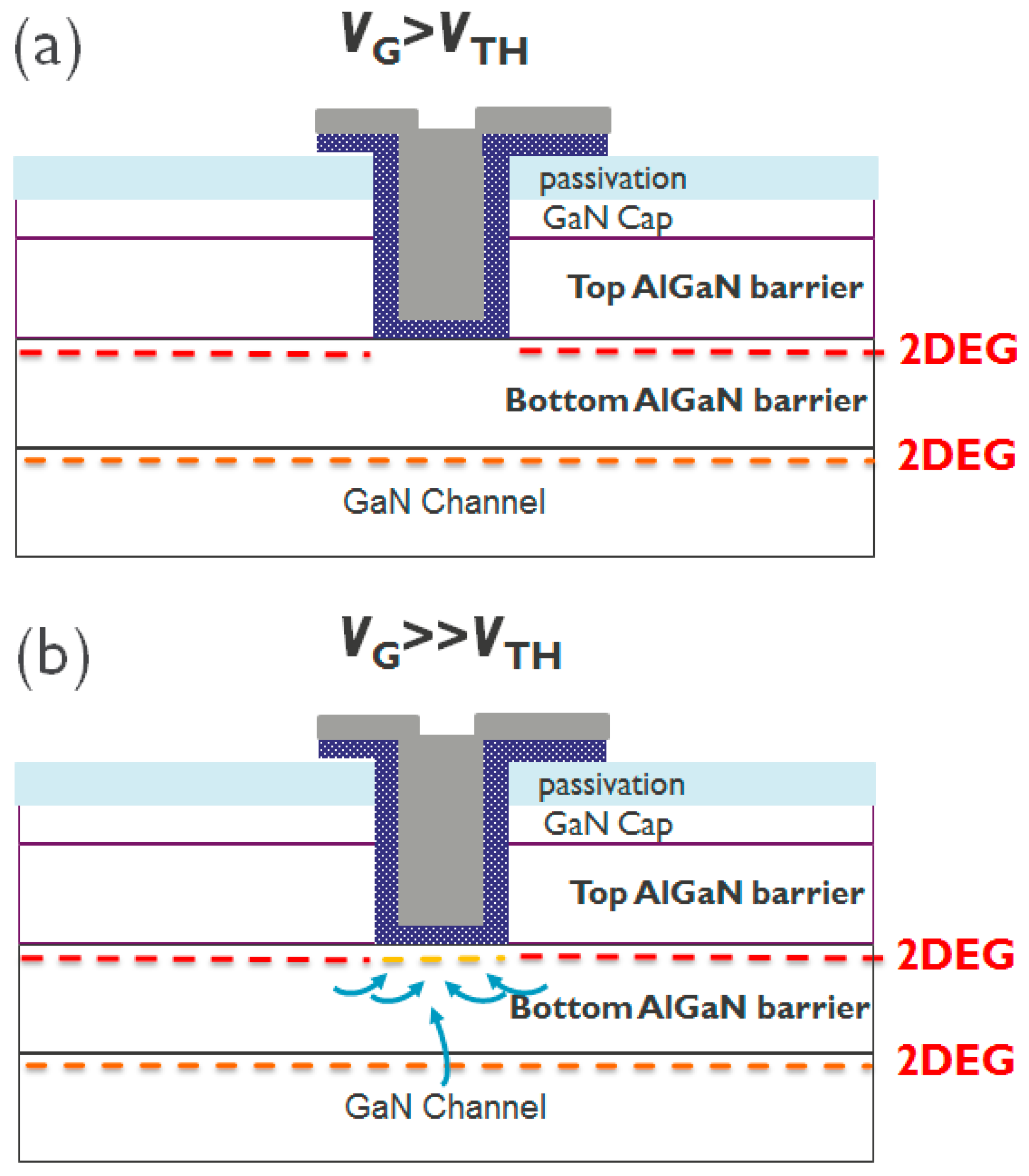

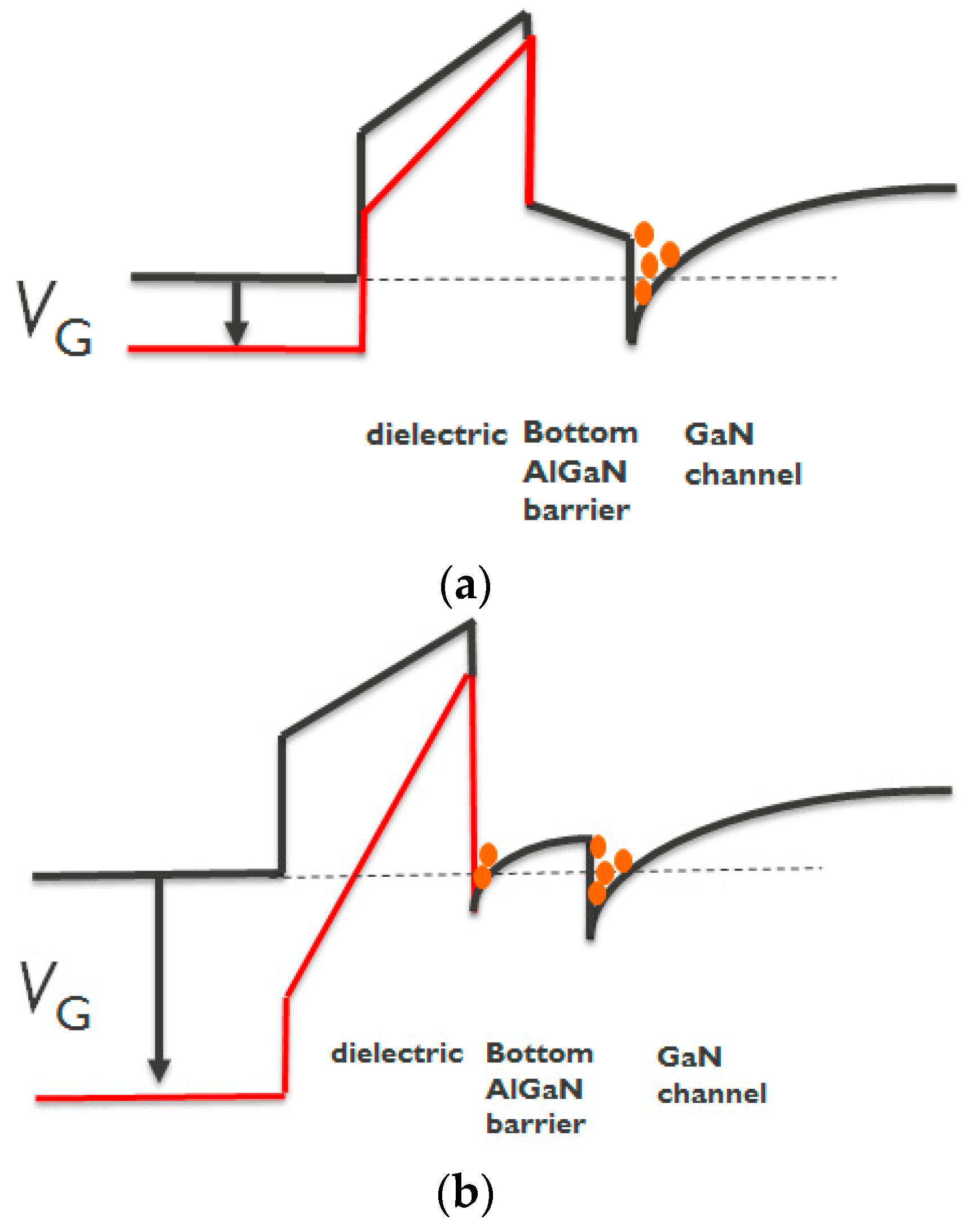

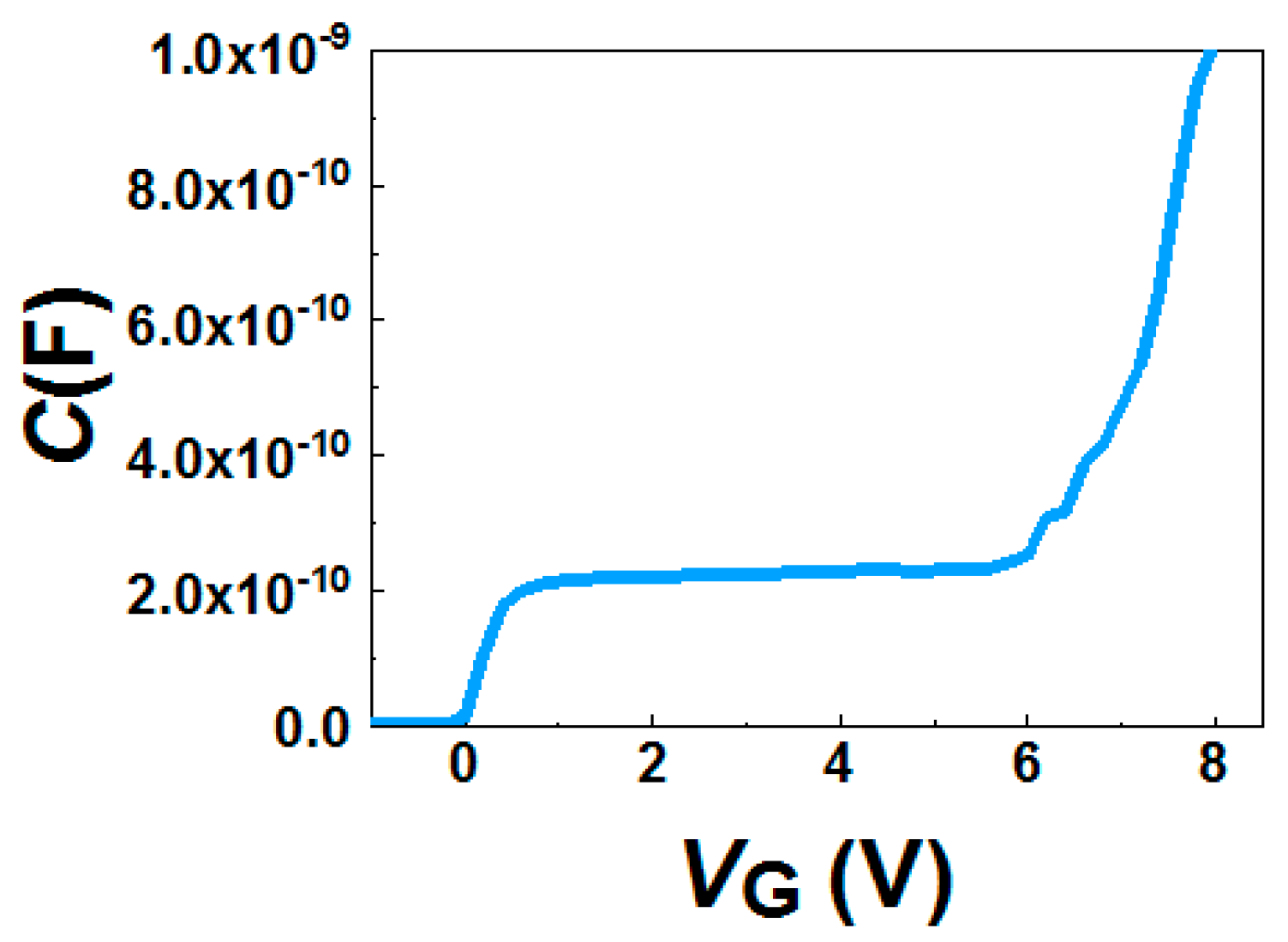

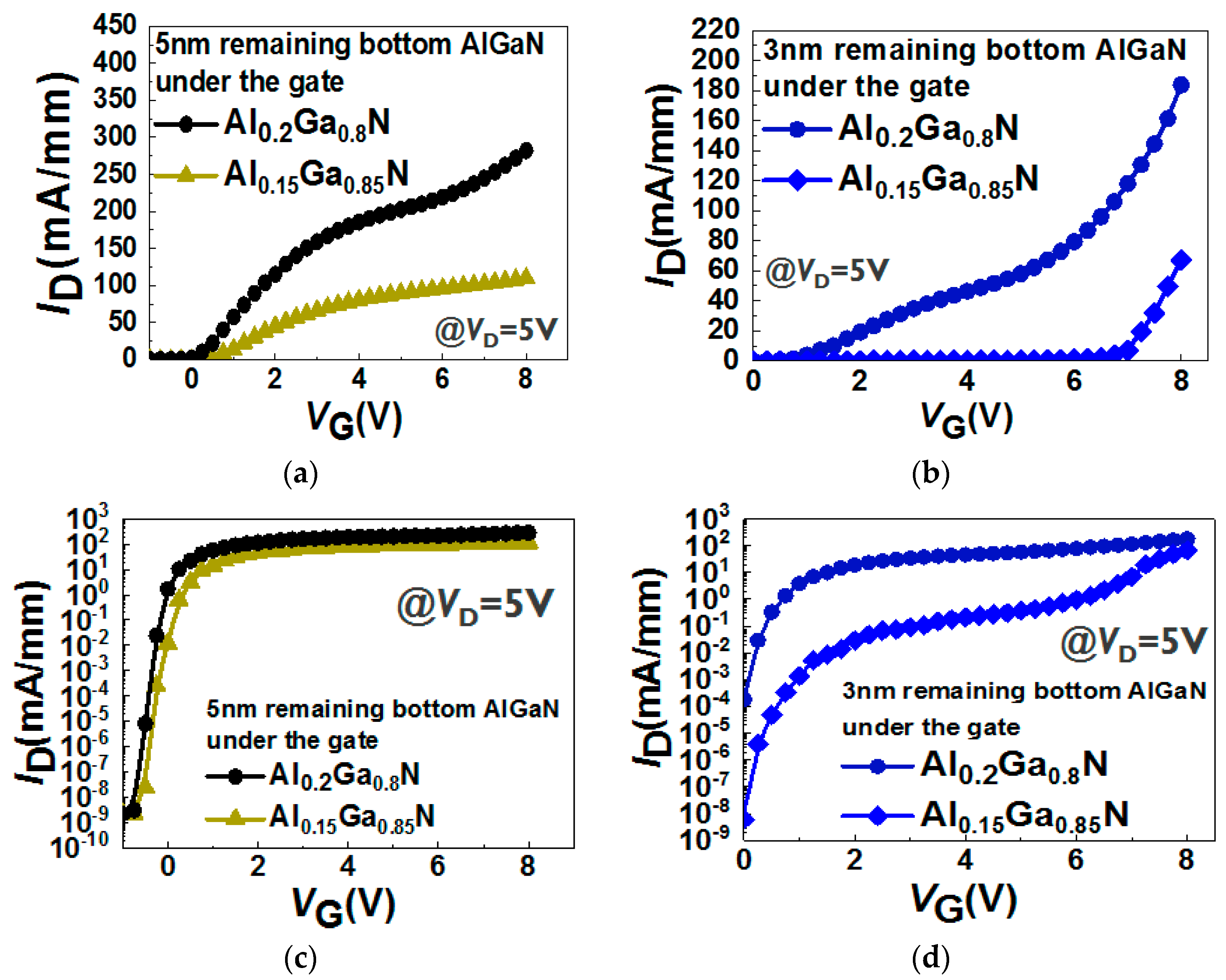

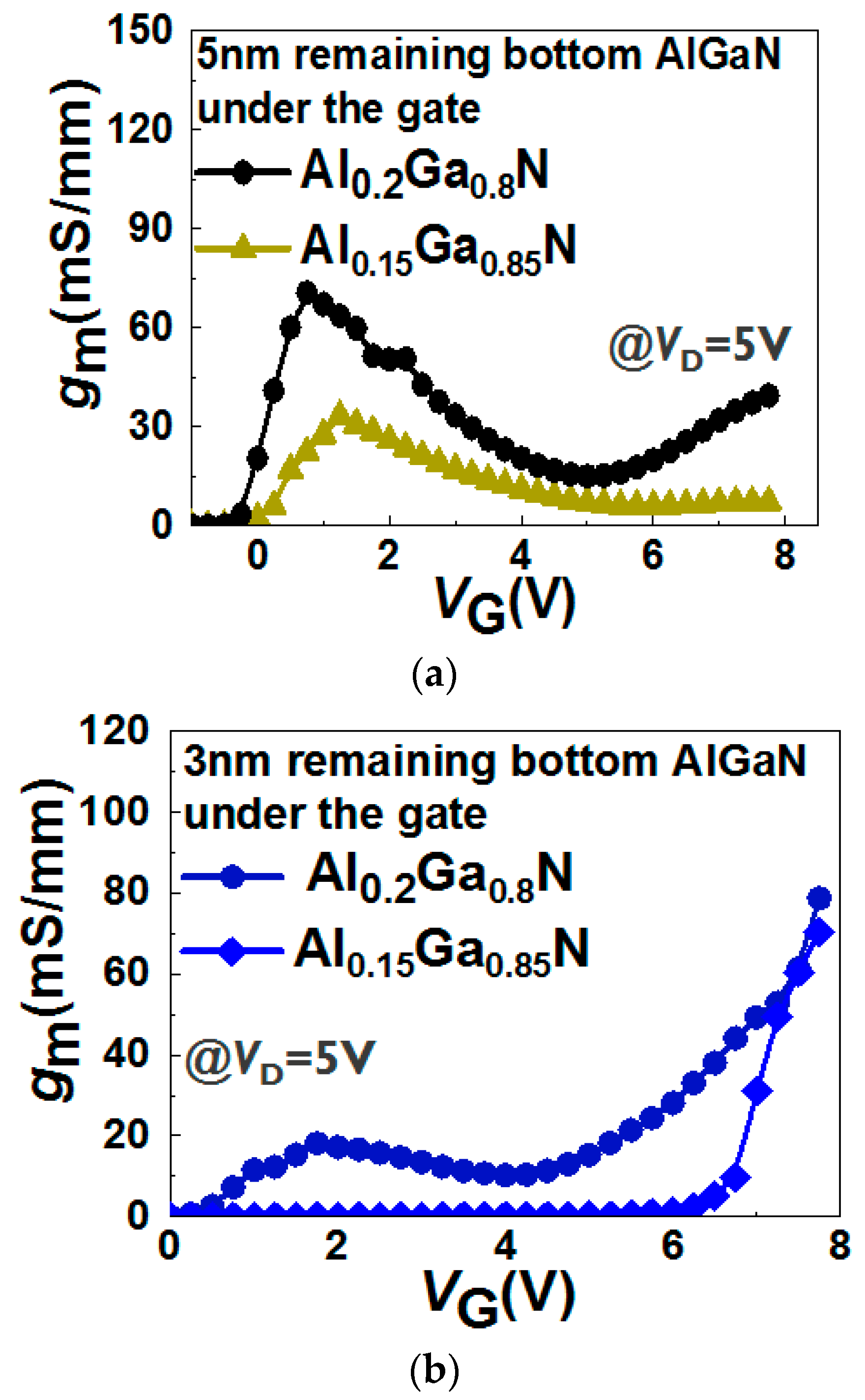

| Our work | Al0.3Ga0.7N/Al0.2Ga0.8N/GaN 5nm remaining bottom Al0.2Ga0.8N | 1.2 × 1011 | 80.7 | ~0 | 68.9 | 39 |

| Al0.3Ga0.7N/Al0.15Ga0.85N/GaN 5nm remaining bottom Al0.15Ga0.85N | 4.8 × 1010 | 87.9 | 0.25 | 34.8 | 7.6 | |

| Al0.3Ga0.7N/ Al0.2Ga0.8N /GaN 3nm remaining bottom Al0.2Ga0.8N | - | 153.1 | 0.5 | 18.8 | 90 | |

| Al0.3Ga0.7N/ Al0.15Ga0.85N /GaN 3nm remaining bottom Al0.15Ga0.85N | 5.5 × 1010 | 229.3 | 3.25 | - | 71.2 | |

| Kamath et al. [17] | Al0.3Ga0.7N/GaN/Al0.15Ga0.75N/GaN | - | - | ~−7.8 | 34 | 89 |

| Wei et al. [19] | AlGaN/AlN/GaN/AlN with 1.5 nm over-etch upper GaN layer | ~109 | 72 | 0.5 | 170 | 103 |

| Lee et al. [23] | AlGaN/GaN/AlGaN/GaN Fin Structure | - | - | 0.2 | 133 | - |

| Deen et al. [24] | AlN/GaN/AlN/GaN | - | - | ~−4 | 190 | - |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wu, T.-L.; Tang, S.-W.; Jiang, H.-J. Investigation of Recessed Gate AlGaN/GaN MIS-HEMTs with Double AlGaN Barrier Designs toward an Enhancement-Mode Characteristic. Micromachines 2020, 11, 163. https://doi.org/10.3390/mi11020163

Wu T-L, Tang S-W, Jiang H-J. Investigation of Recessed Gate AlGaN/GaN MIS-HEMTs with Double AlGaN Barrier Designs toward an Enhancement-Mode Characteristic. Micromachines. 2020; 11(2):163. https://doi.org/10.3390/mi11020163

Chicago/Turabian StyleWu, Tian-Li, Shun-Wei Tang, and Hong-Jia Jiang. 2020. "Investigation of Recessed Gate AlGaN/GaN MIS-HEMTs with Double AlGaN Barrier Designs toward an Enhancement-Mode Characteristic" Micromachines 11, no. 2: 163. https://doi.org/10.3390/mi11020163

APA StyleWu, T.-L., Tang, S.-W., & Jiang, H.-J. (2020). Investigation of Recessed Gate AlGaN/GaN MIS-HEMTs with Double AlGaN Barrier Designs toward an Enhancement-Mode Characteristic. Micromachines, 11(2), 163. https://doi.org/10.3390/mi11020163