An Improved Modulation Method for Suppressing High Frequency Common-Mode Voltage in SiC Motor Drive System

Abstract

:1. Introduction

2. Influence of Voltage Vectors on the Switching Performance of SiC devices

2.1. Definition of Common-Mode Voltage

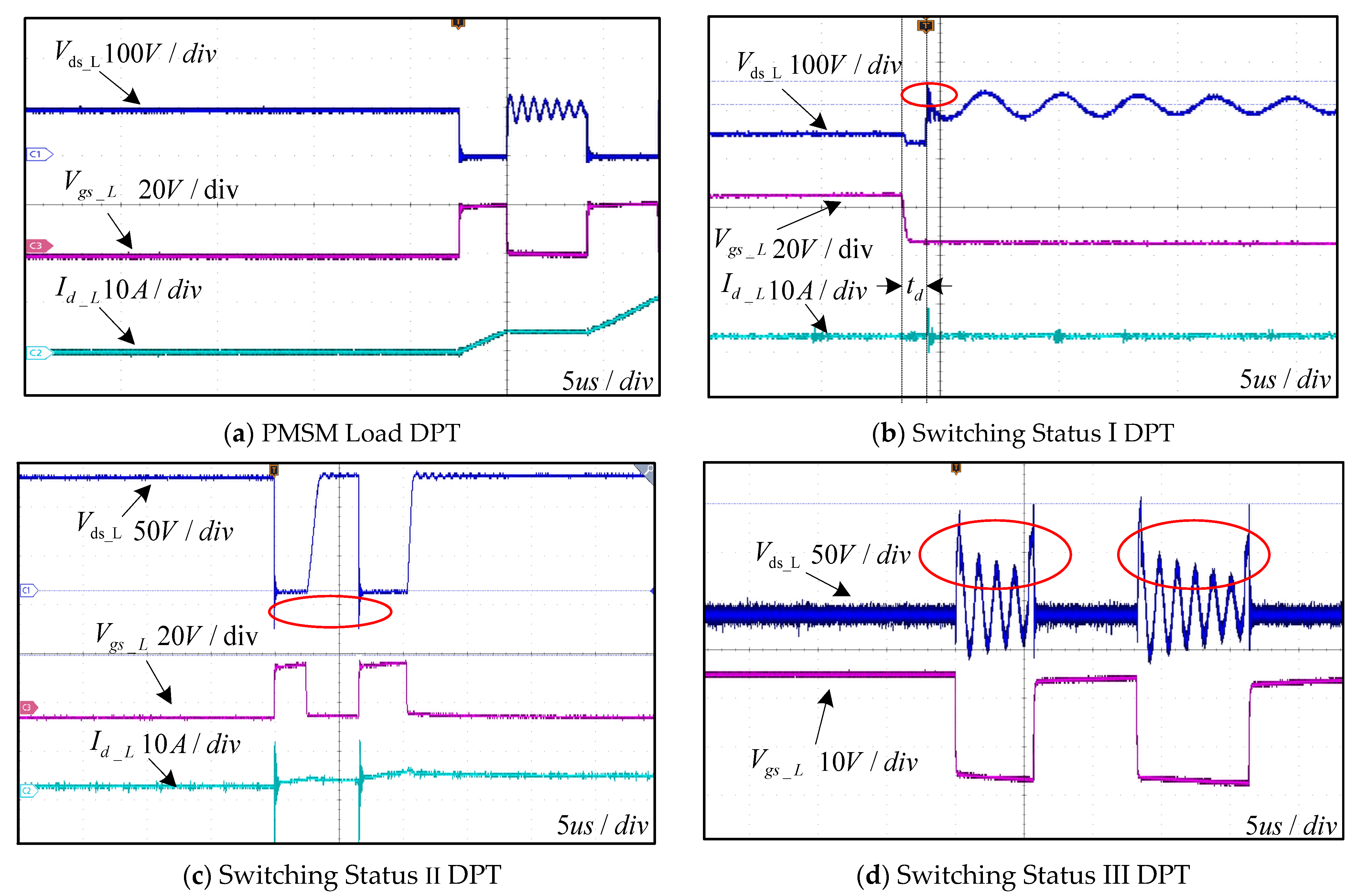

2.2. Double Pulse Test of SiC Three-Phase Full Bridge

3. High-Frequency Common-Mode Voltage Suppression Strategy

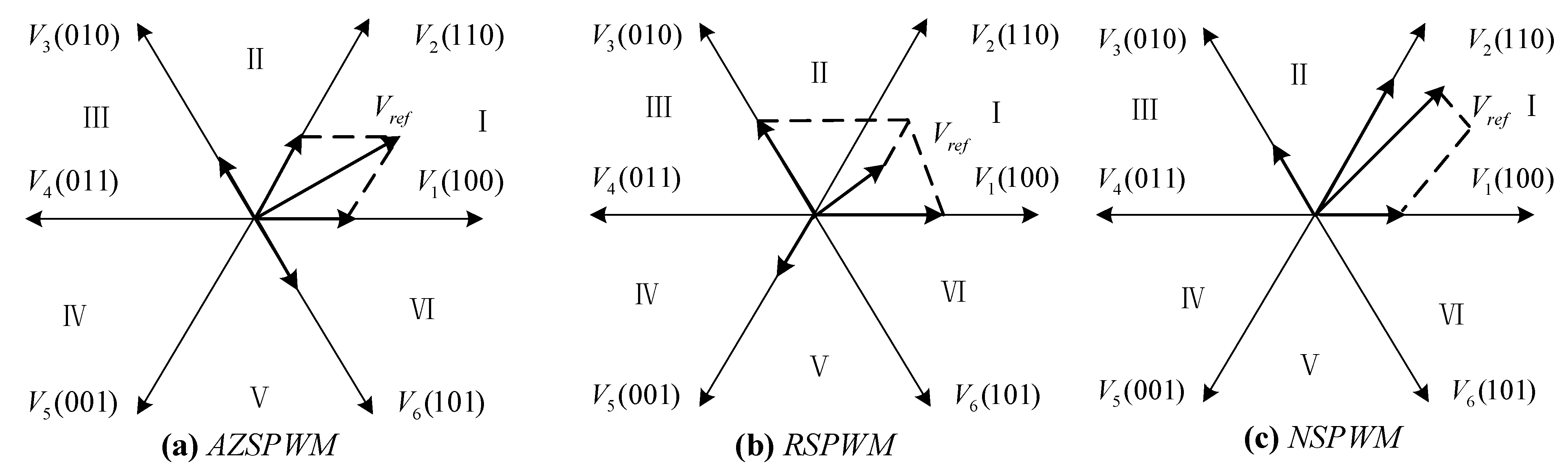

3.1. Reduced Common-Mode Voltage PWM

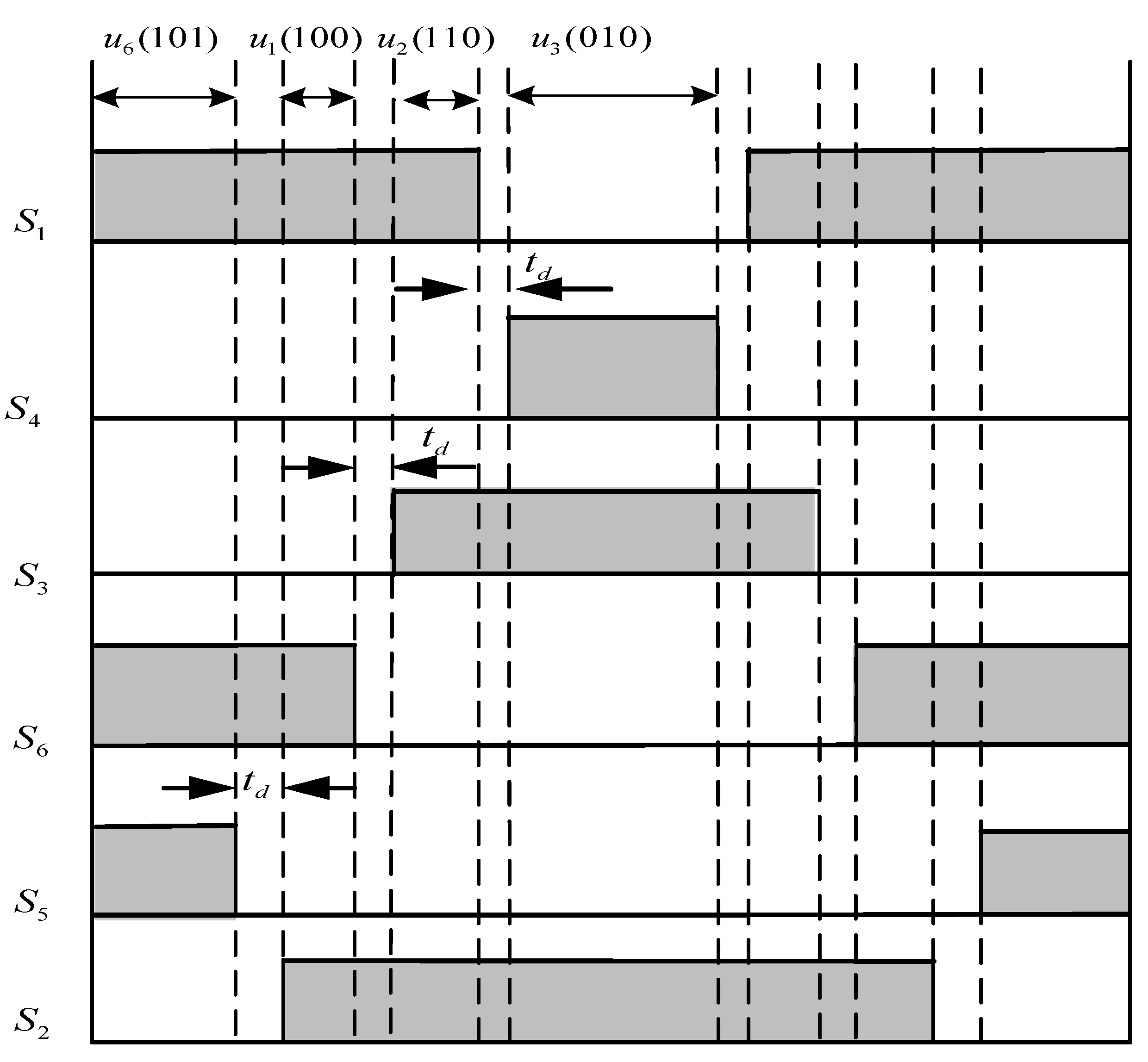

3.2. Dead-Zone Effect under High Switching Frequency

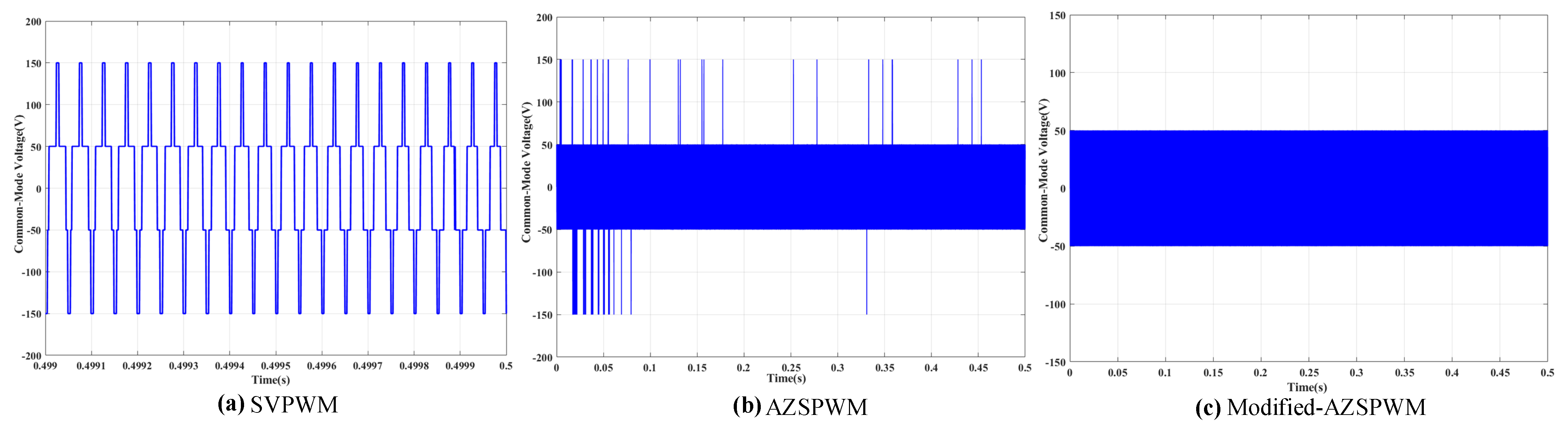

3.3. Modified Active Zero State PWM

4. Simulation and Experimental Verification

5. Conclusions

- The root of high-frequency common-mode voltage oscillation in SiC motor drive system is from the voltage oscillation during the conduction process of the SiC device. At the time of switching, the higher the amplitude of the common-mode voltage, the stronger the high-frequency voltage oscillation of the SiC device. In the zero vector (000, 111) state, the common-mode voltage amplitude is the highest, and the high-frequency voltage oscillation generated by the device is the most serious.

- Traditional AZSPWM method for suppressing common-mode voltage causes the problem of simultaneous operation of two-phase switches. At high switching frequencies, the dead zone effect causes common-mode suppression to fail, resulting in common-mode voltage spikes with an amplitude of ±. The improved AZSPWM adds a set of complementary device turn-on logic to ensure that only one switch acts at the same time, avoiding common-mode voltage spikes caused by sector switching. In view of the influence of the dead zone effect of different switches, different dead zone compensation methods are selected to limit the common-mode voltage amplitude to ±.

- Without increasing hardware cost and sacrificing SiC switching speed, the improved AZSPWM proposed in this paper can solve common-mode voltage suppression failure caused by the dead-zone effect at a high switching frequency and suppress high-frequency voltage oscillation and the overvoltage phenomenon. This can effectively suppress high-frequency common-mode voltage, thereby alleviating the negative effects of high-frequency common-mode voltage in SiC motor drive systems.

Author Contributions

Funding

Conflicts of Interest

References

- Hamada, K.; Nagao, M.; Ajioka, M.; Kawai, F. SiC—Emerging Power Device Technology for Next-Generation Electrically Powered Environmentally Friendly Vehicles. IEEE Trans. Electron. Devices 2015, 62, 278–285. [Google Scholar] [CrossRef]

- Hazra, S.; De, A.; Cheng, L.; Palmour, J.; Schupbach, M.; Hull, B.A.; Allen, S.; Bhattacharya, S. High Switching Performance of 1700-V, 50-A SiC Power MOSFET Over Si IGBT/MOSFET for Advanced Power Conversion Applications. IEEE Trans. Power Electron. 2016, 31, 4742–4754. [Google Scholar]

- Willwerth, A.; Roman, M. Electrical bearing damage—A lurking problem in inverter-driven traction motors. In Proceedings of the 2013 IEEE Transportation Electrification Conference and Expo (ITEC), Metro Detroit, MI, USA, 16–19 June 2013; pp. 1–4. [Google Scholar]

- Han, D.; Morris, C.T.; Lee, W.; Sarlioglu, B. Comparison Between Output CM Chokes for SiC Drive Operating at 20- and 200-kHz Switching Frequencies. IEEE Trans. Ind. Appl. 2017, 53, 2178–2188. [Google Scholar] [CrossRef]

- Hedayati, M.H.; Acharya, A.B.; John, V. Common-Mode Filter Design for PWM Rectifier-Based Motor Drives. IEEE Trans. Power Electron. 2013, 28, 5364–5371. [Google Scholar] [CrossRef]

- Gao, Q.; Xu, D. Design of common-mode and differential-mode voltage dv/dt filter at PWM inverter output ter-minals. Trans. China Electrotech. Soc. 2007, 22, 79–84. [Google Scholar]

- Jiang, Y.; Chen, X.; Xu, D.; Ma, H. A novel feed-forward-type active filter to eliminate shaft voltage and bearing current at motor terminal in a PWM inverter drives. Proc. CSEE 2003, 49, 25–28. [Google Scholar]

- Zhou, J.; Wu, X.; Jiang, Z. A novel 3D-SVPWM algorithm for four-leg converter. Proc. CSEE 2011, 31, 1–8. [Google Scholar]

- Hava, A.M.; Ün, E. A High-Performance PWM Algorithm for Common-Mode Voltage Reduction in Three-Phase Volt-age Source Inverters. IEEE Trans. Power Electron. 2011, 26, 1998–2008. [Google Scholar] [CrossRef]

- Zhou, J.; Wei, C.; Yang, Y. Simplified PWM algorithm and common mode voltage suppression strategy for three phase inverter. Trans. China Electrotech. Soc. 2014, 29, 158–165. [Google Scholar]

- Han, Y.; Lu, H.; Li, Y.; Chai, J. Analysis and Suppression of Shaft Voltage in SiC-Based Inverter for Electric Vehicle Applications. IEEE Trans. Power Electron. 2019, 34, 6276–6285. [Google Scholar] [CrossRef]

- Lai, Y.-S.; Bowes, S. A new suboptimal pulse-width modulation technique for per-phase modulation and space vector modulation. IEEE Trans. Energy Convers. 1997, 12, 310–316. [Google Scholar] [CrossRef]

- Lai, Y.-S.; Shyu, F.-S. Optimal common-mode Voltage reduction PWM technique for inverter control with con-sideration of the dead-time effects-part I: Basic development. IEEE Trans. Ind. Appl. 2004, 40, 1605–1612. [Google Scholar] [CrossRef]

- Lu, H.; Qu, W.; Cheng, X.; Fan, Y.; Zhang, X. A Novel PWM Technique With Two-Phase Modulation. IEEE Trans. Power Electron. 2007, 22, 2403–2409. [Google Scholar] [CrossRef]

- Un, E.; Hava, A.M. A Near-State PWM Method With Reduced Switching Losses and Reduced Common-Mode Voltage for Three-Phase Voltage Source Inverters. IEEE Trans. Ind. Appl. 2009, 45, 782–793. [Google Scholar] [CrossRef]

- Hava, A.M.; Ün, E. Performance Analysis of Reduced Common-Mode Voltage PWM Methods and Comparison with Standard PWM Methods for Three-Phase Voltage-Source Inverters. IEEE Trans. Power Electron. 2009, 24, 241–252. [Google Scholar] [CrossRef]

| Vectors | ||||

|---|---|---|---|---|

| 000 | ||||

| 100 | ||||

| 110 | ||||

| 010 | ||||

| 011 | ||||

| 001 | ||||

| 101 | ||||

| 111 |

| Sector | Logic | Condition | Compensation | |||

|---|---|---|---|---|---|---|

| I | Type I | I | − | + | − | |

| Type I | II | + | − | + | ||

| II | Type II | I | + | − | − | |

| Type II | II | − | + | + | ||

| III | Type I | I | − | − | + | |

| Type I | II | + | + | − | ||

| IV | Type II | I | − | + | − | |

| Type II | II | + | − | + | ||

| V | Type I | I | + | − | − | |

| Type I | II | − | + | + | ||

| VI | Type II | I | − | − | + | |

| Type II | II | + | + | − |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, H.; Zhang, A.; Xiang, X. An Improved Modulation Method for Suppressing High Frequency Common-Mode Voltage in SiC Motor Drive System. World Electr. Veh. J. 2021, 12, 111. https://doi.org/10.3390/wevj12030111

Li H, Zhang A, Xiang X. An Improved Modulation Method for Suppressing High Frequency Common-Mode Voltage in SiC Motor Drive System. World Electric Vehicle Journal. 2021; 12(3):111. https://doi.org/10.3390/wevj12030111

Chicago/Turabian StyleLi, Hui, Aibo Zhang, and Xuewei Xiang. 2021. "An Improved Modulation Method for Suppressing High Frequency Common-Mode Voltage in SiC Motor Drive System" World Electric Vehicle Journal 12, no. 3: 111. https://doi.org/10.3390/wevj12030111

APA StyleLi, H., Zhang, A., & Xiang, X. (2021). An Improved Modulation Method for Suppressing High Frequency Common-Mode Voltage in SiC Motor Drive System. World Electric Vehicle Journal, 12(3), 111. https://doi.org/10.3390/wevj12030111