Adaptive Sliding-Mode Controller for a Zeta Converter to Provide High-Frequency Transients in Battery Applications

Abstract

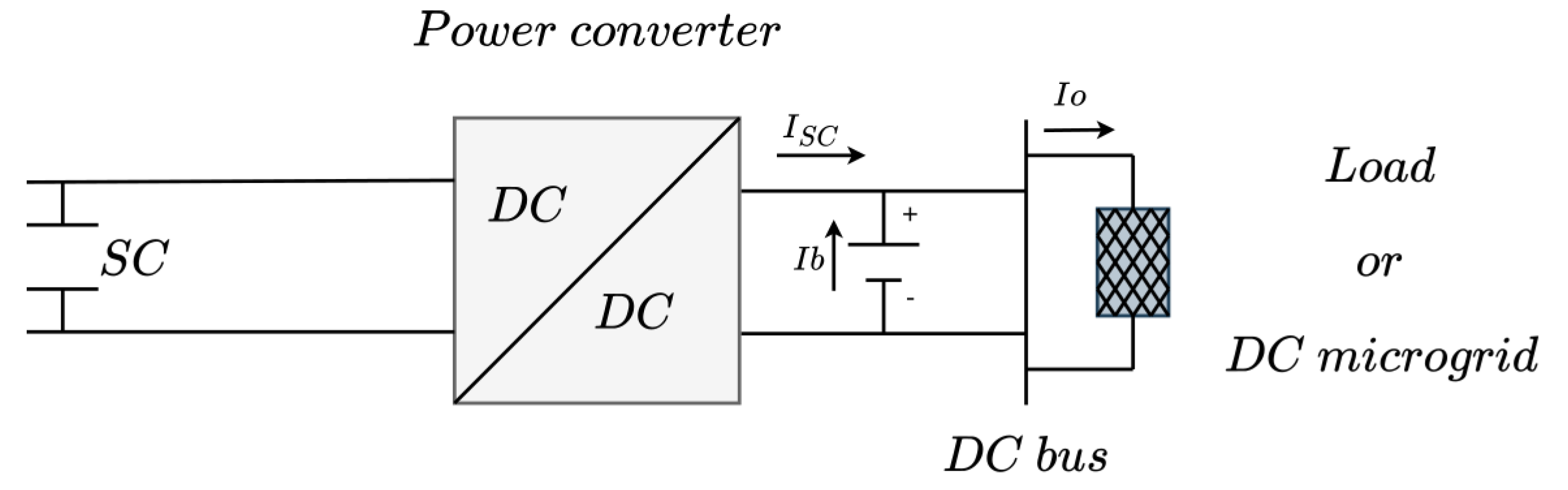

1. Introduction

- Stable DC/DC converter operation.

- Reduced harmonics in the battery current.

- Safe SC voltage regulation.

- Definition of the algorithms for designing the power stage and the adaptive SMC.

- Providing a battery current without high-frequency transients.

- Algorithms for implementing the adaptive SMC on low-cost microcontrollers with low computation burden.

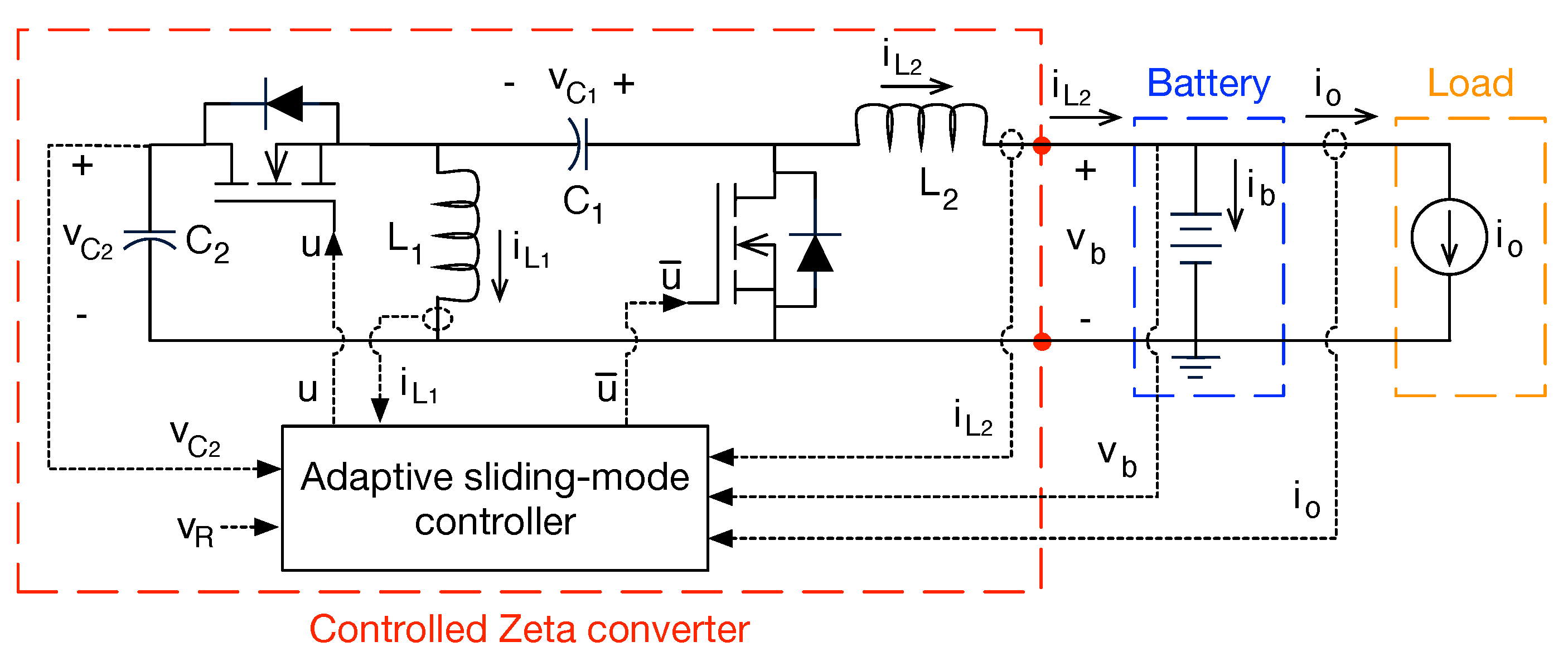

2. Power Circuit Modeling

3. Design and Analysis of the Sliding-Mode Controller

- Stable operation of the Zeta converter, which requires the stable relation between and currents given in Equation (20).

- Regulate the output current of the Zeta converter () to provide the high-frequency components of the load current (), and at the same time, regulate the voltage to avoid a deep discharge or a dangerous overcharge.

3.1. Transversality Analysis

3.2. Reachability Analysis

- Operating under the surface () requires a positive switching function derivative to reach the surface ().

- Operating above the surface () requires a negative switching function derivative to reach the surface ().

3.3. Equivalent Control

3.4. Closed-Loop Dynamics

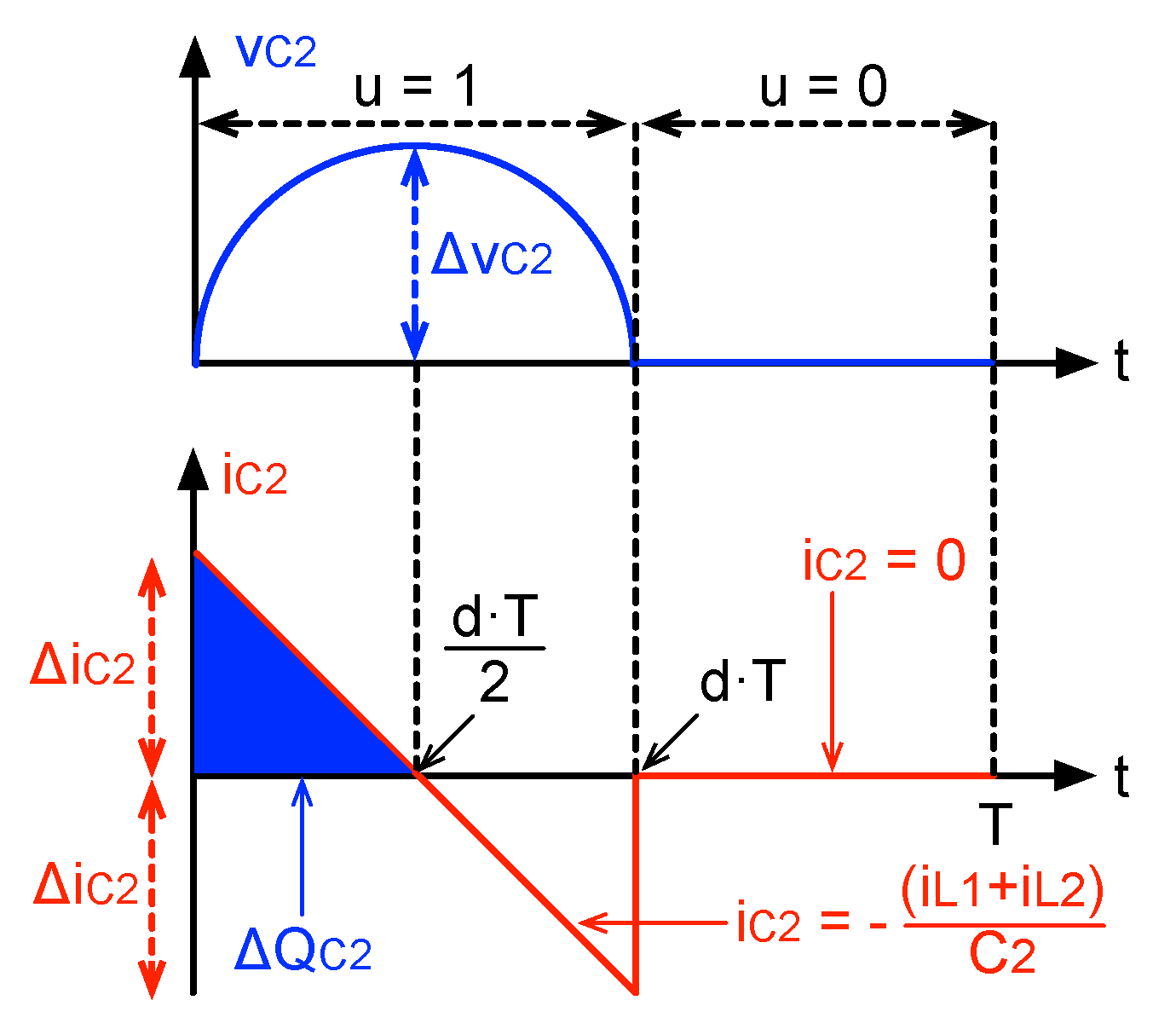

3.5. Switching Frequency

4. Design Procedure and Application Example

4.1. Inductor Design

4.2. Capacitors and High-Pass Filter Design

4.3. Verification of the SMC Stability

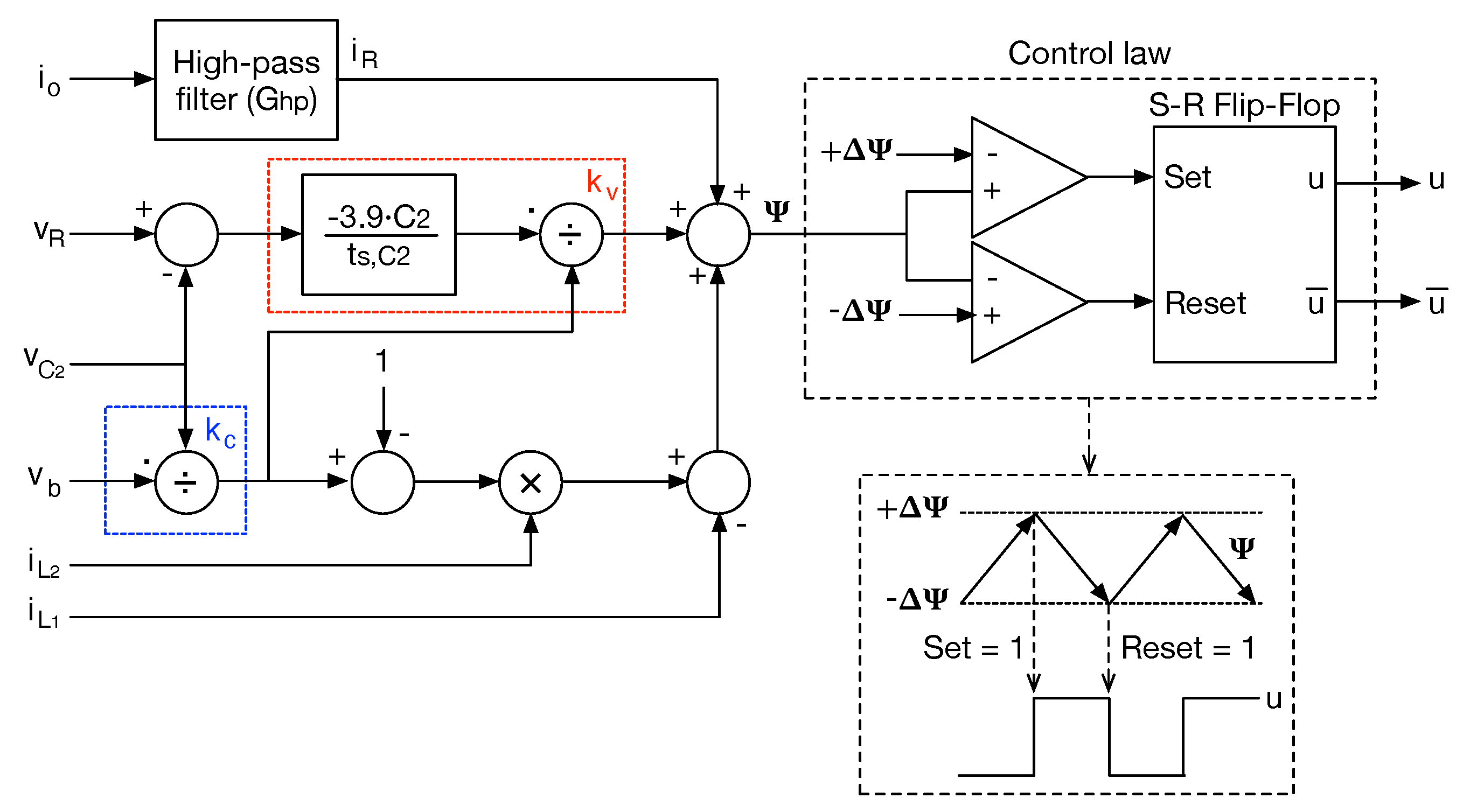

4.4. SMC Control Law

4.5. Summary of the Design and Control Processes

| Algorithm 1 Design of both the power stage and SMC parameters |

| Require: , , , , , , , |

|

| Algorithm 2 Control process | |

| Require: | |

| |

| ▹ Filter the load current to detect the fast transients |

| ▹ Calculate the adaptive current gain |

| ▹ Calculate the adaptive voltage gain |

| ▹ Calculate |

| ▹ Apply the control law |

| |

| ▹u and are provided to the MOSFETs |

| |

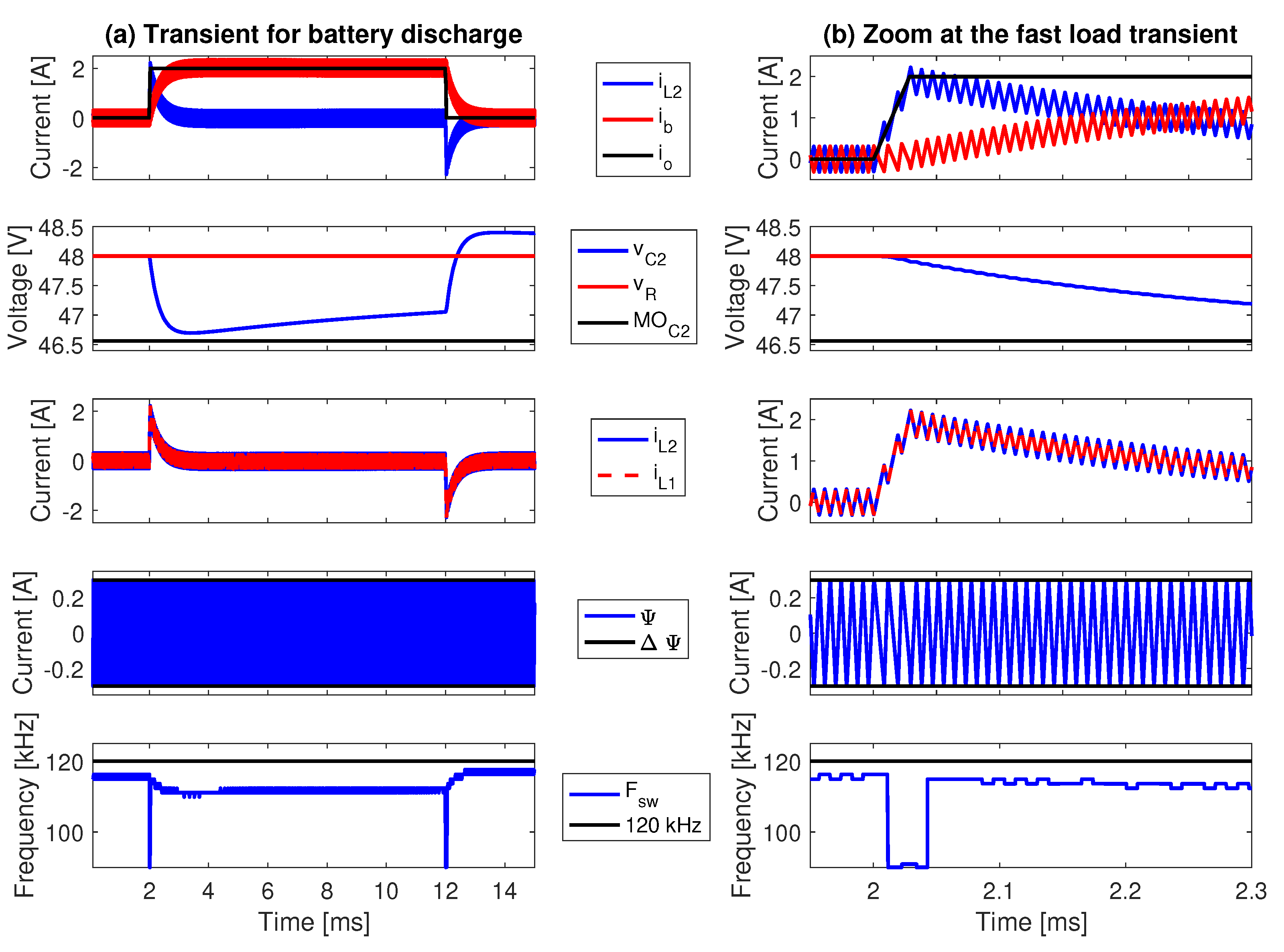

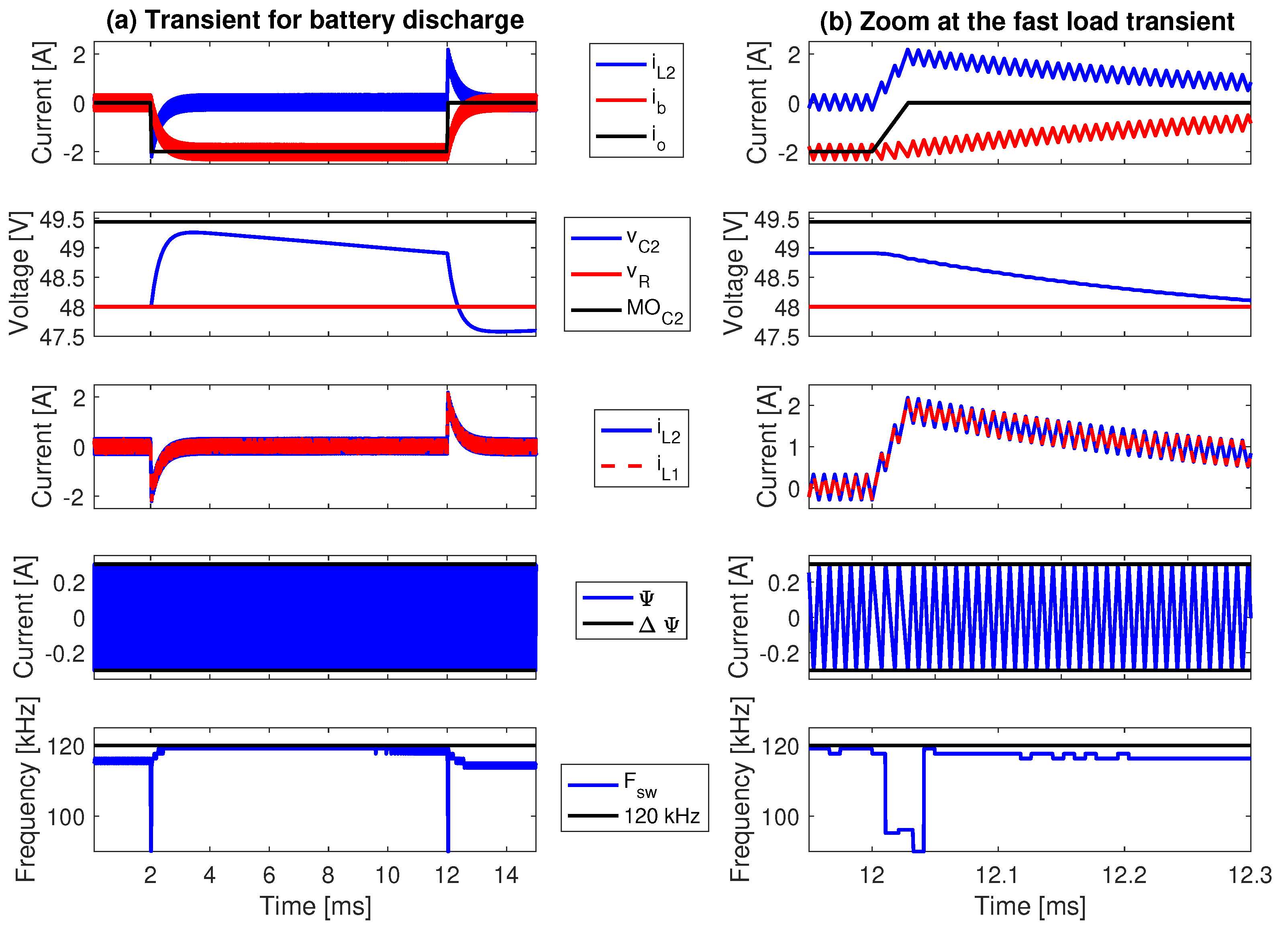

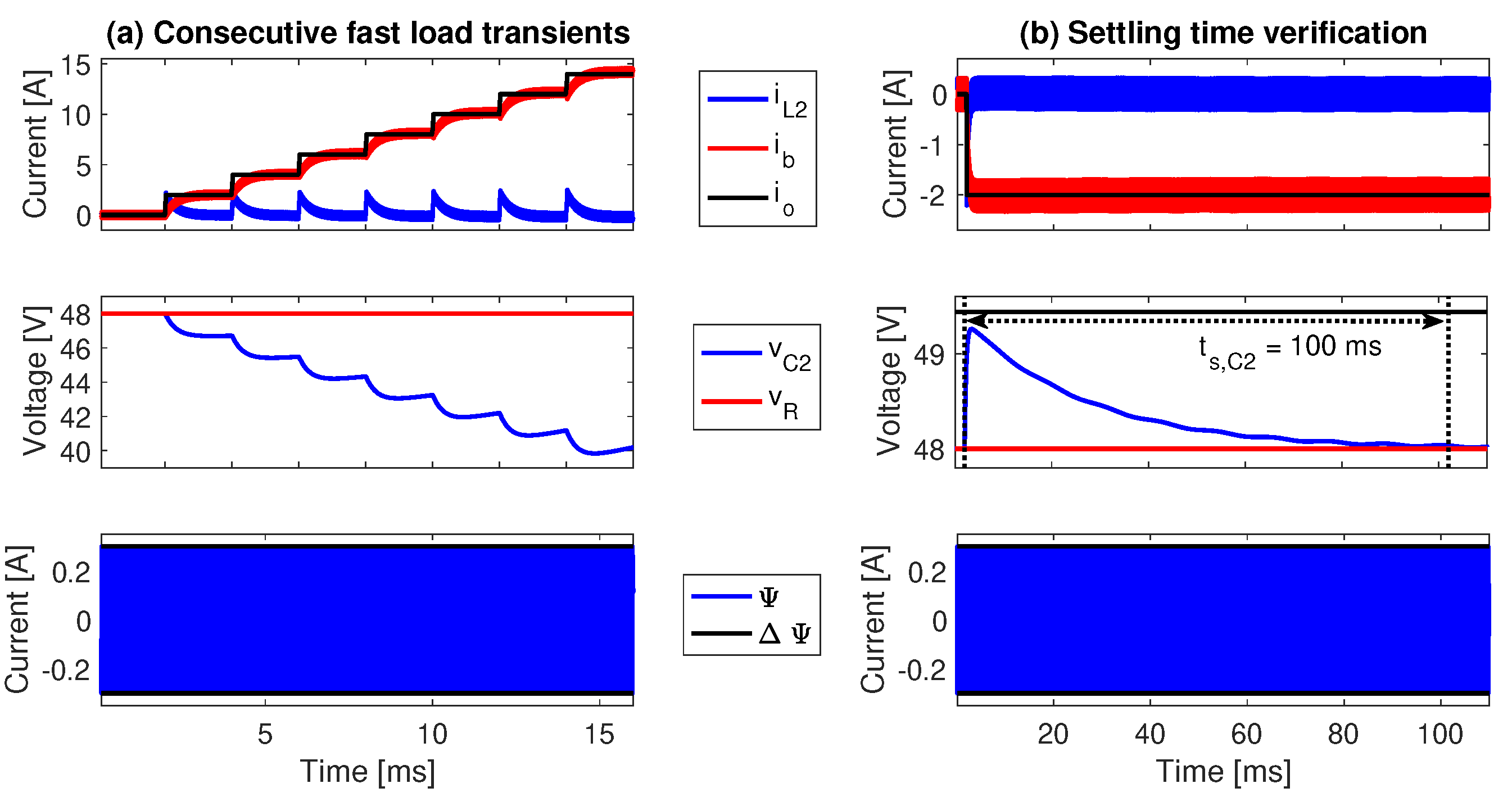

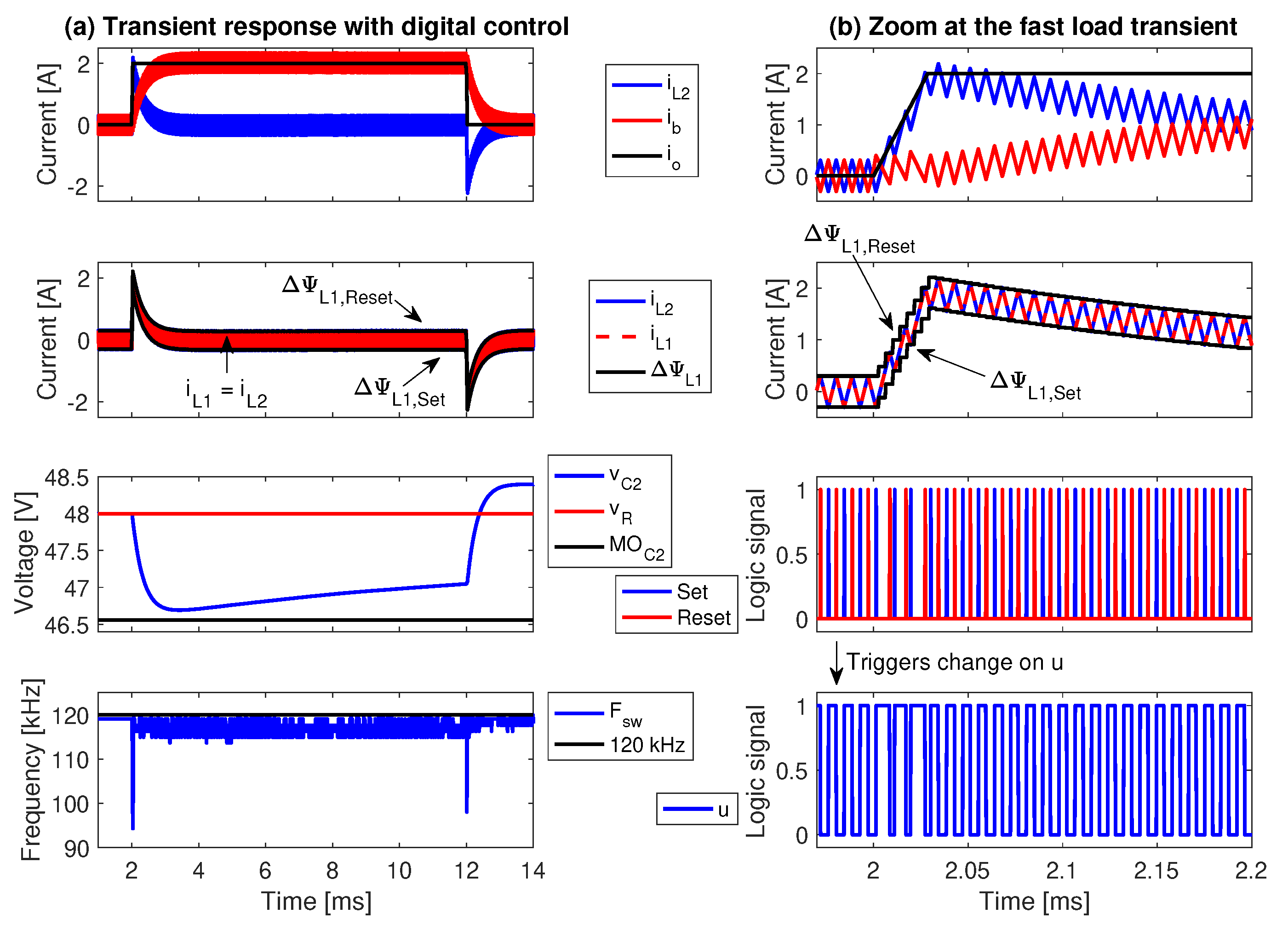

5. Implementation of the Adaptive SMC and Detailed Circuital Simulations

5.1. Analog Implementation of the Adaptive SMC

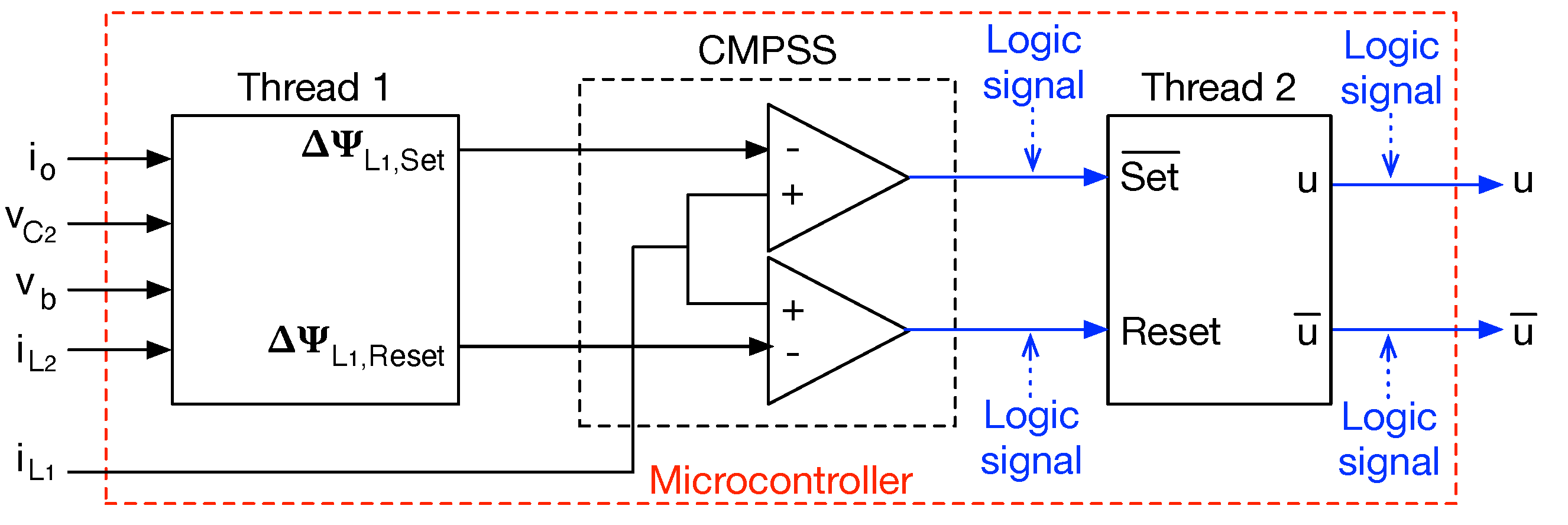

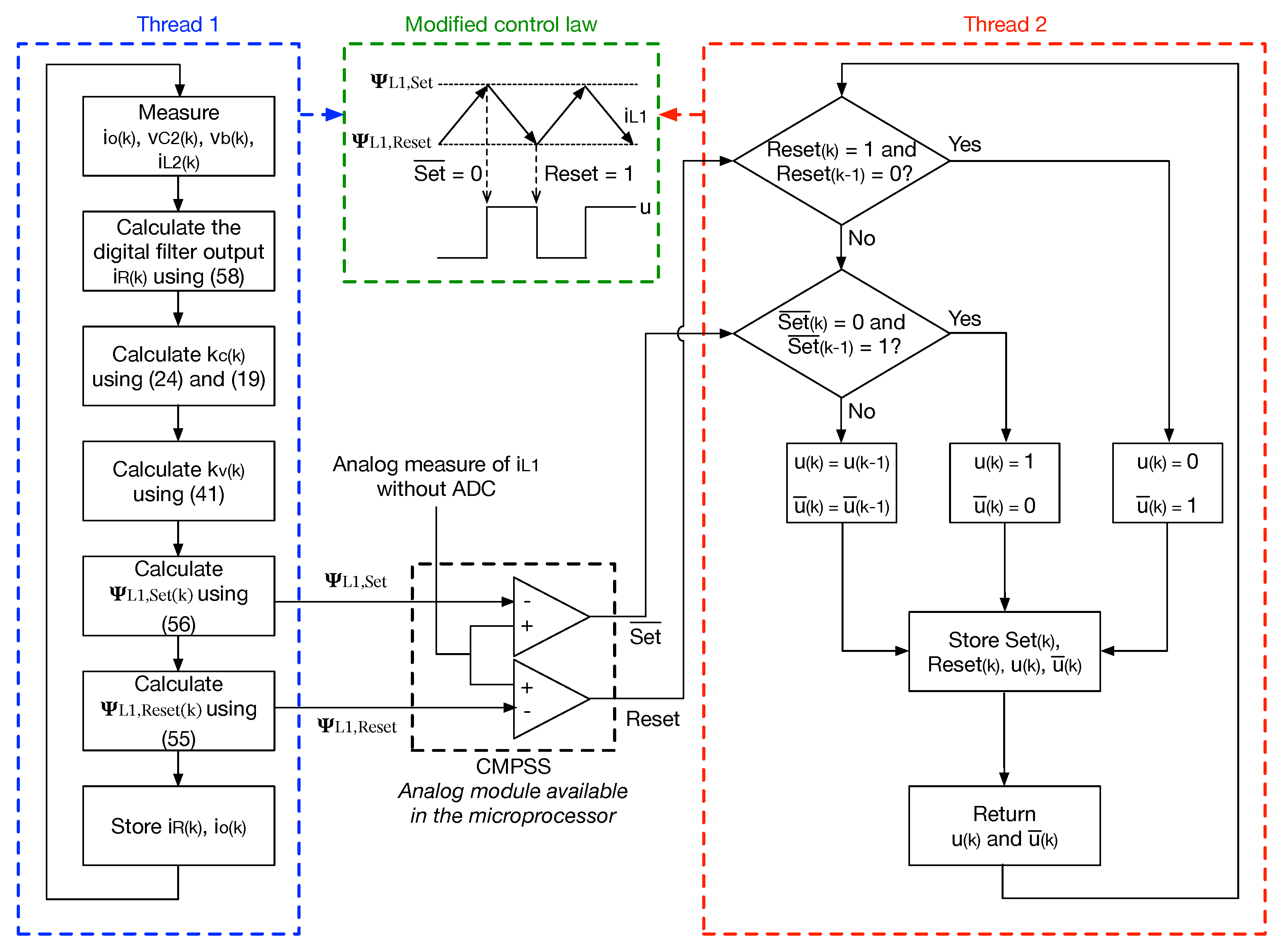

5.2. Digital Implementation of the Adaptive SMC

| Algorithm 3 Thread 1: calculation of the comparator inputs ( and ) | |

| Require: , , , | |

| |

| ▹ High-Pass filter |

| ▹ Calculate the adaptive current gain |

| ▹ Calculate the adaptive voltage gain |

| |

| ▹ Store value |

| ▹ Store value |

| ▹ Signals for the comparators of the CMPSS |

| |

| Algorithm 4 Thread 2: control signal generator (u and ) | |

| |

| ▹ Detect rising edge in |

| |

| ▹ Detect falling edge in |

| |

| ▹ does not change |

| ▹ does not change |

| |

| ▹ Store value |

| ▹ Store value |

| ▹ Store value |

| ▹ Store value |

| ▹ and are provided to the MOSFETs |

| |

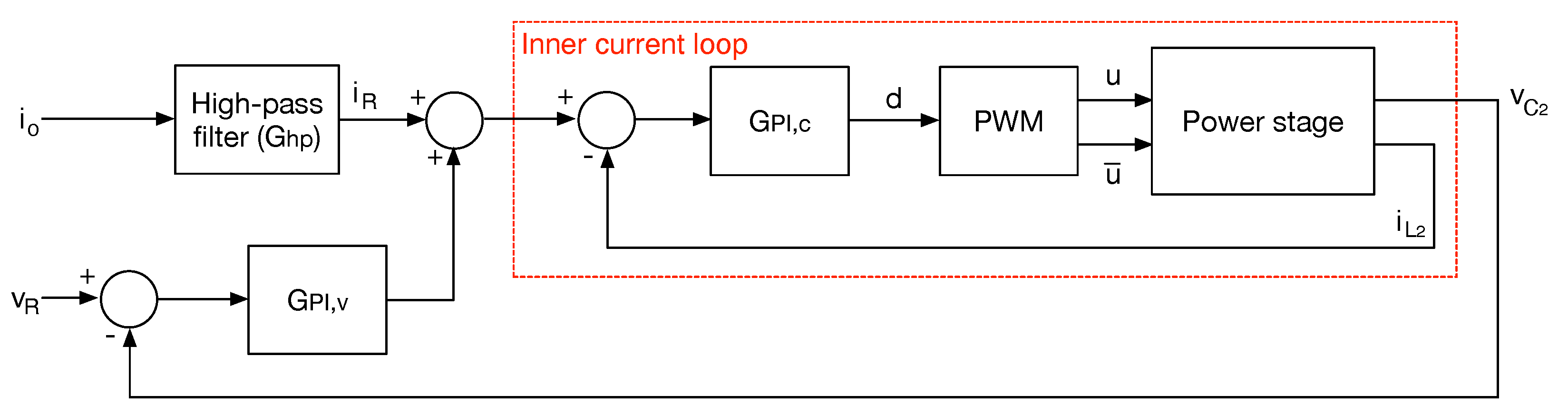

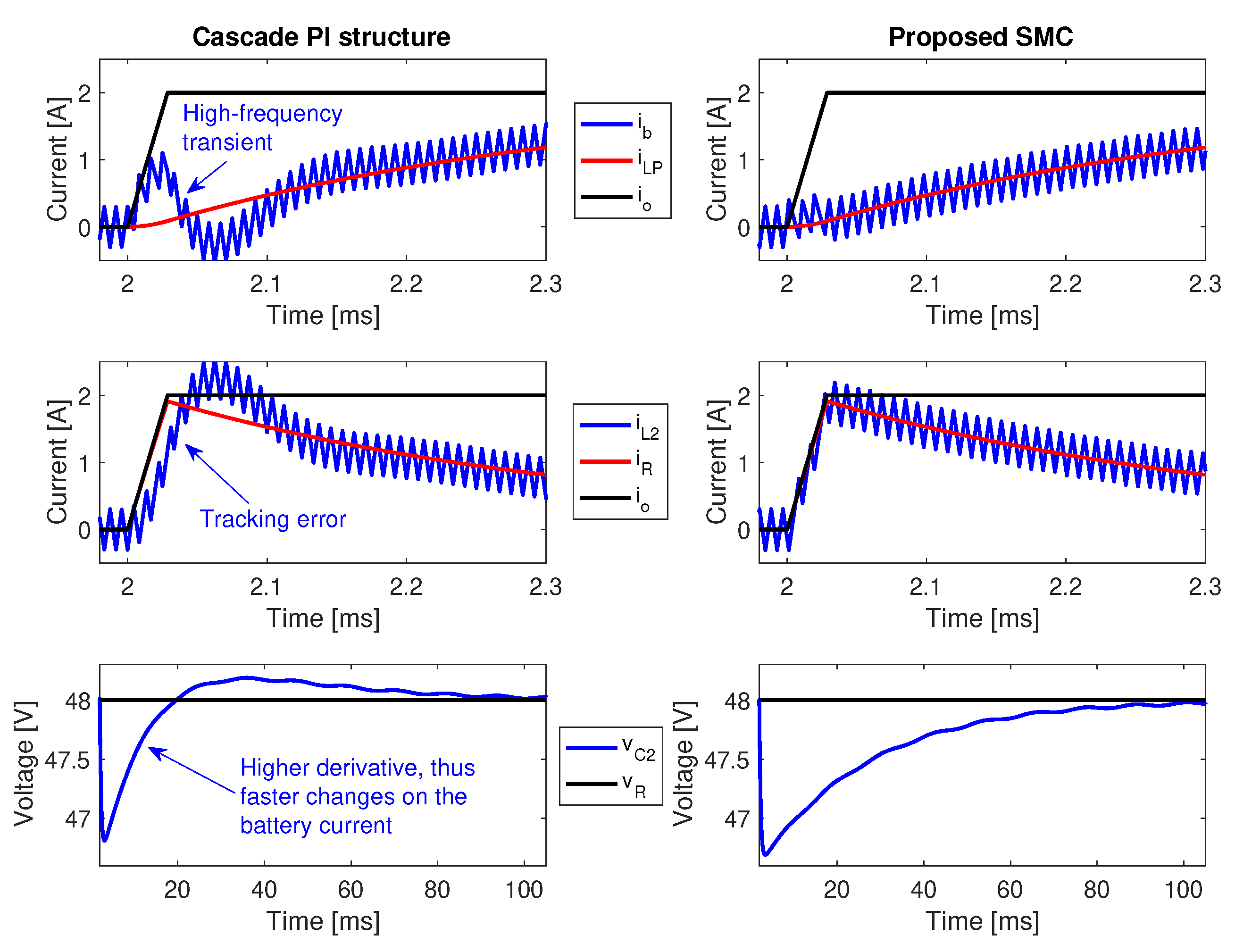

5.3. Comparison with a Classical Controller

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Sun, Y.N.; Zhuang, Z.L.; Xu, H.W.; Qin, W.; Feng, M.J. Data-driven modeling and analysis based on complex network for multimode recognition of industrial processes. J. Manuf. Syst. 2022, 62, 915–924. [Google Scholar] [CrossRef]

- Van De Berg, D.; Savage, T.; Petsagkourakis, P.; Zhang, D.; Shah, N.; Del Rio-Chanona, E.A. Data-driven optimization for process systems engineering applications. Chem. Eng. Sci. 2022, 248, 117135. [Google Scholar] [CrossRef]

- Liu, S.; Cheng, H. Manufacturing Process Optimization in the Process Industry. Int. J. Inf. Technol. Web Eng. 2024, 19, 1–20. [Google Scholar] [CrossRef]

- Ghahramani, M.; Qiao, Y.; Zhou, M.C.; O’Hagan, A.; Sweeney, J. AI-based modeling and data-driven evaluation for smart manufacturing processes. IEEE/CAA J. Autom. Sin. 2020, 7, 1026–1037. [Google Scholar] [CrossRef]

- Cerda-Flores, S.C.; Rojas-Punzo, A.A.; Nápoles-Rivera, F. Applications of Multi-Objective Optimization to Industrial Processes: A Literature Review. Processes 2022, 10, 133. [Google Scholar] [CrossRef]

- Dey, S.; Gupta, N.; Pathak, S.; Kela, D.H.; Datta, S. Data-Driven Design Optimization for Industrial Products. In Optimization in Industry; Datta, S., Davim, J.P., Eds.; Series Title: Management and Industrial Engineering; Springer International Publishing: Cham, Switzerland, 2019; pp. 253–267. [Google Scholar] [CrossRef]

- Zhao, J.; Wang, W.; Sheng, C. Data-Driven Prediction for Industrial Processes and Their Applications; Information Fusion and Data Science; Springer International Publishing: Cham, Switzerland, 2018. [Google Scholar] [CrossRef]

- Aghmadi, A.; Mohammed, O.A. Energy Storage Systems: Technologies and High-Power Applications. Batteries 2024, 10, 141. [Google Scholar] [CrossRef]

- Abo-Khalil, A.G.; Sobhy, A.; Abdelkareem, M.A.; Olabi, A. Advancements and challenges in hybrid energy storage systems: Components, control strategies, and future directions. Int. J. Thermofluids 2023, 20, 100477. [Google Scholar] [CrossRef]

- Leon, J.I.; Dominguez, E.; Wu, L.; Marquez Alcaide, A.; Reyes, M.; Liu, J. Hybrid Energy Storage Systems: Concepts, Advantages, and Applications. IEEE Ind. Electron. Mag. 2021, 15, 74–88. [Google Scholar] [CrossRef]

- Salah, O.; Shamayleh, A.; Mukhopadhyay, S. Energy Management of a Multi-Source Power System. Algorithms 2021, 14, 206. [Google Scholar] [CrossRef]

- Emrani, A.; Berrada, A. A comprehensive review on techno-economic assessment of hybrid energy storage systems integrated with renewable energy. J. Energy Storage 2024, 84, 111010. [Google Scholar] [CrossRef]

- Monhof, M.; Beverungen, D.; Klör, B.; Bräuer, S. Extending Battery Management Systems for Making Informed Decisions on Battery Reuse. In New Horizons in Design Science: Broadening the Research Agenda; Donnellan, B., Helfert, M., Kenneally, J., VanderMeer, D., Rothenberger, M., Winter, R., Eds.; Series Title: Lecture Notes in Computer Science; Springer International Publishing: Cham, Switzerland, 2015; Volume 9073, pp. 447–454. [Google Scholar] [CrossRef]

- Lei, H.; Li, K.; Chong, B. A Review of Hybrid Energy Storage System for Heavy-Duty Electric Vehicle. Transp. Res. Procedia 2023, 70, 234–240. [Google Scholar] [CrossRef]

- Song, Z.; Hofmann, H.; Li, J.; Han, X.; Zhang, X.; Ouyang, M. A comparison study of different semi-active hybrid energy storage system topologies for electric vehicles. J. Power Sources 2015, 274, 400–411. [Google Scholar] [CrossRef]

- Lencwe, M.J.; Chowdhury, S.P.D.; Olwal, T.O. Hybrid energy storage system topology approaches for use in transport vehicles: A review. Energy Sci. Eng. 2022, 10, 1449–1477. [Google Scholar] [CrossRef]

- Hasan, M.K.; Mahmud, M.; Ahasan Habib, A.; Motakabber, S.; Islam, S. Review of electric vehicle energy storage and management system: Standards, issues, and challenges. J. Energy Storage 2021, 41, 102940. [Google Scholar] [CrossRef]

- Castaings, A.; Lhomme, W.; Trigui, R.; Bouscayrol, A. Practical control schemes of a battery/supercapacitor system for electric vehicle. IET Electr. Syst. Transp. 2016, 6, 20–26. [Google Scholar] [CrossRef]

- Shyni, R.; Kowsalya, M. HESS-based microgrid control techniques empowered by artificial intelligence: A systematic review of grid-connected and standalone systems. J. Energy Storage 2024, 84, 111012. [Google Scholar] [CrossRef]

- Atawi, I.E.; Al-Shetwi, A.Q.; Magableh, A.M.; Albalawi, O.H. Recent Advances in Hybrid Energy Storage System Integrated Renewable Power Generation: Configuration, Control, Applications, and Future Directions. Batteries 2022, 9, 29. [Google Scholar] [CrossRef]

- Wang, W.; Yuan, B.; Sun, Q.; Wennersten, R. Application of energy storage in integrated energy systems—A solution to fluctuation and uncertainty of renewable energy. J. Energy Storage 2022, 52, 104812. [Google Scholar] [CrossRef]

- Barelli, L.; Cardelli, E.; Pelosi, D.; Ciupageanu, D.A.; Ottaviano, P.A.; Longo, M.; Zaninelli, D. Energy from the Waves: Integration of a HESS to a Wave Energy Converter in a DC Bus Electrical Architecture to Enhance Grid Power Quality. Energies 2021, 15, 10. [Google Scholar] [CrossRef]

- Moreno, H.; Schaum, A. Low-Order Electrochemical State Estimation for Li-Ion Batteries. Algorithms 2023, 16, 73. [Google Scholar] [CrossRef]

- Liu, S.; Ling, R.; Feng, F. Equalization strategy for fast energy regulation of supercapacitor in hybrid energy storage system. J. Energy Storage 2023, 65, 107318. [Google Scholar] [CrossRef]

- Rahman, A.U.; Zehra, S.S.; Ahmad, I.; Armghan, H. Fuzzy supertwisting sliding mode-based energy management and control of hybrid energy storage system in electric vehicle considering fuel economy. J. Energy Storage 2021, 37, 102468. [Google Scholar] [CrossRef]

- Lencwe, M.J.; Olwal, T.O.; Chowdhury, S.D.; Sibanyoni, M. Nonsolitary two-way DC-to-DC converters for hybrid battery and supercapacitor energy storage systems: A comprehensive survey. Energy Rep. 2024, 11, 2737–2767. [Google Scholar] [CrossRef]

- Zimmermann, T.; Keil, P.; Hofmann, M.; Horsche, M.F.; Pichlmaier, S.; Jossen, A. Review of system topologies for hybrid electrical energy storage systems. J. Energy Storage 2016, 8, 78–90. [Google Scholar] [CrossRef]

- Ramu, S.K.; Vairavasundaram, I.; Palaniyappan, B.; Bragadeshwaran, A.; Aljafari, B. Enhanced energy management of DC microgrid: Artificial neural networks-driven hybrid energy storage system with integration of bidirectional DC-DC converter. J. Energy Storage 2024, 88, 111562. [Google Scholar] [CrossRef]

- Moghadam, M.; Ghaffarzadeh, N. Suppressing solar PV output fluctuations by designing an efficient hybrid energy storage system controller. Unconv. Resour. 2024, 4, 100077. [Google Scholar] [CrossRef]

- Srinivasan, C.; Sheeba Joice, C. Energy management of hybrid energy storage system in electric vehicle based on hybrid SCSO-RERNN approach. J. Energy Storage 2024, 78, 109733. [Google Scholar] [CrossRef]

- Guentri, H.; Allaoui, T.; Mekki, M.; Denai, M. Power management and control of a photovoltaic system with hybrid battery-supercapacitor energy storage based on heuristics methods. J. Energy Storage 2021, 39, 102578. [Google Scholar] [CrossRef]

- Erickson, R.W.; Maksimović, D. Fundamentals of Power Electronics; Springer International Publishing: Cham, Switzerland, 2020. [Google Scholar] [CrossRef]

- Perruquetti, W.; Barbot, J.P. Sliding Mode Control in Engineering; Marcel Dekker: New York, NY, USA, 2002; Volume 11. [Google Scholar]

- Sira-Ramirez, H. Sliding motions in bilinear switched networks. IEEE Trans. Circuits Syst. 1987, 34, 919–933. [Google Scholar] [CrossRef]

- Ogata, K. Modern Control Engineering, 5th ed.; eTextbook; Pearson: London, UK, 2021. [Google Scholar]

- Clayton, G.B.; Winder, S. Operational Amplifiers; Elsevier: Amsterdam, The Netherlands, 2003. [Google Scholar]

- Devices, A. 10 MHz, Four-Quadrant Multiplier/Divider AD734; Datasheet; Analog Device, Inc.: Norwood, MA, USA, 2011. [Google Scholar]

- Instruments, T. TMS320F2837xD Dual-Core Real-Time Microcontrollers; Datasheet; Texas Instruments, Inc.: Dallas, TX, USA, 2024. [Google Scholar]

- Paarmann, L.D. Design and Analysis of Analog Filters: A Signal Processing Perspective; Springer Science & Business Media: Berlin/Heidelberg, Germany, 2001; Volume 617. [Google Scholar]

- Petrone, G.; Ramos-Paja, C.A.; Spagnuolo, G. Photovoltaic Sources Modeling, 1st ed.; Wiley: Hoboken, NJ, USA, 2017. [Google Scholar] [CrossRef]

| Ref. | Storage Device | HESS Type | Control’s Algorithm | Converter | Comments |

|---|---|---|---|---|---|

| [30] | SC-baterry | Fully active | SCSO-RERNN | Buck-boost | EV application |

| [29] | SC-battery | Fully active | PI (battery), MPC (SC) | BC not specified | MG with PV |

| [28] | SC-battery | Fully active | ANN | Buck-boost | References’ generation with ANN |

| [31] | SC-battery | Fully active | PI | Buck-boost | PI tunning with LMI-PSO-GA. |

| [25] | SC-battery | Fully active | SSMC | Buck-boost | References’ generation with fuzzy logic |

| [18] | SC-battery | SC Semi-active | PI | Boost | EV application |

| Description | Variable | Value |

|---|---|---|

| Battery voltage | 48 V | |

| Nominal voltage | 48 V | |

| Maximum deviation of voltage | ||

| Settling time of voltage | 100 ms | |

| Maximum derivative in the load current | A/ms | |

| Maximum load transient magnitude | A | |

| Maximum safe frequency for the battery | 500 Hz | |

| Maximum switching frequency | 120 kHz |

| Parameter | Value | Nominal Condition | Energy Stored |

|---|---|---|---|

| H | A | Wh, Ah | |

| H | A | Wh, Ah | |

| F | V | mWh, mAh | |

| F | V | mWh, mAh | |

| A | - | - |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tobón, A.; Ramos-Paja, C.A.; Orozco-Gutíerrez, M.L.; Saavedra-Montes, A.J.; Serna-Garcés, S.I. Adaptive Sliding-Mode Controller for a Zeta Converter to Provide High-Frequency Transients in Battery Applications. Algorithms 2024, 17, 319. https://doi.org/10.3390/a17070319

Tobón A, Ramos-Paja CA, Orozco-Gutíerrez ML, Saavedra-Montes AJ, Serna-Garcés SI. Adaptive Sliding-Mode Controller for a Zeta Converter to Provide High-Frequency Transients in Battery Applications. Algorithms. 2024; 17(7):319. https://doi.org/10.3390/a17070319

Chicago/Turabian StyleTobón, Andrés, Carlos Andrés Ramos-Paja, Martha Lucía Orozco-Gutíerrez, Andrés Julián Saavedra-Montes, and Sergio Ignacio Serna-Garcés. 2024. "Adaptive Sliding-Mode Controller for a Zeta Converter to Provide High-Frequency Transients in Battery Applications" Algorithms 17, no. 7: 319. https://doi.org/10.3390/a17070319

APA StyleTobón, A., Ramos-Paja, C. A., Orozco-Gutíerrez, M. L., Saavedra-Montes, A. J., & Serna-Garcés, S. I. (2024). Adaptive Sliding-Mode Controller for a Zeta Converter to Provide High-Frequency Transients in Battery Applications. Algorithms, 17(7), 319. https://doi.org/10.3390/a17070319