The Evolution of Organosilicon Precursors for Low-k Interlayer Dielectric Fabrication Driven by Integration Challenges

Abstract

1. Introduction

2. General Classification of Organosilicon Dielectric Material

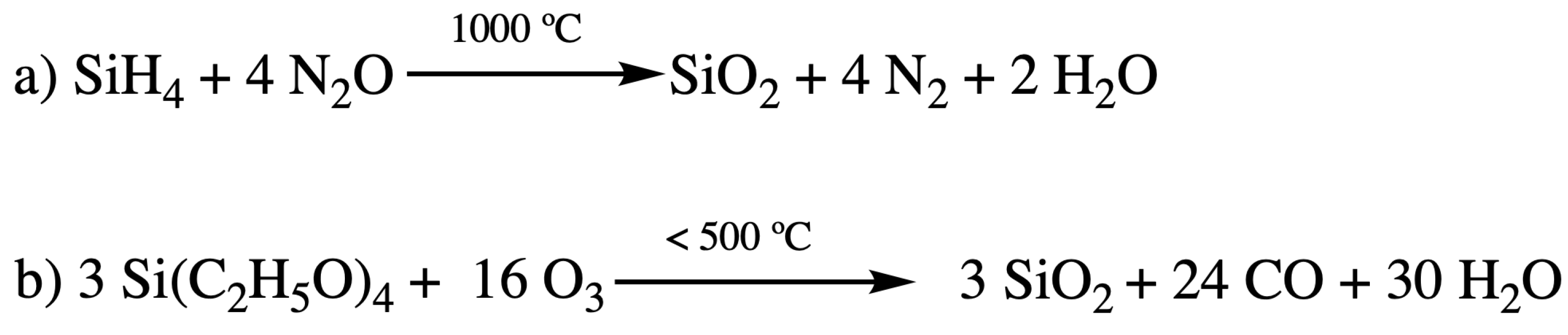

2.1. SiO2

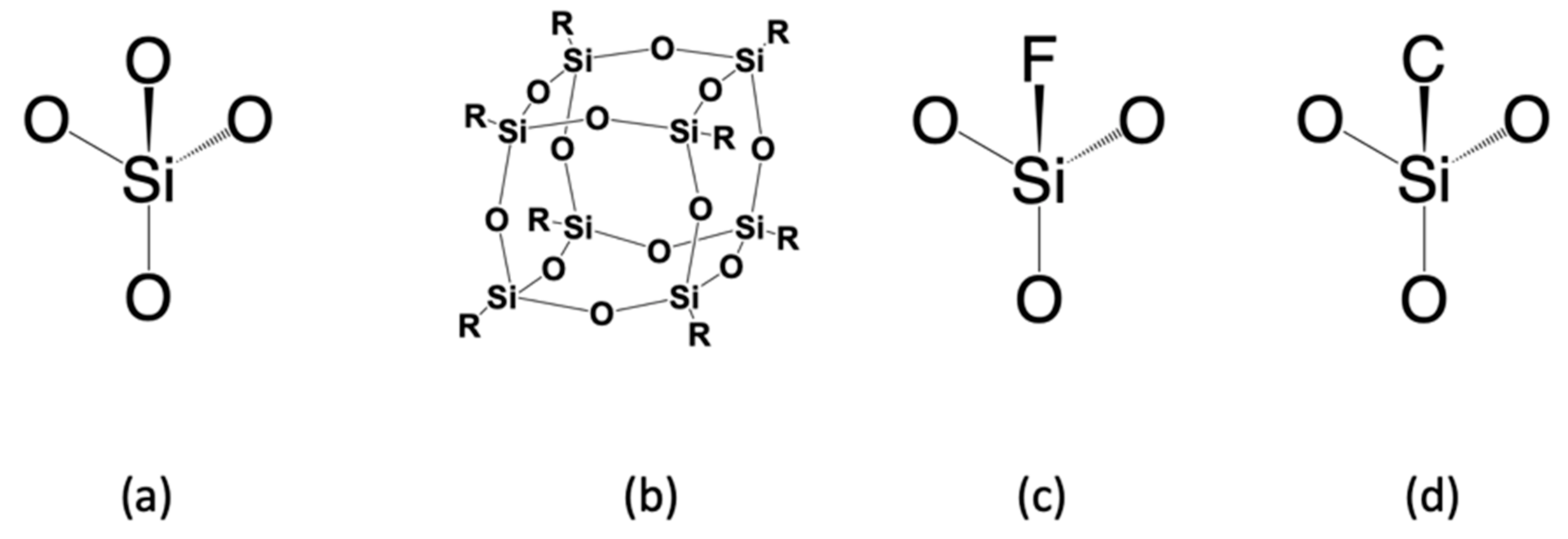

2.2. Silsesquioxane (SSQ) Based Materials

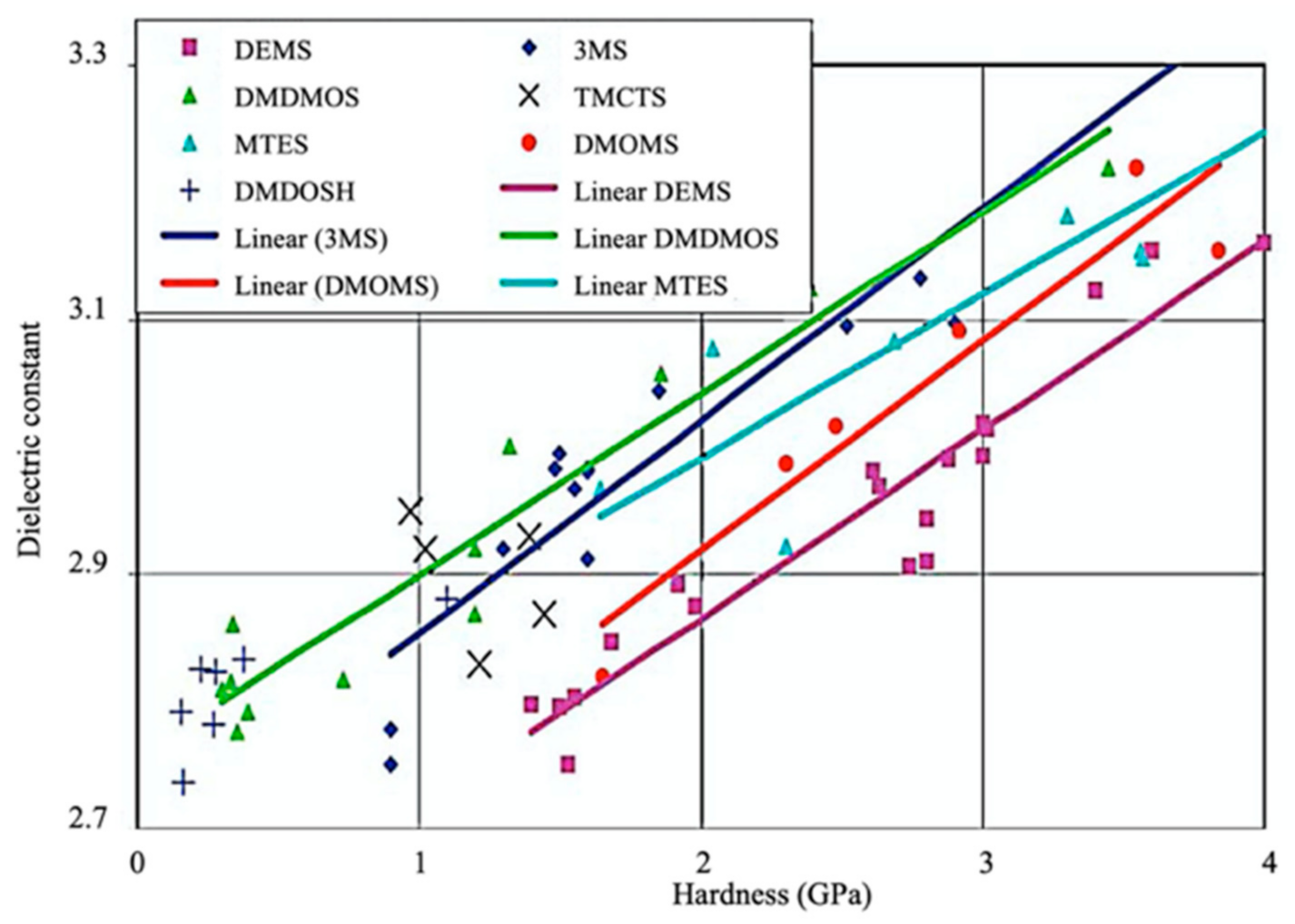

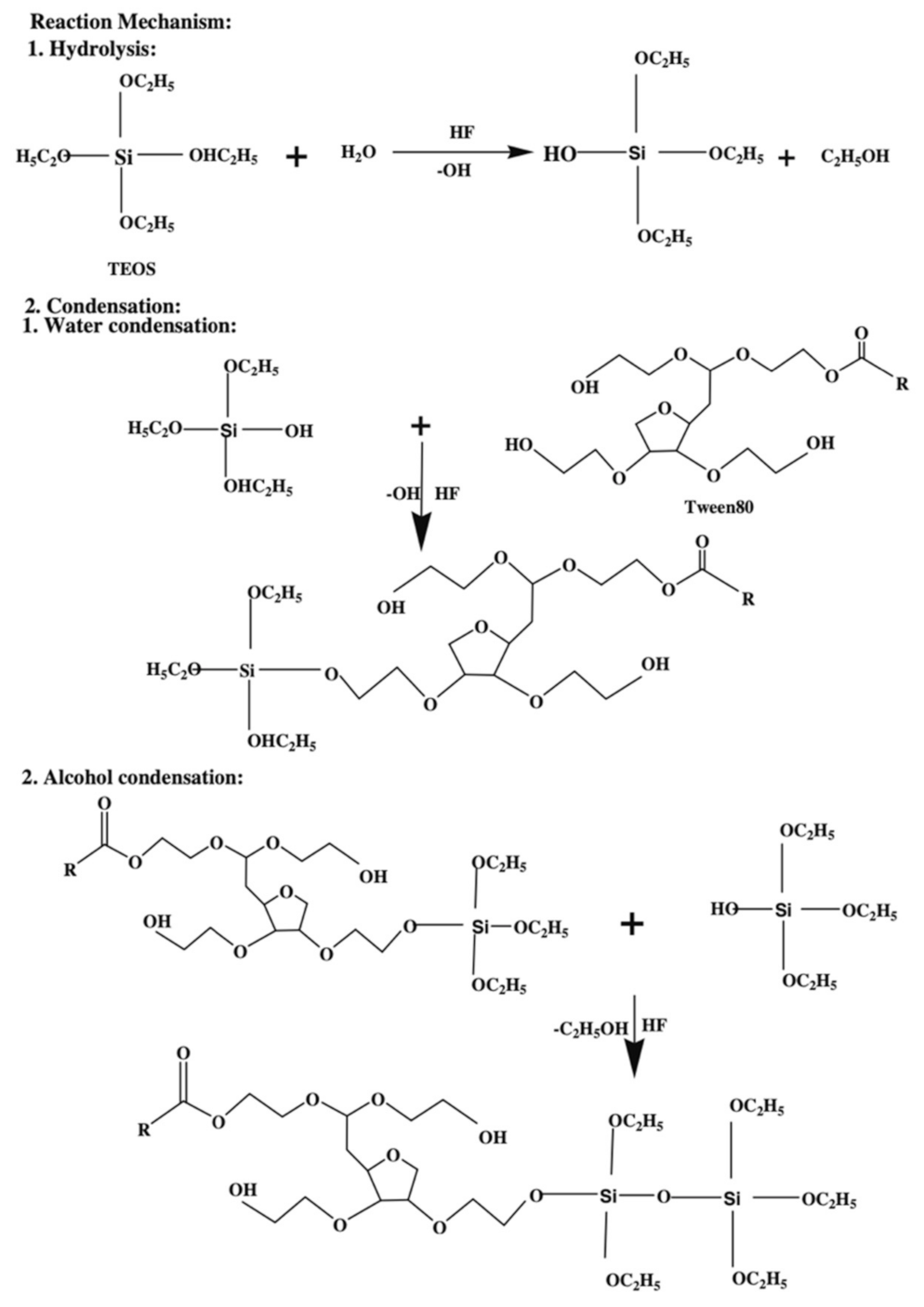

2.3. Silica-Based Materials

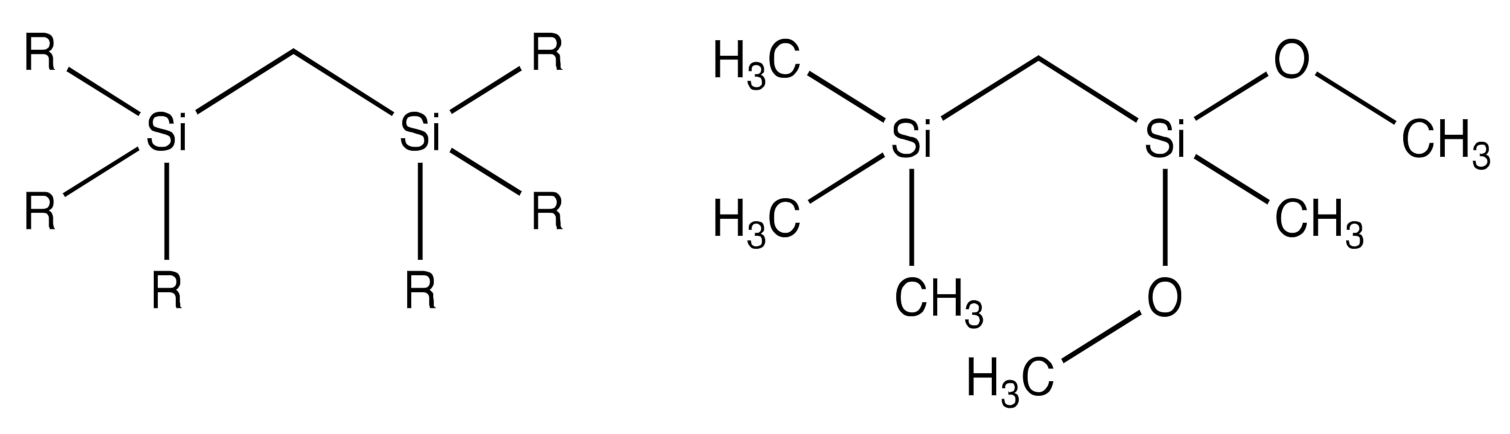

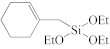

2.4. Porous Organo–Silicon Materials

3. Deposition Methods

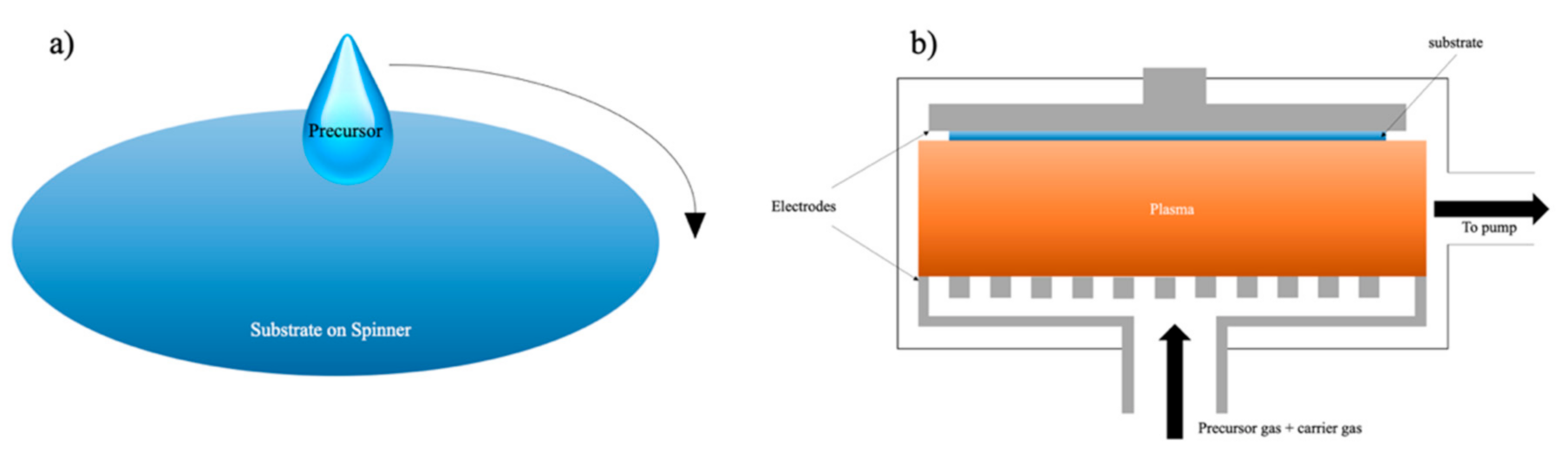

3.1. Spin-On Deposition

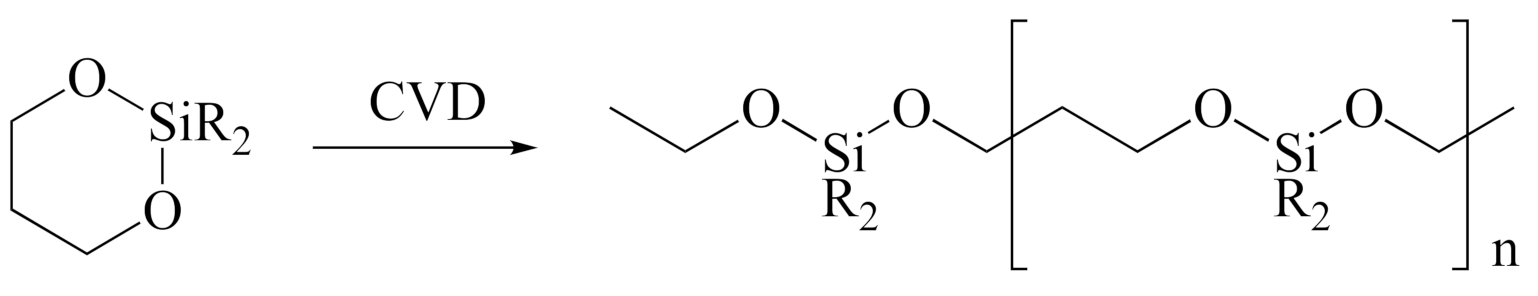

3.2. Chemical Vapor Deposition (CVD)

4. Integration Challenges

4.1. Improving Adhesion

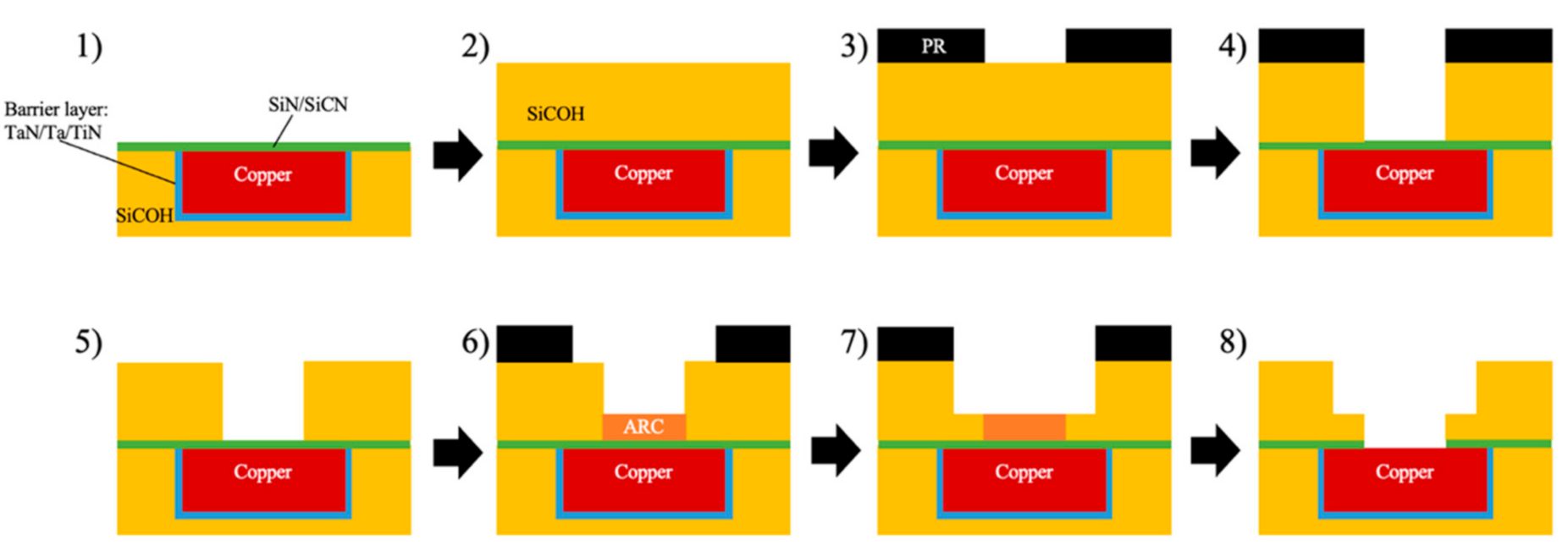

4.2. Dual-Damascene Process and Plasma-Induced Damage

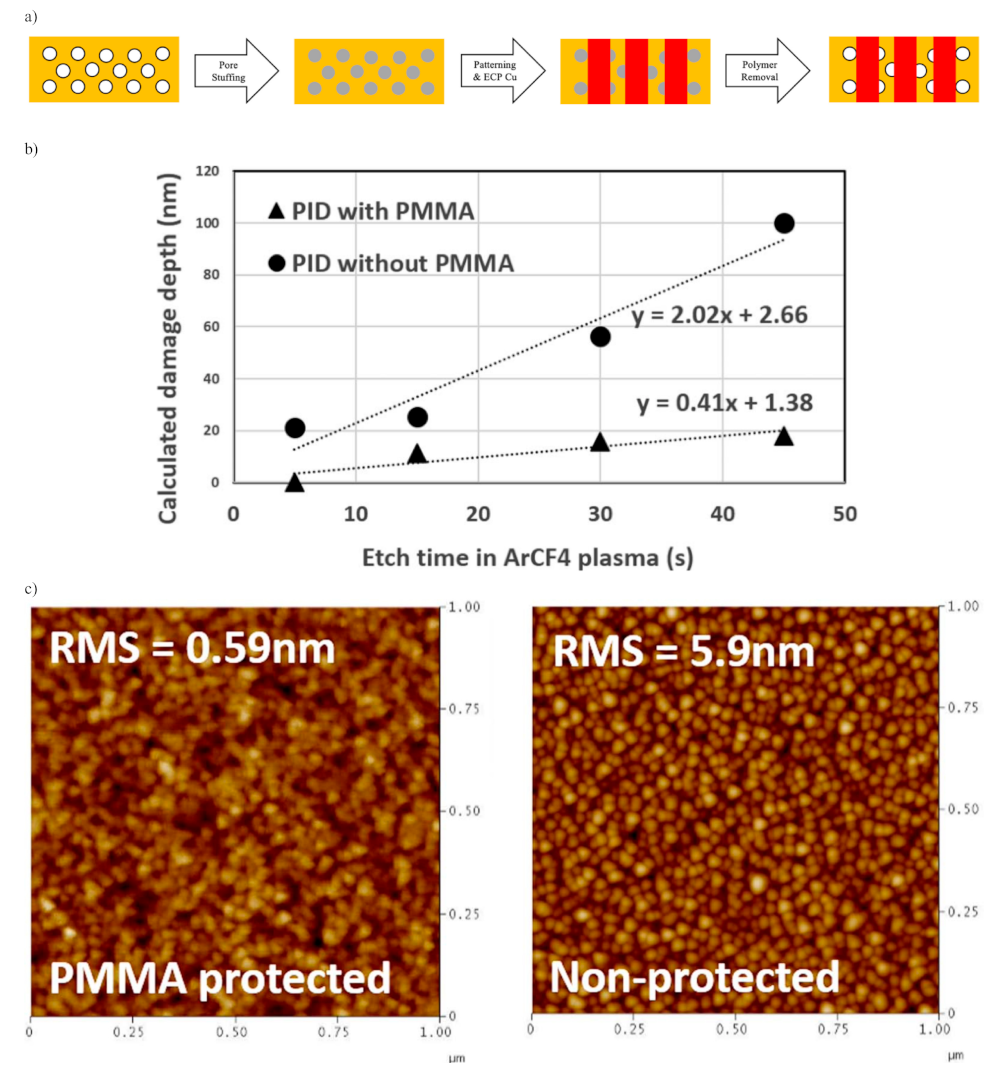

4.3. PID Prevention

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Acknowledgments

Conflicts of Interest

References

- Moore, G. Cramming more components onto integrated circuits. Electronics 1965, 38, 114–117. [Google Scholar] [CrossRef]

- Irven, J. Precursor chemistries for the electronics, opto-electronics and optical industries. J. Mater. Chem. 2004, 14, 3071–3080. [Google Scholar] [CrossRef]

- Ray, S.K.; Maiti, C.K.; Lahiri, S.K.; Chakrabarti, N.B. Properties of silicon dioxide films deposited at low temperatures by microwave plasma enhanced decomposition of tetraethylorthosilicate. J. Vac. Sci. Technol. B 1992, 10, 1139–1150. [Google Scholar] [CrossRef]

- Dobkin, D.M.M.S.; Schmidt, M.; Pant, A.; Robinson, L.; Sherman, A. Mechanisms of Deposition of SiO2 from TEOS and Related Organosilicon Compounds and Ozone. J. Electrochem. Soc. 1995, 142, 2332–2340. [Google Scholar] [CrossRef]

- Okada, H.; Baba, M.; Furukawa, M.; Yamane, K.; Sekiguchi, H.; Wakahara, A. Formation of SiO2 film by chemical vapor deposition enhanced by atomic species extracted from a surface-wave generated plasma. AIP Conf. Proc. 2017, 1807, 020006. [Google Scholar]

- Zhang, J.; Wavhal, D.; Fisher, E. Mechanisms of SiO2 film deposition from tetramethylcyclotetrasiloxane, dimethyldimethoxysilane, and trimethylsilane plasmas. J. Vac. Sci. Technol. A 2004, 22, 201–213. [Google Scholar] [CrossRef]

- Sekhar, V.N. Mechanical Characterization of Black Diamond (Low-k) Structures for 3D Integrated Circuit and Packaging Applications. Nanoindentation Mater. Sci. 2012, 10, 229–256. [Google Scholar]

- Maex, K.; Baklanov, M.R.; Shamiryan, D.; Lacopi, F.; Brongersma, S.H.; Yanovitskaya, Z.S. Low dielectric constant materials for microelectronics. J. Appl. Phys. 2003, 93, 8793–8841. [Google Scholar] [CrossRef]

- Puyrenier, W.; Rouessac, V.; Broussous, L.; Rébiscoul, D.; Ayral, A. Effect of plasma treatments on a porous low-k material—Study of pore sealing. Microporous Mesoporous Mater. 2007, 106, 40–48. [Google Scholar] [CrossRef]

- Peng, H.; Chi, D.; Wang, W.; Li, J.; Zeng, K.; Vallery, R.S.; Frieze, W.E.; Skalsey, M.A.; Gidley, D.W.; Yee, A.F. Pore Sealing by NH3 Plasma Treatment of Porous Low Dielectric Constant Films. J. Electrochem. Soc. 2007, 154, G85–G94. [Google Scholar] [CrossRef]

- Cheng, Y.; Lee, C.; Haung, C. Plasma Damage on Low-k Dielectric Materials. In Plasma Science and Technology-Basic Fundamentals and Modern Applications; IntechOpen: London, UK, 2018. [Google Scholar]

- Seok, S.I.; Ahn, C.H.; Jin, M.Y.; Lee, C.J.; Kang, Y. Effect of molecular weight on the mechanical properties of MSSQ films. Mater. Chem. Phys. 2004, 84, 259–262. [Google Scholar] [CrossRef]

- Cheng, Y.L.; Wang, Y.L.; Liu, C.W.; Wu, Y.L.; Lo, K.Y.; Liu, C.P.; Lan, J.K. Characterization and Reliability of Low Dielectric Constant Fluorosilicate glass and Silicon Rich Oxide Process for Deep Sub-Micro Device Application. Thin Solid Films 2001, 398–399, 533–538. [Google Scholar] [CrossRef]

- Shapiro, M.J.; Nguyen, S.V.; Matsuda, T.; Dobuzinsky, D. CVD of fluorosilicate glass for ULSI applications. Thin Solid Films 1995, 270, 503–507. [Google Scholar] [CrossRef]

- Shamiryan, D.; Abell, T.; Iacopi, F.; Maex, K. Low-k dielectric materials. Mater. Today 2004, 7, 34–39. [Google Scholar] [CrossRef]

- Cheng, Y.L.; Wang, Y.L.; Lan, J.K.; Hwang, G.J.; O’Neil, M.L.; Chen, C.F. Heat, moisture and chemical resistance on low dielectric constant (low-k) film using Diethoxymethylsilane (DEMS) prepared by plasma enhanced chemical vapor deposition. Surf. Coat. Technol. 2006, 200, 3127–3133. [Google Scholar] [CrossRef]

- Cheng, Y.L.; Wang, Y.L.; Hwang, G.J.; O’Neill, M.L.; Karwacki, E.J.; Liu, P.T.; Chen, C.F. Effect of deposition temperature and oxygen flow rate on properties of low dielectric constant SiCOH film prepared by plasma enhanced chemical vapor deposition using diethoxymethylsilane. Surf. Coat. Technol. 2006, 200, 3134–3139. [Google Scholar] [CrossRef]

- Navamathavan, R.; Choi, C.K. Plasma enhanced chemical vapor deposition of low dielectric constant SiOC(–H) films using MTES/O2 precursor. Thin Solid Films 2007, 515, 5040–5044. [Google Scholar] [CrossRef]

- O’Neill, M.; Vrtis, R.; Vincent, J.; Lukas, A.; Karwacki, E.; Peterson, B.; Bitner, M. Optimized Materials Properties for Organosilicate Glasses Produced by Plasma-Enhanced Chemical Vapor Deposition. Mater. Res. Soc. Symp.-Proc. 2003, 766, 8171–8176. [Google Scholar] [CrossRef]

- Du, J.; Summers, J.; Zorman, C. Development of PECVD SiC for MEMS using 3MS as the precursor. MRS Proc. 2006, 911, B05-28. [Google Scholar] [CrossRef]

- Wu, Q.; Gleason, K. Plasma-enhanced chemical vapor deposition of low-k dielectric films using methylsilane, dimethylsilane, and trimethylsilane precursors. J. Vac. Sci. Technol. A 2003, 21, 388–393. [Google Scholar] [CrossRef]

- Vincent, J.L.; O’Neil, M.L.; Withers, H.P.; Beck, S.E.; Vrtis, R.N. Organosilicon Precursors for Interlayer Dielectric Films with Low Dielectric Constants. U.S. Patent 6,583,048, 8 September 2004. [Google Scholar]

- Chapelon, L.L.; Arnal, V.; Broekaart, M.; Gosset, L.G.; Vitiello, J.; Torres, J. Porous ultra low k deposited by PECVD: From deposition to material properties. Microelectron. Eng. 2004, 76, 1–4. [Google Scholar] [CrossRef]

- Dultsev, F.N.; Nekrasov, D.V. Transformation of porous structure under vacuum ultraviolet irradiation of the films based on silicon dioxide. Thin Solid Films 2016, 603, 249–254. [Google Scholar] [CrossRef]

- Zhou, M.; Zhang, B. Preparation of porous ultra low k films using different sacrificial porogen precursors for 28nM technological node. Mater. Sci. Semicond. Process. 2015, 36, 170–178. [Google Scholar] [CrossRef]

- Grill, A. Plasma enhanced chemical vapor deposited SiCOH dielectrics: From low-k to extreme low-k interconnect materials. J. Appl. Phys. 2003, 93, 1785–1790. [Google Scholar] [CrossRef]

- Grill, A.; Gates, S.M.; Ryan, T.E.; Nguyen, S.V.; Priyadarshini, D. Progress in the development and understanding of advanced low k and ultralow k dielectrics for very large-scale integrated interconnects—State of the art. Appl. Phys. Rev. 2014, 1, 1–17. [Google Scholar] [CrossRef]

- Grill, A.; Patel, V. Ultralow-k dielectrics prepared by plasma-enhanced chemical vapor deposition. Appl. Phys. Lett. 2001, 79, 803–805. [Google Scholar] [CrossRef]

- Grill, A. Porous pSiCOH Ultralow-k Dielectrics for Chip Interconnects Prepared by PECVD. Annu. Rev. Mater. Res. 2009, 39, 49–69. [Google Scholar] [CrossRef]

- Wu, Q.; Srinivasan, E.; Vitkavage, D. PECVD Methods for Producing Ultra Low-k Dielectric Films Using UV Treatment. U.S. Patent 7,906,174B1, 15 March 2011. [Google Scholar]

- Nguyen, S.V.; Gates, S.M.; Neumayer, D.A.; Grill, A. Ultra Low k Plasma Enhanced Chemical Vapor Deposition Processes Using a Single Bifunctional Precursor Containing Both a SiCOH Matrix Functionality and Organic Porogen Functionality. U.S. Patent 7,491,658, 11 June 2009. [Google Scholar]

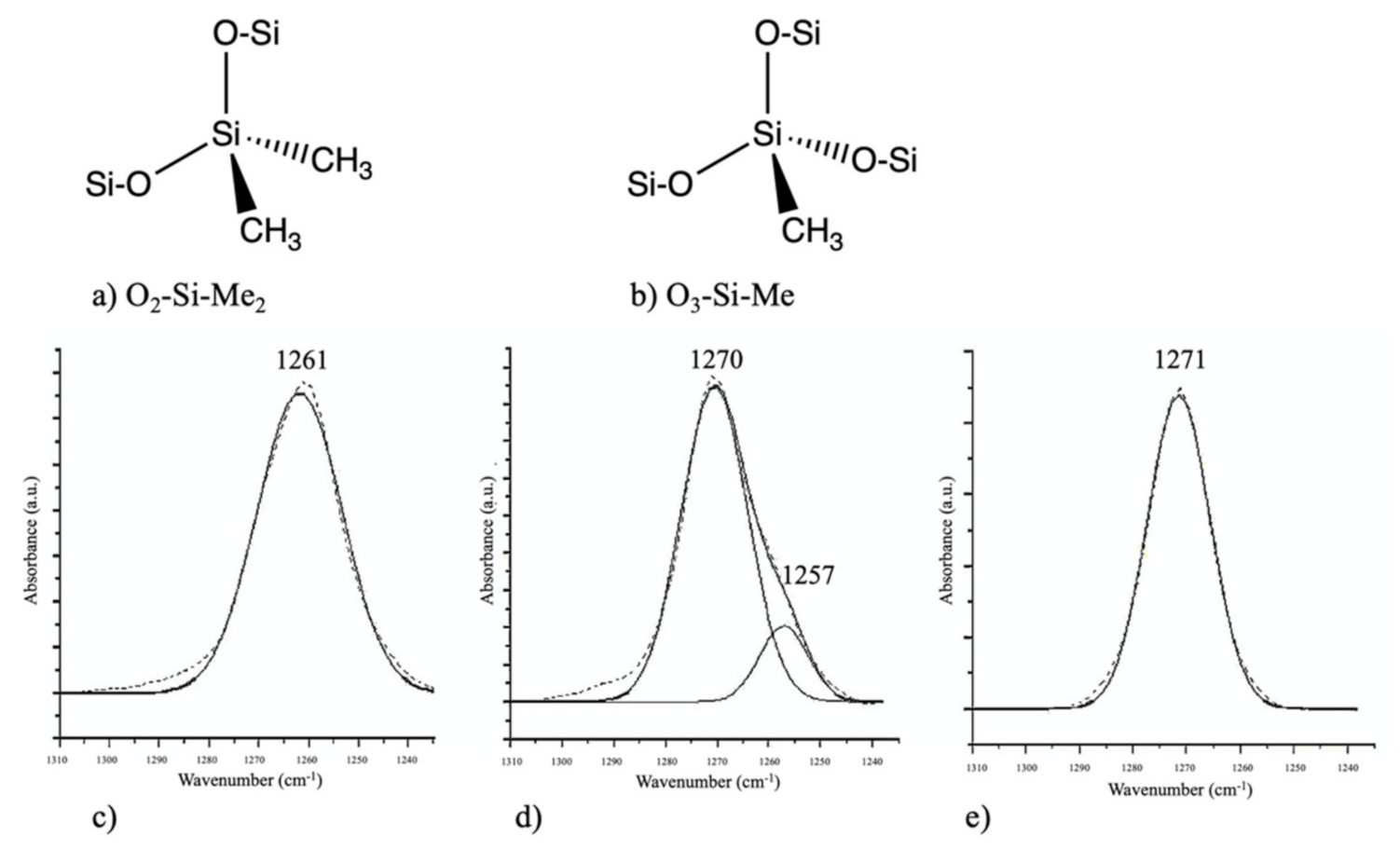

- Shamiryan, D.; Weidner, K.; Gray, W.D.; Baklanov, M.R.; Vanhaelemeersch, S.; Maex, K. Comparative study of PECVD SiOCH low-k films obtained at different deposition conditions. Microelectron. Eng. 2002, 64, 361–366. [Google Scholar] [CrossRef]

- Favennec, L.; Jousseaume, V.; Rouessac, V.; Fusalba, F.; Durand, J.; Passemard, G. Porous extreme low κ (ELκ) dielectrics using a PECVD porogen approach. Mater. Sci. Semicond. Process. 2004, 7, 277–282. [Google Scholar] [CrossRef]

- Grill, A.; Patel, V. Ultralow dielectric constant pSiCOH films prepared with tetramethylcyclotetrasiloxane as skeleton precursor. J. Appl. Phys. 2008, 104, 024113. [Google Scholar] [CrossRef]

- Castex, A.; Favennec, L.; Jousseaume, V.; Bruat, J.; Deval, J.; Remiat, B.; Passemard, G.; Pons, M. Study of plasma mechanisms of hybrid a–SiOC:H low-k film deposition from decamethylcyclopentasiloxane and cyclohexene oxide. Microelectron. Eng. 2005, 82, 416–421. [Google Scholar] [CrossRef]

- Castex, A.; Jousseaume, V.; Deval, J.; Bruat, J.; Favennec, L.; Passemard, G. Ultralow k films by using a plasma-enhanced chemical vapor deposition porogen approach: Study of the precursor reaction mechanisms. J. Vac. Sci. Technol. A 2008, 26, 1343–1354. [Google Scholar] [CrossRef]

- Hsu, I.J.; Vrtis, R.N.; Al-Rashid, J.E.; Mallikarjunan, A.; Theodorou, K.E.; Zielinski, J.M. Understanding the Impact of Porosity and Pore Structure in Ultra Low Dielectric Constant Organosilicate Glasses. MRS Online Proc. Libr. 2012, 1428, 38–44. [Google Scholar] [CrossRef]

- You, H.; Mennell, P.; Shoudy, M.; Sil, D.; Dorman, D.; Cohen, S.; Liniger, E.; Shaw, T.; Leo, T.-L.; Canaperi, D.; et al. Extreme-low k porous pSiCOH dielectrics prepared by PECVD. J. Vac. Sci. Technol. B 2017, 36, 012202. [Google Scholar] [CrossRef]

- Favennec, L.; Jousseaume, V.; Gerbaud, G.; Zenasni, A.; Passemard, G. Ultralow k using a plasma enhanced chemical vapor deposition porogen approach: Matrix structure and porogen loading influences. J. Appl. Phys. 2007, 102, 064107. [Google Scholar] [CrossRef]

- Lehmann, D.; Seidel, F.; Zahn, D.R.T. Thin films with high surface roughness: Thickness and dielectric function analysis using spectroscopic ellipsometry. SpringerPlus 2014, 3, 82. [Google Scholar] [CrossRef] [PubMed]

- Nostell, P.; Roos, A.; Karlsson, B. Optical and mechanical properties of sol-gel antireflective films for solar energy applications. Thin Solid Films 1999, 351, 170–175. [Google Scholar] [CrossRef]

- Alam, M.J.; Cameron, D.C. Optical and electrical properties of transparent conductive ITO thin films deposited by sol–gel process. Thin Solid Films 2000, 377–378, 455–459. [Google Scholar] [CrossRef]

- Pawar, N.B.; Mhaisagar, Y.S.; Gaikwad, A.S.; Mahajan, A.M. Synthesis and Characterization of Porogen Based Porous Low-k Thin Films. Silicon 2017, 9, 439–446. [Google Scholar] [CrossRef]

- Kim, J.; Park, H.; Hyun, S. The evolution of microstructure and surface bonding in SiO2 aerogel film after plasma treatment using O2, N2, and H2 gases. Thin Solid Films 2001, 384, 236–242. [Google Scholar] [CrossRef]

- Brinker, C.J.; Scherer, G.W. Sol-Gel Science, The Physics and Chemistry of Sol–Gel Processing; Academic Press: Cambridge, MA, USA, 1990; ISBN 978-970-908-057103-057104. [Google Scholar]

- Jousseaume, V.; Zenasni, A.; Gourhant, O.; Favennec, L.; Baklanov, M. Ultra-Low-k by CVD: Deposition and Curing. In Advanced Interconnects for ULSI Technology; John Wiley and Sons: Hoboken, NJ, USA, 2012; pp. 35–77. [Google Scholar]

- Jousseaume, V.; Cornec, C.; Ciaramella, F.; Favennec, L.; Zenasni, A.; Simon, G.; Simon, J.; Gerbaud, G.; Passemard, G. PECVD Versus Spin-on to Perform Porous ULK for Advanced Interconnects: Chemical Composition, Porosity and Mechanical Behavior. MRS Proc. 2006, 914, 1–6. [Google Scholar] [CrossRef]

- Stanly Wolf, R.N.T. Silicon Processing for the VLSI Era. In Process Technology, 1st ed.; Lattice Press: Sunset Beach, CA, USA, 1986; Volume 1, ISBN -10. [Google Scholar]

- Adams, A.C. Dielectric and Polysilicon Film Deposition; VLSI Technology: San Jose, CA, USA, 1983; p. 93. [Google Scholar]

- Sivaram, S. Chemical Vapor Deposition: Thermal and Plasma Deposition of Electronic Materials; Springer Science & Business Media: Berlin/Heidelberg, Germany, 1995; ISBN 978-971-4757-4751-4755. [Google Scholar]

- Grill, A.; Edelstein, D.; Lane, M.; Patel, V.; Gates, S.; Restaino, D.; Molis, S. Interface engineering for high interfacial strength between SiCOH and porous SiCOH interconnect dielectrics and diffusion caps. J. Appl. Phys. 2008, 103, 054104. [Google Scholar] [CrossRef]

- Edelstein, D.; Demos, A.; Gates, S.M.; Grill, A.; Molis, S.E.; Nguyen, V.N.T.; Reiter, S.; Restaino, D.D.; Yim, K.S. Structure and Method for Porous SiCOH Dielectric Layers and Adhesion Promoting or Etch Stop Layers Having Increased Interfacial and Mechanical Strength. U.S. Patent 7,615,482, 10 September 2009. [Google Scholar]

- Xie, B.; Demos, A.T.; Raj, D.; Ngo, S.; Yim, K.S. Microelectronic Structure Including a Low k Dielectric and a Method of Controlling Carbon Distribution in the Structure. U.S. Patent 8,349,746, 23 February 2010. [Google Scholar]

- Gambino, J. Process Technology for Copper Interconnects. In Handbook of Thin Film Deposition; William Andrew Publishing: Amsterdam, The Netherlands, 2012; pp. 221–269. [Google Scholar]

- Chylak, B.; Keller, F.; Levine, L. Probing wire bond issues for bonding over Cu/low-K dielectric materials. Solid State Technol. 2004, pp. 1–7. Available online: http://www.processsolutionsconsulting.com/pdf/LowK/K&S_LowK_finrevc.pdf (accessed on 7 July 2021).

- Jahl, M.J.; Carson, D.W.; Riahi, S.; Vrtis, R.N. Deposition of Titanium Amides. U.S. Patent 6,602,783, 17 April 2003. [Google Scholar]

- Marxsen, G.; Merbeth, T.; Nopper, M.; Ortleb, T.; Lehr, M.U.; Roessler, T. Major Influences of Shaping and Profiling of Cu ECP and CMP on Feature Level. In Proceedings of the International Conference on Planarization/CMP Technology, Dresden, Germany, 25–27 October 2007; pp. 1–6. [Google Scholar]

- Yoo, H.; Chang, E.; Kim, N. A Study on the Optimized Copper Electrochemical Plating in Dual Damascene Process. Trans. Electr. Electron. Mater. 2005, 6, 225–228. [Google Scholar] [CrossRef]

- Krishnan, M.; Nalaskowski, J.W.; Cook, L.M. Chemical Mechanical Planarization: Slurry Chemistry, Materials, and Mechanisms. Chem. Rev. 2010, 110, 178–204. [Google Scholar] [CrossRef] [PubMed]

- Cadien, K.C.; Nolan, L. 7-CMP Method and Practice. In Handbook of Thin Film Deposition, 3rd ed.; Seshan, K., Ed.; William Andrew Publishing: Oxford, UK, 2012; pp. 179–219. [Google Scholar]

- Noguchi, J.; Ohashi, N.; Jimbo, T.; Yamaguchi, H.; Takeda, K.I.; Hinode, K. Effect of NH3-plasma treatment and CMP modification on TDDB improvement in Cu metallization. IEEE Trans. Electron Devices 2001, 48, 1340–1345. [Google Scholar] [CrossRef]

- Lin, M.H.; Lin, Y.L.; Chen, J.M.; Yeh, M.; Chang, K.P.; Su, K.C.; Tahui, W. Electromigration lifetime improvement of copper interconnect by cap/dielectric interface treatment and geometrical design. IEEE Trans. Electron Devices 2005, 52, 2602–2608. [Google Scholar] [CrossRef]

- Worsley, M.; Bent, S.; Gates, S.; Fuller, N.; Volksen, W.; Steen, M.; Dalton, T. Effect of plasma interactions with low-films as a function of porosity, plasma chemistry, and temperature. J. Vac. Sci. Technol. B 2005, 23, 395–405. [Google Scholar] [CrossRef]

- Han, Q.; White, B.; Berry, I.; Waldfried, C.; Escorcia, O. Activated He:H2 Strip of Photoresist over Porous Low-k Materials. Solid State Phenom. 2005, 103–104, 341–344. [Google Scholar] [CrossRef]

- Brase, G.; Schroeder, U.P.; Holloway, K.L.; Infineon Technologies, A.G. ‘Via First’ Dual Damascene Process for Copper Metallization. U.S. Patent 6,576,550, 10 June 2003. [Google Scholar]

- Frot, T.; Volksen, W.; Purushothaman, S.; Bruce, R.; Magbitang, T.; Miller, D.; Deline, V.; Dubois, G. Post Porosity Plasma Protection: Scaling of Efficiency with Porosity. Adv. Funct. Mater. 2012, 22, 1–8. [Google Scholar] [CrossRef]

- Zhang, L.; de Marneffe, J.F.; Heyne, M.; Naumov, S.; Sun, Y.; Zotovich, A.; El Otell, Z.; Vajda, F.; De Gendt, S.; Baklanov, M. Improved Plasma Resistance for Porous Low-k Dielectrics by Pore Stuffing Approach. ECS J. Solid State Sci. Technol. 2015, 4, N3098. [Google Scholar] [CrossRef]

| Classification | Material | Fabrication | Dielectric Constant (k) |

|---|---|---|---|

| Silicon dioxide | SiO2 | CVD | 3.9–4.5 |

| Silsesquioxane-based | Hydrogen–Silsesquioxane (HSSQ) | Spin-on | 2.9–3.2 |

| Methyl–Silsesquioxane (MSSQ) | Spin-on | 2.6–2.8 | |

| Silica-based | FSG | CVD | 3.2–4.0 |

| SiCOH | CVD | 2.7–3.3 | |

| Porous | Porous HSSQ | Spin-on | 1.7–2.2 |

| Porous MSSQ | Spin-on | 1.8–2.2 | |

| Porous SiCOH | Spin-on/CVD | 1.5–2.5 | |

| Air gaps | Air | - | 1.0 |

| Molecule | Si–C:Si | Si–O:Si | Si–H:Si | Structure |

|---|---|---|---|---|

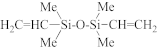

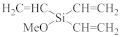

| DEMS | 1:1 | 2:1 | 1:1 |  |

| MTES | 1:1 | 3:1 | 1:1 |  |

| DMOMS | 1:1 | 2:1 | 1:1 |  |

| TOMCATS® | 1:1 | 1:1 | 1:1 |  |

| OMCTS | 2:1 | 1:1 | - |  |

| DMDOSH | 2:1 | 2:1 | - |  |

| DMDMOS | 2:1 | 2:1 | - |  |

| 3MS | 3:1 | - | 1:1 |  |

| Classification | DEMS | 3MS | DMDMOS |

|---|---|---|---|

| RF Power | 300 | 600 | 450 |

| Dielectric constant | 2.90 | 2.85 | 2.88 |

| Precursor flow rate | 1000 (mg/min) | 540 (sccm) | 1500 (mg/min) |

| He (sccm) | 150 | N/A | 500 |

| O2 (sccm) | 0 | 90 | 50 |

| CO2 (sccm) | 0 | N/A | N/A |

| N2O (SCCM) | N/A | N/A | 0 |

| Young’s modulus (GPa) | 16.5 | 8.76 | 6.68 |

| Hardness (GPa) | 2.8 | 1.44 | 1.2 |

| Name | Porogen Functional Group | Structure |

|---|---|---|

| vinylmethyldiethoxysilane | alkene group |  |

| vinyltriethoxysilane | alkene group |  |

| vinyldimethylethoxysilane | alkene group |  |

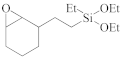

| cyclohexenylethyltriethoxysilane | cyclohexene group |  |

| 1,1-diethoxy-1–Silacyclopent-3-ene | silacyclopent-3-ene |  |

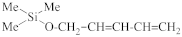

| divinyltetramethyldisiloxane | alkene group |  |

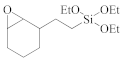

| 2-(3,4-epoxycyclohexyl) ethyltriethoxysilane | epoxy group |  |

| 2-(3,4-epoxycyclohexyl) ethyltrimethoxysilane | epoxy group |  |

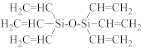

| hexavinyldisiloxane | alkene group |  |

| trivinylmethoxysilane | alkene group |  |

| Trimethylsilyloxy-acetylen | alkyne group |  |

| 1-(trimethylsiloxy)-1,3-butadiene | 1,3-butadiene |  |

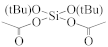

| di-t-butoxydiacetoxysilane | carboxyl group |  |

| Classification | DEMS + BCHD | DEMS + BCHD + TDMMS | Embedded Porogen | Embedded Porogen + TDMMS | |||||

|---|---|---|---|---|---|---|---|---|---|

| Batch code | V1.a | V1.b | V1.c | V2.a | V2.b | V2.c | V3 | V4.a | V4.b |

| k (@150 °C) | 2.53 | 2.4 | 2.2 | 2.56 | 2.35 | 2.2 | 2.46 | 2.53 | 2.42 |

| Breakdown voltage (MV/cm) | >7.3 | >6.0 | >6.5 | >6.0 | >7.0 | 7.0 | |||

| Elastic modulus (GPa) | 7.2 | 4.9 | 4.7 | 6.5 | 4.73 | 3.04 | 6.64 | 10.2 | 6.64 |

| Adhesion (J/cm2) | 4.5 | 4.4 | 3.9 | 4.4 | 3.9 | ||||

| Carbon percentage (%) | 15.7 | 15.5 | 20.6 | 23.2 | 35.0 | 21.1 | 16.3 | 17.4 | |

| Porosity (%) | 16.3 | 24.5 | 29 | 19 | 22 | 26.5 | 14.4 | 17.9 | 19.7 |

| Pore diameter (nm) | 1.2 | 1.2 | 2.4 | 1.2 | 1.2 | 1.32 | 1 | 1.1 | 1.3 |

| PID (ratio control) | 0.67 | 0.9 | 1 | 0.57 | 0.55 | ~0.5 | 0.57 | 0.49 | 0.65 |

| Molecule | Structure | As Deposited after 390 °C | Anneal under N2 | ||

|---|---|---|---|---|---|

| Matrix %/Porogen % | k (Hg 25 °C) | Matrix %/Porogen % | k (Hg 25 °C) | ||

| 1-Hexene |  | 82/18 | 2.8 | 92/8 | 2.3 |

| Hexadiene |  | 69/31 | 2.8 | 91/9 | 2.4 |

| Cyclohexene oxide |  | 75/25 | 2.6 | 89/11 | 2.2 |

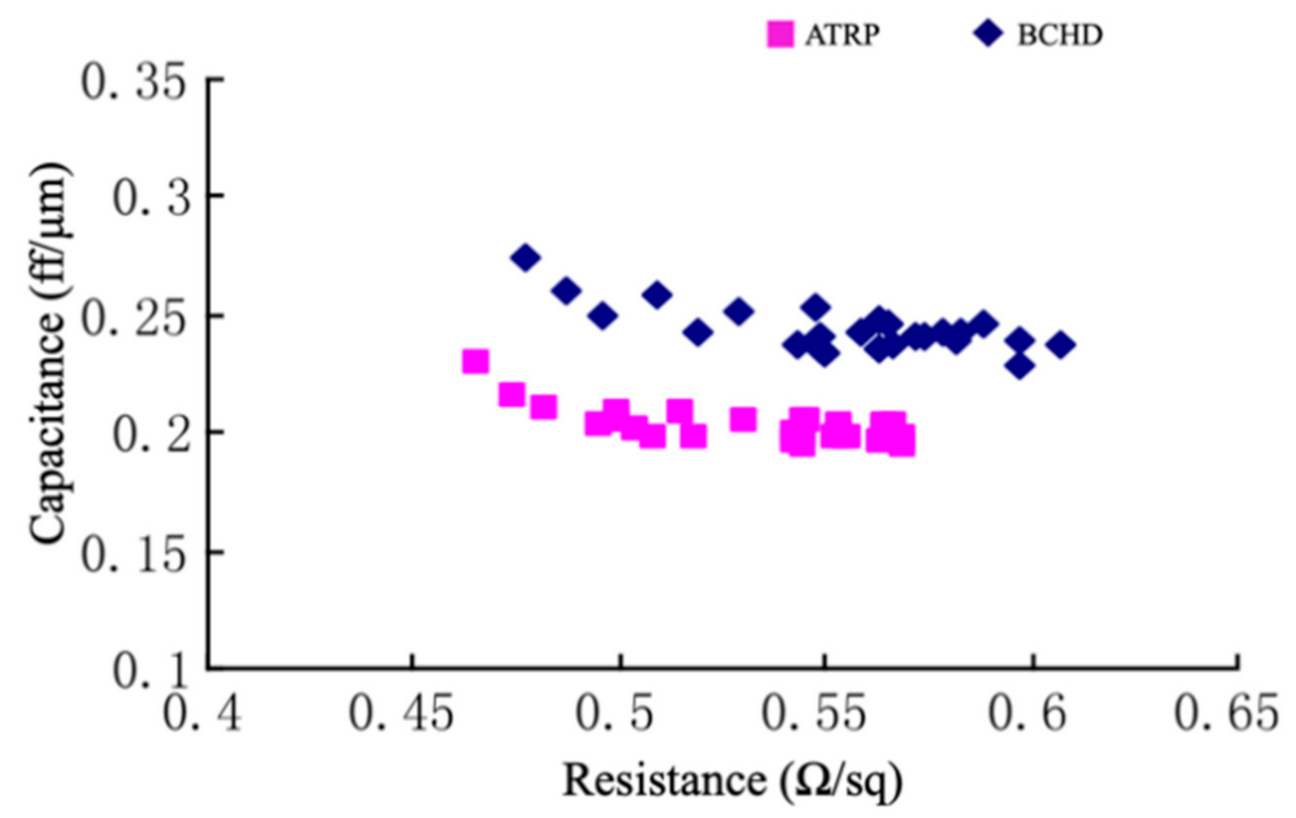

| pULK Performance (I) | |||||||

| Porogen | Thickness (Å) | Uniformity (1 Sigma%) | Stress (MPa) | Shrinkage (%) | Shrinkage Uniformity | k Value | Refractive Index |

| BCHD | 4930 | 1.4 | 50 | 17.2 | 3.44 | 2.48 | 1.355 |

| ATRP | 4920 | 1.3 | 60 | 15.4 | 3.40 | 2.59 | 1.335 |

| pULK Performance (II) | |||||||

| Porogen | Pore Size (Å) | Porosity (%) | Hardness (GPa) | Young’s Modulus (GPa) | Adhesion (J/m2) | Deposition Rate (Å/min) | SiCH3/SiO (Area) |

| BCHD | 11.8 | 25 | 0.7 | 5.1 | 5.4 | 6000 | 3.6 |

| ATRP | 9.5 | 23 | 1.0 | 7.1 | 5.9 | 4000 | 2.6 |

| Samples | Surface Layer Thickness Measured by Ellipsometry (nm) | Surface Layer Permeability Coefficient (mol m−1 s−1 Pa−1) |

|---|---|---|

| Low-k | N/A | N/A |

| Low-k + He | 9 ± 1 | 5 × 10−17 |

| Low-k + NH3/N2 | 6 ± 1 | 9 × 10−17 |

| Low-k + etch + ash | 9 ± 1 | 7 × 10−20 |

| Low-k + NH3 | 8 ± 1 | 8 × 10−21 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hong, N.; Zhang, Y.; Sun, Q.; Fan, W.; Li, M.; Xie, M.; Fu, W. The Evolution of Organosilicon Precursors for Low-k Interlayer Dielectric Fabrication Driven by Integration Challenges. Materials 2021, 14, 4827. https://doi.org/10.3390/ma14174827

Hong N, Zhang Y, Sun Q, Fan W, Li M, Xie M, Fu W. The Evolution of Organosilicon Precursors for Low-k Interlayer Dielectric Fabrication Driven by Integration Challenges. Materials. 2021; 14(17):4827. https://doi.org/10.3390/ma14174827

Chicago/Turabian StyleHong, Nianmin, Yinong Zhang, Quan Sun, Wenjie Fan, Menglu Li, Meng Xie, and Wenxin Fu. 2021. "The Evolution of Organosilicon Precursors for Low-k Interlayer Dielectric Fabrication Driven by Integration Challenges" Materials 14, no. 17: 4827. https://doi.org/10.3390/ma14174827

APA StyleHong, N., Zhang, Y., Sun, Q., Fan, W., Li, M., Xie, M., & Fu, W. (2021). The Evolution of Organosilicon Precursors for Low-k Interlayer Dielectric Fabrication Driven by Integration Challenges. Materials, 14(17), 4827. https://doi.org/10.3390/ma14174827