A Multi-Method Simulation Toolbox to Study Performance and Variability of Nanowire FETs

Abstract

1. Introduction

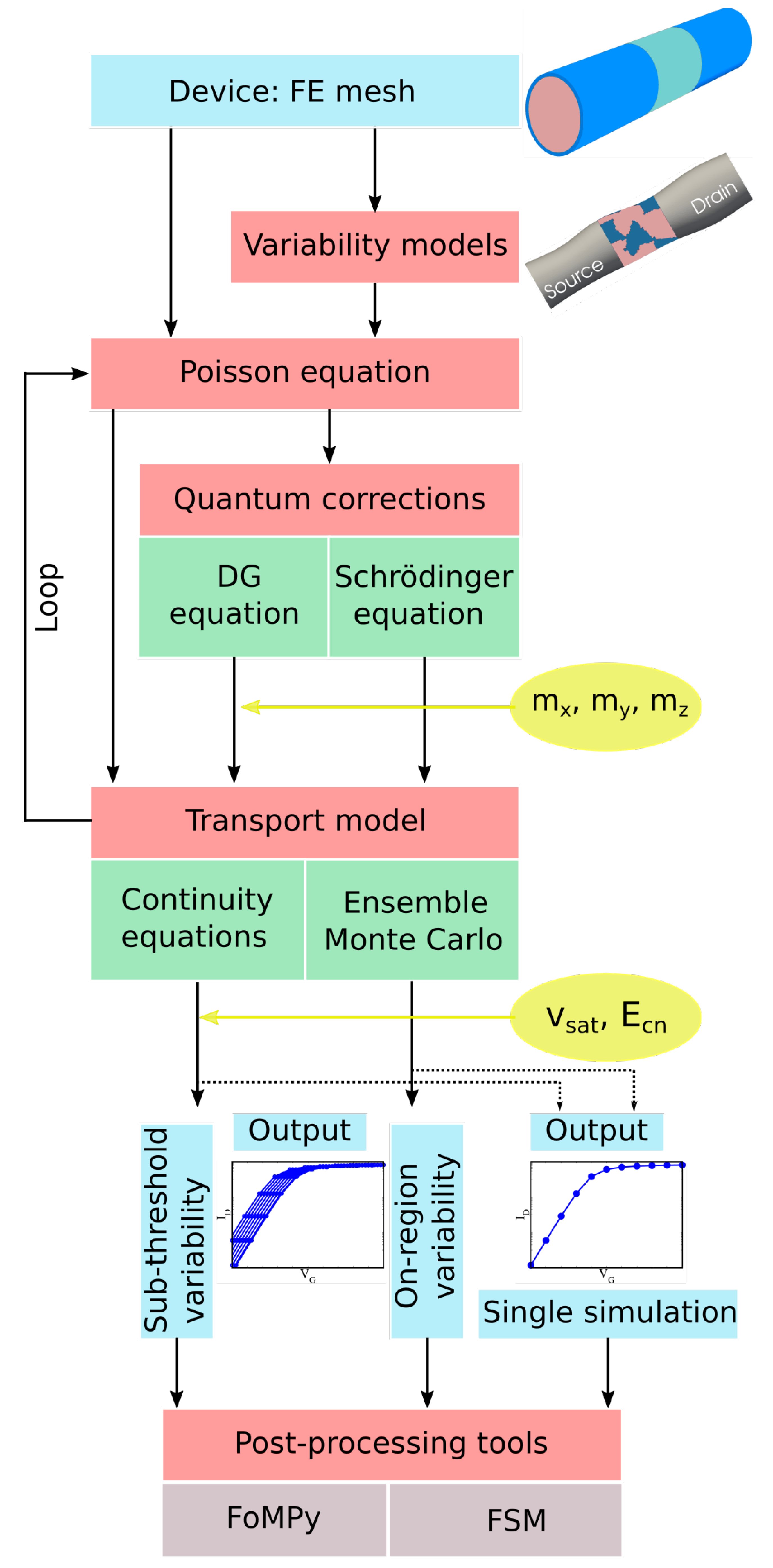

2. Simulation Framework

3. Performance and Variability of GAA-NW FETs

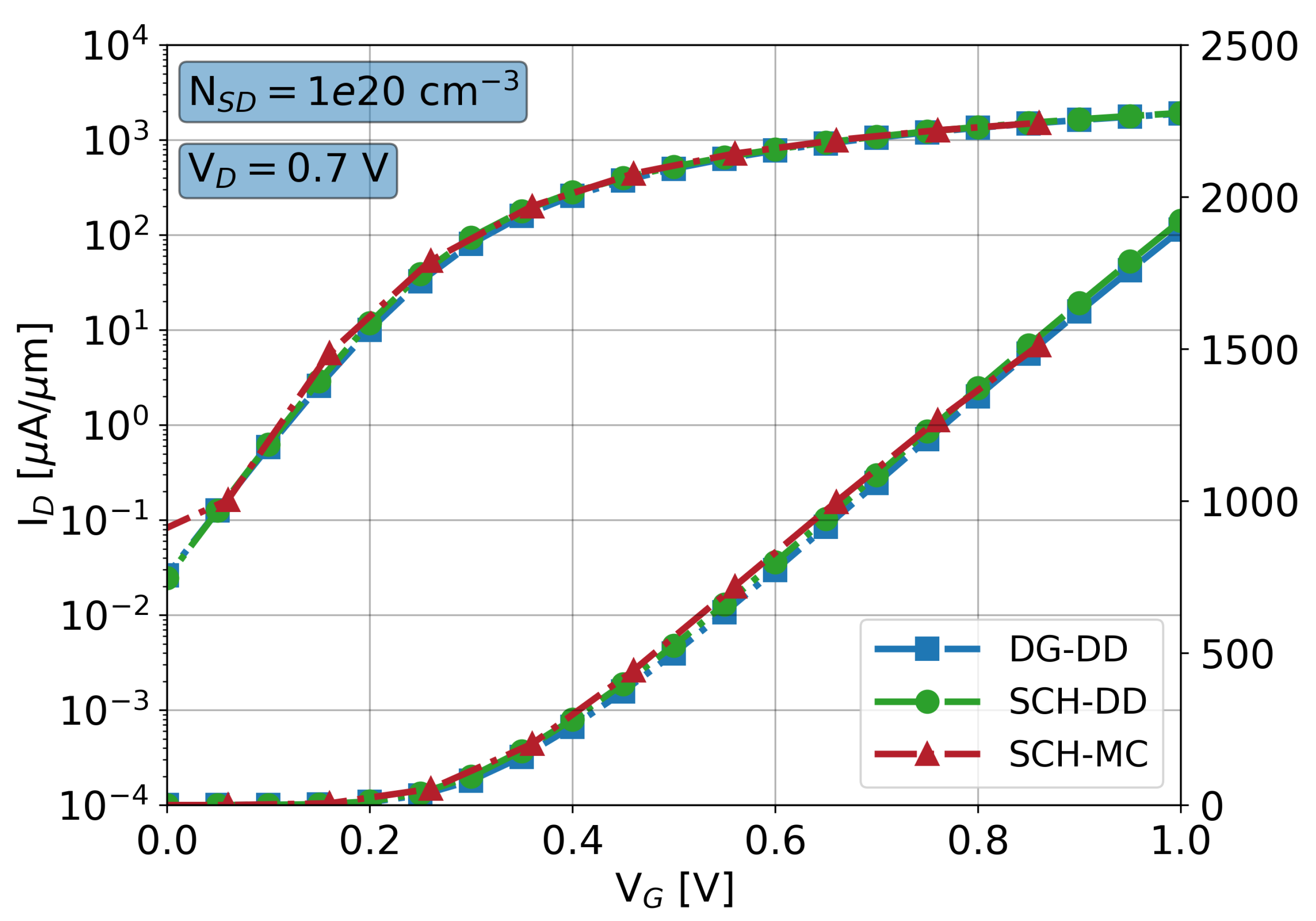

3.1. Benchmark Device

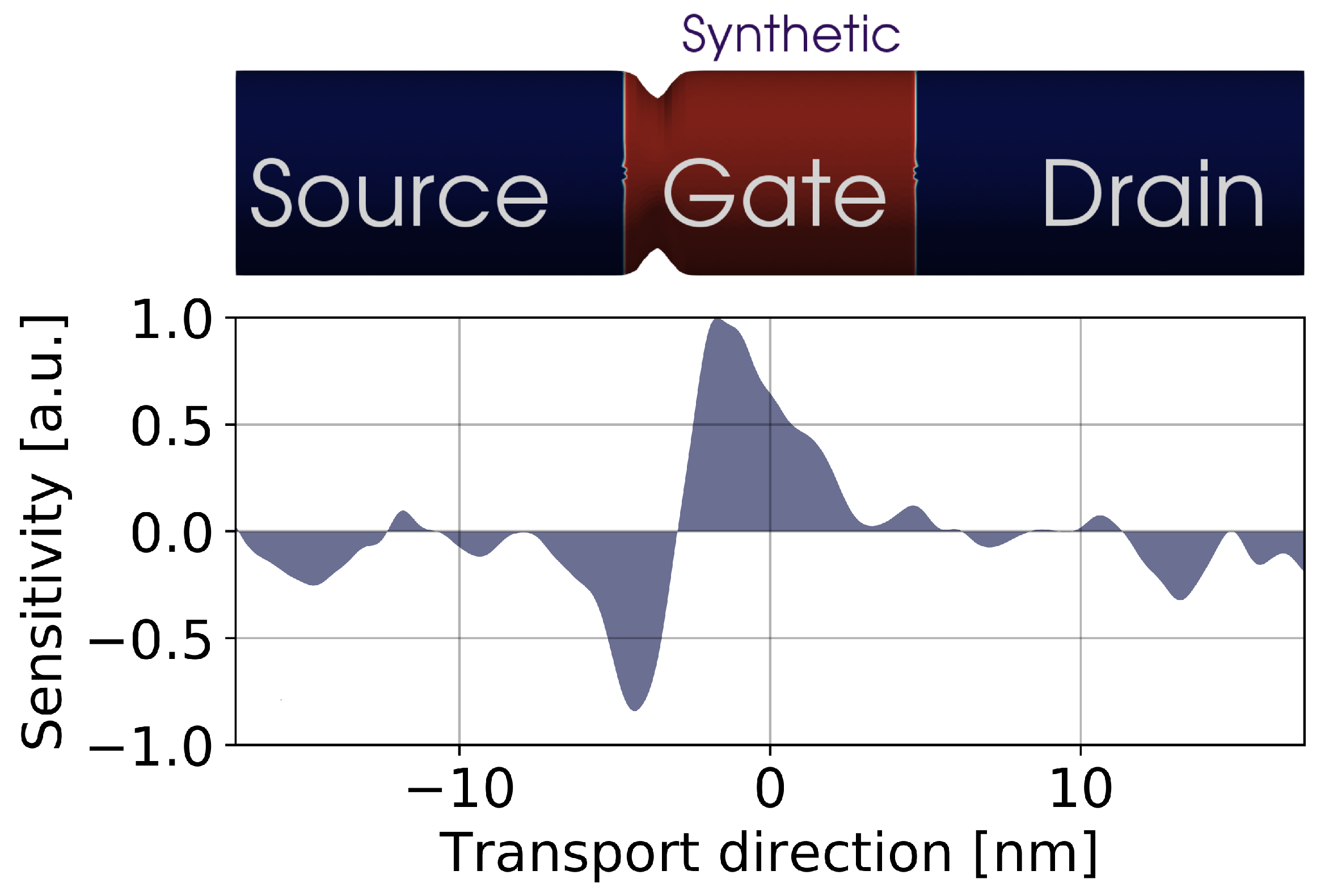

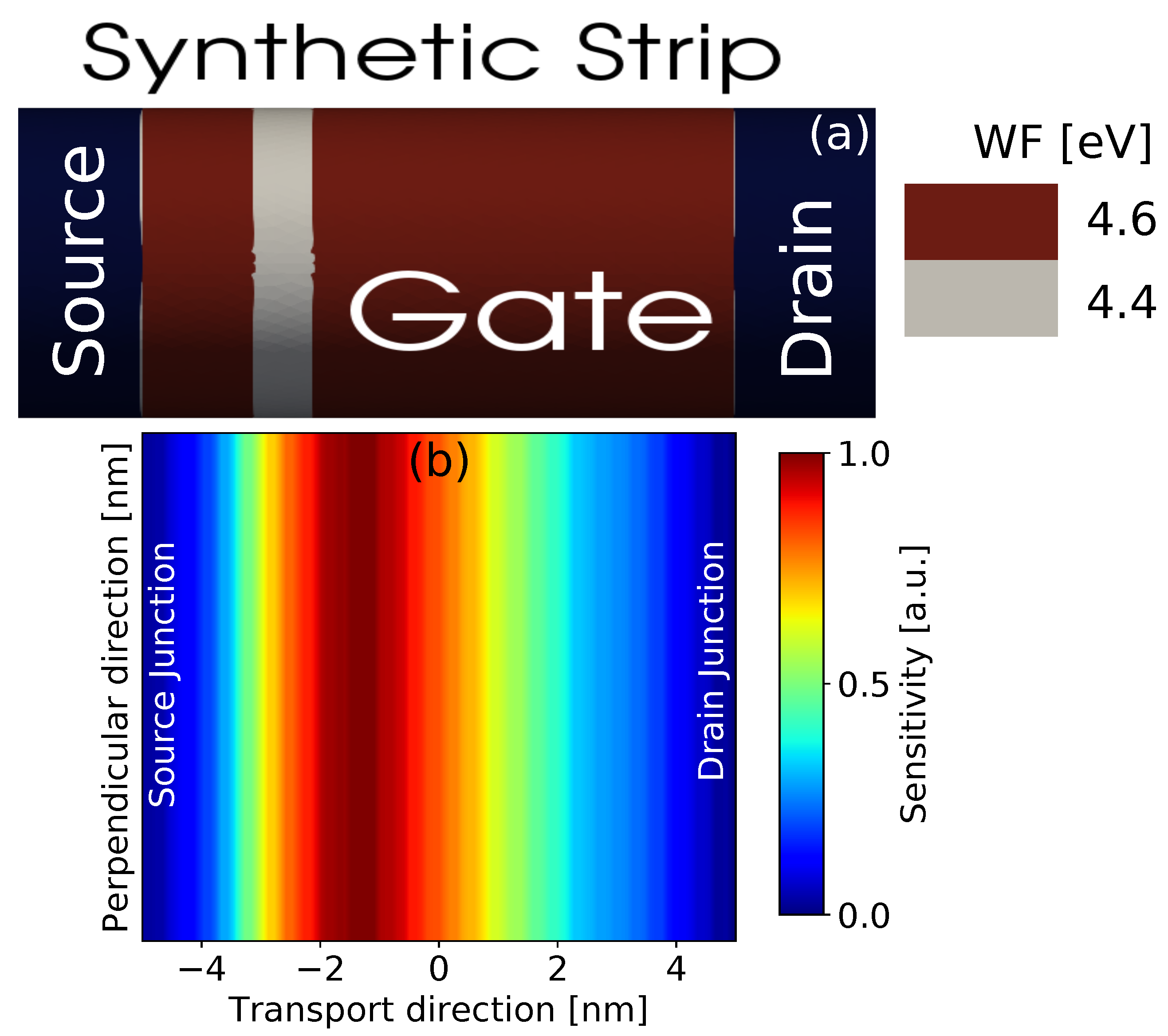

3.2. Variability Models

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Abbreviations

| DD | Drift diffusion |

| DG | Density gradient |

| FE | Finite-element |

| FinFET | Fin field effect transistor |

| FSM | Fluctuation sensitivity map |

| GAA-NW FET | Gate-all-around nanowire field effect transistor |

| GER | Gate edge roughness |

| KPFM | Kelvin probe force microscopy |

| LER | Line edge roughness |

| MC | Monte Carlo |

| MGG | Metal grain granularity |

| RD | Random discrete dopants |

References

- Badami, O.; Driussi, F.; Palestri, P.; Selmi, L.; Esseni, D. Performance comparison for FinFETs, nanowire and stacked nanowires FETs: Focus on the influence of surface roughness and thermal effects. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 13.2.1–13.2.4. [Google Scholar] [CrossRef]

- Yoon, J.S.; Rim, T.; Kim, J.; Meyyappan, M.; Baek, C.K.; Jeong, Y.H. Vertical gate-all-around junctionless nanowire transistors with asymmetric diameters and underlap lengths. J. Appl. Phys. 2014, 105, 102105. [Google Scholar] [CrossRef]

- Mikolajick, T.; Heinzig, A.; Trommer, J.; Pregl, S.; Grube, M.; Cuniberti, G.; Weber, W. Silicon nanowires—A versatile technology platform. Phys. Status Solidi Rapid Res. Lett. 2013, 7, 793–799. [Google Scholar] [CrossRef]

- IEEE International Roadmap for Devices and Systems (IRDS), More Moore. 2017. Available online: https://irds.ieee.org/roadmap-2017 (accessed on 24 July 2019).

- Wang, X.; Brown, A.R.; Cheng, B.; Asenov, A. Statistical variability and reliability in nanoscale FinFETs. In Proceedings of the 2011 International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 5.4.1–5.4.4. [Google Scholar] [CrossRef]

- Nagy, D.; Indalecio, G.; García-Loureiro, A.J.; Elmessary, M.A.; Kalna, K.; Seoane, N. FinFET Versus Gate-All-Around Nanowire FET: Performance, Scaling, and Variability. IEEE J. Electron Devices Soc. 2018, 6, 332–340. [Google Scholar] [CrossRef]

- Espiñeira, G.; Nagy, D.; Indalecio, G.; García-Loureiro, A.J.; Kalna, K.; Seoane, N. Impact of Gate Edge Roughness Variability on FinFET and Gate-All-Around Nanowire FET. IEEE Electron Device Lett. 2019, 40, 510–513. [Google Scholar] [CrossRef]

- Vasileska, D.; Goodnick, S.M.; Klimeck, G. Computational Electronics: Semiclassical and Quantum Device Modeling and Simulation; CRC Press: Boca Raton, FL, USA, 2010. [Google Scholar]

- Asenov, A.; Cheng, B.; Wang, X.; Brown, A.R.; Millar, C.; Alexander, C.; Amoroso, S.M.; Kuang, J.B.; Nassif, S.R. Variability Aware Simulation Based Design—Technology Cooptimization (DTCO) Flow in 14 nm FinFET/SRAM Cooptimization. IEEE Trans. Electron Devices 2015, 62, 1682–1690. [Google Scholar] [CrossRef]

- Selberherr, S. Simulation of Semiconductor Devices and Processes; Springer: Wien, Vienna; New York, NY, USA, 1993. [Google Scholar]

- Fang, J.; Vandenberghe, W.; Fu, B.; Fischetti, M. Pseudopotential-based electron quantum transport: Theoretical formulation and application to nanometer-scale silicon nanowire transistors. J. Appl. Phys. 2016, 119, 035701. [Google Scholar] [CrossRef]

- Datta, S. Nanoscale device modeling: The Green’s function method. Superlattices Microstruct. 2000, 28, 253–278. [Google Scholar] [CrossRef]

- Luisier, M.; Klimeck, G. Atomistic full-band simulations of silicon nanowire transistors: Effects of electron-phonon scattering. Phys. Rev. B 2009, 80, 155430. [Google Scholar] [CrossRef]

- Bangsaruntip, S.; Balakrishnan, K.; Cheng, S.L.; Chang, J.; Brink, M.; Lauer, I.; Bruce, R.L.; Engelmann, S.U.; Pyzyna, A.; Cohen, G.M.; et al. Density scaling with gate-all-around silicon nanowire MOSFETs for the 10 nm node and beyond. In Proceedings of the IEEE Electron Devices Meeting (IEDM), Washington, DC, USA, 9–11 December 2013; pp. 20.2.1–20.2.4. [Google Scholar] [CrossRef]

- Geuzaine, C.; Remacle, J.F. Gmsh: A three-dimensional finite element mesh generator with built-in pre- and post-processing facilities. Int. J. Numer. Meth. Eng. 2009, 79, 1309–1331. [Google Scholar] [CrossRef]

- Elmessary, M.A.; Nagy, D.; Aldegunde, M.; Seoane, N.; Indalecio, G.; Lindberg, J.; Dettmer, W.; Perić, D.; García-Loureiro, A.J.; Kalna, K. Scaling/LER study of Si GAA nanowire FET using 3D finite element Monte Carlo simulations. Solid-State Electron. 2017, 128, 17–24, Extended papers selected from EUROSOI-ULIS 2016. [Google Scholar] [CrossRef]

- Garcia-Loureiro, A.J.; Seoane, N.; Aldegunde, M.; Valin, R.; Asenov, A.; Martinez, A.; Kalna, K. Implementation of the Density Gradient Quantum Corrections for 3-D Simulations of Multigate Nanoscaled Transistors. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2011, 30, 841–851. [Google Scholar] [CrossRef]

- Ancona, M.G.; Yu, Z.; Dutton, R.W.; Voorde, P.J.V.; Cao, M.; Vook, D. Density-Gradient Analysis of MOS Tunneling. IEEE Trans. Electron Devices 2000, 47, 2310–2319. [Google Scholar] [CrossRef]

- Asenov, A.; Watling, J.R.; Brown, A.R.; Ferry, D.K. The Use of Quantum Potentials for Confinement and Tunnelling in Semiconductor Devices. J. Comput. Electron. 2002, 1, 503–513. [Google Scholar] [CrossRef]

- Seoane, N.; Indalecio, G.; Comesana, E.; Aldegunde, M.; García-Loureiro, A.J.; Kalna, K. Random Dopant, Line-Edge Roughness, and Gate Workfunction Variability in a Nano InGaAs FinFET. IEEE Trans. Electron Devices 2014, 61, 466–472. [Google Scholar] [CrossRef]

- Kovac, U.; Alexander, C.; Roy, G.; Riddet, C.; Cheng, B.; Asenov, A. Hierarchical Simulation of Statistical Variability: From 3-D MC With ab initio Ionized Impurity Scattering to Statistical Compact Models. IEEE Trans. Electron Devices 2010, 57, 2418–2426. [Google Scholar] [CrossRef]

- Winstead, B.; Ravaioli, U. A quantum correction based on Schrodinger equation applied to Monte Carlo device simulation. IEEE Trans. Electron Devices 2003, 50, 440–446. [Google Scholar] [CrossRef]

- Lindberg, J.; Aldegunde, M.; Nagy, D.; Dettmer, W.G.; Kalna, K.; García-Loureiro, A.J.; Perić, D. Quantum Corrections Based on the 2-D Schrödinger Equation for 3-D Finite Element Monte Carlo Simulations of Nanoscaled FinFETs. IEEE Trans. Electron Devices 2014, 61, 423–429. [Google Scholar] [CrossRef]

- Elmessary, M.A.; Nagy, D.; Aldegunde, M.; Lindberg, J.; Dettmer, W.G.; Perić, D.; García-Loureiro, A.J.; Kalna, K. Anisotropic Quantum Corrections for 3-D Finite-Element Monte Carlo Simulations of Nanoscale Multigate Transistors. IEEE Trans. Electron Devices 2016, 63, 933–939. [Google Scholar] [CrossRef][Green Version]

- Assad, F.; Banoo, K.; Lundstrom, M. The drift-diffusion equation revisited. Solid-State Electron. 1997, 42, 283–295. [Google Scholar] [CrossRef]

- Caughey, D.M.; Thomas, R.E. Carrier Mobilities in Silicon Empirically Related to Doping and Field. Proc. IEEE 1967, 55, 2192–2193. [Google Scholar] [CrossRef]

- Yamaguchi, K. Field-dependent mobility model for two-dimensional numerical analysis of MOSFET’s. IEEE Trans. Electron Devices 1979, 26, 1068–1074. [Google Scholar] [CrossRef]

- Jacoboni, C.; Lugli, P. The Monte Carlo Method for Semiconductor Device Simulation; Computational Microelectronics; Springer: Vienna, Austria, 2012. [Google Scholar]

- Aldegunde, M.; García-Loureiro, A.J.; Kalna, K. 3D Finite Element Monte Carlo Simulations of Multigate Nanoscale Transistors. IEEE Trans. Electron Devices 2013, 60, 1561–1567. [Google Scholar] [CrossRef]

- Tomizawa, K. Numerical Simulation of Submicron Semiconductor Devices; Artech House Materials Science Library, Artech House: Boston, MA, USA, 1993. [Google Scholar]

- Ridley, B.K. Reconciliation of the Conwell-Weisskopf and Brooks-Herring formulae for charged-impurity scattering in semiconductors: Third-body interference. J. Phys. C Solid State Phys. 1977, 10, 1589. [Google Scholar] [CrossRef]

- De Roer, T.G.V.; Widdershoven, F.P. Ionized impurity scattering in Monte Carlo calculations. J. Appl. Phys. 1986, 59, 813–815. [Google Scholar] [CrossRef]

- Ferry, D. Semiconductor Transport; Taylor & Francis: London, UK, 2000. [Google Scholar]

- Islam, A.; Kalna, K. Monte Carlo simulations of mobility in doped GaAs using self-consistent Fermi–Dirac statistics. Semicond. Sci. Technol. 2012, 26, 039501. [Google Scholar] [CrossRef][Green Version]

- International Technology Roadmap for Semiconductors (ITRS). 2016. Available online: http://www.itrs2.net/ (accessed on 24 July 2019).

- Espiñeira, G.; Seoane, N.; Nagy, D.; Indalecio, G.; García-Loureiro, A.J. FoMPy: A figure of merit extraction tool for semiconductor device simulations. In Proceedings of the 2018 Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon (EUROSOI-ULIS), Granada, Spain, 19–21 March 2018. [Google Scholar] [CrossRef]

- Espiñeira, G.; Nagy, D.; García-Loureiro, A.J.; Seoane, N.; Indalecio, G. Impact of threshold voltage extraction methods on semiconductor device variability. Solid-State Electron. 2019, 159, 165–170. [Google Scholar] [CrossRef]

- Nagy, D.; Indalecio, G.; García-Loureiro, A.J.; Espiñeira, G.; Elmessary, M.A.; Kalna, K.; Seoane, N. Drift-Diffusion Versus Monte Carlo Simulated ON-Current Variability in Nanowire FETs. IEEE Access 2019, 7, 12790–12797. [Google Scholar] [CrossRef]

- Indalecio, G.; Aldegunde, M.; Seoane, N.; Kalna, K.; García-Loureiro, A.J. Statistical study of the influence of LER and MGG in SOI MOSFET. Semicond. Sci. Technol. 2014, 29, 045005. [Google Scholar] [CrossRef]

- Seoane, N.; Indalecio, G.; Nagy, D.; Kalna, K.; García-Loureiro, A.J. Impact of Cross-Sectional Shape on 10-nm Gate Length InGaAs FinFET Performance and Variability. IEEE Trans. Electron Devices 2018, 65, 456–462. [Google Scholar] [CrossRef]

- Wang, R.; Zhuge, J.; Huang, R.; Yu, T.; Zou, J.; Kim, D.W.; Park, D.; Wang, Y. Investigation on Variability in Metal-Gate Si Nanowire MOSFETs: Analysis of Variation Sources and Experimental Characterization. IEEE Trans. Electron Devices 2011, 58, 2317–2325. [Google Scholar] [CrossRef]

- Ruiz, A.; Seoane, N.; Claramunt, S.; García-Loureiro, A.; Porti, M.; Couso, C.; Martin-Martinez, J.; Nafria, M. Workfunction fluctuations in polycrystalline TiN observed with KPFM and their impact on MOSFETs variability. Appl. Phy. Lett. 2019, 114, 093502. [Google Scholar] [CrossRef]

- Indalecio, G.; García-Loureiro, A.J.; Iglesias, N.S.; Kalna, K. Study of Metal-Gate Work-Function Variation Using Voronoi Cells: Comparison of Rayleigh and Gamma Distributions. IEEE Trans. Electron Devices 2016, 63, 2625–2628. [Google Scholar] [CrossRef]

- Asenov, A.; Brown, A.R.; Roy, G.; Cheng, B.; Alexander, C.; Riddet, C.; Kovac, U.; Martinez, A.; Seoane, N.; Roy, S. Simulation of statistical variability in nano-CMOS transistors using drift-diffusion, Monte Carlo and non-equilibrium Green’s function techniques. J. Comput. Electron. 2009, 8, 349–373. [Google Scholar] [CrossRef]

- Asenov, A.; Kaya, S.; Brown, A.R. Intrinsic parameter fluctuations in decananometer MOSFETs introduced by gate line edge roughness. IEEE Trans. Electron Devices 2003, 50, 1254–1260. [Google Scholar] [CrossRef]

- Seoane, N.; García-Loureiro, A.J.; Aldegund, M. Optimisation of linear systems for 3D parallel simulation of semiconductor devices: Application to statistical studies. Int. J. Numer. Model. Electron. Netw. Devices Fields 2009, 22, 235–258. [Google Scholar] [CrossRef]

- Indalecio, G.; Seoane, N.; Kalna, K.; García-Loureiro, A.J. Fluctuation Sensitivity Map: A Novel Technique to Characterise and Predict Device Behaviour Under Metal Grain Work-Function Variability Effects. IEEE Trans. Electron Devices 2017, 64, 1695–1701. [Google Scholar] [CrossRef]

- Indalecio, G.; García-Loureiro, A.J.; Elmessary, M.A.; Kalna, K.; Seoane, N. Spatial Sensitivity of Silicon GAA Nanowire FETs Under Line Edge Roughness Variations. IEEE J. Electron Devices Soc. 2018, 6, 601–610. [Google Scholar] [CrossRef]

| Dimensions | Gate length (L) (nm) | |

| Source and drain (S/D) length (L) (nm) | ||

| Channel width (W) (nm) | ||

| Channel height (H) (nm) | ||

| Equivalent oxide thickness (EOT) (nm) | ||

| Doping values | S/D n-type doping (N) (cm) | |

| S/D doping lateral straggle () | ||

| S/D doping lateral peak (x) (nm) | ||

| Figures of merit | Subthreshold slope () (mV/dec) | |

| Threshold voltage () (V) | ||

| Off-current () (A/m) | ||

| On-current () (A/m) | 1770 | |

| ratio | ||

| Calibration parameters | Saturation velocity () (cm/s) | |

| Perpendicular critical electric field ( | ||

| DG electron mass in the transport direction ( | ||

| DG electron masses in the confinement direction ( |

| Simulation Method | AMD Time (hh:mm) | Intel Time (hh:mm) |

|---|---|---|

| DD | 00:28 | 00:08 |

| DG-DD | 01:02 | 00:20 |

| SCH-DD | 00:55 | 00:16 |

| SCH-MC | 70:00 | 35:00 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Seoane, N.; Nagy, D.; Indalecio, G.; Espiñeira, G.; Kalna, K.; García-Loureiro, A. A Multi-Method Simulation Toolbox to Study Performance and Variability of Nanowire FETs. Materials 2019, 12, 2391. https://doi.org/10.3390/ma12152391

Seoane N, Nagy D, Indalecio G, Espiñeira G, Kalna K, García-Loureiro A. A Multi-Method Simulation Toolbox to Study Performance and Variability of Nanowire FETs. Materials. 2019; 12(15):2391. https://doi.org/10.3390/ma12152391

Chicago/Turabian StyleSeoane, Natalia, Daniel Nagy, Guillermo Indalecio, Gabriel Espiñeira, Karol Kalna, and Antonio García-Loureiro. 2019. "A Multi-Method Simulation Toolbox to Study Performance and Variability of Nanowire FETs" Materials 12, no. 15: 2391. https://doi.org/10.3390/ma12152391

APA StyleSeoane, N., Nagy, D., Indalecio, G., Espiñeira, G., Kalna, K., & García-Loureiro, A. (2019). A Multi-Method Simulation Toolbox to Study Performance and Variability of Nanowire FETs. Materials, 12(15), 2391. https://doi.org/10.3390/ma12152391