Characteristic Fluctuations of Dynamic Power Delay Induced by Random Nanosized Titanium Nitride Grains and the Aspect Ratio Effect of Gate-All-Around Nanowire CMOS Devices and Circuits

Abstract

1. Introduction

2. Statistical LWKF and AR Simulation Techniques

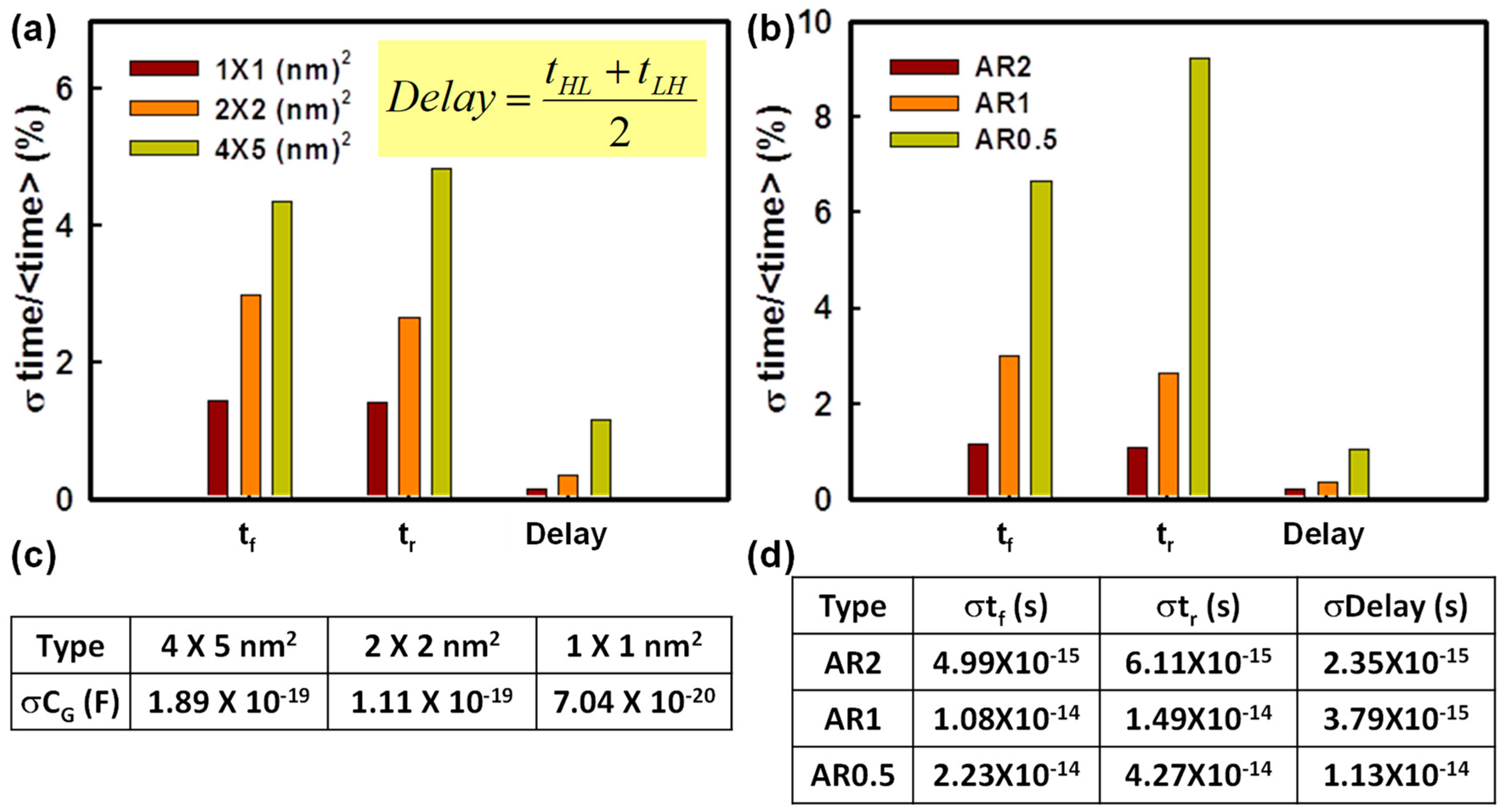

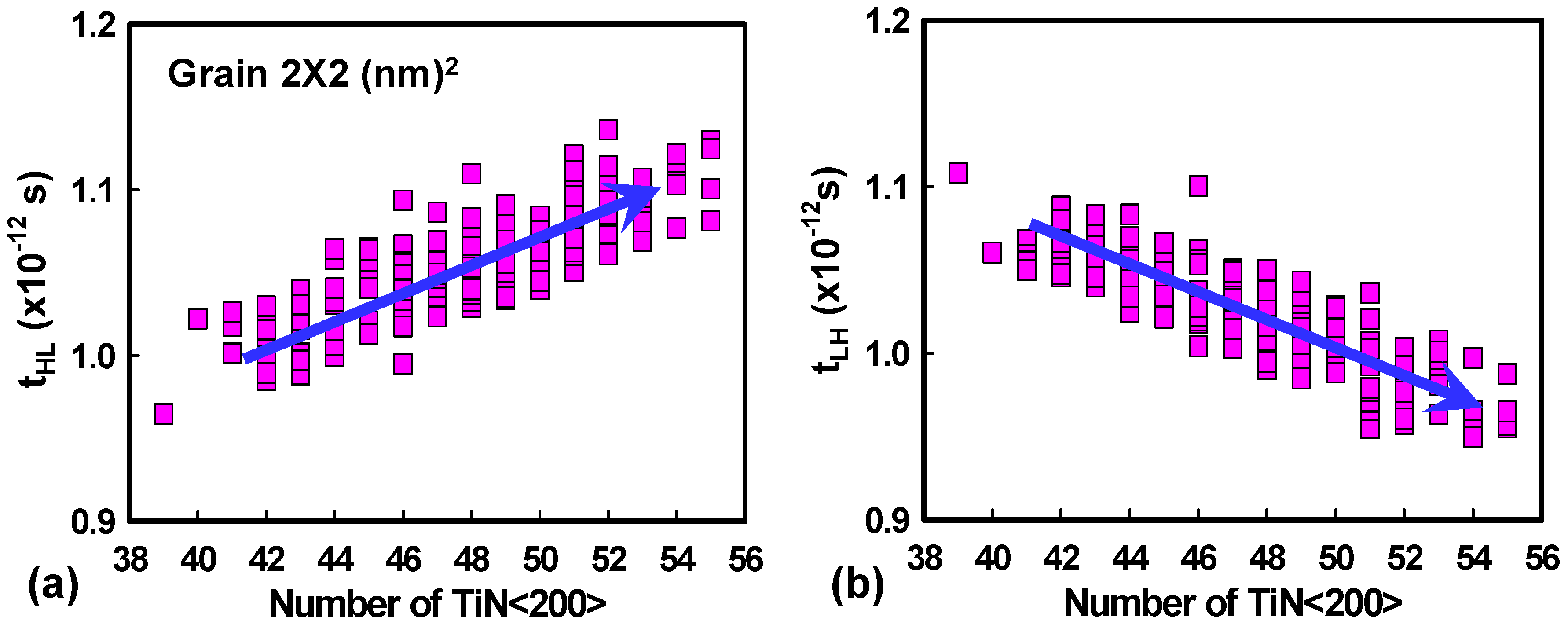

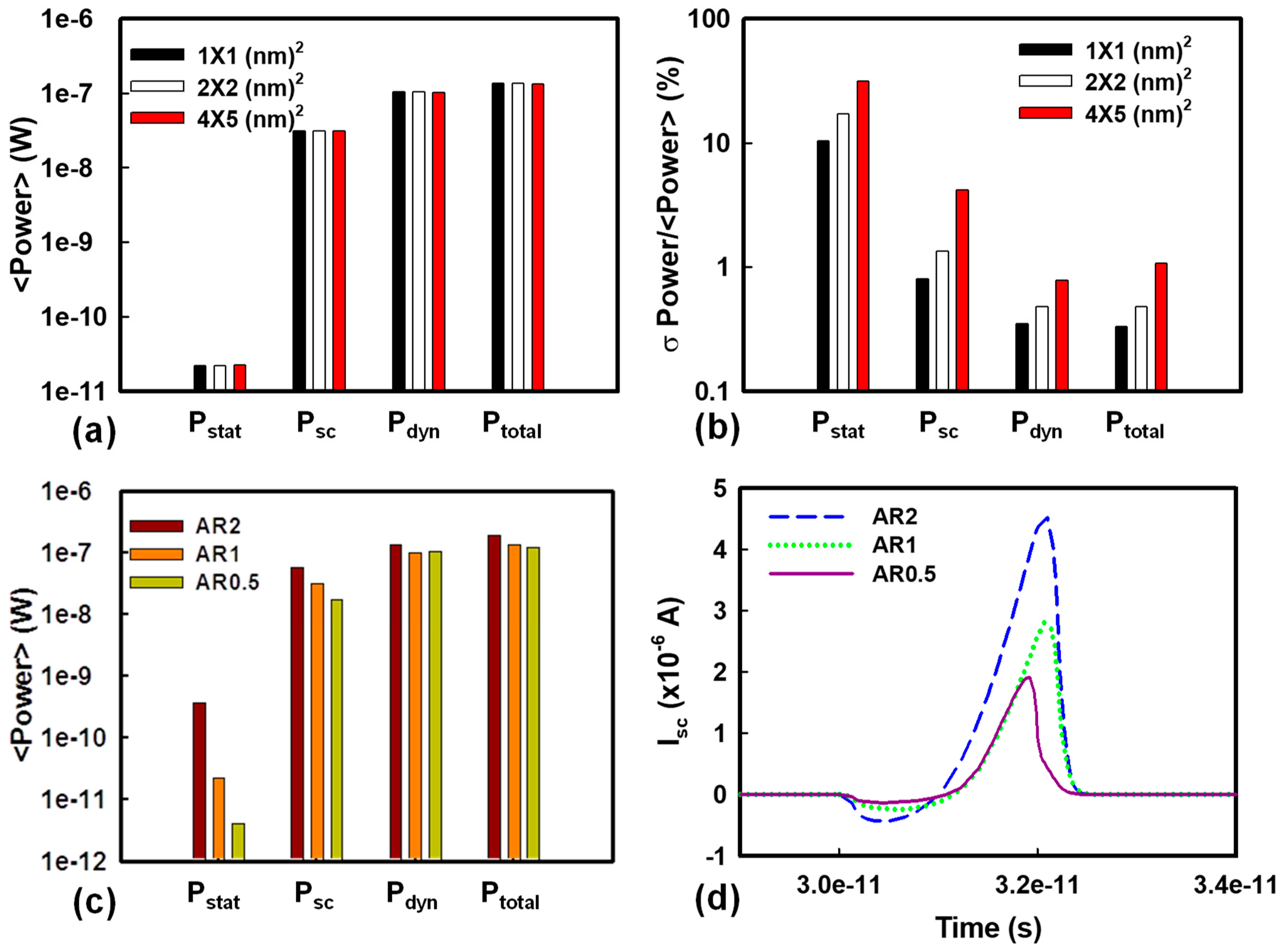

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Li, Y.; Chang, H.-T.; Lai, C.-N.; Chao, P.-J.; Chen, C.-Y. Process Variation Effect, Metal-Gate Work-Function Fluctuation and Random Dopant Fluctuation of 10-nm Gate-All-Around Silicon Nanowire MOSFET Devices. In Proceedings of the Technical Digest of International Electron Devices Meeting, Washington, DC, USA, 7–9 December 2015. [Google Scholar]

- Hwang, C.-H.; Li, T.-Y.; Han, M.-H.; Lee, K.-F.; Cheng, H.-W.; Li, Y. Statistical 3D Simulation of Metal Gate Workfunction Variability, Process Variation, and Random Dopant Fluctuation in Nano-CMOS Circuits. In Proceedings of the International Conference on Simulation of Semiconductor Processes and Devices, San Diego, CA, USA, 9–11 September 2009. [Google Scholar]

- Cheng, H.-W.; Li, F.-H.; Han, M.-H.; Yiu, C.-Y.; Yu, C.-H.; Lee, K.-F.; Li, Y. 3D Device Simulation of Work Function and Interface Trap Fluctuations on High-κ/Metal Gate Devices. In Proceedings of the Technical Digest of International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010. [Google Scholar]

- Tan, C.M.; Chen, X. Random dopant fluctuation in gate-all-around nanowire FET. In Proceedings of the IEEE International Nanoelectronics Conference, Sapporo, Japan, 28–31 July 2014. [Google Scholar]

- Arnaud, F.; Pinzelli, L.; Gallon, C.; Rafik, M.; Mora, P.; Boeuf, F. Challenges and opportunity in performance, variability and reliability in sub-45 nm CMOS technologies. Microelectron. Reliab. 2011, 51, 1508–1514. [Google Scholar] [CrossRef]

- Stathis, J.H.; Wang, M.; Southwick, R.G.; Wu, E.Y.; Linder, B.P.; Liniger, E.G.; Bonilla, G.; Kothari, H. Reliability Challenges for the 10 nm Node and Beyond. In Proceedings of the Technical Digest of International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014. [Google Scholar]

- Kuhn, K.J. Considerations for Ultimate CMOS Scaling. IEEE Trans. Electron Devices 2012, 59, 1813–1828. [Google Scholar] [CrossRef]

- Hussain, M.M.; Quevedo-Lopez, M.A.; Alshareef, H.N.; Wen, H.C.; Larison, D.; Gnade, B.; El-Bouanani, M. Thermal Annealing Effects on A Representative High-κ/Metal Film Stack. Semicond. Sci. Technol. 2006, 21, 1437–1440. [Google Scholar] [CrossRef]

- Heu, J.L.; Setsuhara, Y.; Shimizu, I.; Miyake, S. Structure Refinement and Hardness Enhancement of Titanium Nitride Films by Addition of Copper. Surf. Coat. Technol. 2001, 137, 38–42. [Google Scholar] [CrossRef]

- Matsukawa, T.; Liu, Y.; Endo, K.; Tsukada, J.; Yamauchi, H.; Ishikawa, Y.; O’uchi, S.; Mizubayashi, W.; Ota, H.; Migita, S.; et al. Influence of work function variation of metal gates on fluctuation of sub-threshold drain current for Fin field-effect transistors with undoped channels. Jpn. J. Appl. Phys. 2014, 53, 4S. [Google Scholar] [CrossRef]

- Li, Y.; Cheng, H.-W.; Yiu, C.-Y.; Su, H.-W. Nanosized metal grains induced electrical characteristic fluctuation in 16-nm-gate high-κ/metal gate bulk FinFET devices. Microelectron. Eng. 2011, 88, 1240–1242. [Google Scholar] [CrossRef]

- Kundu, A.; Koley, K.; Dutta, A.; Sarkar, C.K. Impact of gate metal work-function engineering for enhancement of subthreshold analog/RF performance of underlap dual material gate DG-FET. Microelectron. Reliab. 2014, 54, 2717–2722. [Google Scholar] [CrossRef]

- Lee, K.-C.; Fan, M.-L.; Su, P. Investigation and comparison of analog figures-of-merit for TFET and FinFET considering work-function variation. Microelectron. Reliab. 2015, 55, 332–336. [Google Scholar] [CrossRef]

- Seoane, N.; Indalecio, G.; Aldegunde, M.; Nagy, D.; Elmessary, M.A.; García-Loureiro, A.J.; Kalna, K. Comparison of Fin-Edge Roughness and Metal Grain Work Function Variability in InGaAs and Si FinFETs. IEEE Trans. Electron Devices 2016, 63, 1209–1216. [Google Scholar] [CrossRef]

- Nawaz, S.M.; Mallik, A. Effects of Device Scaling on the Performance of Junctionless FinFETs Due to Gate-Metal Work Function Variability and Random Dopant Fluctuations. IEEE Electron Device Lett. 2016, 37, 958–961. [Google Scholar] [CrossRef]

- Yang, C.-C.; Huang, W.-H.; Hsieh, T.-Y.; Wu, T.-T.; Wang, H.-H.; Shen, C.-H.; Yeh, W.-K.; Shiu, J.-H.; Chen, Y.-H.; Wu, M.-C.; et al. High Gamma Value 3D-Stackable HK/MG-Stacked Tri-Gate Nanowire Poly-Si FETs With Embedded Source/Drain and Back Gate Using Low Thermal Budget Green Nanosecond Laser Crystallization Technology. IEEE Electron Device Lett. 2016, 37, 533–536. [Google Scholar] [CrossRef]

- Dev, S.; Meena, M.; Harsha Vardhan, P.; Lodha, S. Statistical Simulation Study of Metal Grain-Orientation-Induced MS and MIS Contact Resistivity Variability for 7-nm FinFETs. IEEE Trans. Electron Devices 2018, 65, 3104–3111. [Google Scholar] [CrossRef]

- Li, Y.; Cheng, H.-W.; Chiu, Y.-Y.; Yiu, C.-Y.; Su, H.-W. A Unified 3D Device Simulation of Random Dopant, Interface Trap and Work Function Fluctuations on High-κ/Metal Gate Device. In Proceedings of the Technical Digest of International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011. [Google Scholar]

- Dadgour, H.; Endo, K.; Vivek, D.; Banerjee, K. Modeling and analysis of grain-orientation effects in emerging metal-gate devices and implications for sram reliability. In Proceedings of the Technical Digest of International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008. [Google Scholar]

- Li, Y.; Chen, C.-Y.; Chen, Y.-Y. Random-Work-Function-Induced Characteristic Fluctuation in 16-nm-Gate Bulk and SOI FinFETs. Int. J. Nanotechnol. 2014, 11, 1029–1038. [Google Scholar] [CrossRef]

- Dadgour, H.F.; Endo, K.; De, V.K.; Banerjee, K. Grain-orientation induced work function variation in nanoscale metal-gate transistors—Part I: Modeling, analysis, and experimental validation. IEEE Trans. Electron Devices 2010, 57, 2504–2514. [Google Scholar] [CrossRef]

- Indalecio, G.; García-Loureiro, A.J.; Iglesias, N.S.; Kalna, K. Study of Metal-Gate Work-Function Variation Using Voronoi Cells: Comparison of Rayleigh and Gamma Distributions. IEEE Trans. Electron Devices 2016, 63, 2625–2628. [Google Scholar] [CrossRef]

- Li, Y.; Huang, C.-H. The Effect of the Geometry Aspect Ratio on the Silicon Ellipse-Shaped Surrounding-Gate Field-Effect Transistor and Circuit. Semicond. Sci. Technol. 2009, 24, 095018. [Google Scholar] [CrossRef]

- Tienda-Luna, I.M.; Ruiz, F.G.; Godoy, A.; Donetti, L.; G’amiz, F. Effects of deviations in the cross-section of square nanowires. In Proceedings of the International Workshop on Computational Electronics, Pisa, Italy, 26–29 October 2010. [Google Scholar]

- Jha, S.; Kumar, A.; Kumar, S. Impact of Elliptical Cross-Section on Some Electrical Properties of Gate-All-Around MOSFETs. Bonfring Int. J. Power Syst. Integr. Circuits 2012, 2, 18–22. [Google Scholar] [CrossRef]

- Li, Y.; Huang, C.-H.; Li, T.-Y.; Han, M.-H. Process-Variation Effect, Metal-Gate Work-Function Fluctuation, and Random-Dopant Fluctuation in Emerging CMOS Technologies. IEEE Trans. Electron Device 2010, 57, 437–447. [Google Scholar] [CrossRef]

- Han, M.-H.; Li, Y.; Hwang, C.-H. The impact of high-frequency characteristics induced by intrinsic parameter fluctuations in nano-MOSFET device and circuit. Microelectron. Reliab. 2010, 50, 657–661. [Google Scholar] [CrossRef]

- Hwang, C.-H.; Li, Y.; Han, M.-H. Statistical Variability in FinFET Devices with Intrinsic Parameter Fluctuations. Microelectron. Reliab. 2010, 50, 635–638. [Google Scholar] [CrossRef]

- Li, Y.; Hwang, C.-H.; Cheng, H.-W. Process-variation- and random-dopants-induced threshold voltage fluctuations in nanoscale planar MOSFET and bulk FinFET devices. Microelectron. Eng. 2009, 86, 277–282. [Google Scholar] [CrossRef]

- Kuhn, K.J. CMOS Scaling for the 22 nm Node and Beyond: Device Physics and Technology. In Proceedings of the International Symposium on VLSI Technology, Systems and Applications, Hsinchu, Taiwan, 25–27 April 2011. [Google Scholar]

- Li, Y. Optimal Geometry Aspect Ratio of Ellipse-Shaped-Surrounding-Gate Nanowire Field Effect Transistors. J. Nanosci. Nanotechnol. 2016, 16, 920–923. [Google Scholar] [CrossRef]

- Han, K.; Hsu, P.-F.; Beach, M.; Henry, T.; Yoshida, N.; Brand, A. Metal Gate Work Function Modulation by Ion Implantation for Multiple Threshold Voltage FinFET Devices. In Proceedings of the Extended Abstracts of International Workshop on Junction Technology, Kyoto, Japan, 6–7 June 2013. [Google Scholar]

- Han, K.; Lee, J.; Tang, S.; Maynard, H.; Yoshida, N.; Brand, A. FinFET Multi-Vt Tuning with Metal Gate Work Function Modulation by Plasma Doping. In Proceedings of the International Workshop on Junction Technology, Shanghai, China, 18–20 May 2014. [Google Scholar]

- Yang, F.-L.; Lee, D.-H.; Chen, H.-Y.; Chang, C.-Y.; Liu, S.-D.; Huang, C.-C.; Chung, T.-X.; Chen, H.-W.; Huang, C.-C.; Liu, Y.-H.; et al. 5 nm-Gate Nanowire FinFET. In Proceedings of the Digest of Technical Papers, Symposium on VLSI Technology, Honolulu, HI, USA, 17–19 June 2004. [Google Scholar]

- Sung, W.-L.; Li, Y. DC/AC/RF Characteristic Fluctuations Induced by Various Random Discrete Dopants of Gate-All-Around Silicon Nanowire n-MOSFETs. IEEE Trans. Electron Devices 2018, 65, 2638–2646. [Google Scholar] [CrossRef]

- Li, Y.; Cheng, H.-W.; Hwang, C.-H. Threshold Voltage Fluctuation in 16-nm-Gate FinFETs Induced by Random Work Function of Nanosized Metal Grain. J. Nanosci. Nanotechnol. 2012, 12, 4485–4488. [Google Scholar] [CrossRef]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, Y.; Chen, C.-Y.; Chuang, M.-H.; Chao, P.-J. Characteristic Fluctuations of Dynamic Power Delay Induced by Random Nanosized Titanium Nitride Grains and the Aspect Ratio Effect of Gate-All-Around Nanowire CMOS Devices and Circuits. Materials 2019, 12, 1492. https://doi.org/10.3390/ma12091492

Li Y, Chen C-Y, Chuang M-H, Chao P-J. Characteristic Fluctuations of Dynamic Power Delay Induced by Random Nanosized Titanium Nitride Grains and the Aspect Ratio Effect of Gate-All-Around Nanowire CMOS Devices and Circuits. Materials. 2019; 12(9):1492. https://doi.org/10.3390/ma12091492

Chicago/Turabian StyleLi, Yiming, Chieh-Yang Chen, Min-Hui Chuang, and Pei-Jung Chao. 2019. "Characteristic Fluctuations of Dynamic Power Delay Induced by Random Nanosized Titanium Nitride Grains and the Aspect Ratio Effect of Gate-All-Around Nanowire CMOS Devices and Circuits" Materials 12, no. 9: 1492. https://doi.org/10.3390/ma12091492

APA StyleLi, Y., Chen, C.-Y., Chuang, M.-H., & Chao, P.-J. (2019). Characteristic Fluctuations of Dynamic Power Delay Induced by Random Nanosized Titanium Nitride Grains and the Aspect Ratio Effect of Gate-All-Around Nanowire CMOS Devices and Circuits. Materials, 12(9), 1492. https://doi.org/10.3390/ma12091492