Efficiency Optimization of a Series-Resonant Dual-Active-Bridge Converter with Voltage-Doubler Rectification

Abstract

1. Introduction

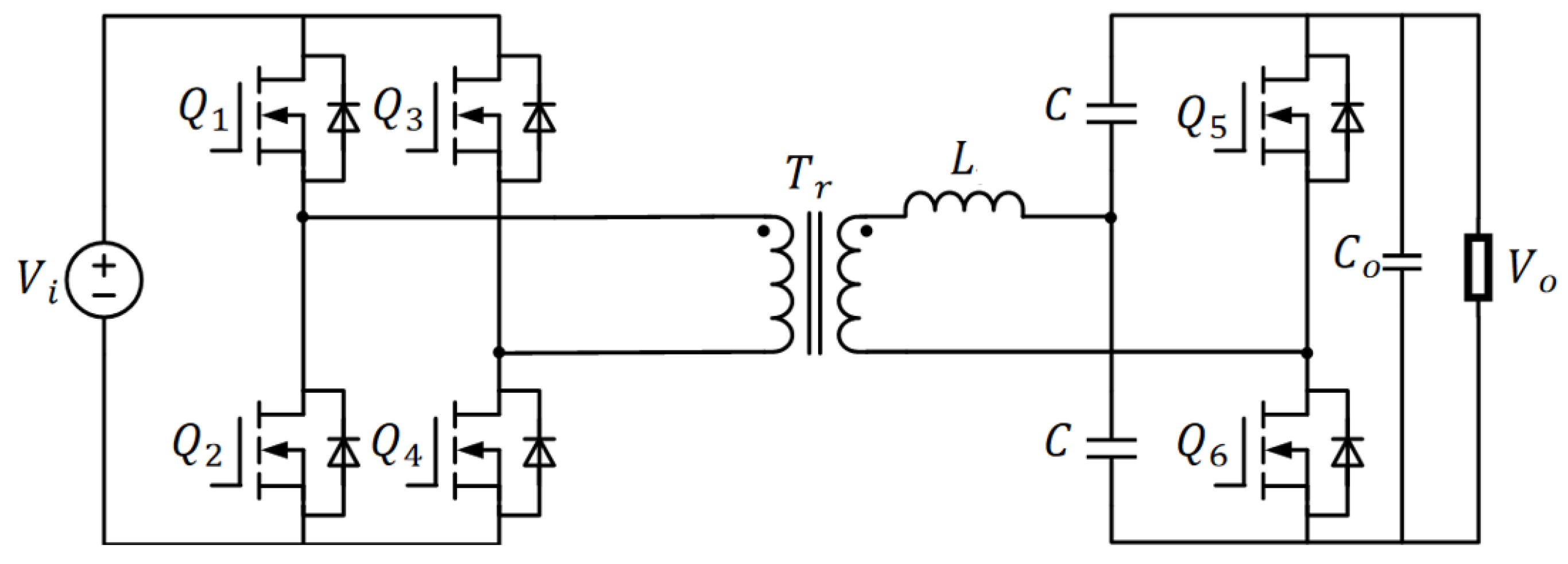

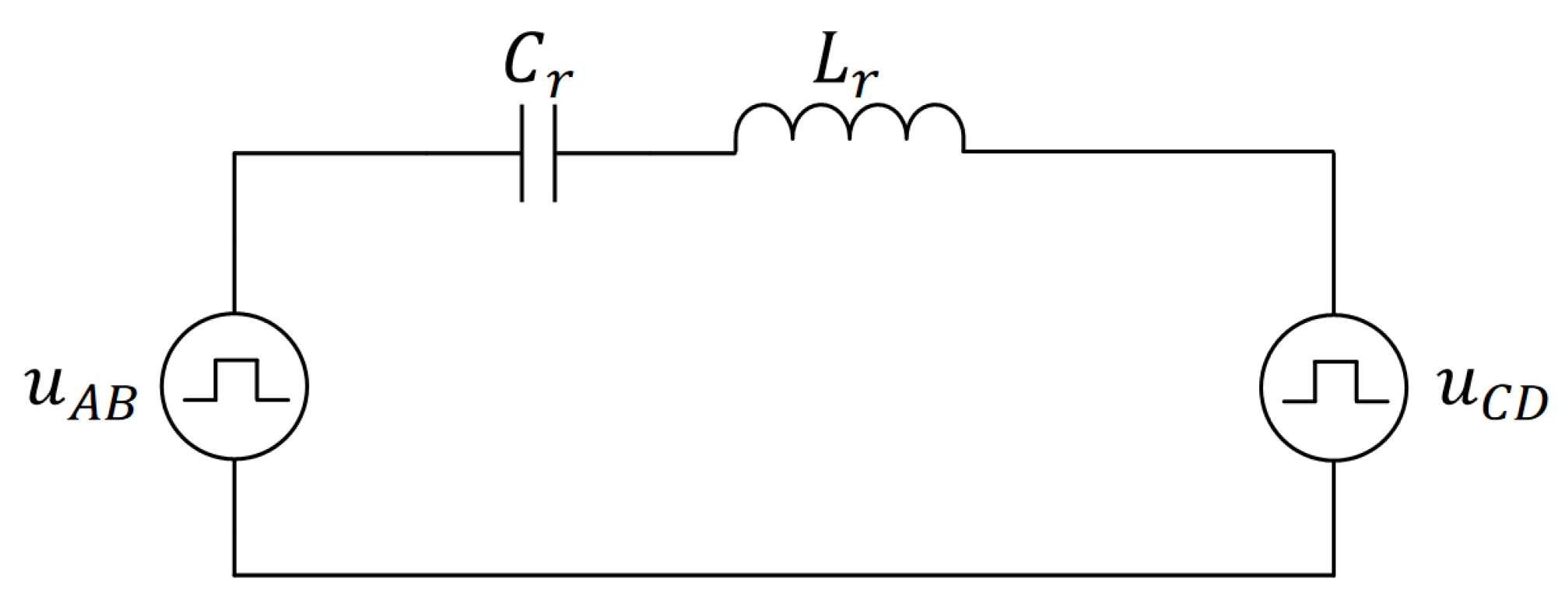

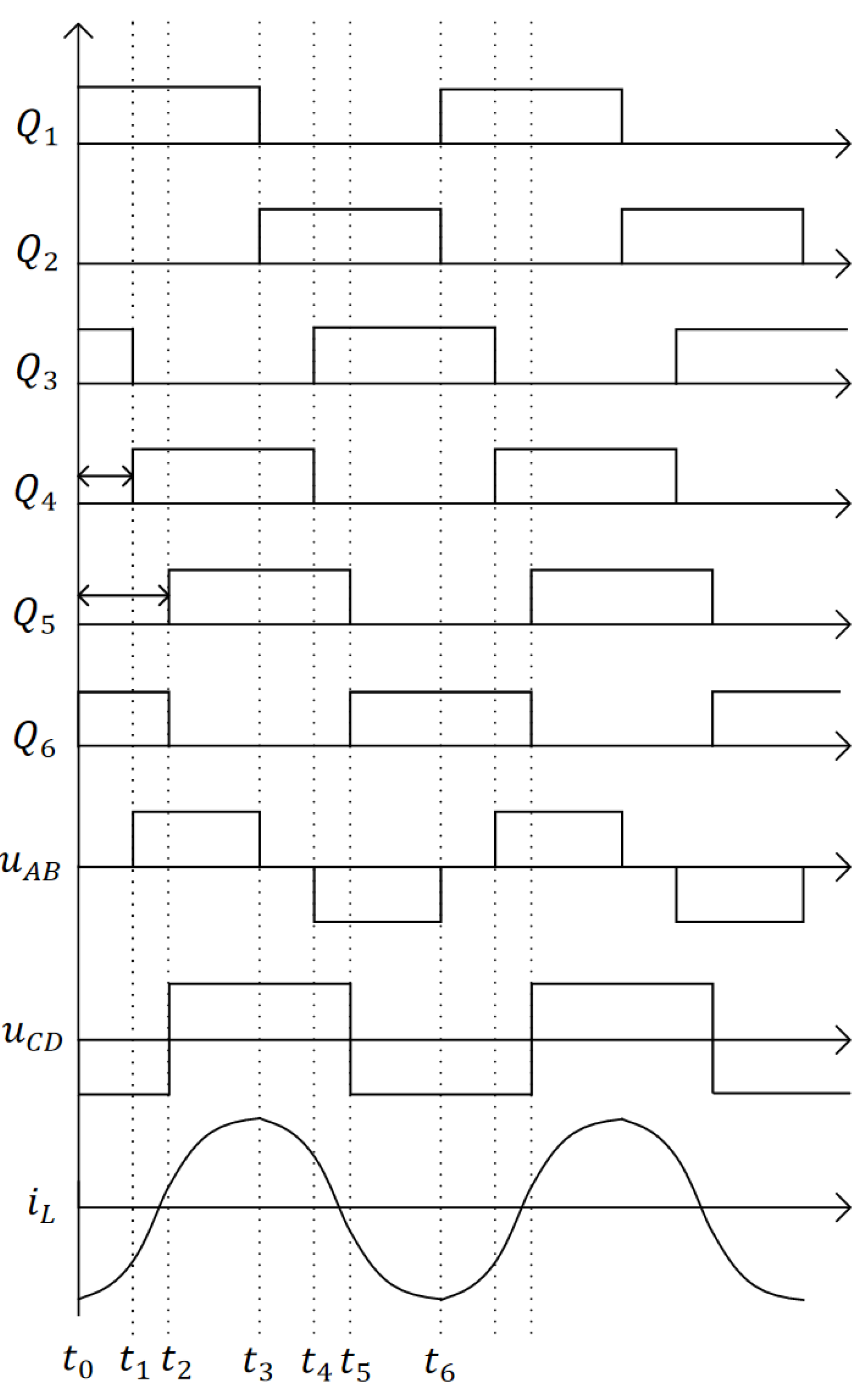

2. Operating Principle of the Voltage-Doubler-Based SRDAB Converter

2.1. Topology Description

2.2. Phasor-Time Domain Hybrid Modeling

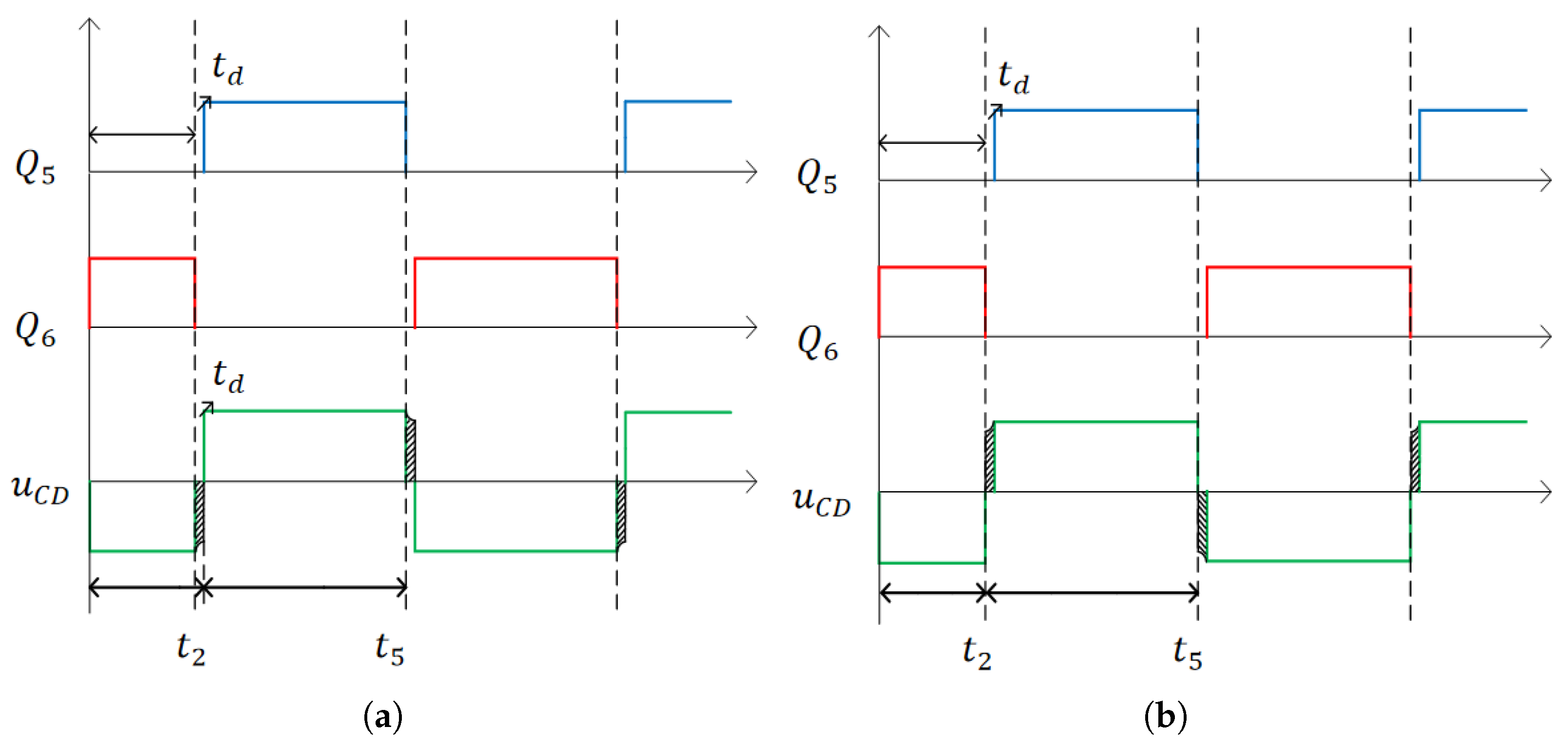

3. Output Voltage Gain Correction Considering Dead Time and Parasitic Parameters

4. Efficiency Optimization Under Soft-Switching Conditions

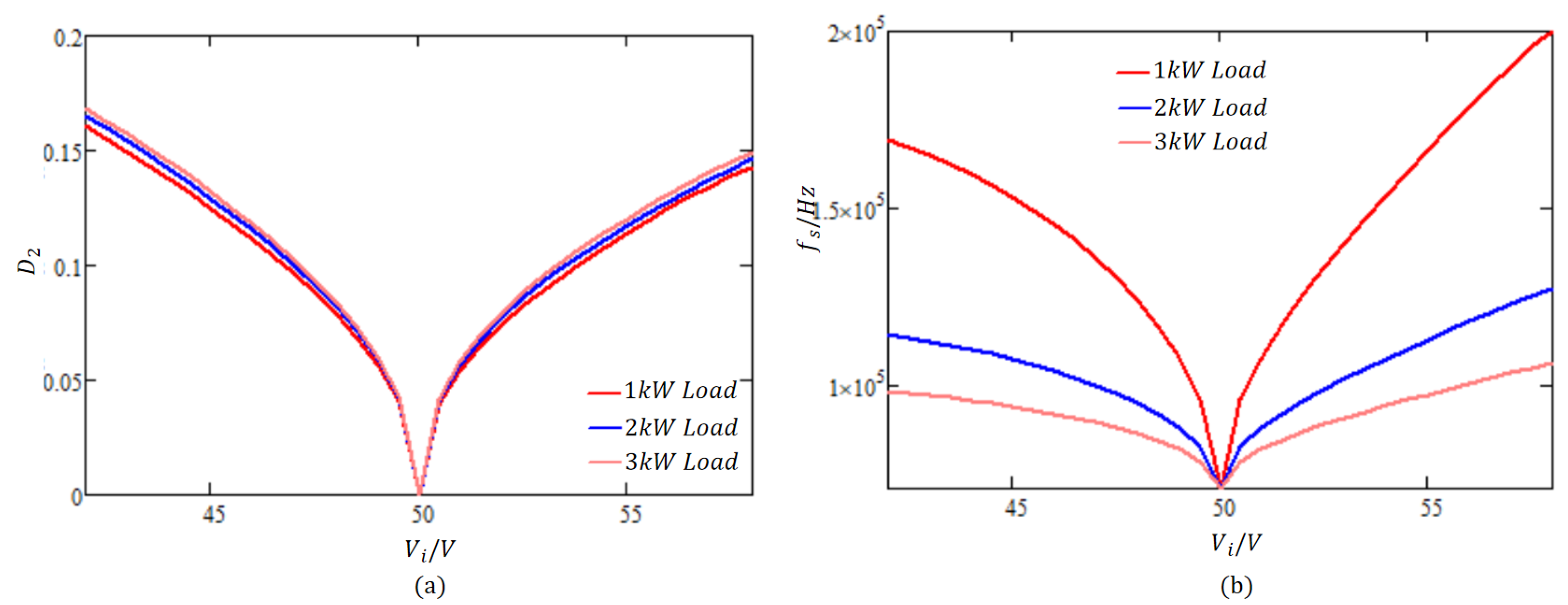

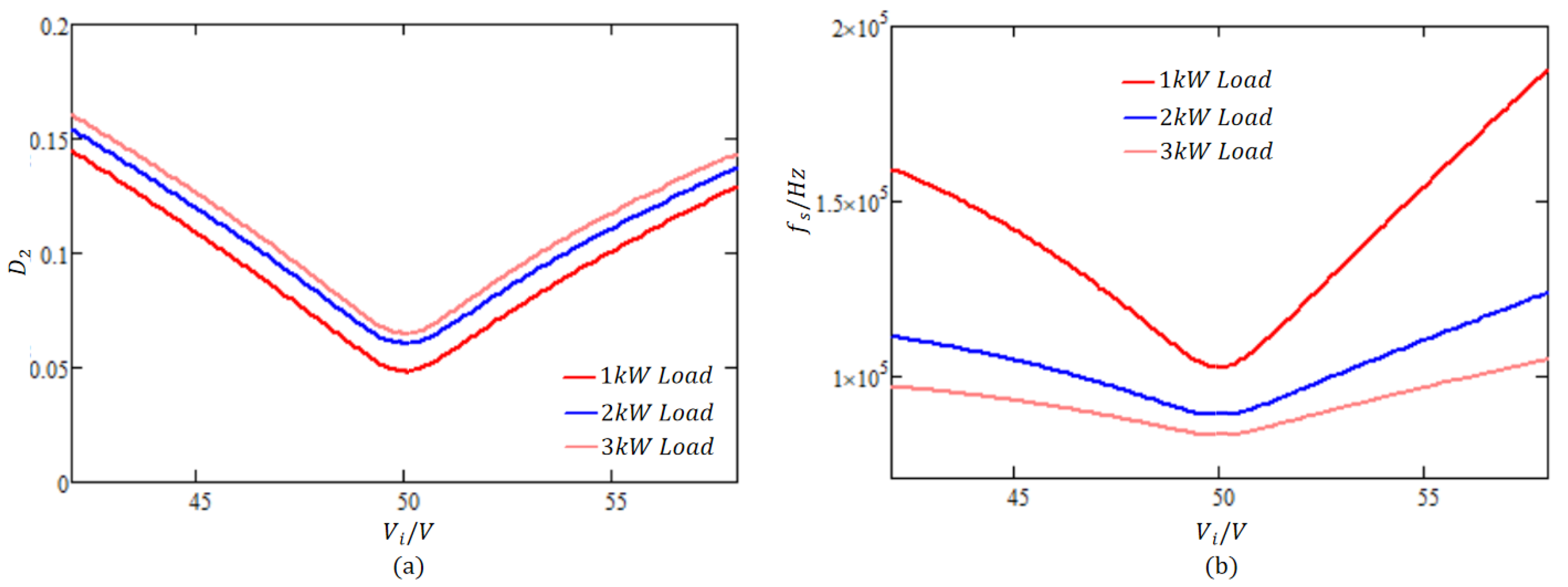

4.1. Reactive Power and RMS Current Minimization

4.2. Minimization of RMS Switching Instantaneous Current

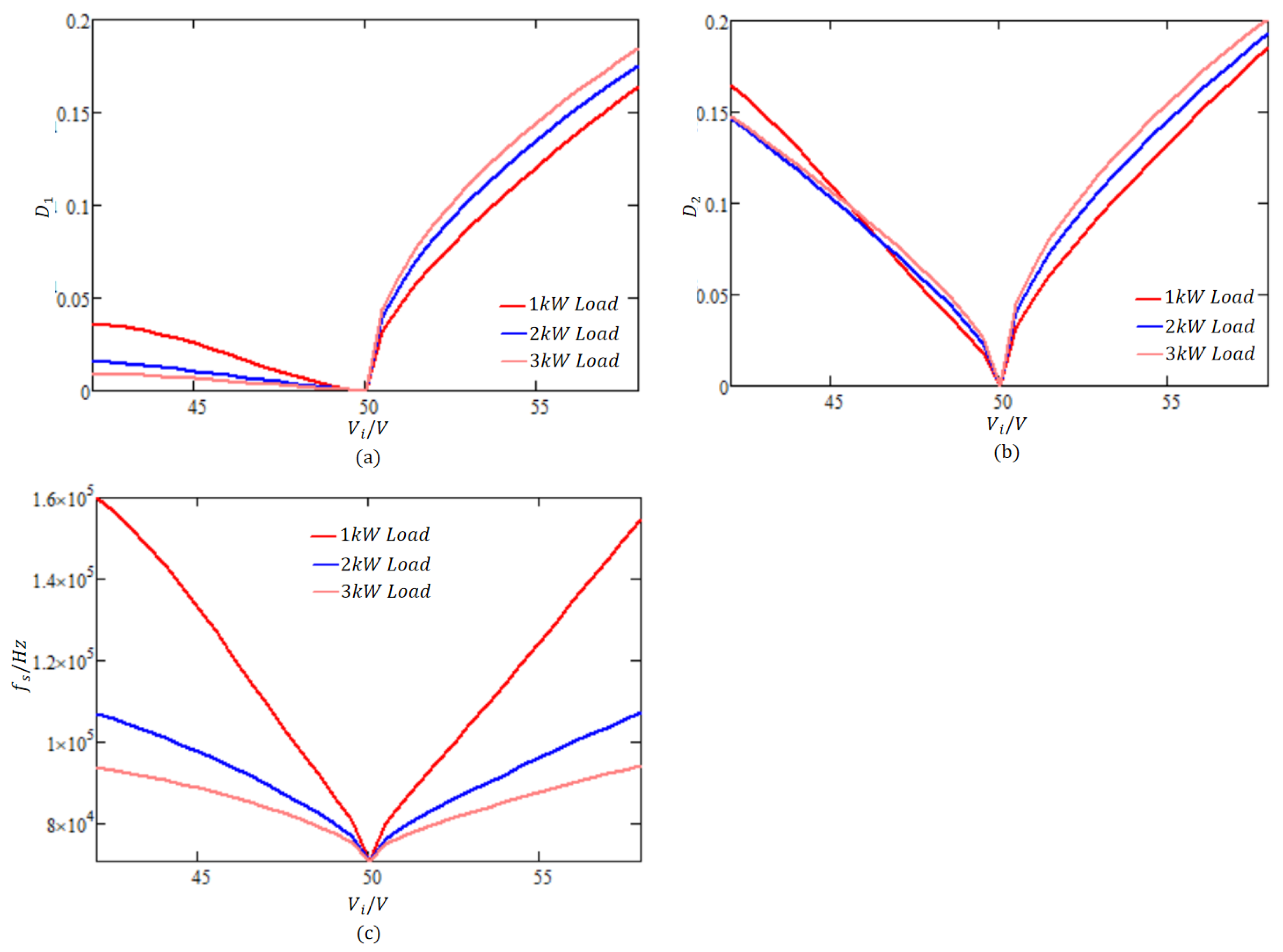

- At V, , and , the system operates near resonance in an open-loop manner, resembling an LLC resonant converter, achieving peak efficiency;

- When V, is close to zero, resulting in SPS-like behavior;

- When V, , equivalent to primary-side internal phase-shift control, similar to a phase-shift full-bridge (PSFB) converter.

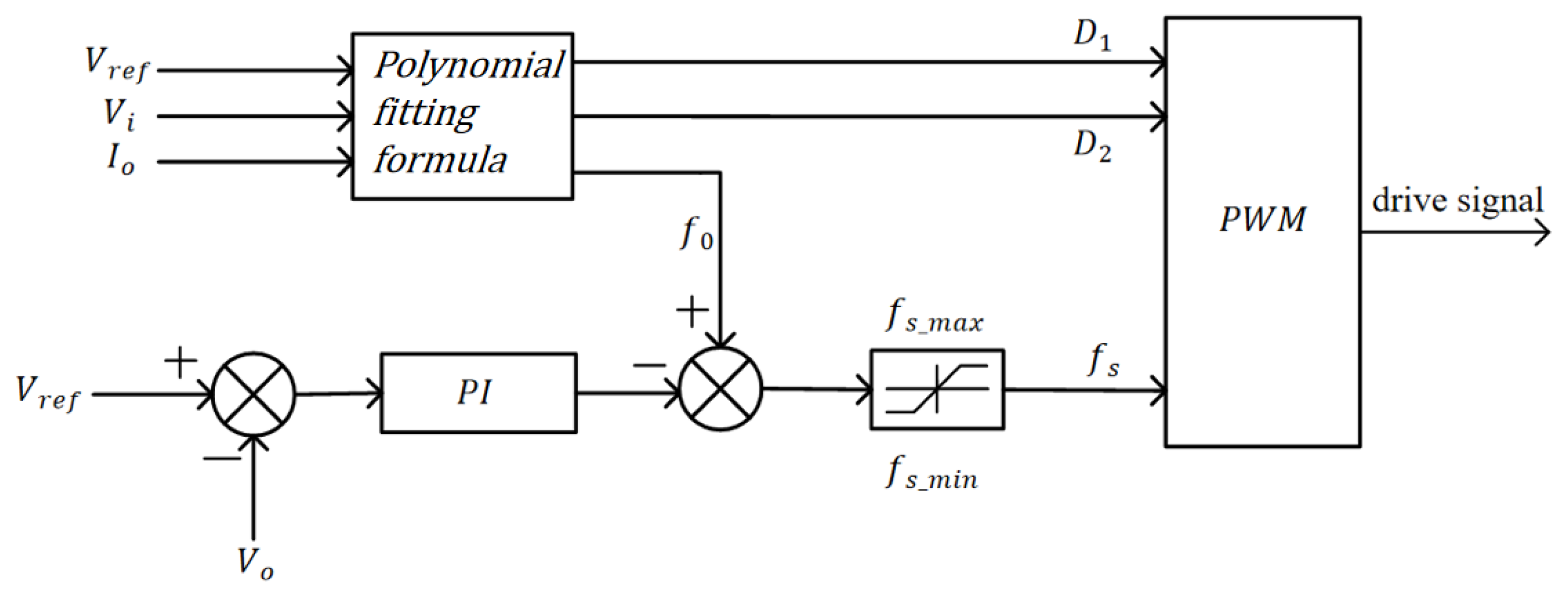

4.3. Closed-Loop Control Design and Implementation

- : reference output voltage;

- : sampled output current;

- : phase-shift ratios and base frequency calculated online from fitted optimization curves;

- : minimum and maximum allowable switching frequencies.

- During load transients, it proactively shifts the operating point to the new optimal frequency, minimizing the magnitude and duration of resonant current excursions;

- More importantly, it ensures ZVS for all power switches—even under worst-case step-load conditions.

5. Experimental Validation

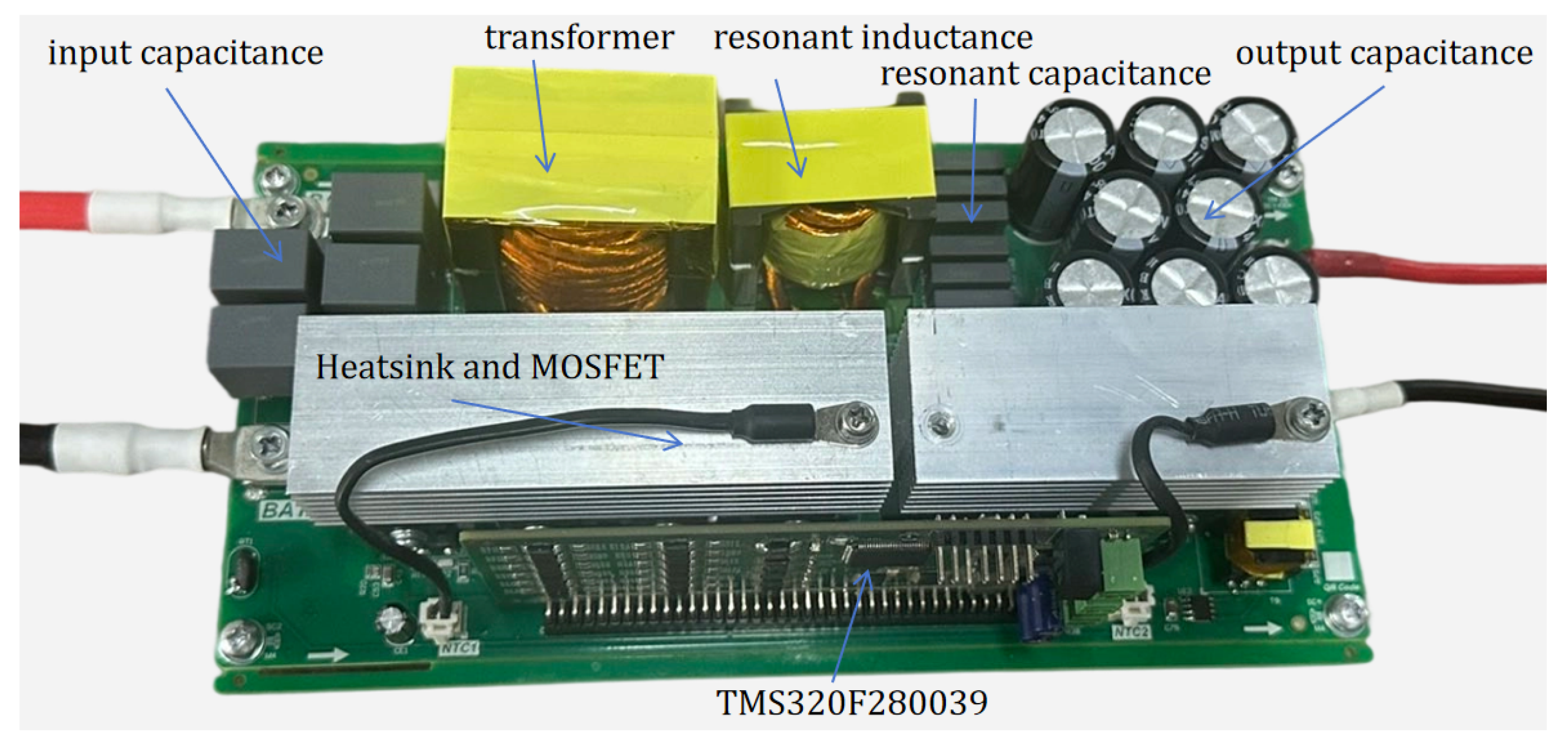

5.1. Prototype Setup

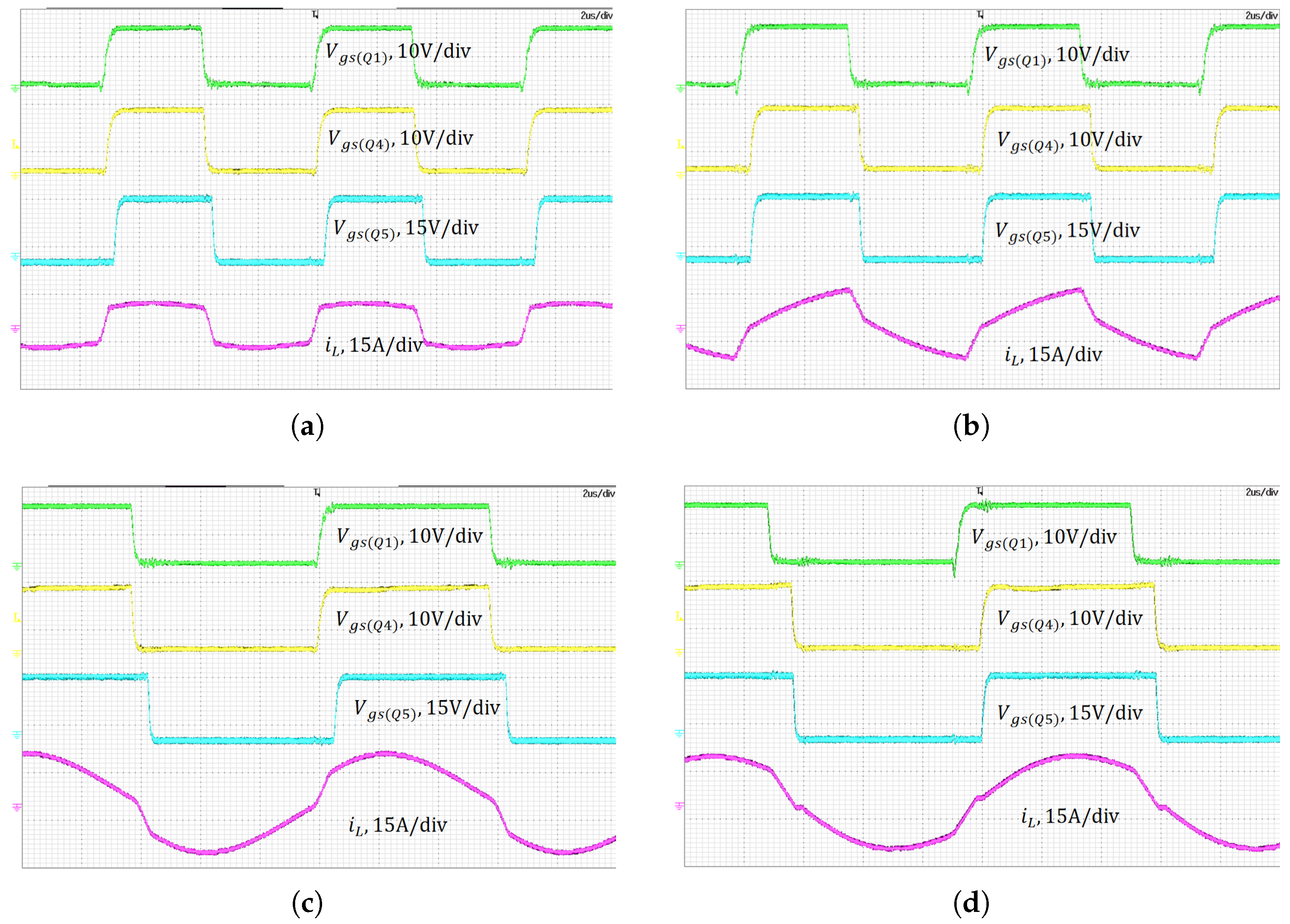

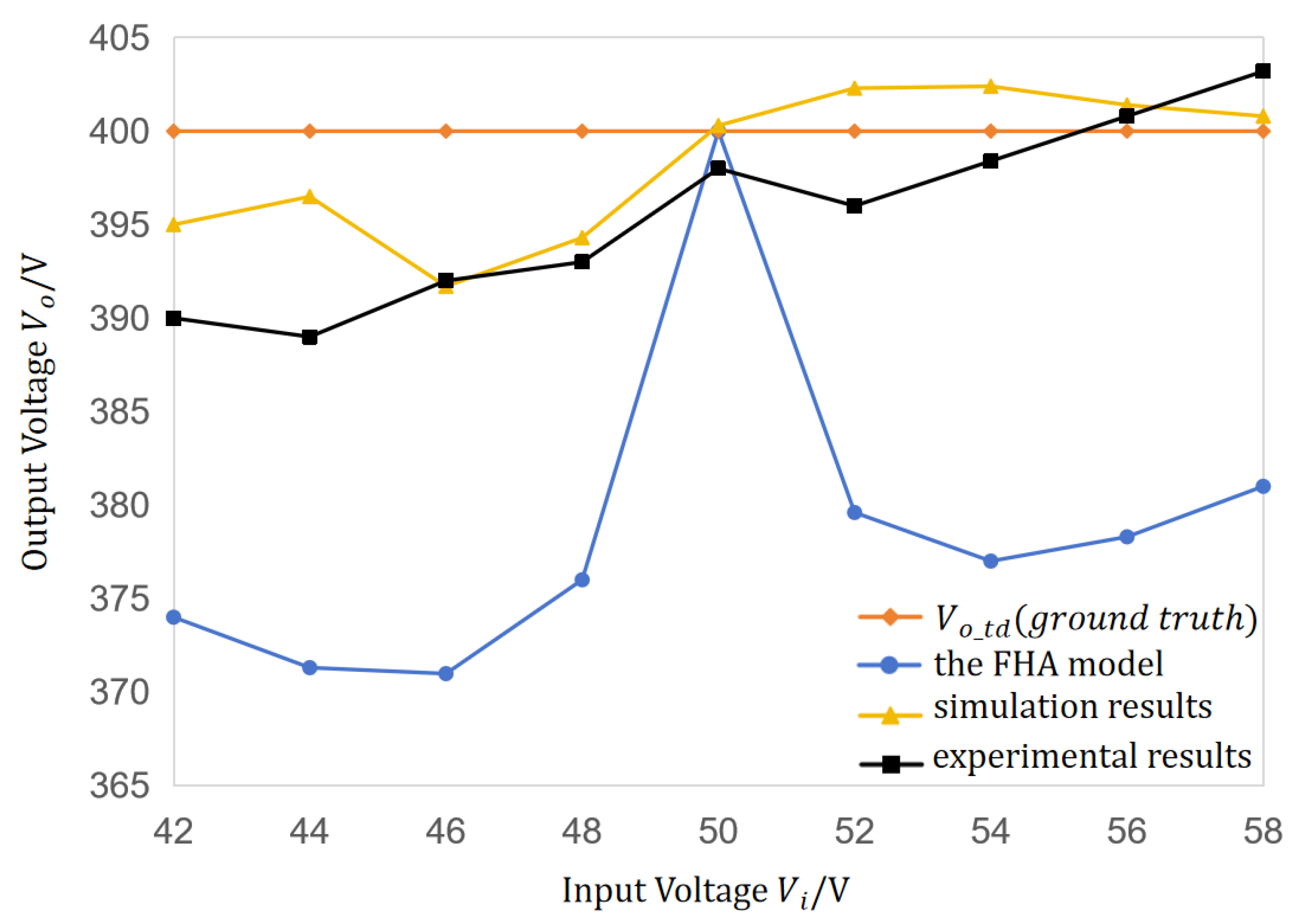

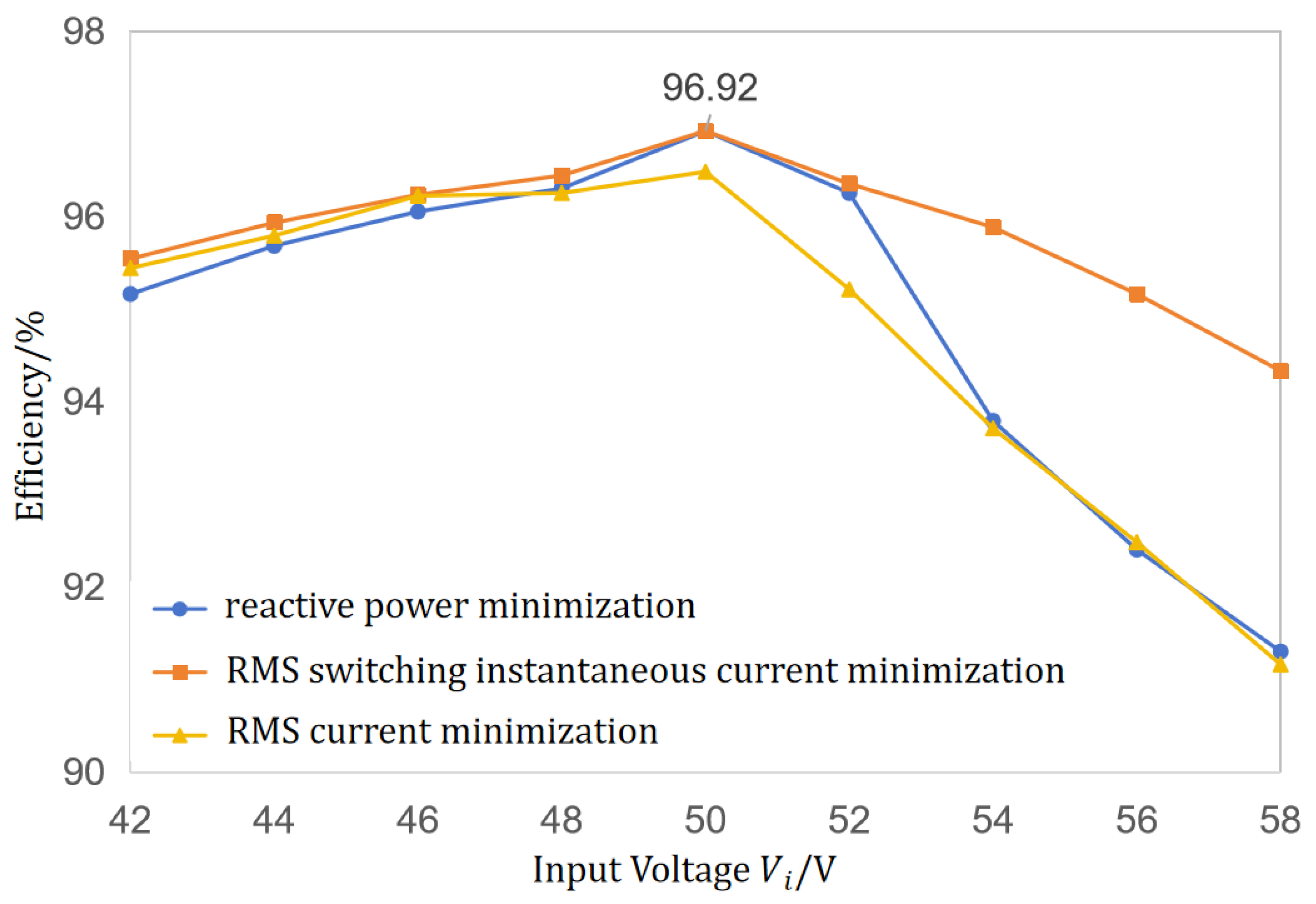

5.2. Soft-Switching Performance and Efficiency Evaluation

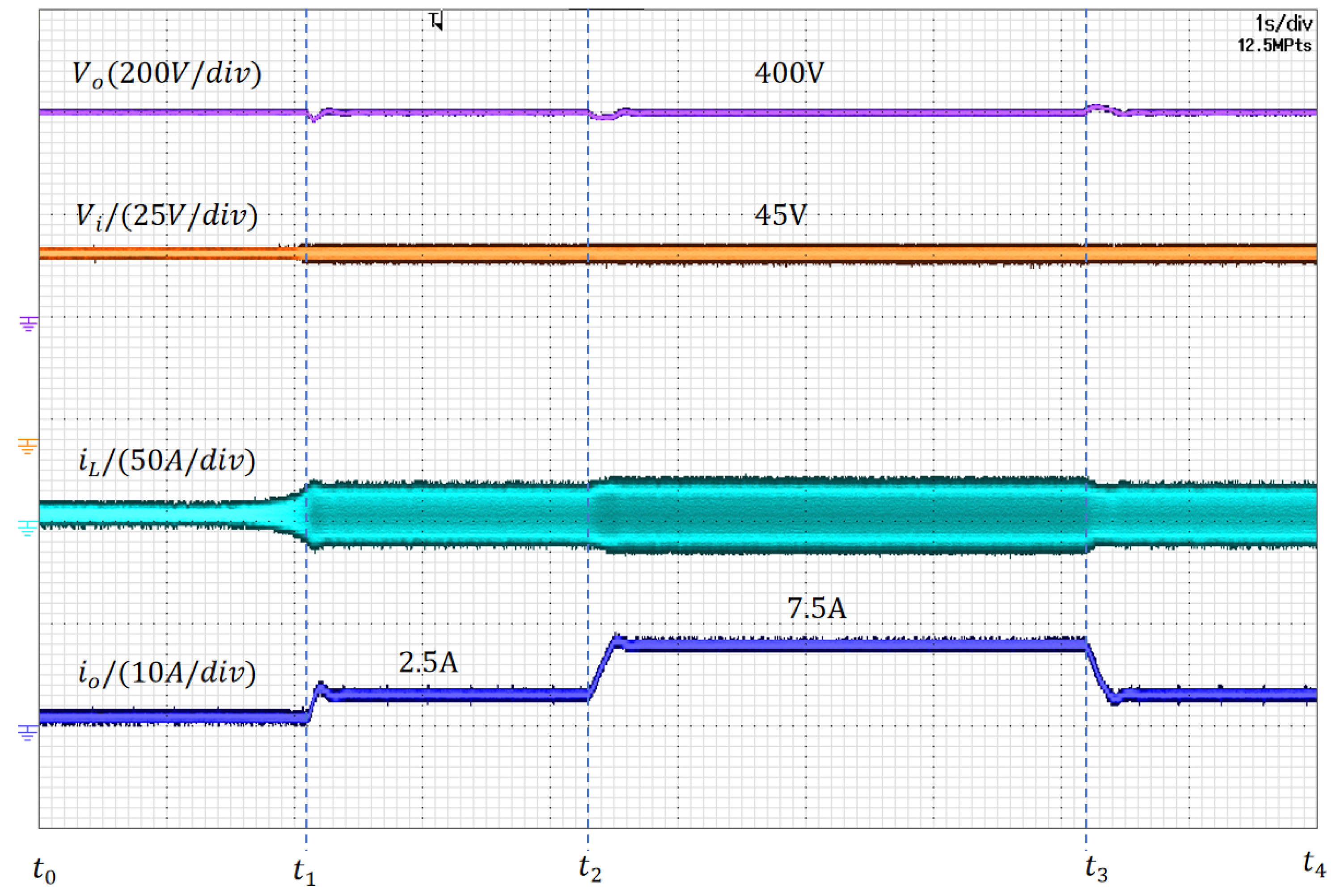

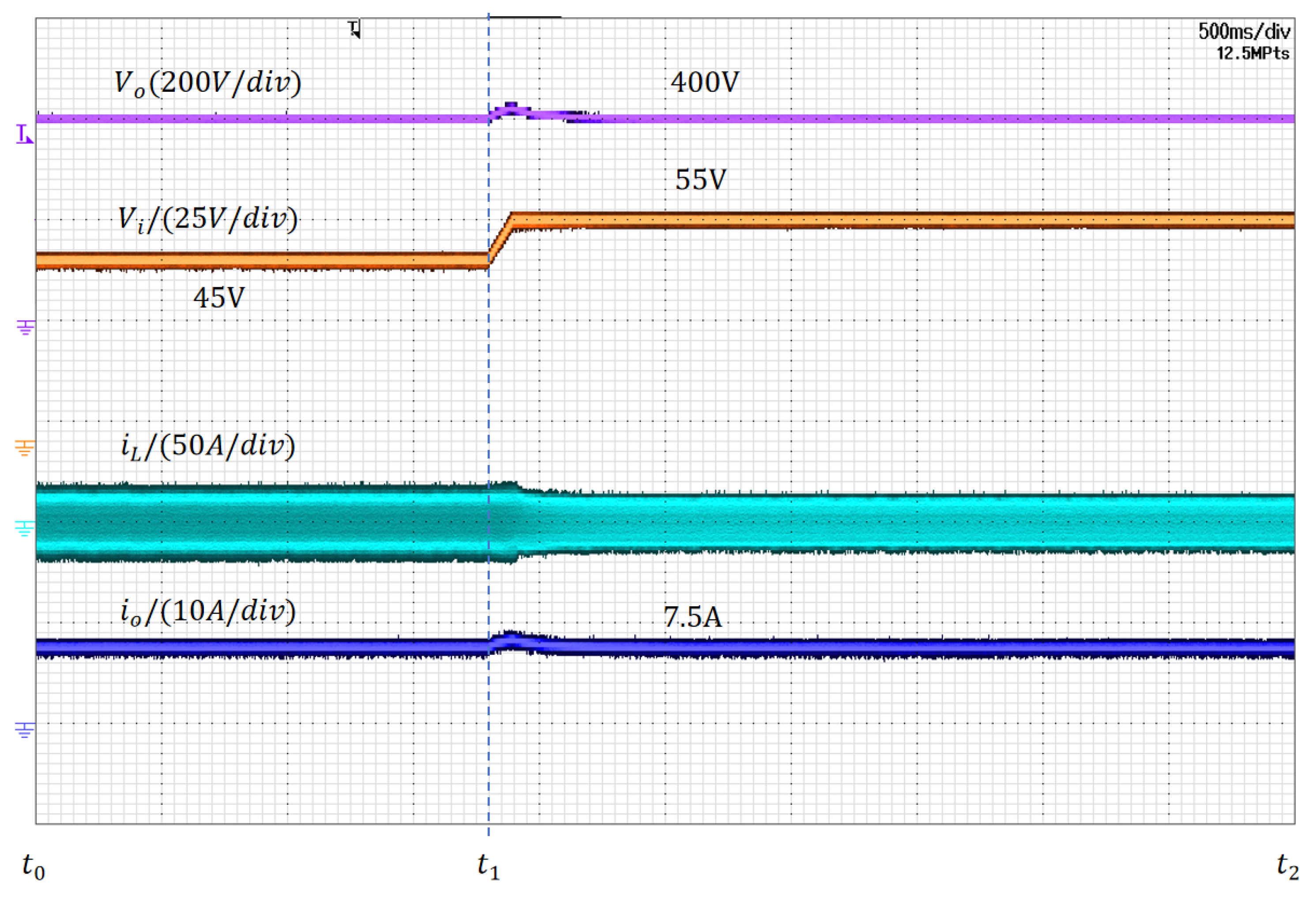

5.3. Dynamic Performance Validation

6. Conclusions

- 1.

- The proposed phasor-time domain model achieves high accuracy in predicting output voltage gain and ZVS conditions, closely matching both simulation and measurement data;

- 2.

- The RMS switching instantaneous current minimization strategy achieves higher overall efficiency compared to reactive power minimization and RMS current minimization, with up to 4% efficiency improvement under high-input-voltage conditions;

- 3.

- The proposed optimization and control method ensures reliable ZVS across wide voltage gain and load ranges, fully leveraging the soft-switching advantages of resonant DAB converters.

- 4.

- The real-time feedforward implementation enables fast and stable dynamic response under both load and line transients. Experimental waveforms show that the output voltage recovers from large steps (e.g., 1 kW → 3 kW) within less than 300 ms, with minimal overshoot/undershoot, and maintains regulation during ±20% input voltage variations, confirming the practical viability of the model-driven control approach.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Li, Z.X.; Fan, G.Q.; Zhao, C.; Zhang, H.; Wang, P.; Li, Y. Research Review of Power Electronic Transformer Technologies. Proc. CSEE 2018, 38, 1274–1289. [Google Scholar] [CrossRef]

- Wang, Y.; Zheng, Z.; Li, Y. Review of Topology and Control Application of Medium and High Voltage Power Electronic Transformer. Adv. Technol. Electr. Eng. Energy 2017, 36, 1–10. [Google Scholar] [CrossRef]

- Shen, K.; Tong, P.; Hang, L.; Li, G.; Zhu, M.; Dai, R. Soft Switching Modulation Strategy of Dual Active Bridge Converters Applied in Renewable Energy Systems. Autom. Electr. Power Syst. 2019, 43, 154–159. [Google Scholar] [CrossRef]

- Zhao, B.; An, F.; Song, Q.; Yu, Z.; Zeng, R. Development and Application of DC Transformer Based on Dual-Active-Bridge. Proc. CSEE 2021, 41, 288–298. [Google Scholar] [CrossRef]

- Shao, S.; Chen, H.; Wu, X.; Zhang, J.; Sheng, K. Circulating Current and ZVS-On of a Dual Active Bridge DC-DC Converter: A Review. IEEE Access 2019, 7, 50561–50572. [Google Scholar] [CrossRef]

- Liu, H.; Mao, C.; Lu, J. Energy Storage System of Electronic Power Transformer and Its Optimal Control. Trans. China Electrotech. Soc. 2010, 25, 54–60. [Google Scholar]

- Xue, X.; Liu, Z.; Li, W.; Su, H. Design of a Single-Stage Dual Active Bridge Micro-Inverter with Wide Load Adaptability Based on Loss Optimization. IEEE Trans. Power Electron 2025, 40, 7919–7935. [Google Scholar] [CrossRef]

- Wu, H.; Sun, K.; Li, Y.; Xing, Y. Fixed-Frequency PWM-Controlled Bidirectional Current-Fed Soft-Switching Series-Resonant Converter for Energy Storage Applications. IEEE Trans. Ind. Electron. 2017, 64, 6190–6201. [Google Scholar] [CrossRef]

- Hao, C.; Lei, J.; Ma, H.; Guo, Z.; Qin, G. Phase-Shift Variable-Frequency Control Strategy of a Single-Stage Micro Inverter Based on Dual Active Bridge Topology. In Proceedings of the 2024 IEEE 12th International Conference on Smart Energy Grid Engineering (SEGE), Oshawa, ON, Canada, 18–20 August 2024; pp. 20–24. [Google Scholar] [CrossRef]

- Han, W.; Corradini, L. General Closed-Form ZVS Analysis of Dual-Bridge Series Resonant DC-DC Converters. IEEE Trans. Power Electron 2019, 34, 9289–9302. [Google Scholar] [CrossRef]

- Zhao, F.; Gan, Y.; Chen, X.; Wang, Y. Design of Dual Active Bridge Series Resonant Converter Based on Frequency Domain Analysis and Closed-Loop Control. High Volt. Eng. 2022, 48, 4557–4567. [Google Scholar] [CrossRef]

- Xiao, C.; Zhao, S. Minimum RMS Current Scheme of DAB Converter Based on Frequency Domain Analysis. Power Electron 2024, 58, 36–39. [Google Scholar] [CrossRef]

- Wu, J.; Cheng, Y.; Yan, X.; Sun, X. Power Loss of Series Resonant Three-Phase Dual Active Bridge Converter. Acta Energiae Solaris Sin. 2022, 43, 149–156. [Google Scholar] [CrossRef]

- Yaqoob, M.; Loo, K.H.; Lai, Y.M. A Four-Degrees-of-Freedom Modulation Strategy for Dual-Active-Bridge Series-Resonant Converter Designed for Total Loss Minimization. IEEE Trans. Power Electron. 2019, 34, 1065–1081. [Google Scholar] [CrossRef]

- Yang, B.; Ge, Q.; Zhao, L.; Zhou, Z. The Backflow Power Optimization of Dual Bridge Series Resonant DC/DC Converter. Proc. CSEE 2019, 39, 6990–6999. [Google Scholar] [CrossRef]

- Wu, J.; Li, Y.; Zhang, Z.; Wen, P.; Sun, X. Analysis on Soft-Switching Characteristics of Series Resonant Dual-Active-Bridge Converter. Acta Energiae Solaris Sin. 2017, 38, 3005–3011. [Google Scholar]

- Fan, E.; Li, Y.; Ge, Q. Feedforward Control Strategy of Dual Active Bridge Series Resonant Converter Based on Optimized Phase Shift. Trans. China Electrotech. Soc. 2025, 40, 5324–5333. [Google Scholar] [CrossRef]

- Gao, Y.; Zhou, Z.; Zhang, X.; Ma, H. Minimum Backflow Current Control of Under-Resonant Dual Bridge Series Resonant Converter. Trans. China Electrotech. Soc. 2024, 39, 4480–4494. [Google Scholar] [CrossRef]

- Wang, Q.; Sun, H.; Wang, C.; Wang, L. Optimal Control Strategy of DAB Converter Based on Frequency Domain Analysis. Power Electron. 2024, 58, 40–43. [Google Scholar] [CrossRef]

- Hu, Y.; Li, Z.; Zhao, C.; Luo, L.; Li, Y. Mechanism Analysis and Suppression of Oscillation in Dead Time of Series Resonant Dual Active Bridge Based on MOSFET. Trans. China Electrotech. Soc. 2022, 37, 2549–2558. [Google Scholar] [CrossRef]

- Xiao, Z.; He, Z.; Guan, R.; Luo, A. Piecewise-Approximated Time Domain Analysis of LLC Resonant Converter Considering Parasitic Capacitors and Deadtime. IEEE Trans. Power Electron. 2023, 38, 578–592. [Google Scholar] [CrossRef]

| Compensated Output Voltage | |||

|---|---|---|---|

| >0 | >0 | <0 | |

| <0 | <0 | >0 | |

| >0 | >0 | >0 | |

| <0 | <0 | <0 | |

| <0 | >0 | >0 | |

| <0 | >0 | <0 |

| Parameter | Value |

|---|---|

| Input voltage (V) | 42–58 |

| Output voltage (V) | 400 |

| Transformer turns ratio | 1:4 |

| Secondary Resonant inductance L (including leakage) (µH) | 25 |

| Secondary Resonant capacitor C (nF) | 110 |

| Switching frequency (kHz) | 70–220 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, Y.; Lei, J.; Jing, L.; Liu, J. Efficiency Optimization of a Series-Resonant Dual-Active-Bridge Converter with Voltage-Doubler Rectification. Energies 2025, 18, 6166. https://doi.org/10.3390/en18236166

Zhang Y, Lei J, Jing L, Liu J. Efficiency Optimization of a Series-Resonant Dual-Active-Bridge Converter with Voltage-Doubler Rectification. Energies. 2025; 18(23):6166. https://doi.org/10.3390/en18236166

Chicago/Turabian StyleZhang, Yongbo, Jianhua Lei, Long Jing, and Jingdou Liu. 2025. "Efficiency Optimization of a Series-Resonant Dual-Active-Bridge Converter with Voltage-Doubler Rectification" Energies 18, no. 23: 6166. https://doi.org/10.3390/en18236166

APA StyleZhang, Y., Lei, J., Jing, L., & Liu, J. (2025). Efficiency Optimization of a Series-Resonant Dual-Active-Bridge Converter with Voltage-Doubler Rectification. Energies, 18(23), 6166. https://doi.org/10.3390/en18236166