Numerical Study of the Impact of Inter-Die Thermal Conductance on the Thermal Performance of 3D ICs Cooled by a Single-Layer Microchannel Heat Exchanger

Abstract

1. Introduction

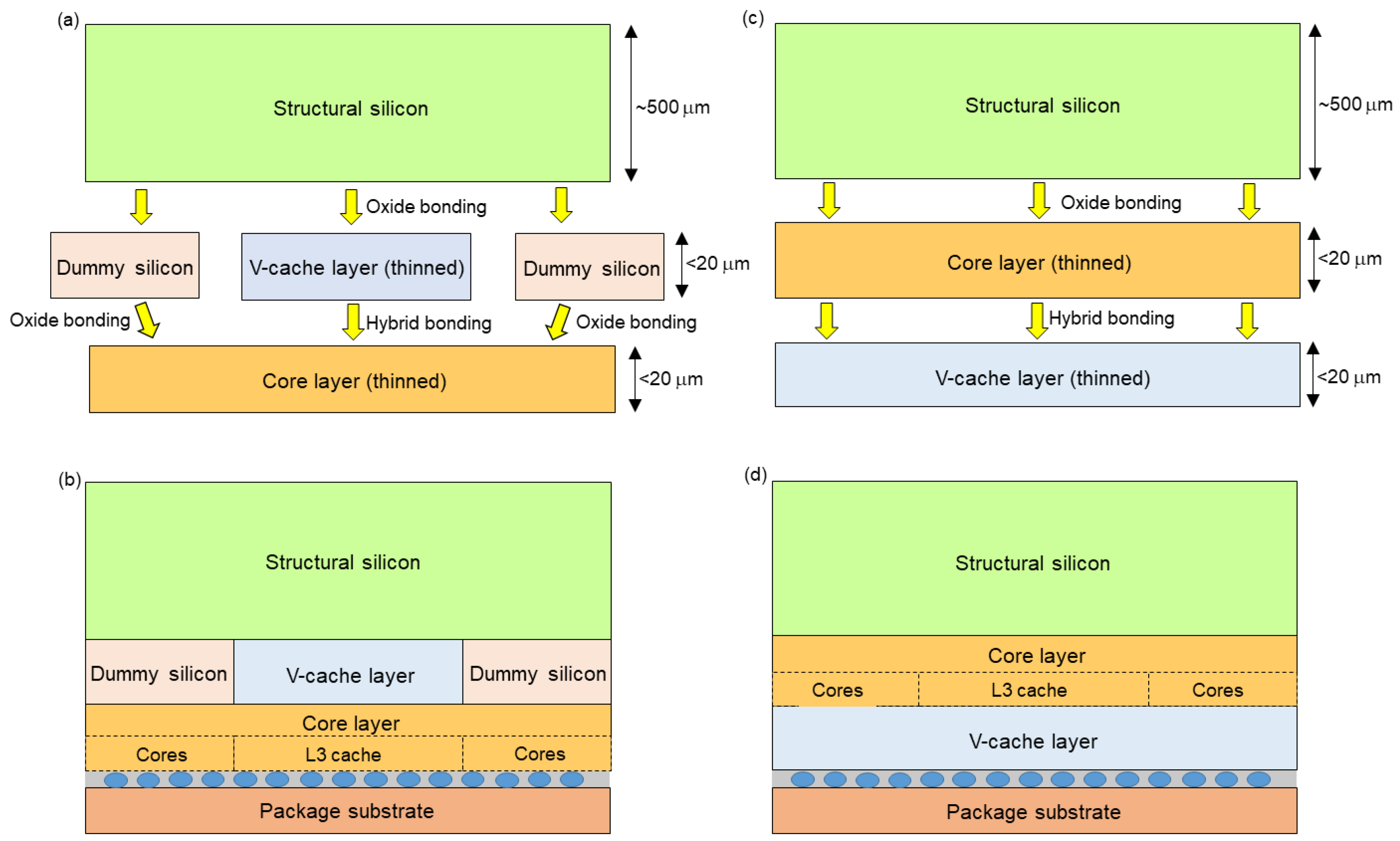

1.1. AMD’s 3D Processor Design with V-Cache

1.2. Microchannel Heat Exchanger as Future Solution for Cooling 3D Processors

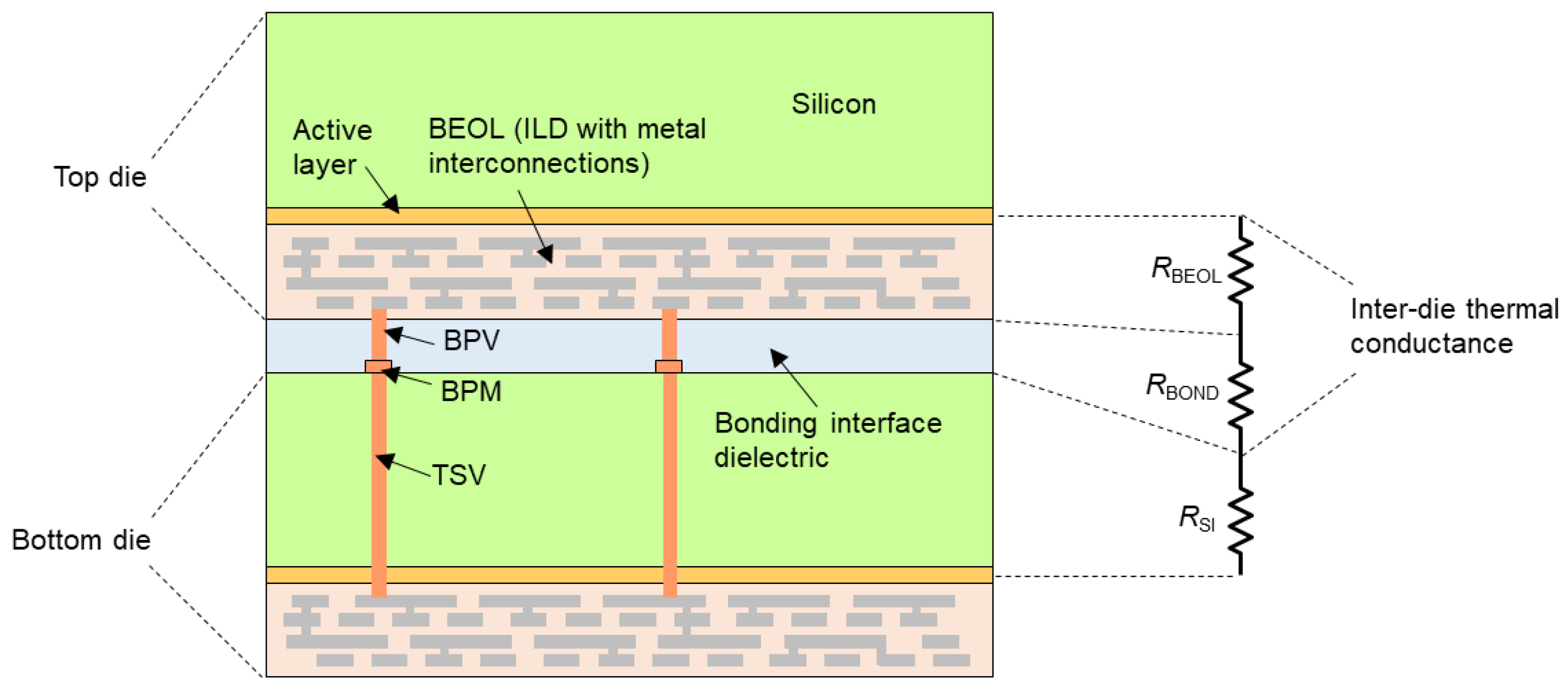

1.3. Inter-Die Thermal Conductance in 3D ICs

1.4. Motivation

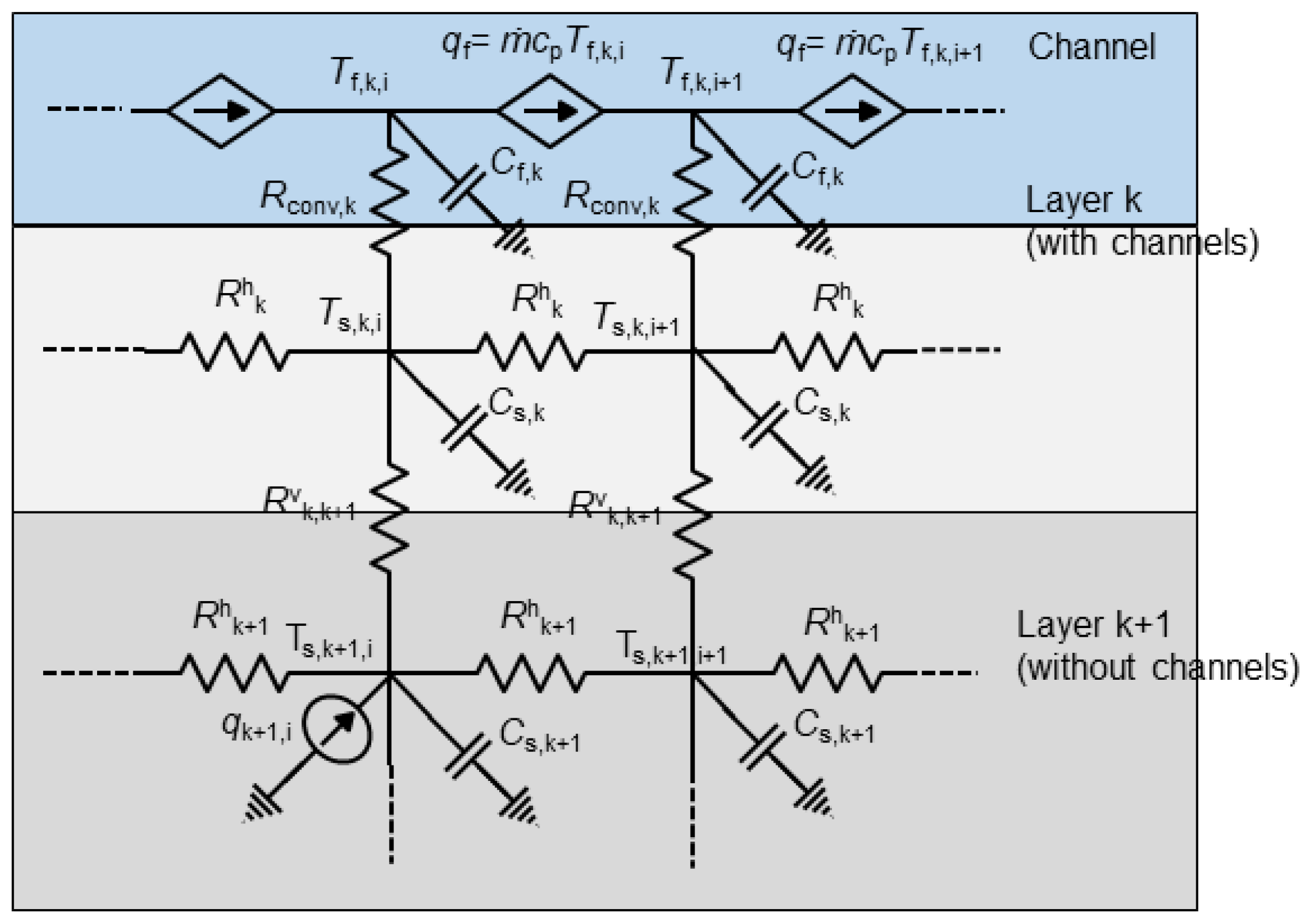

2. Simulation Methodology

2.1. Simulation Tool

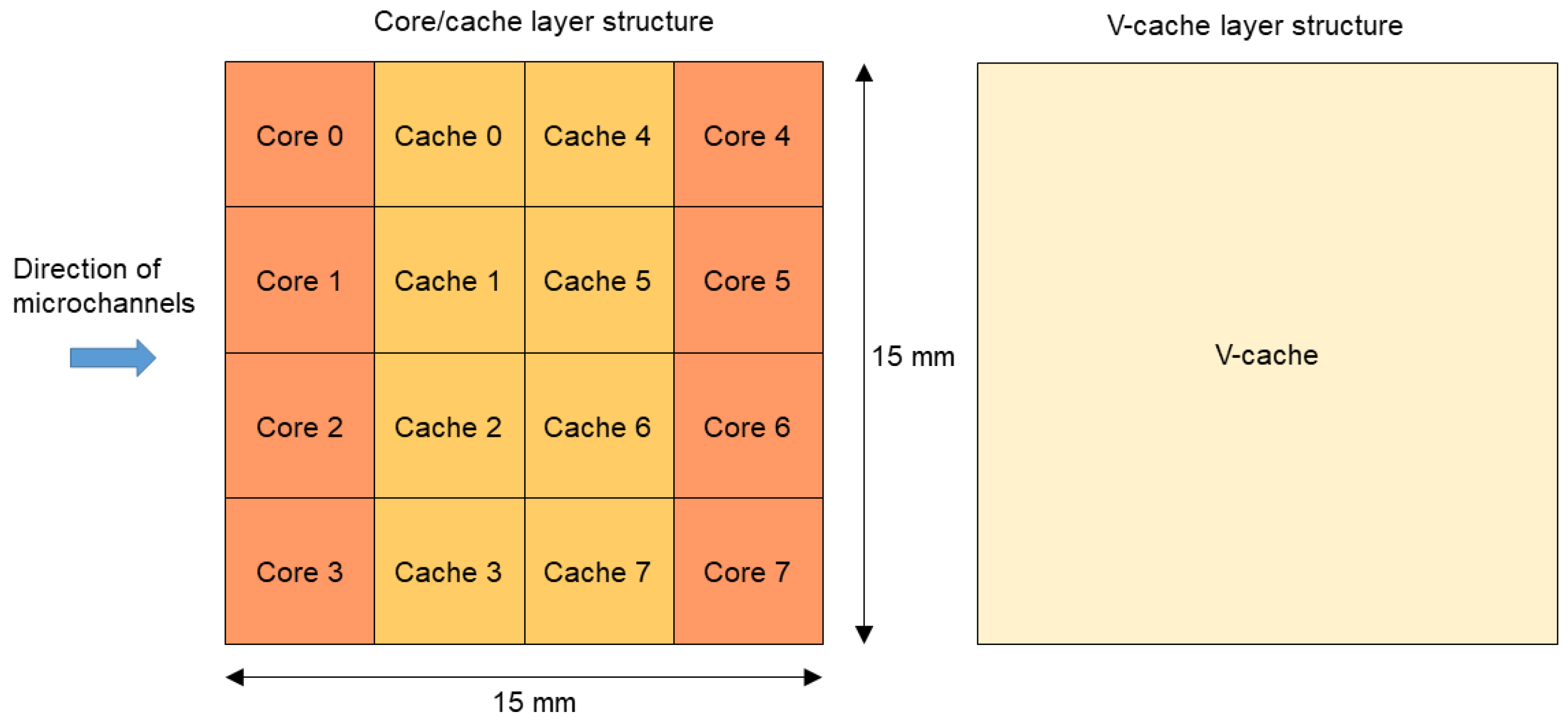

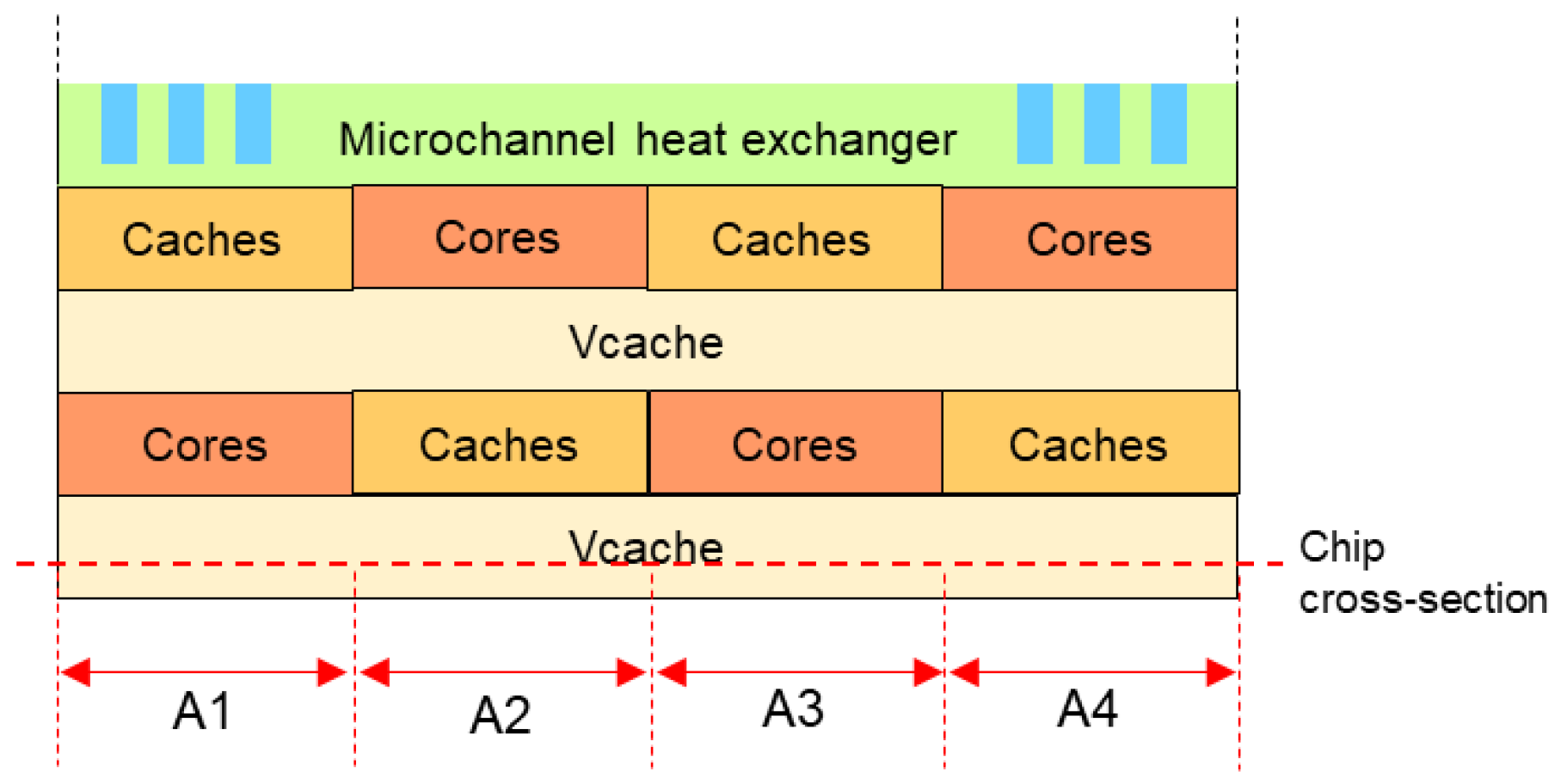

2.2. Simulated 3D Processor Stack

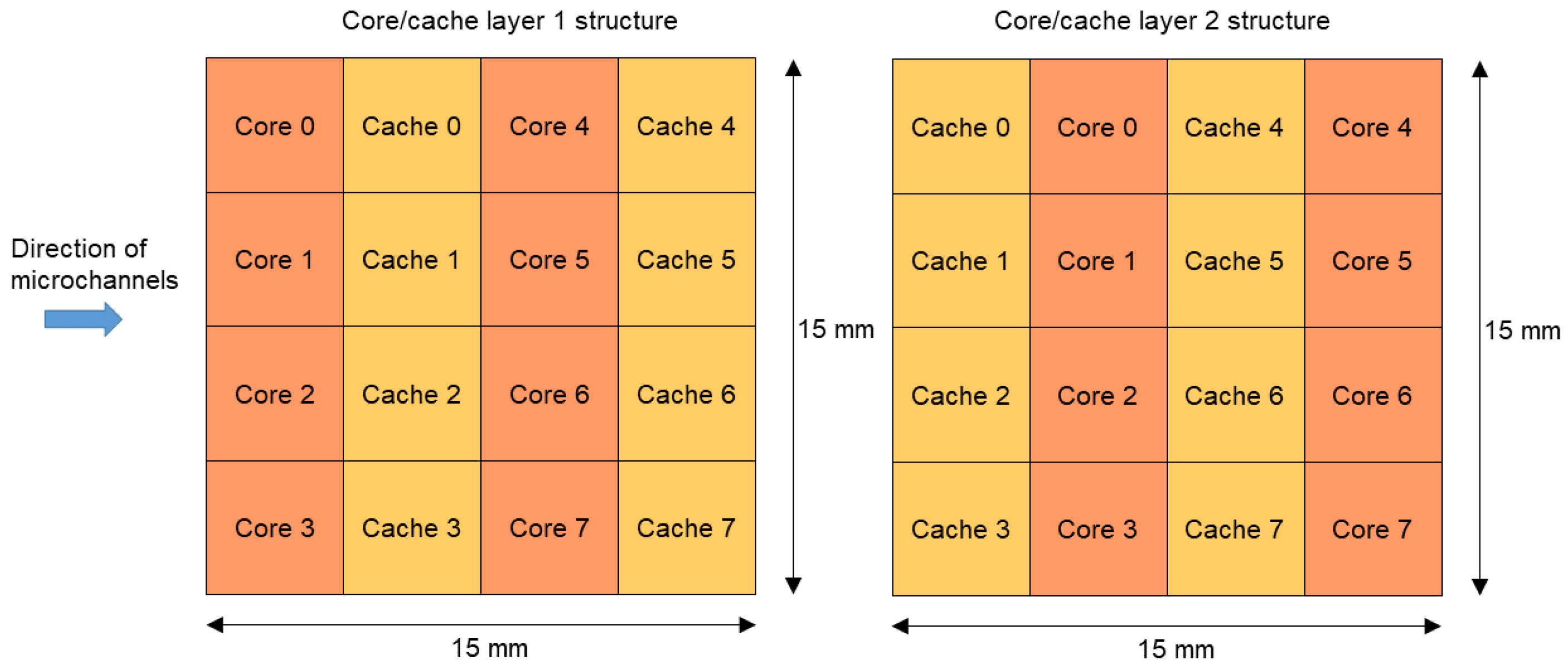

3. Results and Discussion

3.1. Analysis 1: The Impact of Inter-Die Thermal Conductance on Temperatures for Variable Inlet Fluid Velocity

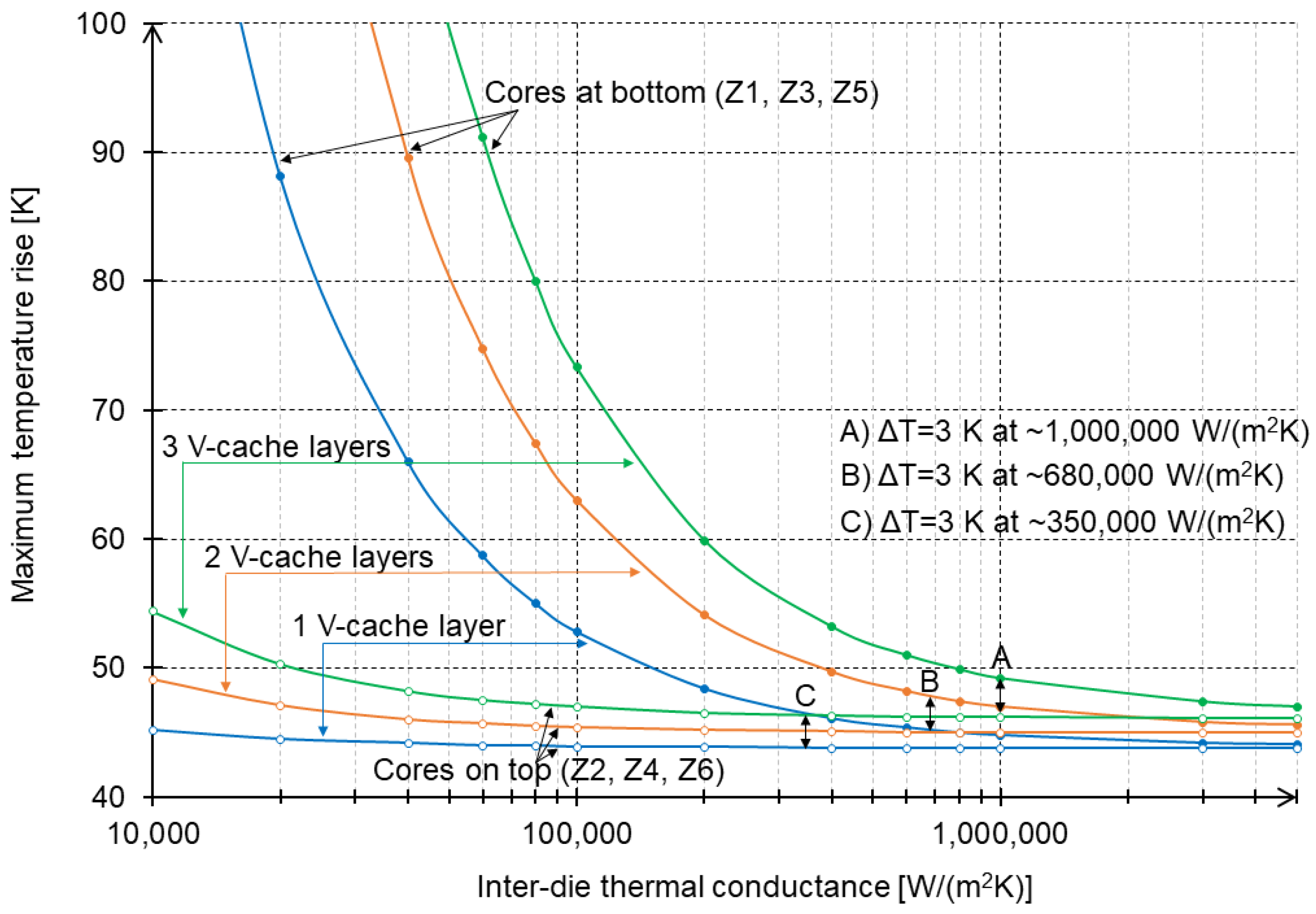

3.2. Analysis 2: The Impact of Inter-Die Thermal Conductance on Temperatures for Variable Number of Chip Dies

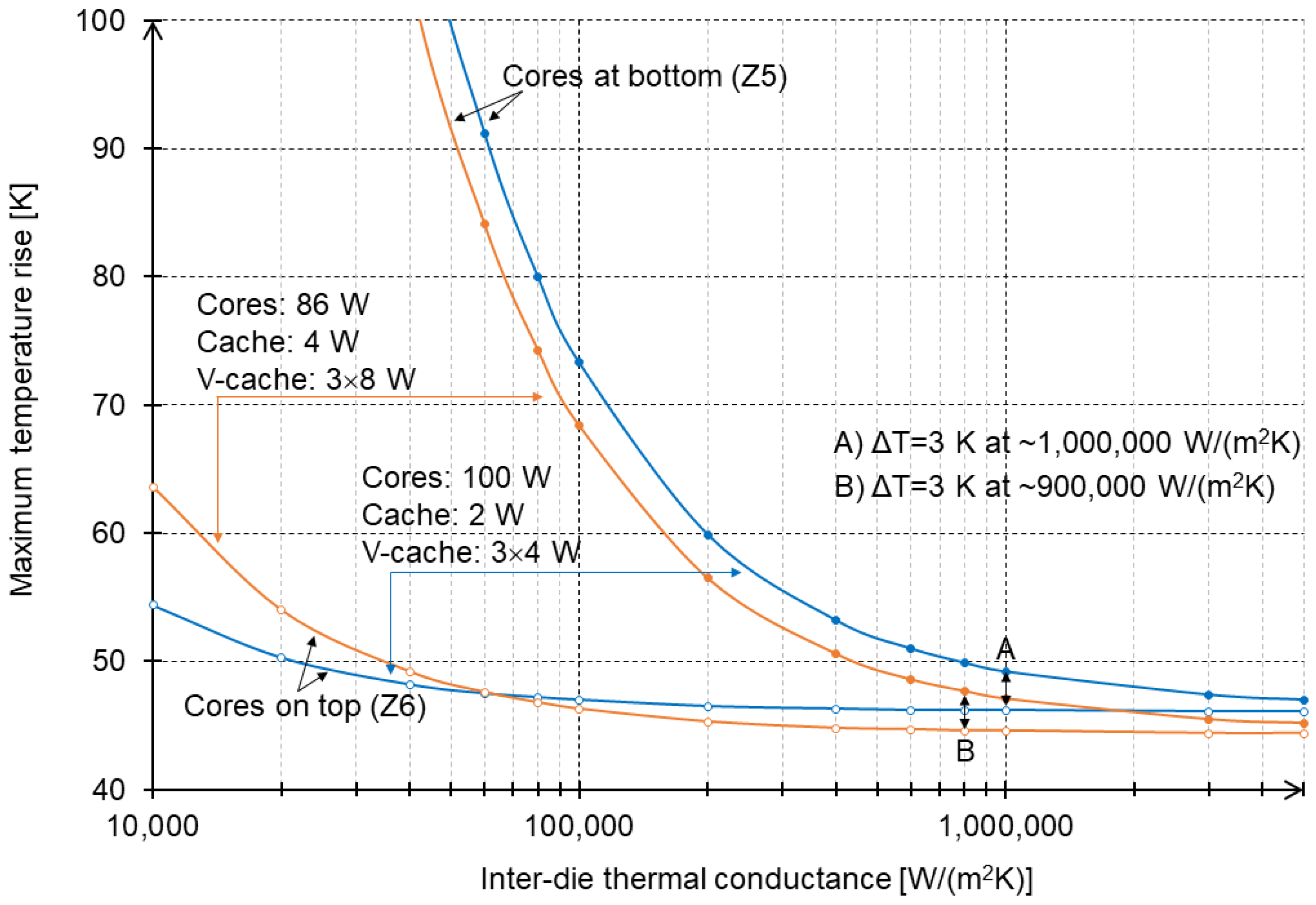

3.3. Analysis 3: The Impact of Inter-Die Thermal Conductance on Temperatures for Various Core/Cache Power Dissipation Breakdowns

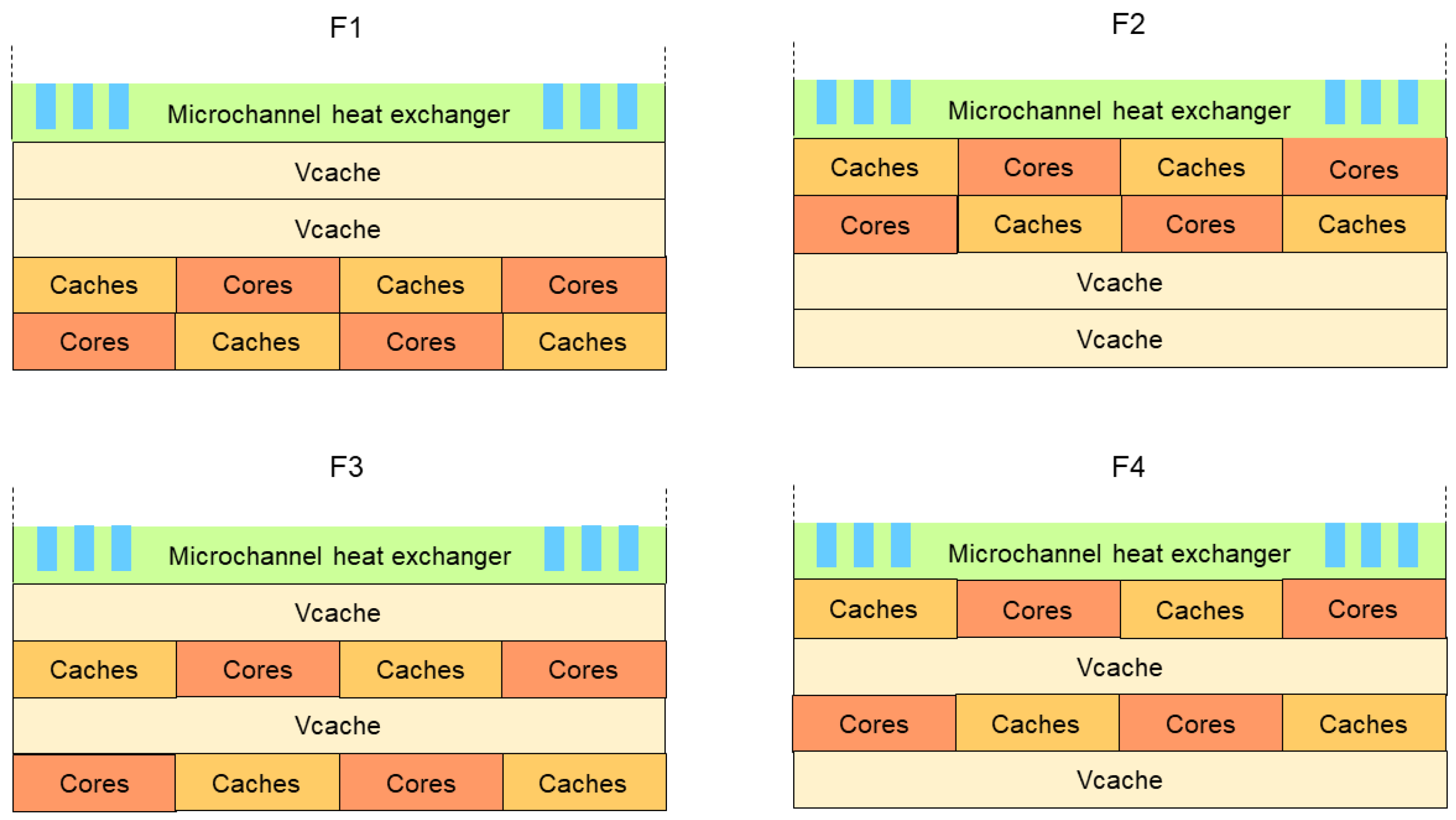

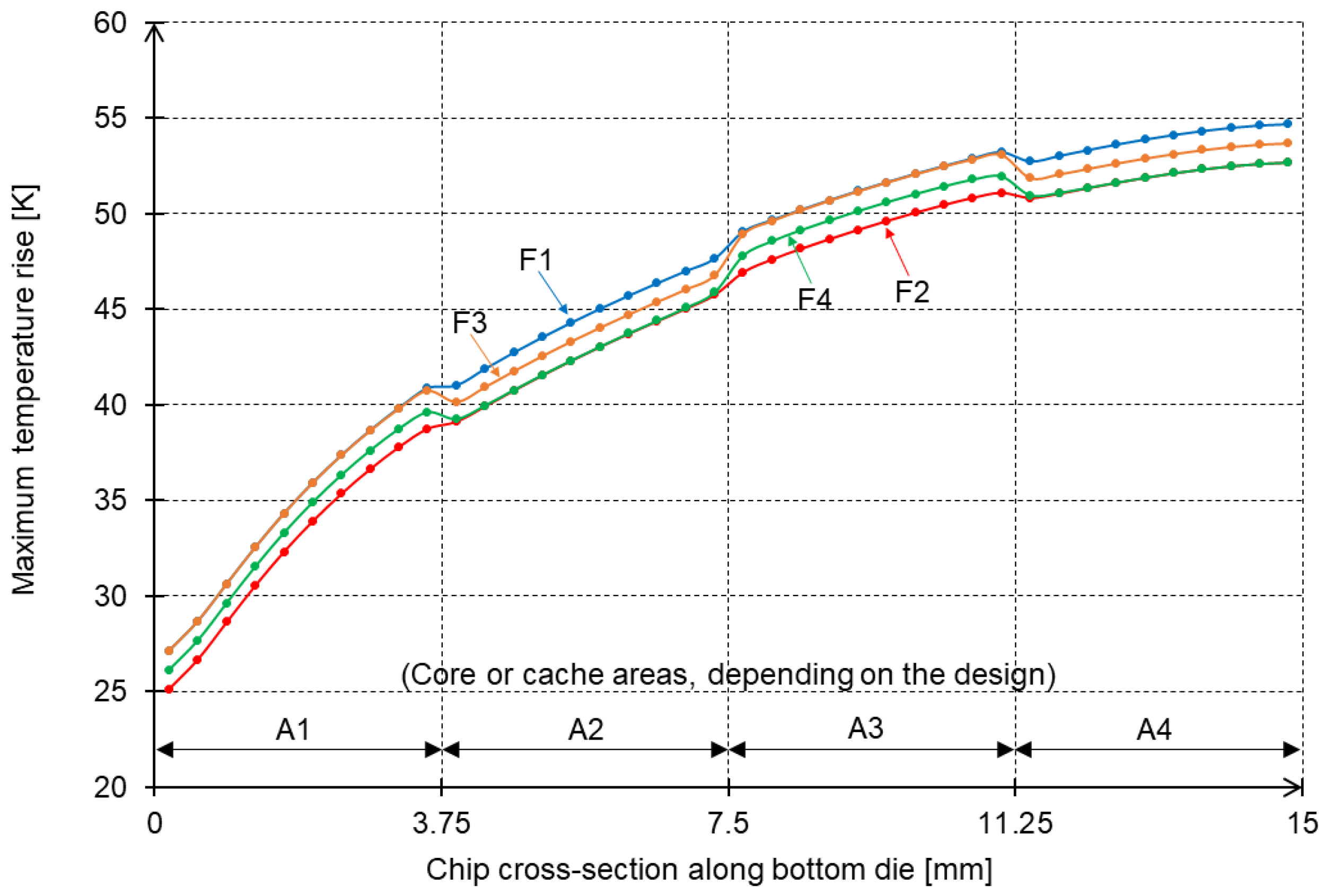

3.4. Analysis 4: The Impact of Inter-Die Thermal Conductance on Temperatures for Different Vertical Arrangements of Core and V-Cache Dies

3.5. Analysis 5: The Impact of Inter-Die Thermal Conductance on the Intensity of Local Temperature Hot Spots

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Beyne, E. The 3-D Interconnect Technology Landscape. IEEE Des. Test 2016, 33, 8–20. [Google Scholar] [CrossRef]

- Sharma, R. Design of 3D Integrated Circuits and Systems; CRC Press: Boca Raton, FL, USA, 2014. [Google Scholar]

- Zhang, X.; Lin, J.K.; Wickramanayaka, S.; Zhang, S.; Weerasekera, R.; Dutta, R.; Chang, K.F.; Chui, K.J.; Li, H.Y.; Wee Ho, D.S.; et al. Heterogeneous 2.5D integration on through silicon interposer. Appl. Phys. Rev. 2015, 2, 021308. [Google Scholar] [CrossRef]

- Kim, J.; Kim, Y. HBM: Memory solution for bandwidth-hungry processors. In Proceedings of the 2014 IEEE Hot Chips 26 Symposium (HCS), Cupertino, CA, USA, 10–12 August 2014; pp. 1–24. [Google Scholar] [CrossRef]

- Sohn, K.; Yun, W.J.; Oh, R.; Oh, C.S.; Seo, S.Y.; Park, M.S.; Shin, D.H.; Jung, W.C.; Shin, S.H.; Ryu, J.M.; et al. A 1.2 V 20 nm 307 GB/s HBM DRAM With At-Speed Wafer-Level IO Test Scheme and Adaptive Refresh Considering Temperature Distribution. IEEE J. Solid-State Circuits 2017, 52, 250–260. [Google Scholar] [CrossRef]

- Wuu, J.; Agarwal, R.; Ciraula, M.; Dietz, C.; Johnson, B.; Johnson, D.; Schreiber, R.; Swaminathan, R.; Walker, W.; Naffziger, S. 3D V-Cache: The Implementation of a Hybrid-Bonded 64MB Stacked Cache for a 7nm x86-64 CPU. In Proceedings of the 2022 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 20–26 February 2022; Volume 65, pp. 428–429. [Google Scholar] [CrossRef]

- Ingerly, D.B.; Amin, S.; Aryasomayajula, L.; Balankutty, A.; Borst, D.; Chandra, A.; Cheemalapati, K.; Cook, C.S.; Criss, R.; Enamul, K.; et al. Foveros: 3D Integration and the use of Face-to-Face Chip Stacking for Logic Devices. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 19.6.1–19.6.4. [Google Scholar] [CrossRef]

- Lu, T.; Serafy, C.; Yang, Z.; Samal, S.K.; Lim, S.K.; Srivastava, A. TSV-Based 3-D ICs: Design Methods and Tools. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2017, 36, 1593–1619. [Google Scholar] [CrossRef]

- Abdullah, M.; Lee, H. Technology review of CNTs TSV in 3D IC and 2.5D packaging: Progress and challenges from an electrical viewpoint. Microelectron. Eng. 2024, 290, 112189. [Google Scholar] [CrossRef]

- Kim, J.; Zhu, L.; Torun, H.M.; Swaminathan, M.; Lim, S.K. Micro-bumping, Hybrid Bonding, or Monolithic? A PPA Study for Heterogeneous 3D IC Options. In Proceedings of the 2021 58th ACM/IEEE Design Automation Conference (DAC), San Francisco, CA, USA, 5–9 December 2021; pp. 1189–1194. [Google Scholar] [CrossRef]

- Evers, M.; Barnes, L.; Clark, M. The AMD Next-Generation “Zen 3” Core. IEEE Micro 2022, 42, 7–12. [Google Scholar] [CrossRef]

- Elsherbini, A.; Liff, S.; Swan, J.; Jun, K.; Tiagaraj, S.; Pasdast, G. Hybrid Bonding Interconnect for Advanced Heterogeneously Integrated Processors. In Proceedings of the 2021 IEEE 71st Electronic Components and Technology Conference (ECTC), Virtual, 1 June–4 July 2021; pp. 1014–1019. [Google Scholar] [CrossRef]

- Arnaud, L.; Moreau, S.; Jouve, A.; Jani, I.; Lattard, D.; Fournel, F.; Euvrard, C.; Exbrayat, Y.; Balan, V.; Bresson, N.; et al. Fine pitch 3D interconnections with hybrid bonding technology: From process robustness to reliability. In Proceedings of the 2018 IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, USA, 11–15 March 2018; pp. 4D.4-1–4D.4-7. [Google Scholar] [CrossRef]

- Kim, Y.; Kim, J.; Kim, H.; Lee, H.; Kim, D.; Seo, S.K.; Jo, C.; Kim, D.W. Die to Wafer Hybrid Cu Bonding for Fine Pitch 3D-IC Applications. In Proceedings of the 2023 IEEE 73rd Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2023; pp. 1043–1047. [Google Scholar] [CrossRef]

- Kim, S.W.; Detalle, M.; Peng, L.; Nolmans, P.; Heylen, N.; Velenis, D.; Miller, A.; Beyer, G.; Beyne, E. Ultra-Fine Pitch 3D Integration Using Face-to-Face Hybrid Wafer Bonding Combined with a Via-Middle Through-Silicon-Via Process. In Proceedings of the 2016 IEEE 66th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 31 May–3 June 2016; pp. 1179–1185. [Google Scholar] [CrossRef]

- Guo, F.; Suo, Z.J.; Xi, X.; Bi, Y.; Li, T.; Wang, C.; Su, K.; Zou, X.; Li, R. Recent Developments in Thermal Management of 3D ICs: A Review. IEEE Access 2025, 13, 94286–94301. [Google Scholar] [CrossRef]

- Wang, S.; Yin, Y.; Hu, C.; Rezai, P. 3D Integrated Circuit Cooling with Microfluidics. Micromachines 2018, 9, 287. [Google Scholar] [CrossRef] [PubMed]

- Bianco, N.; Cherella, N.; Fragnito, A.; Iasiello, M.; Mauro, G.M. Multi-material topology optimization of innovative microchannel heat sinks equipped with metal foams. Int. J. Heat Mass Transf. 2024, 222, 125201. [Google Scholar] [CrossRef]

- Zając, P. Compact Thermal Modelling Tool for Fast Design Space Exploration of 3D ICs with Integrated Microchannels. Energies 2020, 13, 2217. [Google Scholar] [CrossRef]

- Brunschwiler, T.; Michel, B.; Rothuizen, H.; Kloter, U.; Wunderle, B.; Oppermann, H.; Reichl, H. Forced convective interlayer cooling in vertically integrated packages. In Proceedings of the 2008 11th Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems, Orlando, FL, USA, 28–31 May 2008; pp. 1114–1125. [Google Scholar] [CrossRef]

- Shi, B.; Srivastava, A.; Bar-Cohen, A. Co-design of micro-fluidic heat sink and thermal through-silicon-vias for cooling of three-dimensional integrated circuit. IET Circuits Devices Syst. 2013, 7, 223–231. [Google Scholar] [CrossRef]

- Wang, J.; Duan, F.; Lv, Z.; Chen, S.; Yang, X.; Chen, H.; Liu, J. A Short Review of Through-Silicon via (TSV) Interconnects: Metrology and Analysis. Appl. Sci. 2023, 13, 8301. [Google Scholar] [CrossRef]

- Chen, X.; Chen, Z.; Xiao, L.; Hao, Y.; Wang, H.; Ding, Y.; Zhang, Z. Fabrication and Electrical Characterization of High Aspect Ratio Through-Silicon Vias with Polyimide Liner for 3D Integration. Micromachines 2022, 13, 1147. [Google Scholar] [CrossRef] [PubMed]

- Biswal, L.; Chakraborty, S.; Som, S.K. Design and Optimization of Single-Phase Liquid Cooled Microchannel Heat Sink. IEEE Trans. Components Packag. Technol. 2009, 32, 876–886. [Google Scholar] [CrossRef]

- Ren, Z.; Alqahtani, A.; Bagherzadeh, N.; Lee, J. Thermal TSV Optimization and Hierarchical Floorplanning for 3-D Integrated Circuits. IEEE Trans. Components Packag. Manuf. Technol. 2020, 10, 599–610. [Google Scholar] [CrossRef]

- Qu, C.; Dai, R.; Zheng, J.; Hu, Y.; Zhang, J. Thermal and mechanical reliability of thermal through-silicon vias in three-dimensional integrated circuits. Microelectron. Reliab. 2023, 143, 114952. [Google Scholar] [CrossRef]

- Cong, J.; Zhang, Y. Thermal via planning for 3-D ICs. In Proceedings of the ICCAD-2005, IEEE/ACM International Conference on Computer-Aided Design, San Jose, CA, USA, 6–10 November 2005; pp. 745–752. [Google Scholar] [CrossRef]

- Zając, P.; Janicki, M.; Napieralski, A. On the applicability of single-layer integrated microchannel cooling in 3D ICs. In Proceedings of the 2018 19th International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems (EuroSimE), Toulouse, France, 15–18 April 2018; pp. 1–6. [Google Scholar] [CrossRef]

- Zając, P. TIMiTIC: A C++ based Compact Thermal Simulator for 3D ICs with Microchannel Cooling. In Proceedings of the 2019 25th International Workshop on Thermal Investigations of ICs and Systems (THERMINIC), Lecco, Italy, 25–27 September 2019; pp. 1–6. [Google Scholar] [CrossRef]

- Guennebaud, G.; Jacob, B.; Avery, P.; Bachrach, A.; Barthelemy, S. Eigen v3. Available online: http://eigen.tuxfamily.org (accessed on 3 June 2024).

- Bennett, T.D. Correlations for the Graetz problem in convection—Part 1: For round pipes and parallel plates. Int. J. Heat Mass Transf. 2019, 136, 832–841. [Google Scholar] [CrossRef]

| Parameter | Value |

|---|---|

| Chip area | 15 mm × 15 mm |

| Number of microchannels | 40 |

| Microchannel width | 250 µm |

| Microchannel height | 400 µm |

| Fluid velocity | 0.5 m/s (unless otherwise specified) |

| Inlet fluid temperature | 300 K |

| Ambient air temperature | 300 K |

| Chip die thickness | 20 µm |

| Heat exchanger layer thickness | 600 µm |

| TIM thickness | 60 µm |

| Heat spreader thickness | 1000 µm |

| Top chip convection coefficient | 10 W/(m2 K) |

| Bottom chip convection coefficient | 1 W/(m2 K) |

| Number of nodes per layer | 40 × 40 = 1600 |

| Heat exchanger bottom thermal contact conductance | 106 W/(m2 K) |

| Inter-die thermal conductance | variable |

| Power dissipation per layer (cores) | 8 × 12.5 W (unless otherwise specified) |

| Power dissipation per layer (caches) | 8 × 0.25 W (unless otherwise specified) |

| Power dissipation per layer (V-caches) | 4 W (unless otherwise specified) |

| Cooling fluid | water, k = 0.591 W/(mK), = 1000 kg/(m3), = 4184 J/(kgK), = 0.000653 Ns/(m2), = 3.56 |

| Chip layer material | silicon, k = 130 W/(mK), = 2330 kg/(m3), = 700 J/(kgK) |

| TIM material | k = 2 W/(mK), = 2000 kg/(m3), = 700 J/(kgK) |

| Heat spreader material | copper, k = 400 W/(mK), = 8960 kg/(m3), = 385 J/(kgK) |

| Location | Boundary Condition |

|---|---|

| Top chip surface | Convective (constant HTC) |

| Bottom chip surface | Convective (constant HTC) |

| Side chip walls | Adiabatic |

| Microchannel inlets | Isothermal |

| Microchannel outlets | Zero gradient (convective outflow) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zając, P.; Zabierowski, W. Numerical Study of the Impact of Inter-Die Thermal Conductance on the Thermal Performance of 3D ICs Cooled by a Single-Layer Microchannel Heat Exchanger. Energies 2025, 18, 6150. https://doi.org/10.3390/en18236150

Zając P, Zabierowski W. Numerical Study of the Impact of Inter-Die Thermal Conductance on the Thermal Performance of 3D ICs Cooled by a Single-Layer Microchannel Heat Exchanger. Energies. 2025; 18(23):6150. https://doi.org/10.3390/en18236150

Chicago/Turabian StyleZając, Piotr, and Wojciech Zabierowski. 2025. "Numerical Study of the Impact of Inter-Die Thermal Conductance on the Thermal Performance of 3D ICs Cooled by a Single-Layer Microchannel Heat Exchanger" Energies 18, no. 23: 6150. https://doi.org/10.3390/en18236150

APA StyleZając, P., & Zabierowski, W. (2025). Numerical Study of the Impact of Inter-Die Thermal Conductance on the Thermal Performance of 3D ICs Cooled by a Single-Layer Microchannel Heat Exchanger. Energies, 18(23), 6150. https://doi.org/10.3390/en18236150