1. Introduction

Fault self-healing in intelligent distribution networks is a key technology for smart grids [

1]. As a crucial component of smart grids, flexibly interconnected DC distribution networks rely on the rapid operation of section switches and tie switches within the DC network to achieve efficient reconfiguration of load transfer paths and the formation of planned islands [

2,

3,

4]. However, traditional circuit breaker-based section and tie switches are incapable of achieving millisecond-level fault self-healing in intelligent distribution networks. Therefore, there is an urgent need to research novel DC circuit breaker topologies to enable rapid circuit closing and breaking actions [

5,

6,

7].

Achieving fast operation in DC circuit breakers primarily involves addressing the following two challenges:

1. Adaptive connection of current-limiting components: Direct installation of inductor-based current limiters in the main circuit can cause system operating point drift, increasing instability risks [

8]. It can also induce voltage oscillations during system transients, amplifying transient voltage peaks [

9]. Thus, implementing adaptive connection of current-limiting inductors is critical to minimize system oscillation risks.

2. Rapid isolation of faulted lines: The fault isolation speed of a DC circuit breaker is constrained by the fault detection delay time and the fault current clearing time [

10]. The fault detection delay depends on the detection algorithm, while fault current clearing depends on the design of the breaker’s energy dissipation circuit. Consequently, achieving efficient energy dissipation within a breaker to shorten the fault current clearing time is a vital aspect of circuit breaker topology design.

However, traditional DC circuit breakers struggle to achieve both adaptive connection of current limiters and rapid isolation of faulted lines. The difficulties include the following two points:

On the one hand, DC circuit breakers can be classified into three types based on their interruption principles and structural characteristics: mechanical DC circuit breakers (MCBs) [

11], solid-state circuit breakers (SSCBs) [

12], and hybrid circuit breakers (HCBs) [

13,

14,

15]. MCBs rely on mechanical contacts to interrupt the current, achieving interruption by creating an artificial current zero and being equipped with arc-extinguishing devices [

16]. SSCBs utilize solid-state switching elements to achieve arc-less fast tripping [

17]. HCBs achieve interruption through a composite structure combining mechanical switches with solid-state switching elements [

18]. However, traditional DC circuit breakers directly connecting the current-limiting inductor to the main circuit increase the risk of oscillations. Solid-State Fault Current Limiters (SSFCLs) [

19] can achieve fault current limiting without relying on current-limiting inductors. Compared with mechanical circuit breakers and hybrid circuit breakers, solid-state circuit breakers offer the fastest breaking/opening speed, have no physically separating mechanical contacts (eliminating arc formation), and possess an extremely high operating frequency, enabling them to withstand extremely frequent opening and closing operations. This limiting method implements fault current limiting within an extremely short time after a fault occurs by adding solid-state elements to the circuit, thereby reducing the risk of system oscillations. Nevertheless, the inclusion of solid-state elements also results in higher steady-state losses in the circuit breaker [

20]. Therefore, achieving adaptive (on-demand) connection of the current limiter—such that it does not increase system oscillation risk under normal conditions but automatically engages upon fault occurrence to perform its current-limiting function—represents a significant challenge in the design of novel DC circuit breaker topologies.

On the other hand, employing inductors for current limiting in DC lines can address the issue of high fault current rise rates [

21]. However, since the inductor stores inductive energy during the current-limiting process, it requires coordination with a Metal Oxide Varistor (MOV) for energy dissipation [

22]. The effectiveness of this energy dissipation depends on the MOV’s capacity and its own parameter design. Crucially, this approach has limited energy handling capability and cannot perform continuous interruptions; each interruption operation requires a cooling interval of over half an hour. Superconducting Fault Current Limiters (SFCLs) are suitable for large-scale power grids and high-load conditions [

23]. Upon fault occurrence, the superconducting material within an SFCL enters a quenching state due to the increased fault current, rapidly generating high resistance to limit the current peak. This significantly increases the fault current clearing speed. However, the superconducting material relies on additional cooling systems, substantially increasing the physical footprint and the cost for practical applications. Positive Temperature Coefficient (PTC) thermistors can address issues of overload protection and fast recovery based on a similar principle [

24]. While both SFCLs and PTC devices avoid the need to dissipate stored inductive energy after a fault, their return to the normal-state temperature after fault isolation depends on additional cooling systems.

To meet the requirements for adaptive connection and rapid isolation in DC circuit breakers, this paper proposes a topology design scheme based on a symmetrical full-bridge solid-state circuit breaker (SSCB). Its primary innovations are as follows:

1. To address the issue of oscillations induced by power flow variations during normal system operation in circuit breakers employing inductive current limiting, this paper proposes a circuit breaker topology with adaptive commutation capability. Compared to traditional solid-state circuit breakers (SSCBs), this topology enables the current-limiting inductor to remain disconnected from the system under normal conditions and automatically connect to the system upon fault occurrence. This effectively mitigates the system oscillation risk.

2. To address the issues of energy dissipation delay and limited isolation speed inherent in traditional fault isolation schemes relying on Metal Oxide Varistors (MOVs), this paper proposes an auxiliary energy dissipation scheme based on an energy dissipation circuit (EDC). This scheme enables the release of current-limiting inductor energy through an independent EDC loop after fault tripping. By connecting an MOV in parallel across the IGBT for voltage stabilization, it significantly shortens the faulted line isolation time. Compared to traditional MOV-dependent schemes (which exhibit an isolation delay of 3 ms), the proposed energy dissipation scheme can compress the fault isolation time to less than 0.1 ms, achieving microsecond-level rapid isolation. Concurrently, it reduces the thermal runaway risk of the MOV during the fault isolation process, effectively enhancing both the safety and response speed of circuit breaker tripping.

3. Simulation Verification

3.1. Simulation Platform Construction

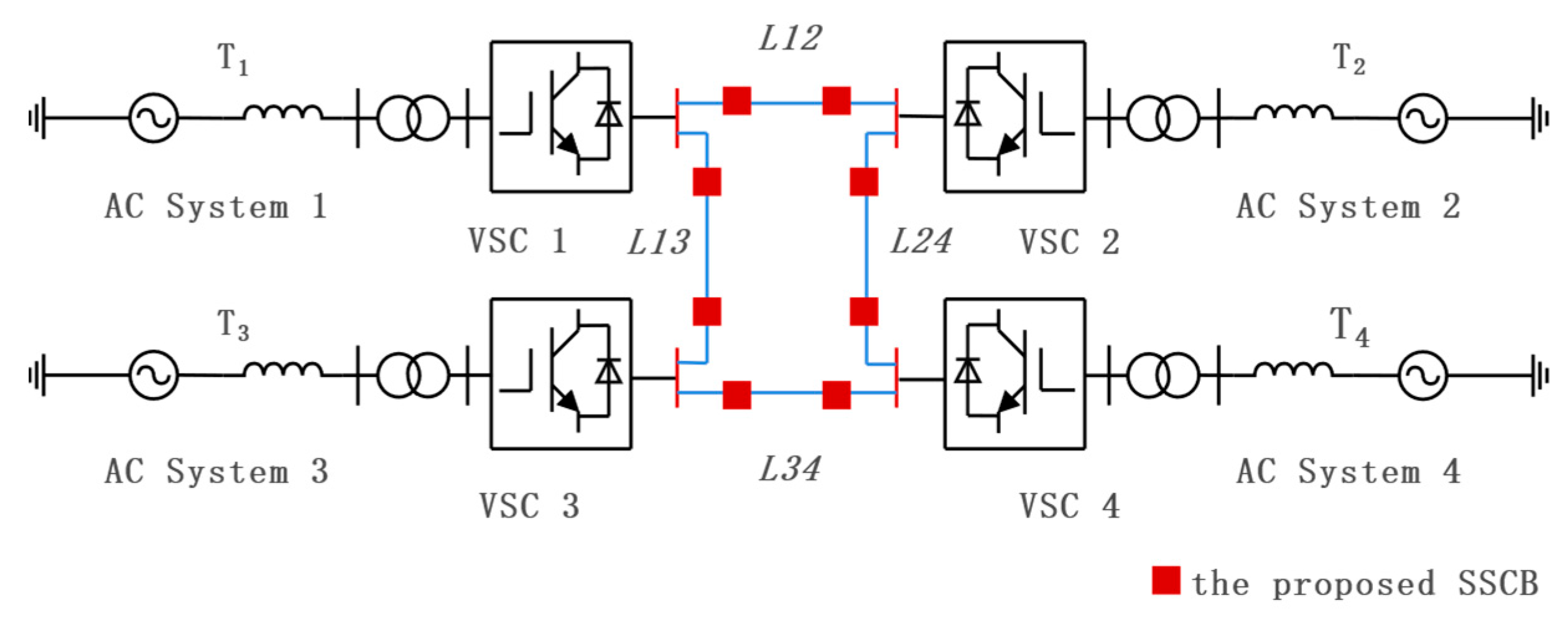

A four-terminal VSC-MTDC system was established in a SIMULINK real-time simulator, as shown in

Figure 5. The main system parameters are listed in

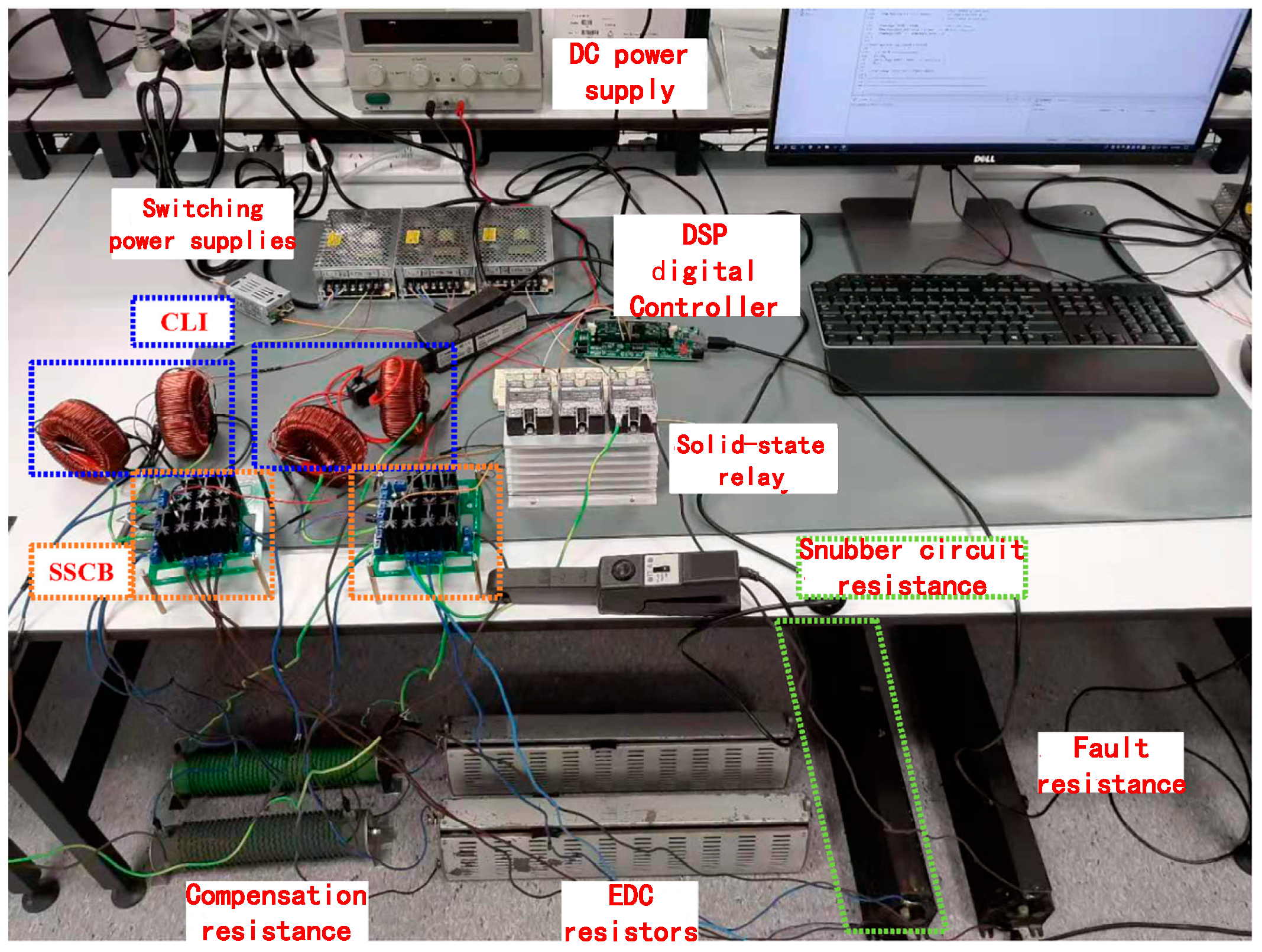

Table 1. Solid-state circuit breakers (SSCBs) were installed at the DC line terminals, and the simulation primarily demonstrated pole-to-pole (PP) faults and load variations.

The steady-state DC line current was maintained at 2.6 A. Pole-to-pole (PP) faults were generated by a DC solid-state relay (SSR). According to university laboratory safety requirements, the maximum fault current needed to be limited to less than 25 A. Nevertheless, this range was analogous to typical fault currents in low-voltage DC systems (i.e., 63 A). Furthermore, the primary objective of this study was to characterize the SSCB’s performance; thus, greater emphasis was placed on the fault current waveform profile. Building upon this work, future research will extend it to testing in industrial-scale installations.

While the detailed analysis focused on the fault current waveform profile (magnitude, di/dt, etc.) as a key indicator of SSCB performance during the initial fault interruption phase, it is crucial to acknowledge the fundamental physical significance of the subsequent switching process, particularly concerning the Transient Recovery Voltage (TRV). Following successful current interruption by the SSCB, the TRV is the voltage transient that appears across its opening contacts. This voltage stresses the newly formed gap and is critical for determining whether the interruption is ultimately successful (arc does not re-ignite) or fails.

The magnitude and wave shape of the TRV were governed by the system’s inherent parameters (inductance, capacitance, and resistance) and the magnitude of the interrupted current. Crucially, the physical implications of the TRV scale dramatically with system voltage and current levels. A TRV of 10 V across a contact gap interrupting 10 A presents negligible stress on insulation and poses minimal re-ignition risk. In stark contrast, a TRV reaching 100 kV across contacts interrupting 10 kA imposes extreme dielectric stress, demanding sophisticated contact design (e.g., larger gaps, arc chutes, and vacuum/SF6 insulation) and precise control to manage the intense electric field and prevent destructive re-strikes. Similarly, interrupting 10 kA generates vastly higher electromagnetic forces, contact erosion, and arc energy compared to interrupting 10 A, fundamentally altering the stresses on the switching device.

Therefore, while the present study utilized RTDS and focused on characterizing SSCB behavior under the constrained, low-energy conditions (25 A max fault current and the low system voltage implied by the TRV levels achievable in this setup) pertinent to the laboratory safety scale and analogous low-voltage DC applications, we explicitly recognize that scaling to industrial-level voltages (hundreds of V to kV) and fault currents (kA range) introduces orders-of-magnitude greater challenges. The TRV becomes a dominant factor requiring careful design consideration, and the physical phenomena (electromagnetic forces, arc plasma dynamics, and dielectric recovery) during the interruption and the TRV phase become significantly more intense and complex. Future work targeting industrial applications will necessitate dedicated investigations of SSCB performance under these high-stress TRV and high-current interruption conditions.

3.2. Analysis of Simulation Results

3.2.1. Fault Clearing Simulation Analysis

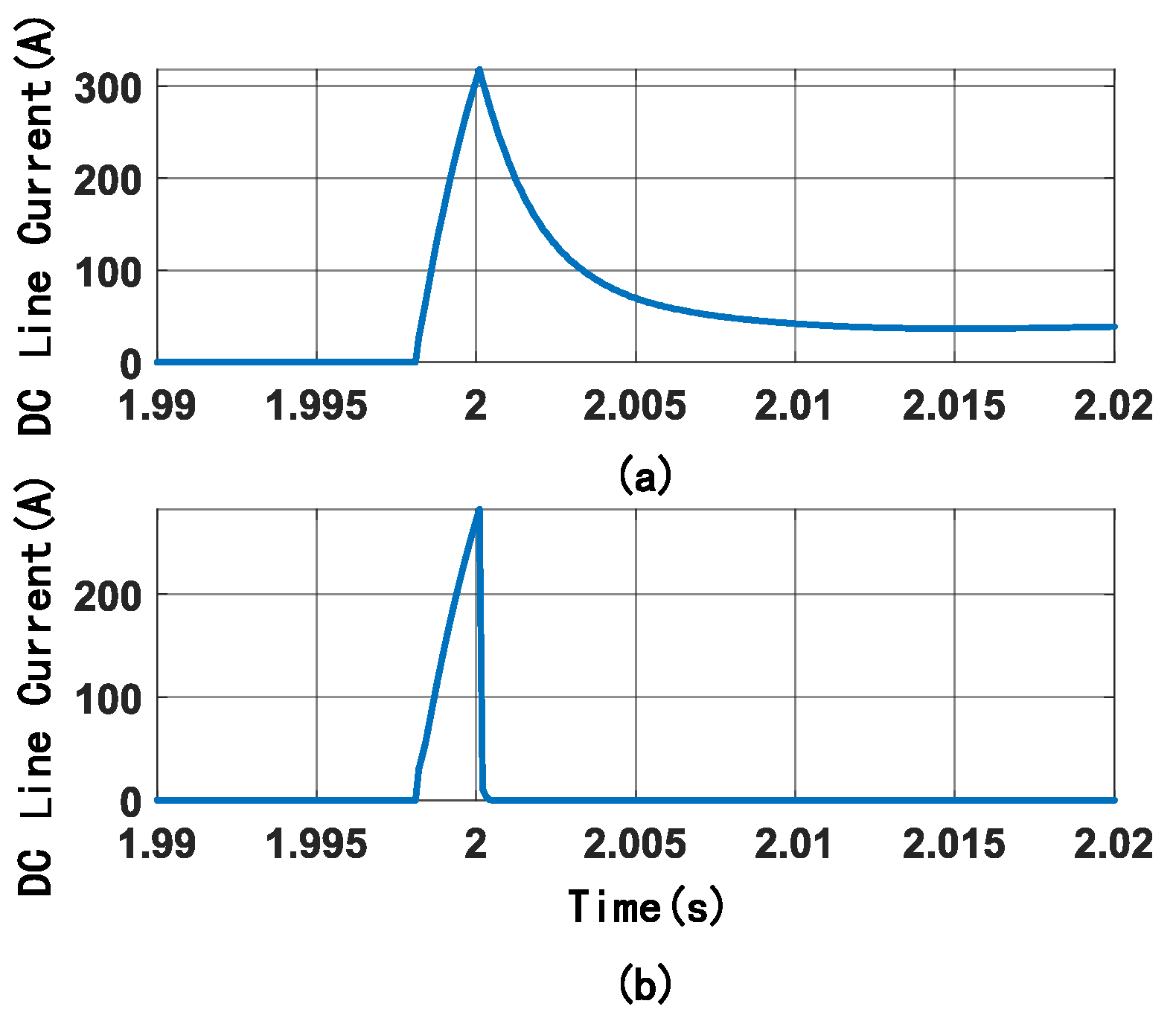

The SSCB designed in this paper was set to initiate a fault signal at 1.998 s. The current in the DC circuit path is shown in

Figure 6. As can be seen in the figure, the current started to drop abruptly after a 0.02 s delay post-fault. This was because the current-limiting branch incorporated a DC bias source. The current-limiting effect was only activated when the fault current exceeded the DC bias current, causing IGBT S3 to interrupt. This action thus altered the current path, interrupting the fault current after it reached its peak.

Furthermore, as shown in

Figure 6, the fault current in the mutual-inductor-based current-limiting scheme exhibited a gradual decline due to the inductance restricting abrupt current changes, resulting in an excessively long current-limiting period. In contrast, the fault current in the designed SSCB demonstrated a nearly vertical slope during its descent, significantly reducing the fault isolation time.

3.2.2. Current-Limiting Simulation Analysis

Under conditions without triggering tripping, a functional comparison of the two current-limiting methods was conducted. As shown in

Figure 7, both the mutual-inductor-based current-limiting scheme and the designed SSCB current-limiting method could effectively suppress diode current disturbances and active power disturbances in VSC1, as well as reduce the peak current in the faulted line. The figure reveals no significant visual difference between the waveforms produced by the mutual-inductor-based scheme and the designed SSCB method. However, these two distinct current-limiting approaches exhibited significant differences in other functional aspects.

3.2.3. Simulation Analysis of Current-Limiting Inductor Voltages When Using Different Resistors

The voltage variation across the current-limiting inductor under different resistances is shown in

Figure 8a. When a fault pulse occurred at t = 1.998 s, the voltage across the inductor instantly surged. This phenomenon occurred because the inductor current could not change abruptly while the inductor voltage could experience instantaneous changes. Within a short duration, the inductor voltage rapidly climbed to its peak. During the period from 1.998 s to 2 s, the current-limiting voltage initially rose to its peak value and then gradually declined, maintaining an overall inductor voltage below 60 V. At t = 2 s, when the IGBT tripped, the current-limiting voltage dropped rapidly. This enabled immediate isolation of the DC line, even while the current-limiting inductor continued dissipating energy for a brief period.

As indicated in the figure, when the resistance in the energy dissipation circuit (connected in parallel with the current-limiting inductor) was altered, the voltage across the current-limiting inductor changed accordingly. At t = 2 s, when the IGBT began to trip, the current was diverted from the current-limiting path to the energy dissipation circuit. Since inductor current cannot change instantaneously, the voltage across it increases with higher resistance values. The duration of this voltage is governed by the time constant (τ), where τ = L/R. For a fixed inductance, more resistance results in a shorter voltage duration. Therefore, by comprehensively considering the subsequent voltage across the IGBT, an appropriate resistance value was selected to enable rapid dissipation of the energy stored in the current-limiting inductor.

3.2.4. Simulation Analysis of IGBT Voltage Under Different Resistances

As shown in

Figure 8b, the voltage variations across the IGBT under different resistances after fault occurrence demonstrated the following behavior: At the initial fault inception (t = 1.998 s), the IGBT maintained its conducting state due to its inherent high input impedance, while the fault current remained below the DC bias current. At t = 2 s, when the fault current exceeded the DC bias current, the freewheeling current through the current-limiting inductor and line inductance generated a back electromotive force (EMF) during the subsequent fault current decline. This back EMF forced the IGBT to turn off, thereby interrupting the fault current.

As observed in the figure, the voltage across the IGBT differed at resistance values of 10 Ω, 5 Ω, and 1 Ω. For IGBT voltage, lower values are preferable since excessive voltage may cause breakdown, preventing normal operation after fault recovery. Considering the voltage behavior across the current-limiting inductor under different resistances (as previously analyzed), we must ensure both rapid dissipation of energy from the current-limiting voltage and maintenance of the IGBT voltage within a safe threshold. This study adopted 5 Ω for the resistor in the energy dissipation circuit.

3.2.5. Fault Ride-Through Simulation Analysis

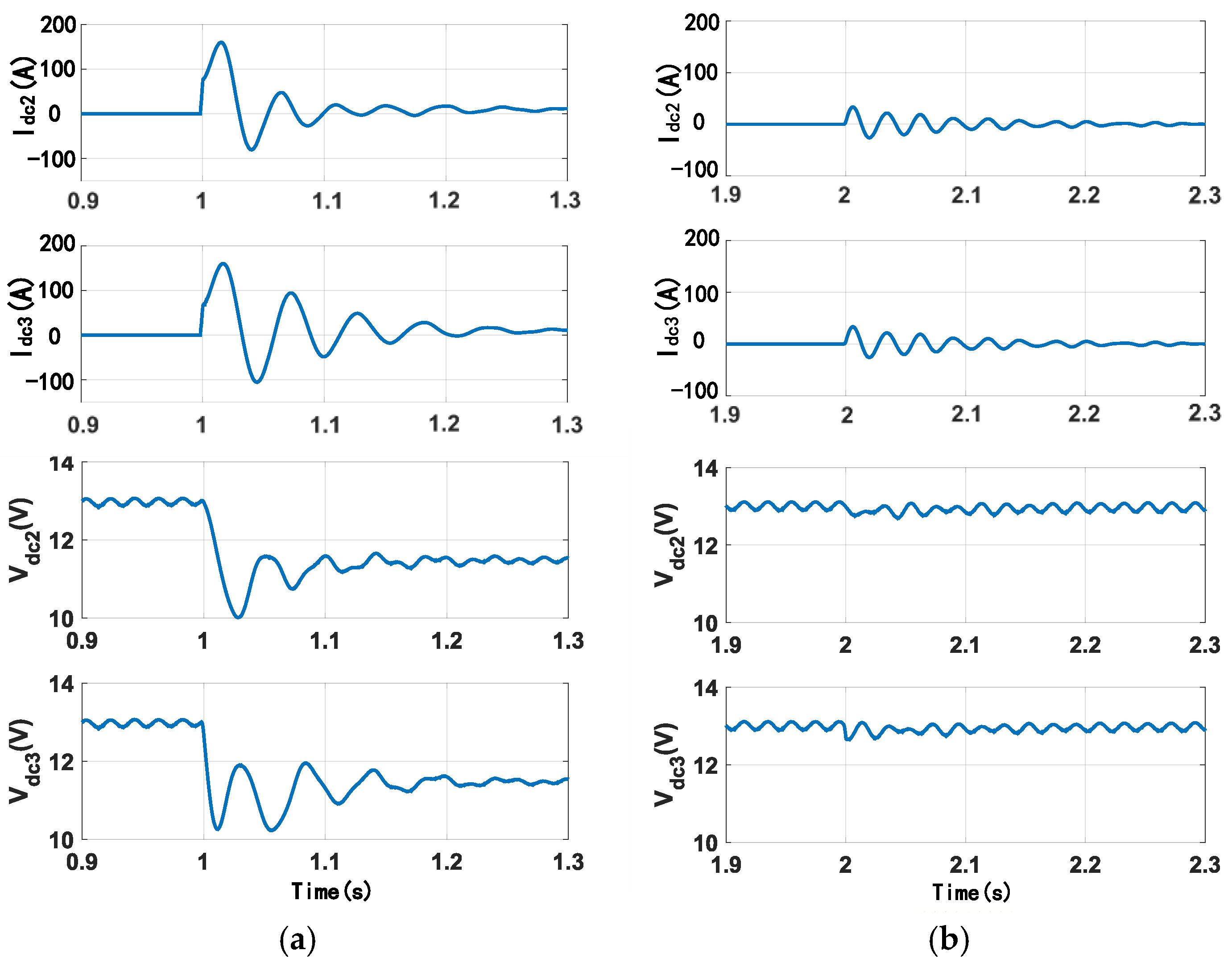

Following the trip event at t = 2 s, the system response of healthy components to the fault occurrence is illustrated in

Figure 9. Here, I

dc2 and I

dc3 represent the DC currents of VSC2 and VSC3, respectively, while V

dc2 and V

dc3 denote the DC voltages of VSC2 and VSC3, respectively.

The DC current and voltage limits of the voltage regulator were set to 4 × I

dN = 200 A and M × U

dN = 11.05 kV (where M is the modulation index of the voltage regulator, taken as 0.85 in this study). As shown in

Figure 9, the mutual-inductance current-limiting method could restrict the DC current of the VSC, but the VSC’s DC voltage decayed below 11.05 kV. In contrast, with the designed SSCB, after the trip event occurred, both the DC current and voltage of the VSC remained essentially stable. Therefore, by adopting the proposed SSCB scheme, the healthy portion of the flexible DC system successfully rode through the DC fault.

5. Conclusions

This paper proposes a novel SSCB topology with adaptive fault current-limiting capability specifically designed for enhancing the protection and self-healing capabilities in both low-voltage DC (LVDC, e.g., 380 V, 750 V, and 1500 V DC) and medium-voltage DC (MVDC, e.g., 10 kV, 20 kV, and 35 kV DC) distribution networks. Its ultra-fast isolation performance makes it particularly suitable for critical infrastructure requiring high power availability and minimal disruption, including the following:

1. Data center power distribution: To prevent cascading failures and maintain uninterrupted operation of sensitive IT loads.

2. Electric vehicle (EV) fast-charging stations: To ensure safety and enable rapid recovery after faults in high-power charging infrastructure.

3. Shipboard and aerospace DC microgrids: Where space, weight, and fault resilience are paramount concerns.

4. Industrial DC microgrids with sensitive processes: To minimize downtime and protect expensive equipment.

5. Renewable energy integration points (e.g., PV farms and battery storage interconnections): For reliable protection of converters and DC collection systems.

The novel SSCB topology incorporates an energy dissipation circuit (EDC) with auxiliary MOV-assisted energy dissipation and a snubber circuit. The primary innovation of this work lies in proposing a topology featuring adaptive switching functionality, enabling adaptive connection of the inductor to the main DC line. Furthermore, an auxiliary energy dissipation scheme based on an energy dissipation circuit (EDC) is introduced. In this EDC, a resistor serves as the primary element for dissipating the inductor’s stored energy, while an auxiliary MOV provides voltage clamping support. This design significantly accelerates fault isolation and reduces the energy burden, hence the capacity requirement placed on the MOV compared to traditional schemes where the MOV is solely responsible for energy absorption. Consequently, the proposed scheme achieves rapid isolation of the fault line with substantially alleviated constraints imposed by MOV capacity limitations. Compared to a traditional SSCB solution with a current limiter installed directly in the DC line, simulation and experimental results demonstrate that the proposed SSCB scheme successfully achieves adaptive commutation and realizes rapid isolation of the fault line within 0.1 ms.