Analysis and Design of Independent DC Bus Structure Multiport Power Electronic Transformer Based on Maximum Power Transmission Capability of Low-Voltage DC Ports

Abstract

1. Introduction

- (1)

- Three basic structures of LVDC ports are established and all of the IDBS-MPET topologies can be derived based on them. Accordingly, the general graphical representation and naming method of the IDBS-MPET are given.

- (2)

- The maximum power transmission capability (MPTC) is proposed to evaluate the capability of the IDBS-MPET to deal with a power imbalance.

- (3)

- Three topology design rules are derived from the MPTC calculation results of more than 80 typical IDBS-MPET topologies. Based on the three topology design rules, the systematic design scheme of the IDBS-MPET topology is proposed. The optimal IDBS-MPET to deal with a power imbalance can be found quickly and easily.

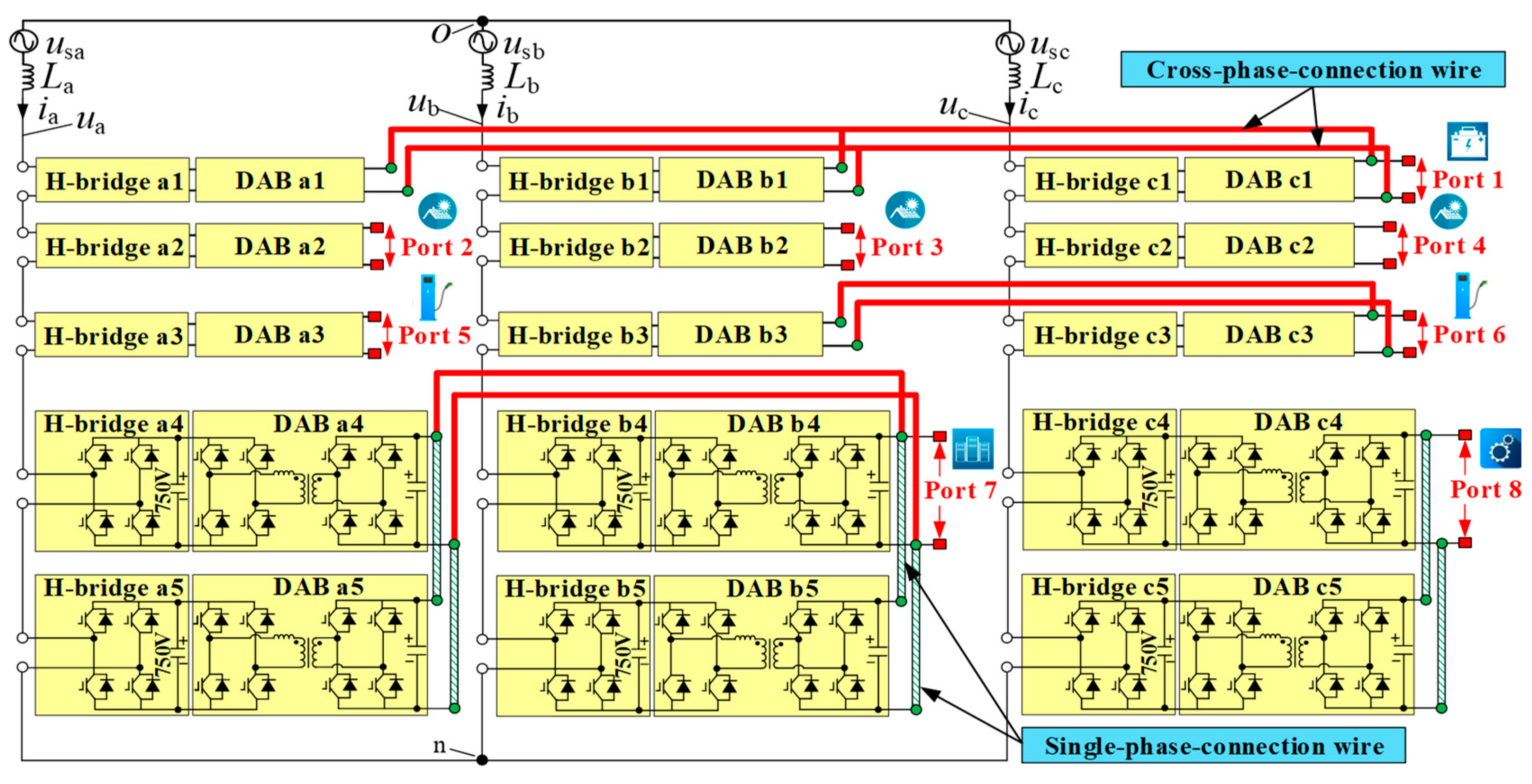

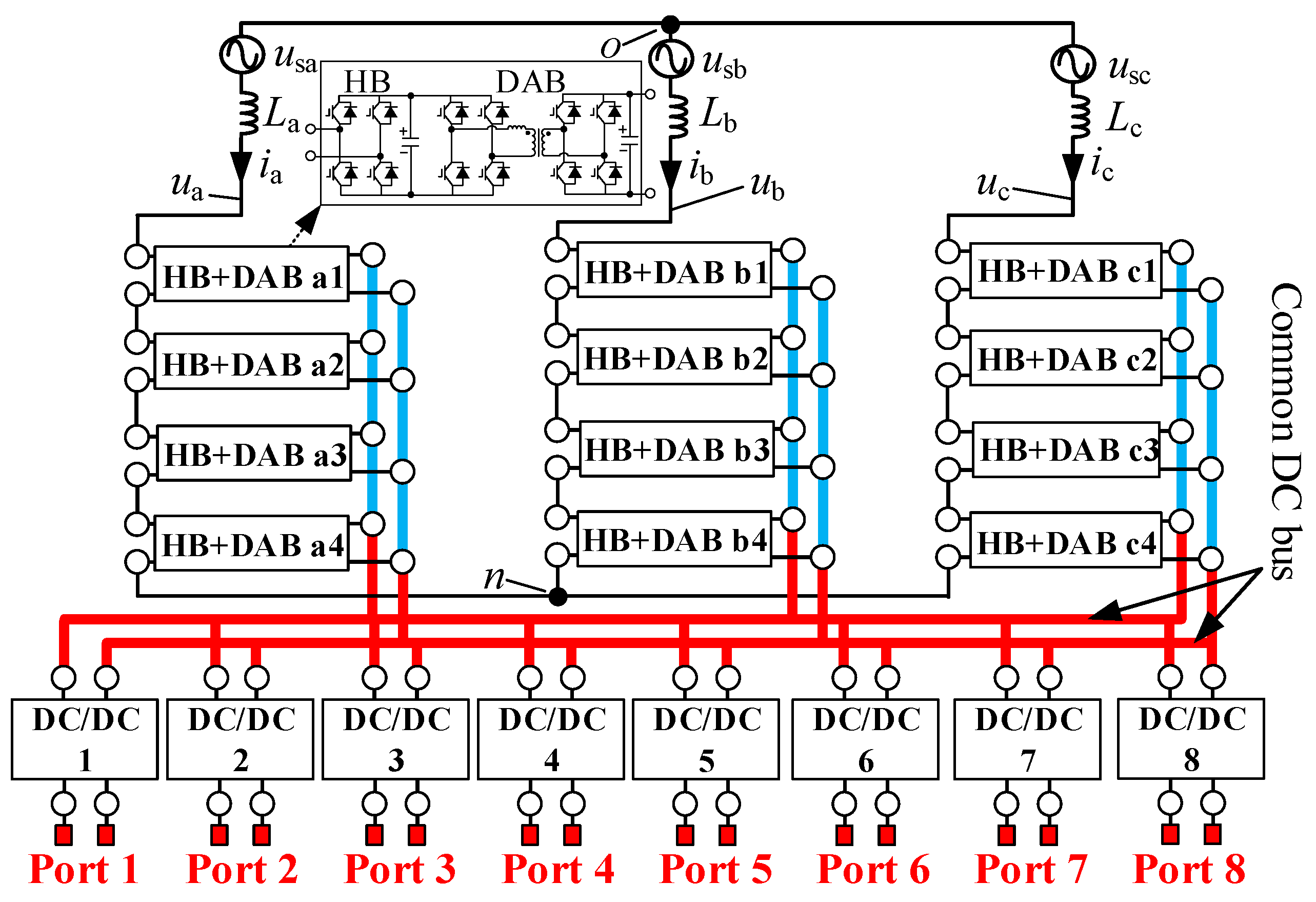

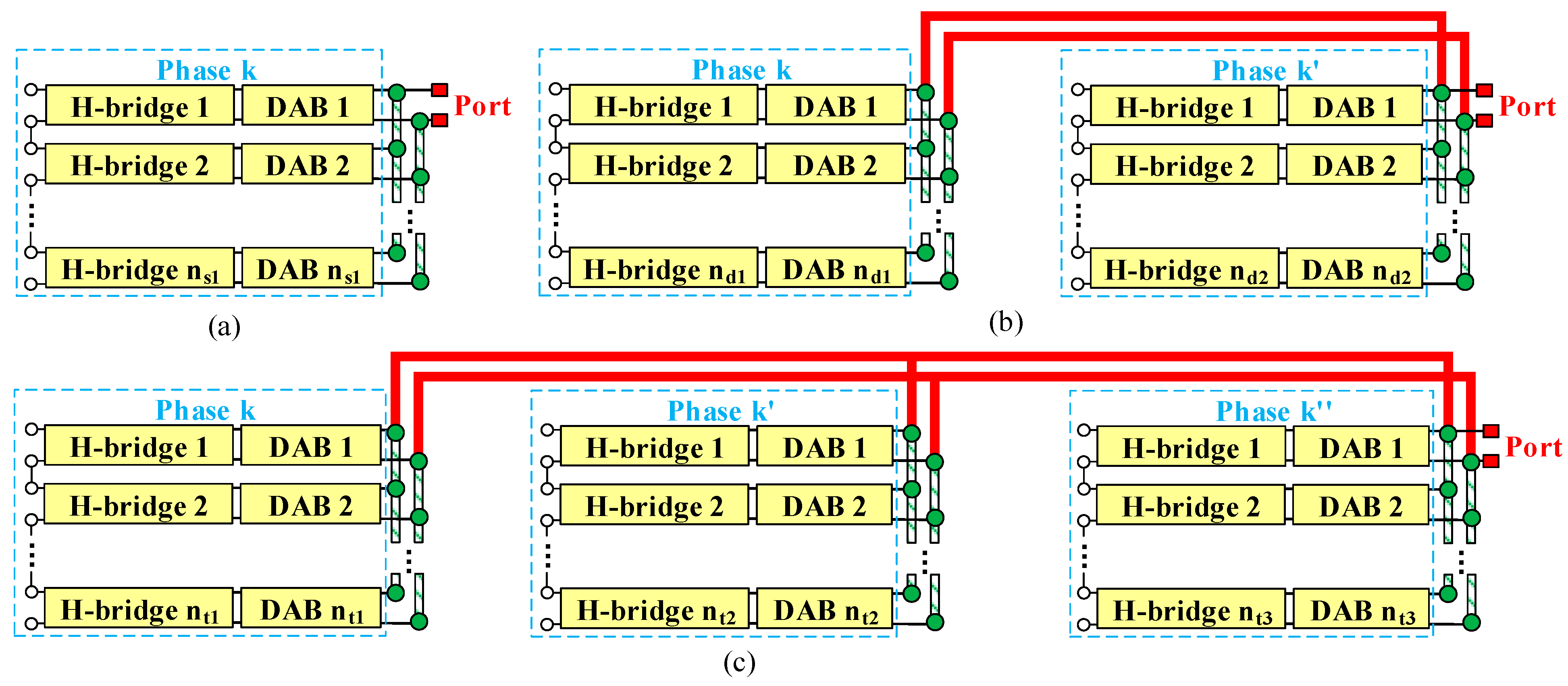

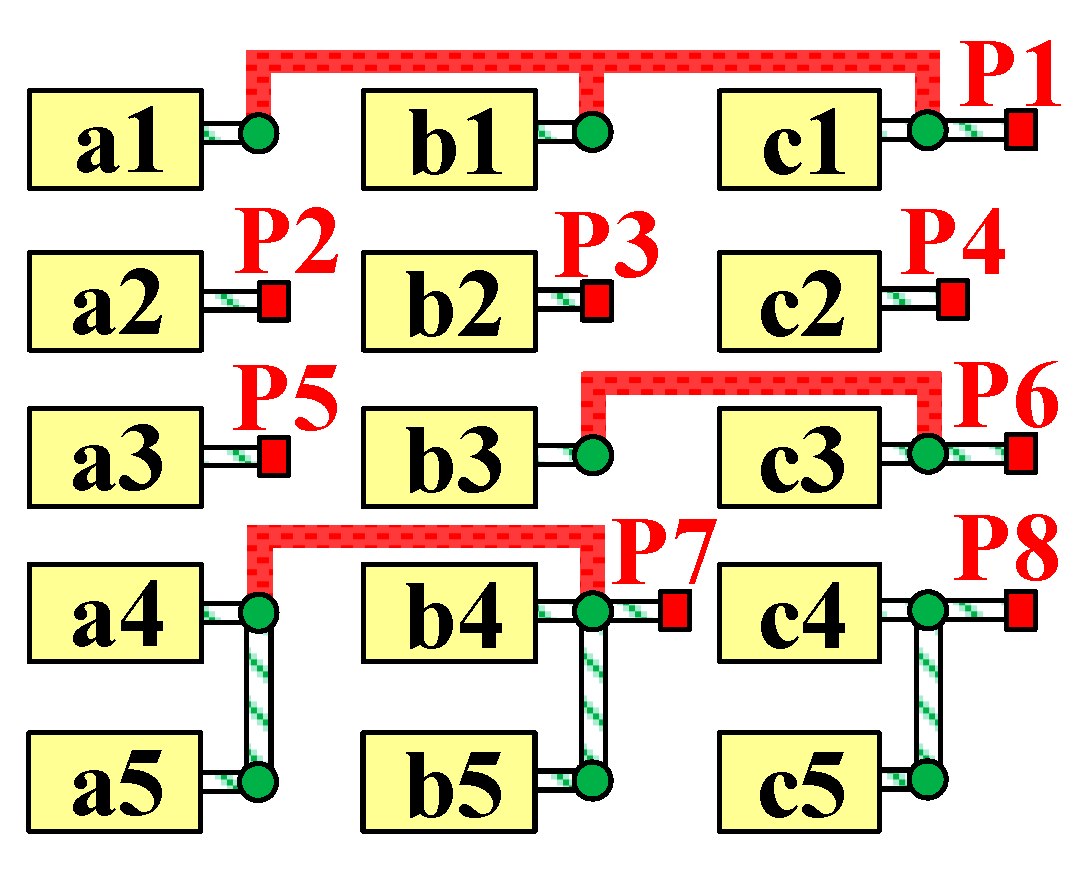

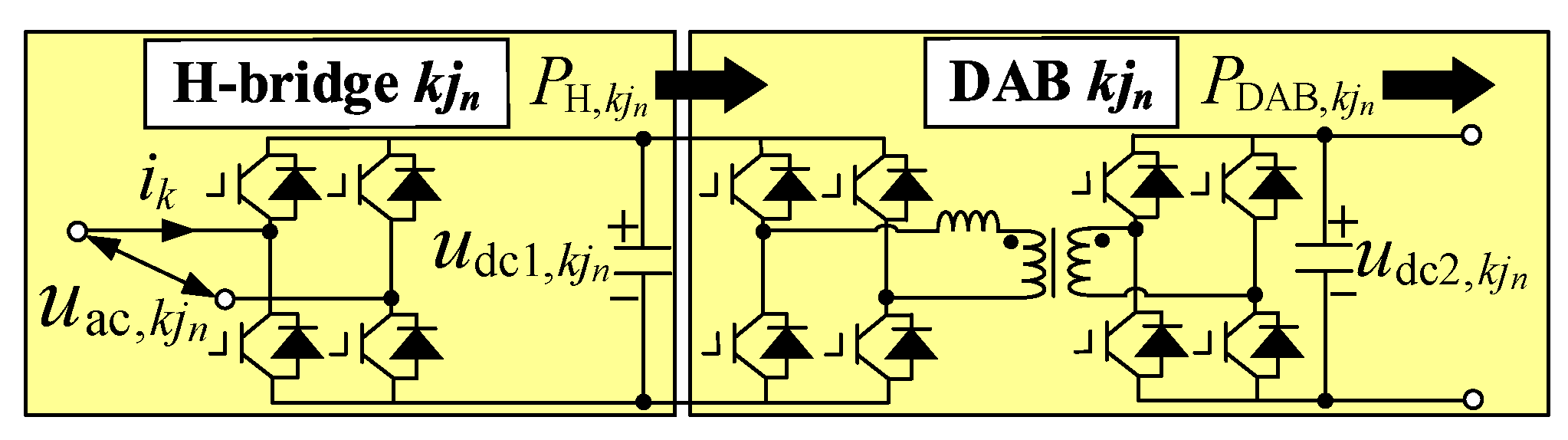

2. Topology Configuration of the IDBS-MPET

2.1. Overview of IDBS-MPET

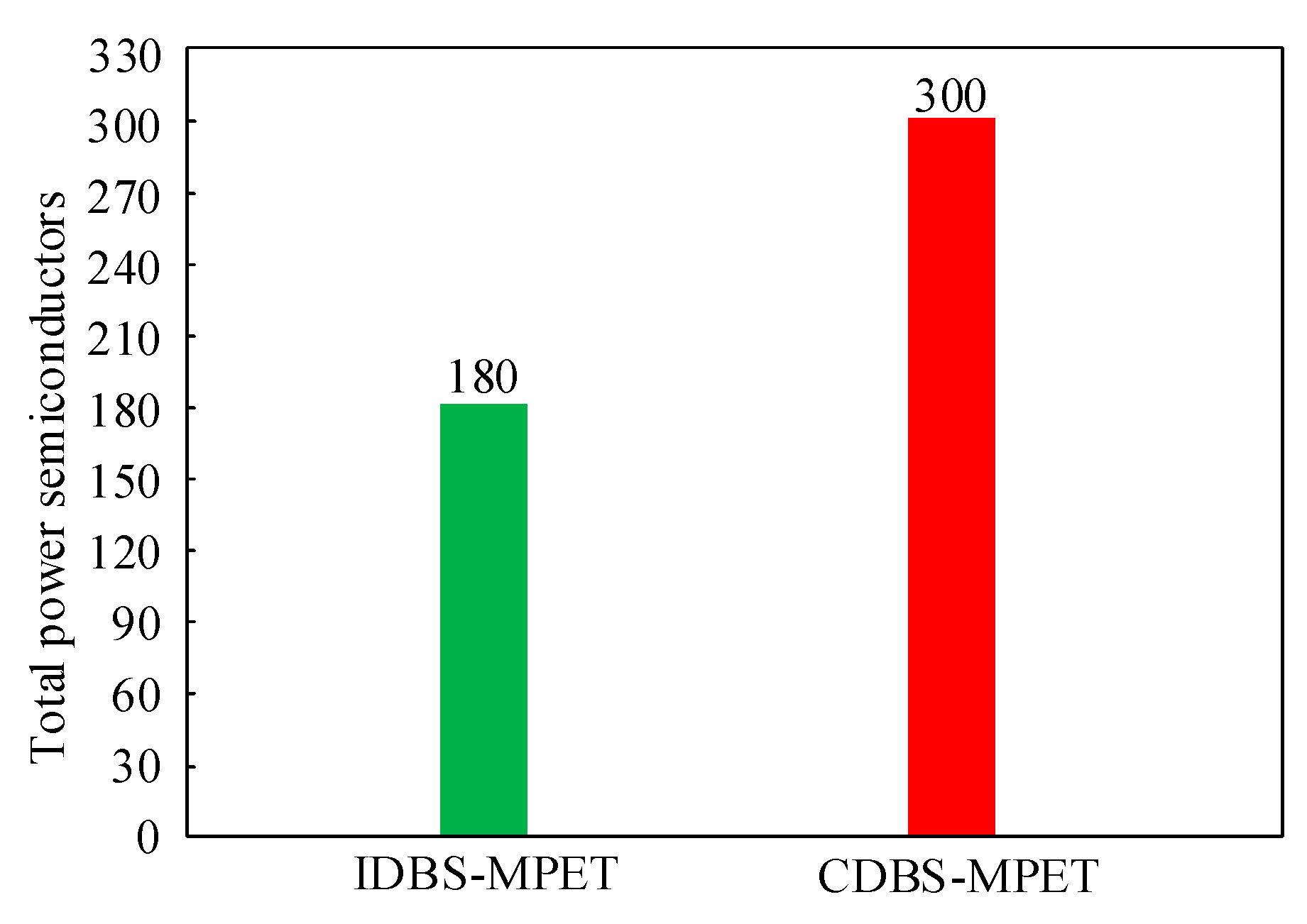

- (1)

- Lower hardware costs. Without adding any additional DC/DC converters, multiple LVDC ports are directly formed by the parallel connection of DABs. Therefore, a huge amount of power semiconductors in the IDBS-MPET can be saved compared with the CDBS-MPET.

- (2)

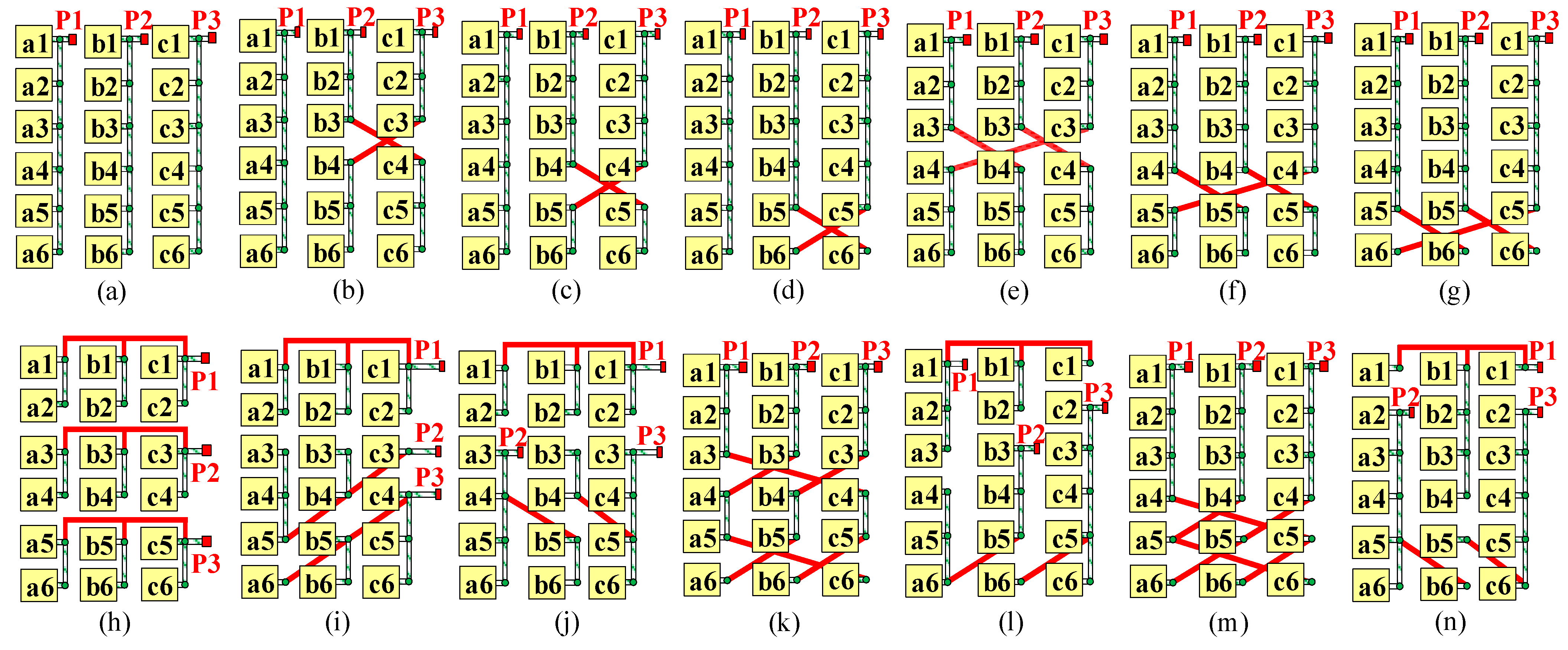

- Cross-phase connections are adopted. As multiple LVDC ports are distributed in three phases independently, a power imbalance will arise. To better deal with the problem, the cross-phase connection patterns of DABs are adopted in the IDBS-MPET.

- (3)

- Galvanic isolation. Since there is a high-frequency transformer in each DAB, all of the LVDC ports are galvanically isolated from each other and from the gird as well.

- (4)

- Modularity design. All H-bridges have the same electrical parameters, and so do all DABs. The power level of the entire power electronic transformer can be improved only by expanding the number of modules.

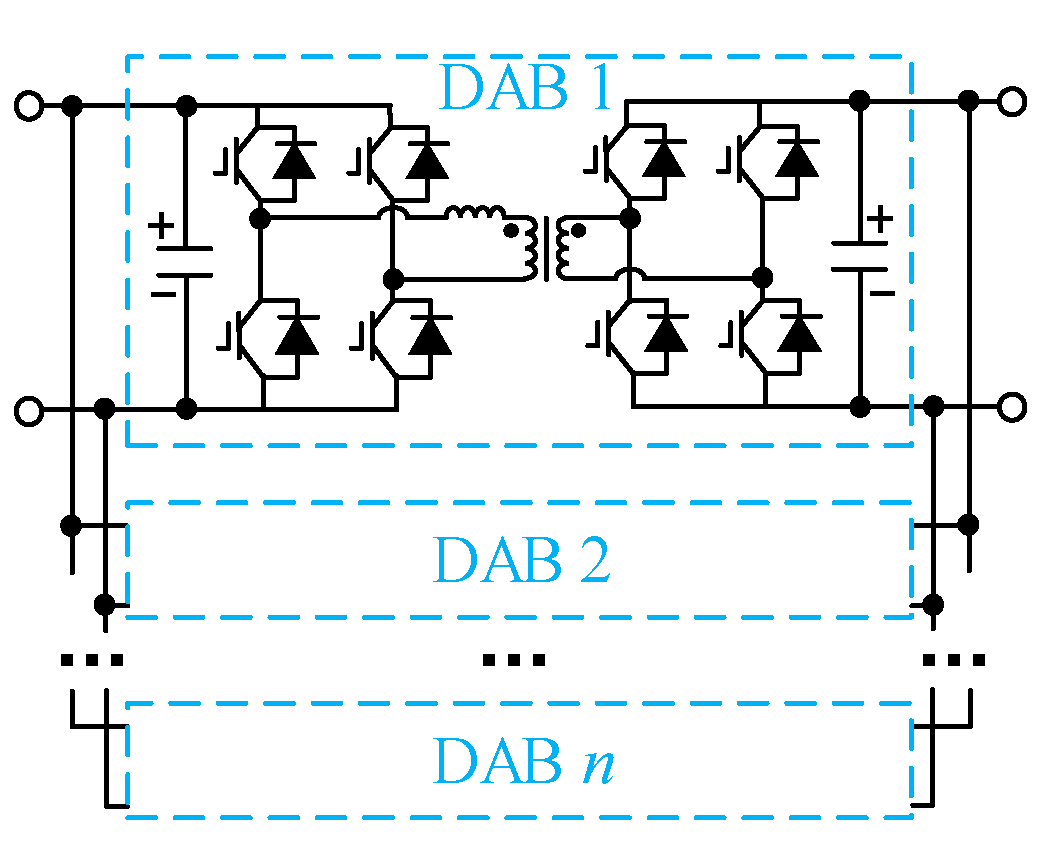

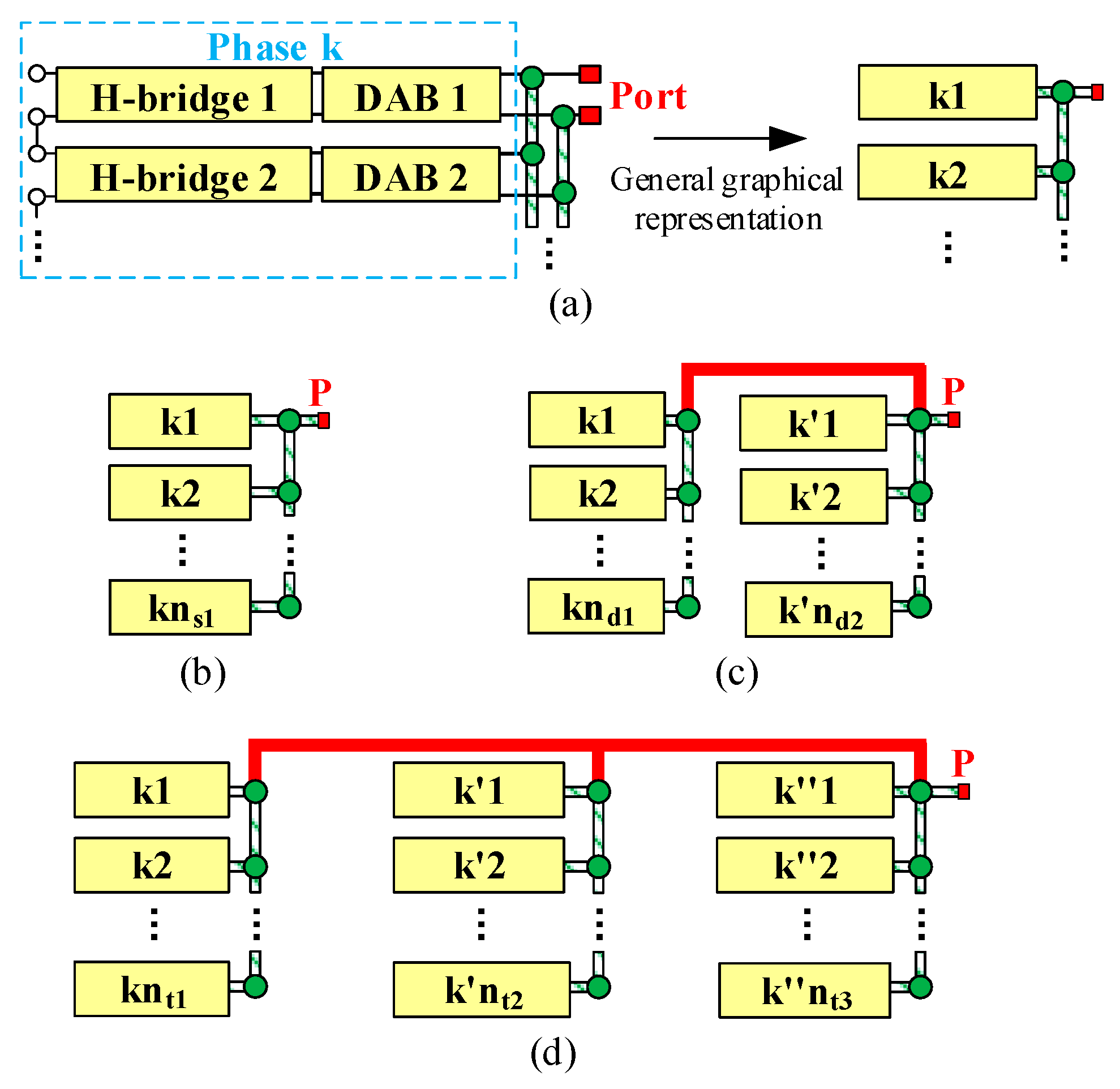

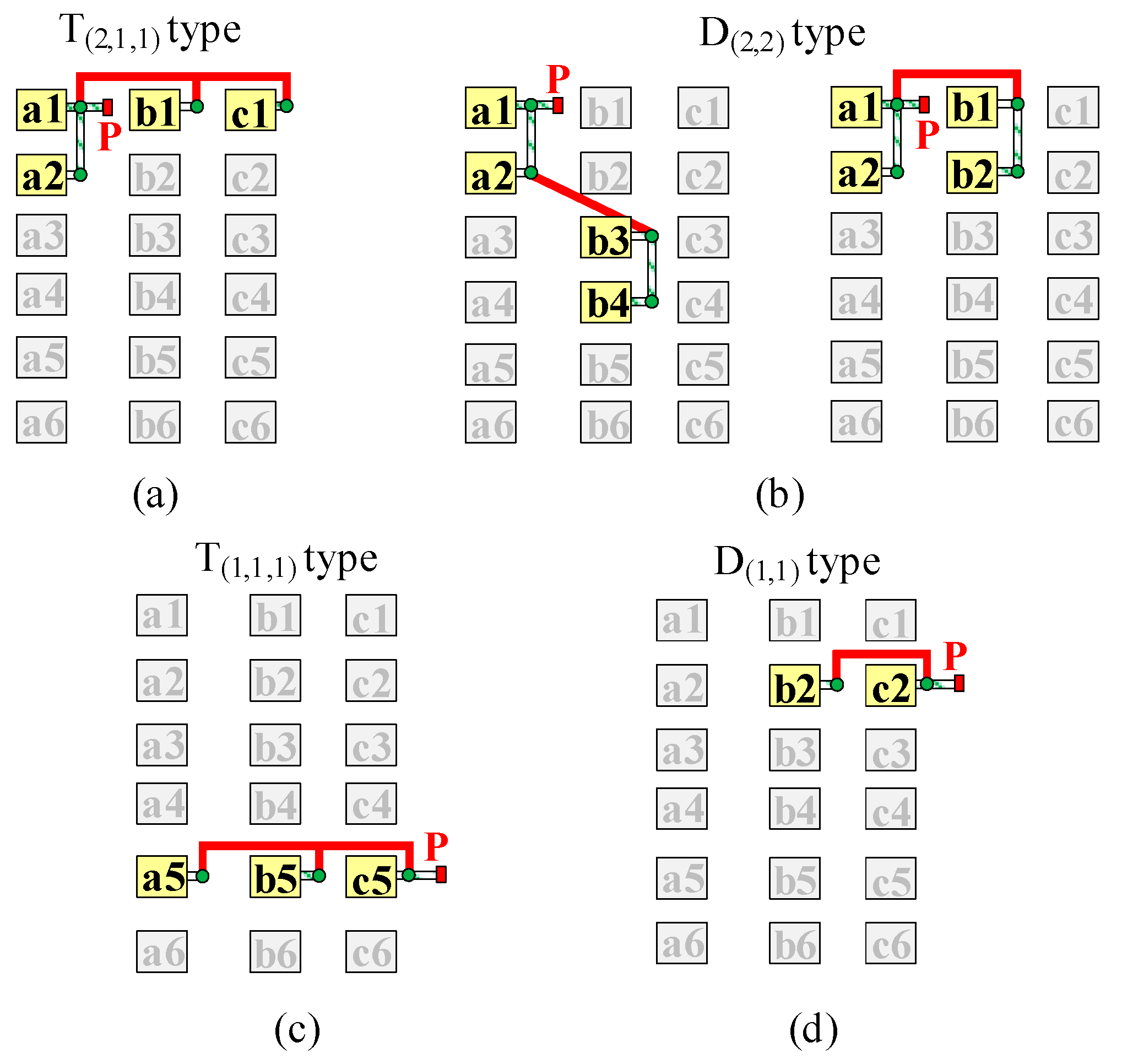

2.2. Basic Structure of LVDC Ports

2.3. Comprehensive Graphical Depiction and Nomenclature Approach for the IDBS-MPET

3. MPTC Definition and Calculation Method

3.1. MPTC Definition

3.2. MPTC Calculation Method

4. The IDBS-MPET Design Scheme

4.1. Analysis of MPTC Results

- (1)

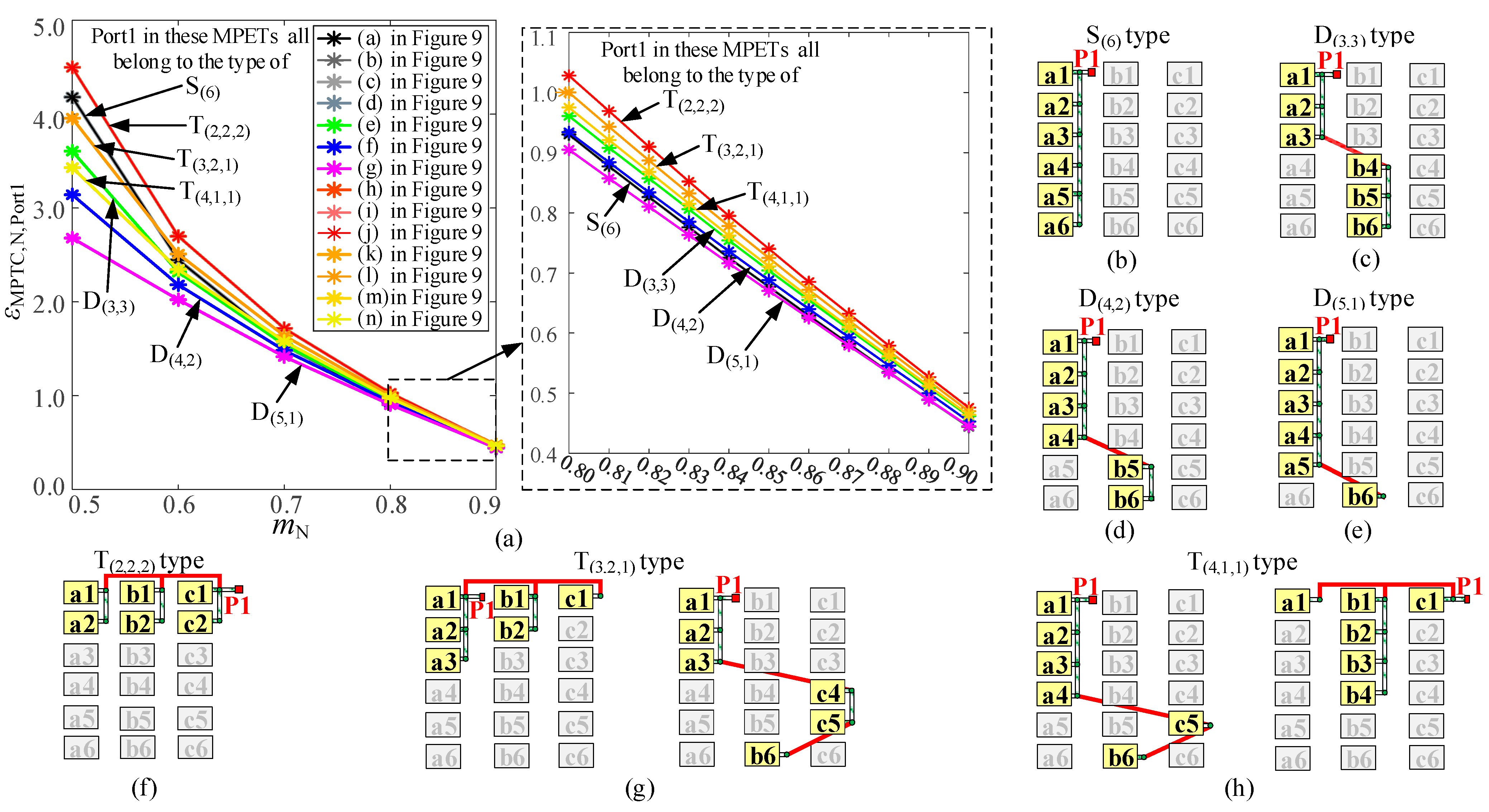

- The symmetrical LVDC port attains a larger MTPC value at every mN compared to the asymmetrical ones of the same type. As mentioned in Part B of Section 2, the T-Port can be divided into symmetrical T-Port and asymmetrical T-Port, the same as for the D-Port. As shown in Figure 10a, the MPTC value of the symmetrical T-Port (i.e., T(2,2,2)) is larger than that of asymmetrical T-Ports (i.e., T(3,2,1) and T(4,1,1)) at every mN. The MPTC value of the symmetrical D-Port (i.e., D(3,3)) is larger than that of asymmetrical D-Ports (i.e., D(4,2) and D(5,1)) at every mN. In addition, the MPTC value becomes smaller as the structure of the LVDC port becomes more asymmetrical. For example, the MPTC value of the T(4,1,1) type is smaller than that of the T(3,2,1) type at every mN. Therefore, the symmetrical T-Port is most preferable for the construction of the LVDC port, and the less asymmetrical T-Port can also be suitable as an option.

- (2)

- The symmetrical T-Port attains the largest MTPC value at every mN, and the most asymmetrical D-Port attains the smallest MTPC value at every mN. As shown in Figure 10a, the MPTC value of the symmetrical T-Port (i.e., T(2,2,2)) is the largest. The MPTC value of the most asymmetrical D-Port (i.e., D(5,1)) is the smallest. Moreover, as shown in Figure 10a and in the supplementary material of this paper, the MPTC value of asymmetrical D-Ports always becomes less than that of the T-Ports, symmetrical D-Ports and S-Ports. Therefore, it is best not to choose an asymmetrical D-Port to construct a LVDC port.

- (3)

- The MPTC value of the S-Ports is larger than that of the D-Ports when mN < 0.7, and larger than that of some extreme asymmetrical T-Ports when mN < 0.6. As shown in Figure 10a, when mN < 0.7, the MPTC value of the S-Port (i.e., S(6)) is larger than that of the D-Ports (i.e., D(3,3), D(4,2) and D(5,1)). When mN < 0.6, the MPTC value of the S-Port is even larger than that of the asymmetrical T-Ports (i.e., T(4,1,1)). The MPTC of the S-Port will become smaller than that of most T-Ports and the symmetrical D-Port when mN ≥ 0.7, whereas it is still larger or close to the value of the asymmetrical D-Port (i.e., D(4,2) and D(5,1)). Therefore, it is much better to choose an S-Port to construct an LVDC port rather than an asymmetrical D-Port.

- (4)

- Regardless of the type of LVDC port, the MPTC value increases with the reduction in mN. In industrial PET products, the mN is usually set between 0.7 and 0.9 [9,14,26]. As shown in Figure 10a, when mN is in the range from 0.8 to 0.9, the MPTC value of any type of LVDC port is less than 1. In order to improve the MPTC of the LVDC port, it is much better to set the mN of the IDBS-MPET in the range from 0.7 to 0.8 or even in the range from 0.6 to 0.8.

- (5)

- For the same type of LVDC port, the arrangement of modules in each phase does not affect the MPTC. As show in Figure 10g,h, both the T(3,2,1)- and T(4,1,1)-type LVDC port have two variants. As shown in Figure 10a, the two variants of the T(3,2,1)-type LVDC port have the same MPTC, and so does the T(4,1,1)-type LVDC port.

- (6)

- The variations in the MPTC among different configurations, especially the close performance between S(6) and the highest percentages in other types, can be attributed to the inherent design and operational characteristics of each configuration. For example, symmetrical configurations like T(2,2,2) generally offer a higher MPTC due to balanced power distribution among phases, while asymmetrical ones like D(5,1) might lag due to uneven load handling. The S(6) configuration, despite being a single-phase connection, leverages its design to maximize power transfer, thereby offering a compelling alternative for specific applications where compact design and high power-transfer capability are critical.

4.2. Three Topology Design Rules

- (1)

- Topology design rule 1: when designing an IDBS-MPET, it is preferable that the LVDC ports are constructed as symmetrical and less asymmetrical T-Ports.

- (2)

- Topology design rule 2: when as many LVDC ports as possible have been designed based on topology design rule 1, it is preferable that the remaining LVDC ports are constructed as symmetrical D-Ports.

- (3)

- Topology design rule 3: when as many LVDC ports as possible have been designed based on topology design rule 1 and topology design rule 2, it is preferable that the remaining LVDC ports are constructed as S-Ports.

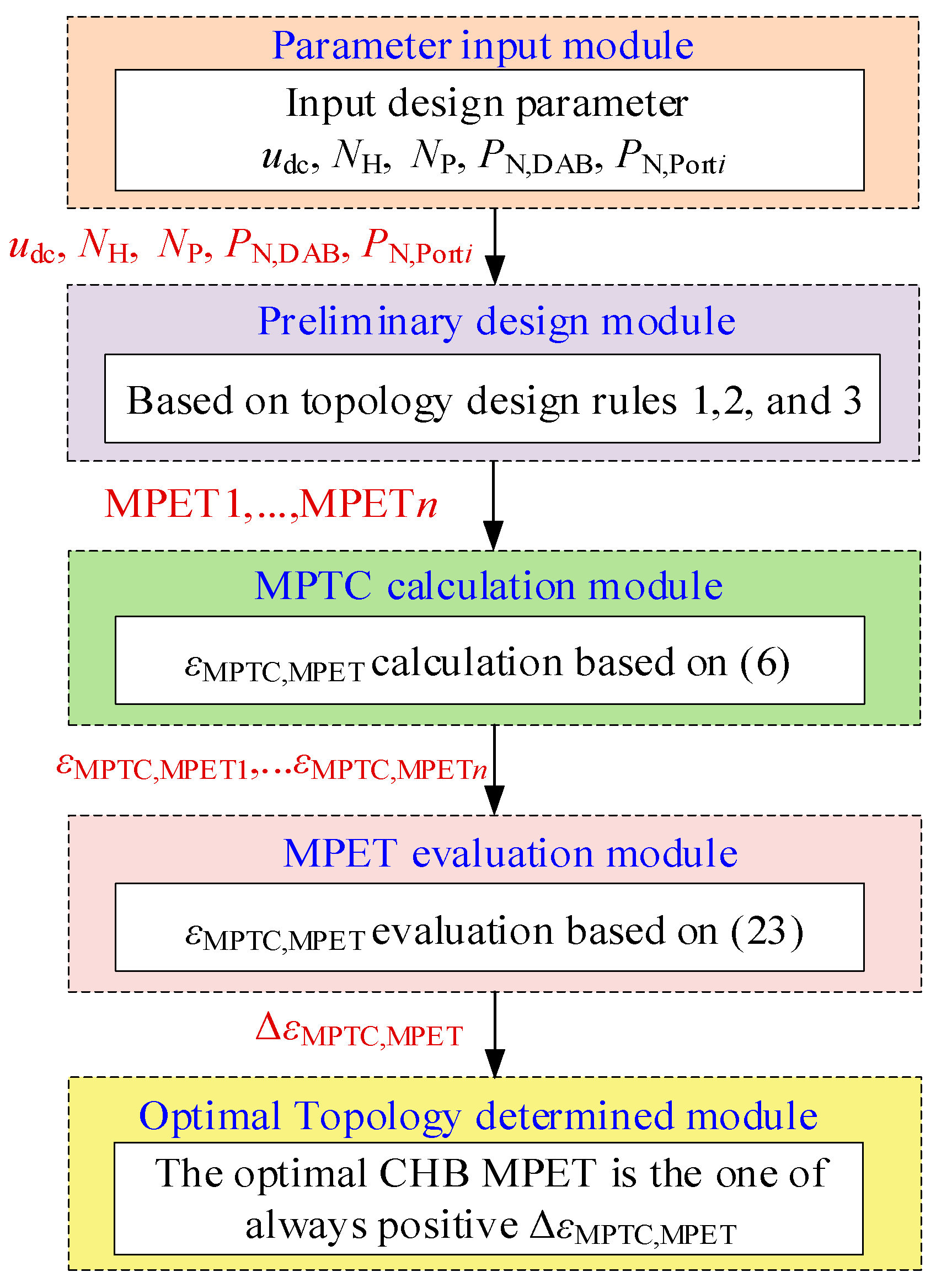

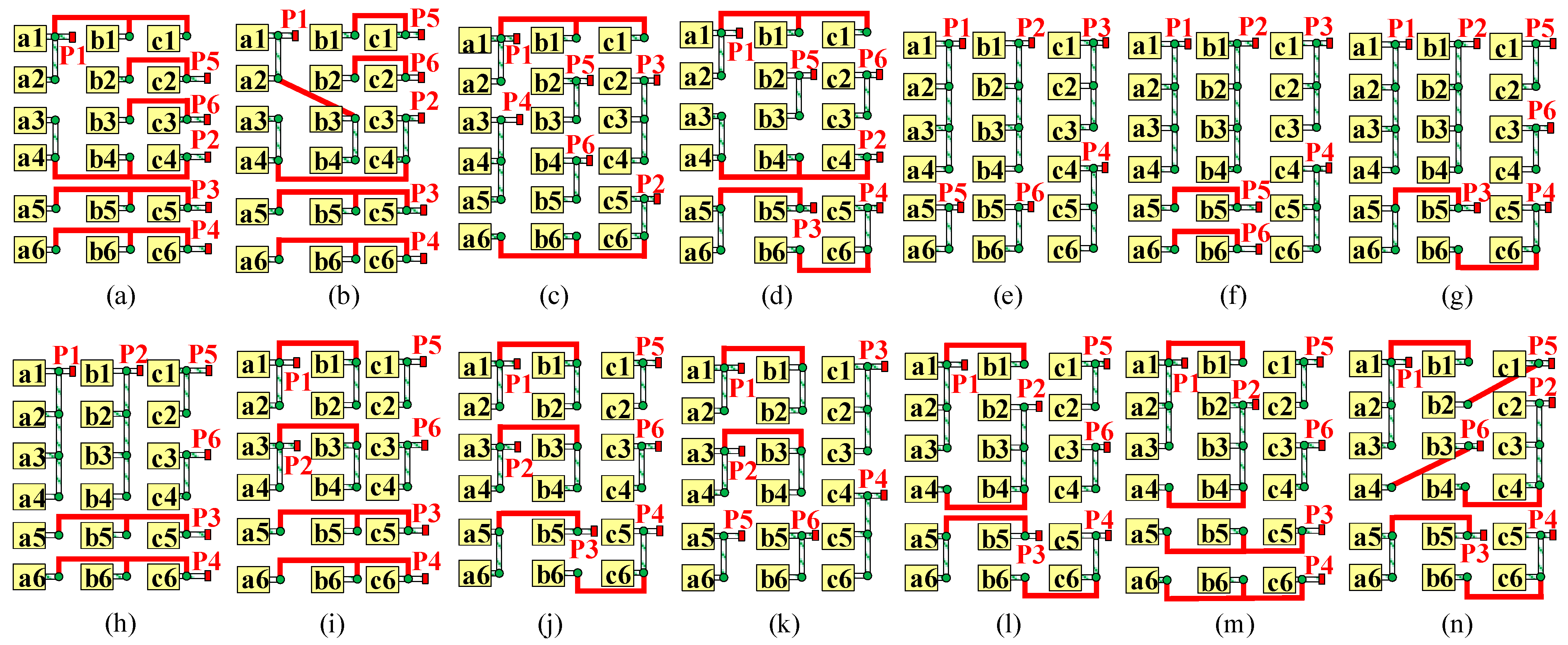

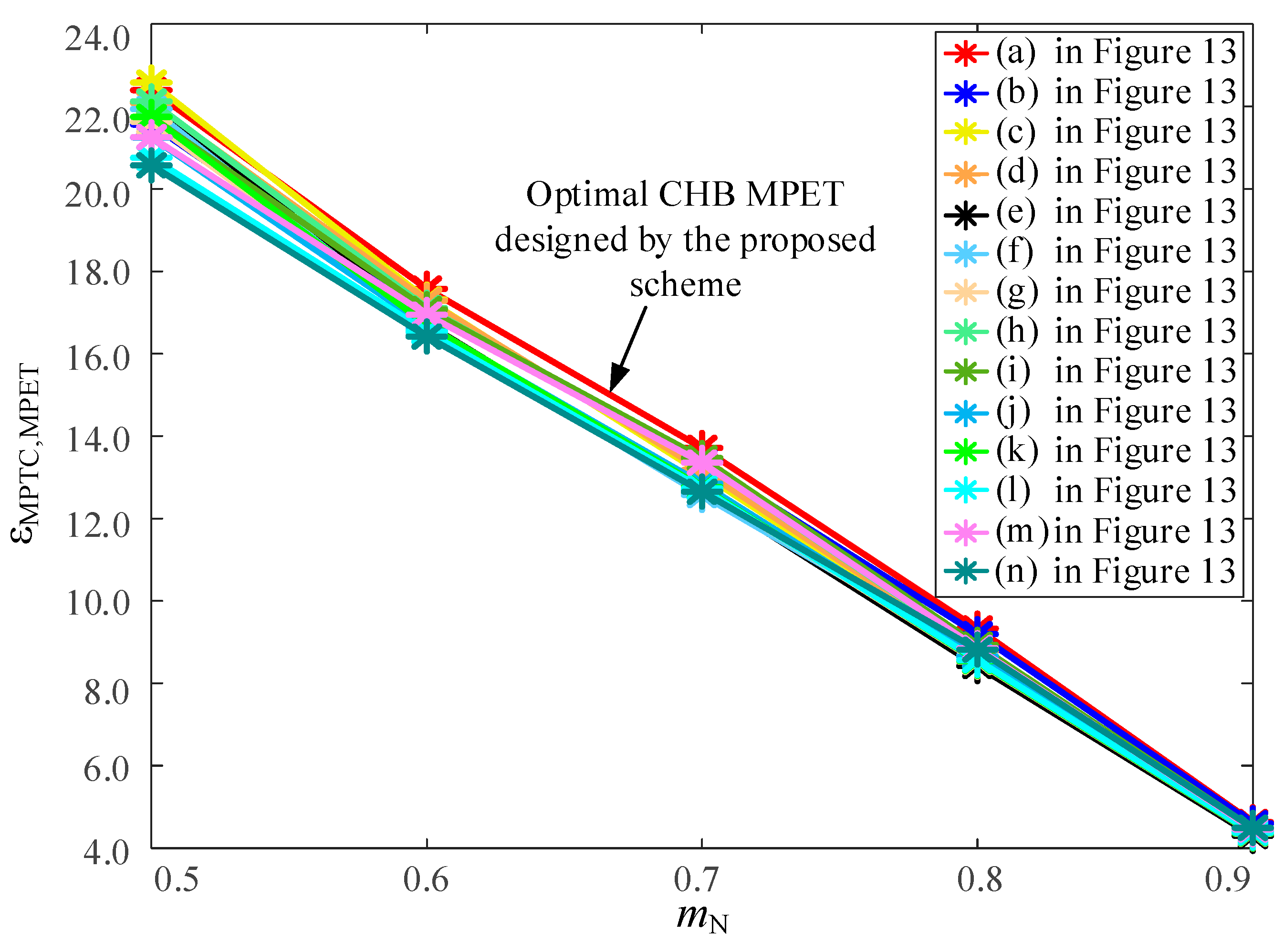

4.3. IDBS-MPET Design Scheme

- (1)

- Parameter input module. The udc, NH can be designed based on the MVAC grid voltage. Previous studies have proved that 1200 V or 1700 V are identified as optimum blocking voltages of the power semiconductors [27]. Thus, the udc can be set around 600 V or 850 V. In industrial PET products, the mN is usually set between 0.7 and 0.9 [14,16], so NH can be determined by (22). The NP, PN,DAB and PN,Portj (j = 1…NP) can be designed based on the variety and the power demand of DGs and DC loads.

- (2)

- Preliminary design module. Several IDBS-MPETs are preliminarily designed based on the three topology design rules. As mentioned in Part A of this section, the asymmetrical T-Port may gain advantage or disadvantage over the symmetrical D-Port. Moreover, the range of the advantage of the symmetrical D-Port over the S-Port may be wide or narrow. Thus, more than one IDBS-MPET topology may emerge after the preliminary designing process. It is noted the topologies will not be too much. These topologies shall be systematically identified and enumerated as MPET1, MPET2, …, through MPETn, for ease of reference and subsequent analysis.

- (3)

- MPTC calculation module. The MPTCs of MPET1, …, MPETn are calculated based on (5), namely, εMPTC,MPET1, …, εMPTC,MPETn.

- (4)

- MPET evaluation module. In order to determine the optimal topology, the evaluation index ΔεMPTC,MPET is proposed. If two MPETs are under comparison, namely, the MPETx1 and the MPETx2, ΔεMPTC,MPET is defined as follows:where εMPTC,MPETx1,mN is the εMPTC,MPET of MPETx1 on mN; εMPTC,MPETx2,mN is the εMPTC,MPET of MPETx2 on mN. The ΔεMPTC,MPET makes a comprehensive MPTC evaluation of the two MPETs on each mN. When the ΔεMPTC,MPET > 0, the MPETx1 emerges as preferable compared to MPETx2 and vice versa.

- (5)

- Optimal topology output module. Finally, the optimal IDBS-MPET is the one that always has a positive ΔεMPTC,MPET.

5. Evaluation Results

6. Discussion

7. Conclusions

Supplementary Materials

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Li, K.; Wen, W.; Zhao, Z.; Yuan, L.; Cai, W.; Mo, X.; Gao, C. Design and implementation of four-port megawatt-level high-frequency-bus based power electronic transformer. IEEE Trans. Power Electron. 2020, 36, 6429–6442. [Google Scholar] [CrossRef]

- Liserre, M.; Perez, M.A.; Langwasser, M.; Rojas, C.A.; Zhou, Z. Unlocking the hidden capacity of the electrical grid through smart transformer and smart transmission. Proc. IEEE 2022, 111, 421–437. [Google Scholar] [CrossRef]

- Wen, W.; Li, K.; Zhao, Z.; Yuan, L.; Mo, X.; Cai, W. Analysis and control of a four-port megawatt-level high-frequency-bus-based power electronic transformer. IEEE Trans. Power Electron. 2021, 36, 13080–13095. [Google Scholar] [CrossRef]

- Li, Y.; Li, Y.W. The evolutions of multilevel converter topology: A roadmap of topological invention. IEEE Ind. Electron. Mag. 2021, 16, 11–18. [Google Scholar] [CrossRef]

- Huber, J.E.; Kolar, J.W. Applicability of solid-state transformers in today’s and future distribution grids. IEEE Trans. Smart Grid 2017, 10, 317–326. [Google Scholar] [CrossRef]

- Hu, Y.; Li, Z.; Zhang, H.; Zhao, C.; Gao, F.; Luo, L.; Luan, K.; Wang, P.; Li, Y.; Yuan, X. High-frequency-link current stress optimization of cascaded h-bridge-based solid-state transformer with third-order harmonic voltage injection. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 9, 1027–1038. [Google Scholar] [CrossRef]

- Ruiz, F.; Perez, M.A.; Espinosa, J.R.; Gajowik, T.; Stynski, S.; Malinowski, M. Surveying solid-state transformer structures and controls: Providing highly efficient and controllable power flow in distribution grids. IEEE Ind. Electron. Mag. 2020, 14, 56–70. [Google Scholar] [CrossRef]

- Kolar, J.W.; Ortiz, G. Solid-state-transformers: Key components of future traction and smart grid systems. In Proceedings of the International Power Electronics Conference—ECCE Asia (IPEC 2014), Hiroshima, Japan, 18–21 May 2014; pp. 22–35. [Google Scholar]

- Chen, Y.; Shi, K.; Chen, M.; Xu, D. Data center power supply systems: From grid edge to point-of-load. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 11, 2441–2456. [Google Scholar] [CrossRef]

- Zhao, B.; Song, Q.; Li, J.; Xu, X.; Liu, W. Comparative analysis of multilevel-high-frequency-link and multilevel-DC-link DC–DC transformers based on MMC and dual-active bridge for MVDC application. IEEE Trans. Power Electron. 2017, 33, 2035–2049. [Google Scholar] [CrossRef]

- Costa, L.F.; De Carne, G.; Buticchi, G.; Liserre, M. The smart transformer: A solid-state transformer tailored to provide ancillary services to the distribution grid. IEEE Power Electron. Mag. 2017, 4, 56–67. [Google Scholar] [CrossRef]

- Huang, A.Q.; Crow, M.L.; Heydt, G.T.; Zheng, J.P.; Dale, S.J. The future renewable electric energy delivery and management (freedm) system: The energy internet. Proc. IEEE 2010, 99, 133–148. [Google Scholar] [CrossRef]

- Zhao, B.; Song, Q.; Liu, W. A practical solution of high-frequency-link bidirectional solid-state transformer based on advanced components in hybrid microgrid. IEEE Trans. Ind. Electron. 2014, 62, 4587–4597. [Google Scholar] [CrossRef]

- Wang, D.; Tian, J.; Mao, C.; Lu, J.; Duan, Y.; Qiu, J.; Cai, H. A 10-kV/400-V 500-kVA Electronic Power Transformer. IEEE Trans. Ind. Electron. 2016, 63, 6653–6663. [Google Scholar] [CrossRef]

- Jia, H.; Xiao, Q.; He, J. An improved grid current and DC capacitor voltage balancing method for three-terminal hybrid AC/DC microgrid. IEEE Trans. Smart Grid 2018, 10, 5876–5888. [Google Scholar] [CrossRef]

- Ouyang, S.; Liu, J.; Wang, X.; Song, S.; Hou, X. Comparison of four power electronic transformer topologies on unbalanced load correction capacity. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, Canada, 20–24 September 2015; pp. 3702–3709. [Google Scholar]

- Wang, X.; Liu, J.; Ouyang, S.; Meng, F. Research on unbalanced-load correction capability of two power electronic transformer topologies. IEEE Trans. Power Electron. 2014, 30, 3044–3056. [Google Scholar] [CrossRef]

- Iov, F.; Blaabjerg, F.; Clare, J.; Wheeler, P.; Rufer, A.; Hyde, A. Uniflex-PM–A key-enabling technology for future European electricity networks. Eur. Power Electron. Drives Assoc. J. 2009, 19, 6–16. [Google Scholar] [CrossRef]

- Watson, A.J.; Dang, H.Q.S.; Mondal, G.; Clare, J.C.; Wheeler, P.W. Experimental implementation of a multilevel converter for power system integration. In Proceedings of the 2009 IEEE Energy Conversion Congress and Exposition, San Jose, CA, USA, 20–24 September 2009; pp. 2232–2238. [Google Scholar]

- Zhao, T.; Wang, G.; Bhattacharya, S.; Huang, A.Q. Voltage and power balance control for a cascaded H-bridge converter-based solid-state transformer. IEEE Trans. Power Electron. 2012, 28, 1523–1532. [Google Scholar] [CrossRef]

- Yu, Y.; Konstantinou, G.; Hredzak, B.; Agelidis, V.G. Power balance optimization of cascaded H-bridge multilevel converters for large-scale photovoltaic integration. IEEE Trans. Power Electron. 2015, 31, 1108–1120. [Google Scholar] [CrossRef]

- Yan, Y.; Bai, H.; Foote, A.; Wang, W. Securing full-power-range zero-voltage switching in both steady-state and transient operations for a dual-active-bridge-based bidirectional electric vehicle charger. IEEE Trans. Power Electron. 2019, 35, 7506–7519. [Google Scholar] [CrossRef]

- Abuishmais, I.; Shahroury, F.R. Bidirectional dual active bridge for interfacing battery energy storage systems with DC microgrid. In Proceedings of the 2021 International Conference on Electrical, Computer and Energy Technologies (ICECET), Cape Town, South Africa, 9–10 December 2021; pp. 1659–1663. [Google Scholar]

- Shi, J.; Zhou, L.; He, X. Common-duty-ratio control of input-parallel output-parallel (IPOP) connected DC–DC converter modules with automatic sharing of currents. IEEE Trans. Power Electron. 2011, 27, 3277–3291. [Google Scholar] [CrossRef]

- Wang, M.; Zhang, X.; Zhao, T.; Ma, M.; Hu, Y.; Wang, F.; Wang, X. Harmonic compensation strategy for single-phase cascaded H-bridge PV inverter under unbalanced power conditions. IEEE Trans. Ind. Electron. 2020, 67, 10474–10484. [Google Scholar] [CrossRef]

- Dujic, D.; Zhao, C.; Mester, A.; Steinke, J.K.; Weiss, M.; Lewdeni-Schmid, S.; Chaudhuri, T.; Stefanutti, P. Power electronic traction transformer-low voltage prototype. IEEE Trans. Power Electron. 2013, 28, 5522–5534. [Google Scholar] [CrossRef]

- Huber, J.E.; Kolar, J.W. Optimum number of cascaded cells for high-power medium-voltage AC–DC converters. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 5, 213–232. [Google Scholar] [CrossRef]

| Port Name | Devices Connected to Port 1 to 8 | Nominal Power and Voltages |

|---|---|---|

| Port 1 | Energy storage | PN,Port1 = 240 kW, VN,Port1 = 750 V |

| Port 2 | PV | PN,Port2 = 80 kW, VN,Port2 = 600 V |

| Port 3 | PV | PN,Port3 = 80 kW, VN,Port3 = 600 V |

| Port 4 | PV | PN,Port4 = 80 kW, VN,Port4 = 600 V |

| Port 5 | EV fast charger | PN,Port5 = 80 kW, VN,Port5 = 400 V |

| Port 6 | EV ultra-fast charger | PN,Port6 = 160 kW, VN,Port6 = 800 V |

| Port 7 | Data center | PN,Port7 = 320 kW, VN,Port7 = 400 V |

| Port 8 | Industrial load | PN,Port8 = 160 kW, VN,Port8 = 750 V |

| Circuit Parameters | Value |

|---|---|

| Nominal grid line-to-line voltage RMS | 2500 V |

| Number of H-bridge cells per phase | 5 |

| H-bridge DC voltage | 750 V |

| DAB high-frequency transformer turn ratio | 1:1 |

| Nominal power of H-bridge | PN,Hbridge = 80 kW |

| Nominal power of DAB | PN,DAB = 80 kW |

| Name | Number of IPOP DABs |

|---|---|

| DC/DC 1 | 3 |

| DC/DC 2 | 1 |

| DC/DC 3 | 1 |

| DC/DC 4 | 1 |

| DC/DC 5 | 1 |

| DC/DC 6 | 2 |

| DC/DC 7 | 4 |

| DC/DC 8 | 2 |

| Kinds of LVDC Ports | Naming |

|---|---|

| S-Port | S(ns)(ns1) |

| D-Port | D(nd)(nd1, nd2) |

| T-Port | T(nt)(nt1,nt2,nt3) |

| mN | T(2,2,2) | T(3,2,1) | T(4,1,1) | D(3,3) | D(4,2) | D(5,1) | S(6) |

|---|---|---|---|---|---|---|---|

| 0.5 | 4.498 | 3.957 | 3.430 | 3.606 | 3.142 | 2.679 | 4.181 |

| 0.6 | 2.699 | 2.509 | 2.346 | 2.317 | 2.181 | 2.023 | 2.447 |

| 0.7 | 1.718 | 1.639 | 1.578 | 1.542 | 1.483 | 1.417 | 1.541 |

| 0.8 | 1.028 | 1.000 | 0.975 | 0.961 | 0.934 | 0.905 | 0.930 |

| 0.9 | 0.476 | 0.470 | 0.464 | 0.462 | 0.453 | 0.445 | 0.444 |

| mN | T(3,2,1) | T(4,1,1) | D(3,3) | D(4,2) | D(5,1) | S(6) |

|---|---|---|---|---|---|---|

| 0.5 | 87.97% | 76.26% | 80.17% | 69.85% | 59.56% | 92.95% |

| 0.6 | 92.96% | 86.92% | 85.85% | 80.81% | 74.95% | 90.66% |

| 0.7 | 95.40% | 91.85% | 89.76% | 86.32% | 82.48% | 89.70% |

| 0.8 | 97.28% | 94.84% | 93.48% | 90.86% | 88.04% | 90.47% |

| 0.9 | 98.74% | 97.48% | 97.06% | 95.17% | 93.49% | 93.28% |

| Design Parameters | Value |

|---|---|

| udc | 750 V |

| NH | 6 |

| NP | 6 |

| PN,DAB | 50 kW |

| PN,Port1 | 200 kW |

| PN,Port2 | 200 kW |

| PN,Port3 | 150 kW |

| PN,Port4 | 150 kW |

| Port Type | mN = 0.9 | mN = 0.8 | mN = 0.7 | mN = 0.6 | mN = 0.5 | |||||

|---|---|---|---|---|---|---|---|---|---|---|

| Pmax/kW | Pmin/kW | Pmax/kW | Pmin/kW | Pmax/kW | Pmin/kW | Pmax/kW | Pmin/kW | Pmax/kW | Pmin/kW | |

| T(2,1,1) | 229.4 | 110.9 | 269.0 | 23.6 | 324.8 | −61.8 | 409.3 | −145.4 | 551.4 | −209.0 |

| S(4) | 229.4 | 119.7 | 269.2 | 49.6 | 325.5 | −17.1 | 411.7 | −84.3 | 559.8 | −154.9 |

| D(2,2) | 229.4 | 113.8 | 268.5 | 36.7 | 323.2 | −30.4 | 404.8 | −88.0 | 539.0 | −138.3 |

| D(3,1) | 229.2 | 116.7 | 267.6 | 43.8 | 319.8 | −22.6 | 393.8 | −85.8 | 505.3 | −122.6 |

| mN | εMPTC,MPET | |||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Figure 13a | Figure 13b | Figure 13c | Figure 13d | Figure 13e | Figure 13f | Figure 13g | Figure 13h | Figure 13i | Figure 13j | Figure 13k | Figure 13l | Figure 13m | Figure 13n | |

| 0.5 | 22.39 | 21.56 | 22.58 | 22.08 | 22.12 | 21.94 | 21.63 | 22.12 | 21.75 | 21.25 | 21.75 | 20.76 | 21.25 | 20.57 |

| 0.6 | 17.58 | 16.96 | 17.32 | 17.29 | 16.3 | 16.61 | 16.70 | 17.11 | 17.08 | 16.67 | 16.70 | 16.54 | 16.95 | 16.42 |

| 0.7 | 13.71 | 13.38 | 13.09 | 13.18 | 12.65 | 12.57 | 12.74 | 13.36 | 13.47 | 12.85 | 12.76 | 12.74 | 13.35 | 12.65 |

| 0.8 | 9.33 | 9.19 | 8.68 | 8.78 | 8.42 | 8.68 | 8.52 | 8.81 | 8.94 | 8.64 | 8.54 | 8.56 | 8.86 | 8.82 |

| 0.9 | 4.63 | 4.60 | 4.39 | 4.44 | 4.30 | 4.42 | 4.35 | 4.43 | 4.49 | 4.41 | 4.36 | 4.38 | 4.46 | 4.50 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, J.; Wu, J.; Xiong, F. Analysis and Design of Independent DC Bus Structure Multiport Power Electronic Transformer Based on Maximum Power Transmission Capability of Low-Voltage DC Ports. Energies 2024, 17, 1096. https://doi.org/10.3390/en17051096

Li J, Wu J, Xiong F. Analysis and Design of Independent DC Bus Structure Multiport Power Electronic Transformer Based on Maximum Power Transmission Capability of Low-Voltage DC Ports. Energies. 2024; 17(5):1096. https://doi.org/10.3390/en17051096

Chicago/Turabian StyleLi, Junchi, Junyong Wu, and Fei Xiong. 2024. "Analysis and Design of Independent DC Bus Structure Multiport Power Electronic Transformer Based on Maximum Power Transmission Capability of Low-Voltage DC Ports" Energies 17, no. 5: 1096. https://doi.org/10.3390/en17051096

APA StyleLi, J., Wu, J., & Xiong, F. (2024). Analysis and Design of Independent DC Bus Structure Multiport Power Electronic Transformer Based on Maximum Power Transmission Capability of Low-Voltage DC Ports. Energies, 17(5), 1096. https://doi.org/10.3390/en17051096