1. Introduction

In the pursuit of global efforts toward developing clean energy sources, the proportion of renewable energy sources, including wind and photovoltaic power, in the power grid is escalating, paralleled by a remarkable surge in the installed capacity of these units [

1,

2]. According to the latest data released by the International Energy Agency (IEA) in June 2023, global renewable energy capacity additions are anticipated to surge to 550 GW in 2024, necessitating the integration of an increasing amount of renewable energy into the grid via converters. This extensive and high-capacity integration of renewable energy imposes stringent performance criteria on converters [

3], particularly in terms of their efficiency [

4], reliability [

5], and active support capabilities [

6].

In the novel operational setting, the switching loss of the converter assumes a pivotal role as a critical quality factor, accounting for an increasing percentage of the overall loss due to high-frequency switching operations [

7]. Silicon carbide (SiC) metal–oxide–semiconductor field-effect transistors (MOSFETs) offer a substantial edge over silicon (Si) insulated-gate bipolar transistors (IGBTs), exhibiting a remarkable 2.86-fold reduction in switching losses across the same frequency range [

8]. Furthermore, SiC MOSFETs boast not only lower switching losses but also reduced conduction losses compared to Si MOSFETs [

9]. Theoretically, under equivalent withstand voltage, the drift layer resistance per unit area of SiC can be significantly diminished up to 300 times lower than Si [

10]. Additionally, Si-based devices have encountered their inherent physical constraints in terms of blocking voltage, making them insufficient for the upcoming era of high-voltage DC transmission lines, which typically boast rated voltages reaching up to 800 kV [

11]. In contrast, SiC devices exhibit a significantly superior blocking capability, allowing systems that employ these devices to reduce the number of components required in series submodule units [

12] and affiliated auxiliary electronic components [

4,

13]. This, in turn, leads to a further miniaturization of the converter. Furthermore, SiC material possesses the inherent advantage of being able to operate at elevated temperatures, unlike Si [

14]. By capitalizing on these advantages, SiC MOSFETs demonstrate exceptional performance in high-temperature, high-frequency, and high-voltage applications [

15]. However, despite the numerous benefits of SiC MOSFETs, their long-term reliability issues, as an emerging power electronic device, still necessitate in-depth research and solutions [

16].

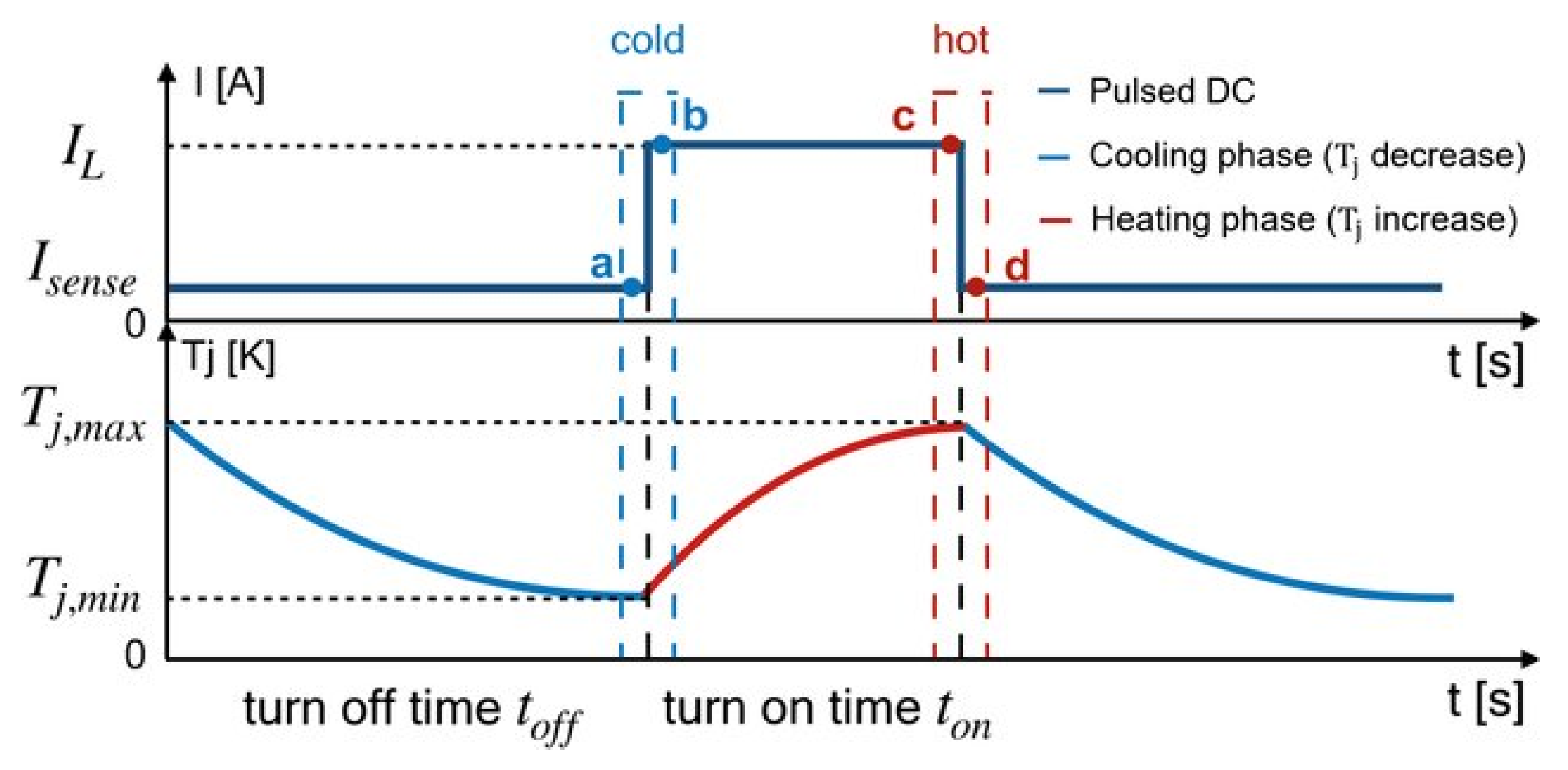

Power electronic devices consist of materials exhibiting diverse coefficients of thermal expansion (CTE), as depicted in

Figure 1. Temperature fluctuations within high-temperature, high-frequency, and high-voltage operating environments give rise to internal thermal stresses, resulting in degradation phenomena such as cracks. These cracks ultimately limit the device’s lifespan [

17]. In practical working conditions, device failure is a gradual process that occurs over an extended period. Consequently, in experimental research, the power cycling test (PCT) method is frequently utilized to expedite the failure process. The PCT is designed to simulate the thermo-mechanical stresses imposed on power electronic devices in their actual operating environments, enabling the investigation of component failures [

18].

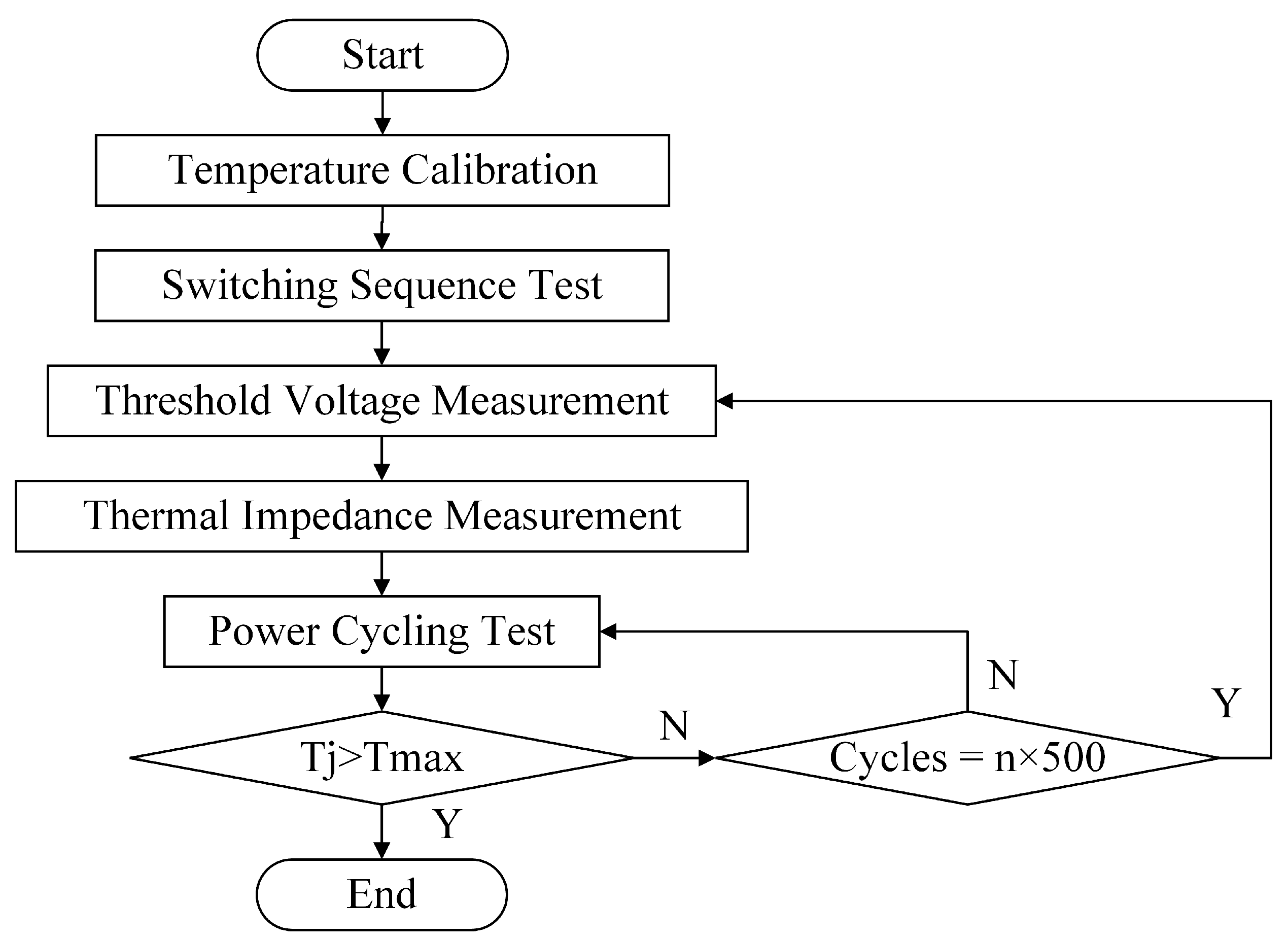

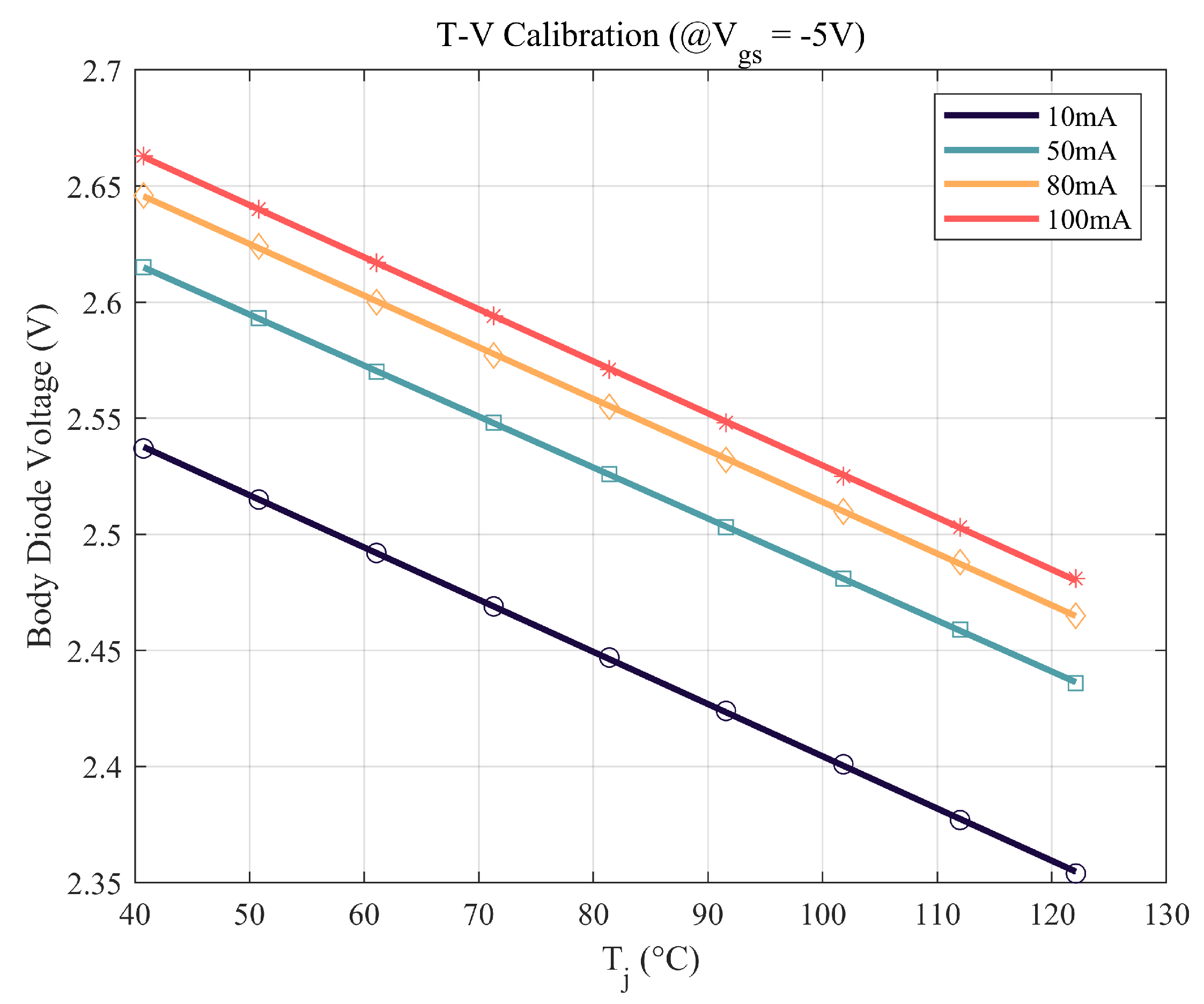

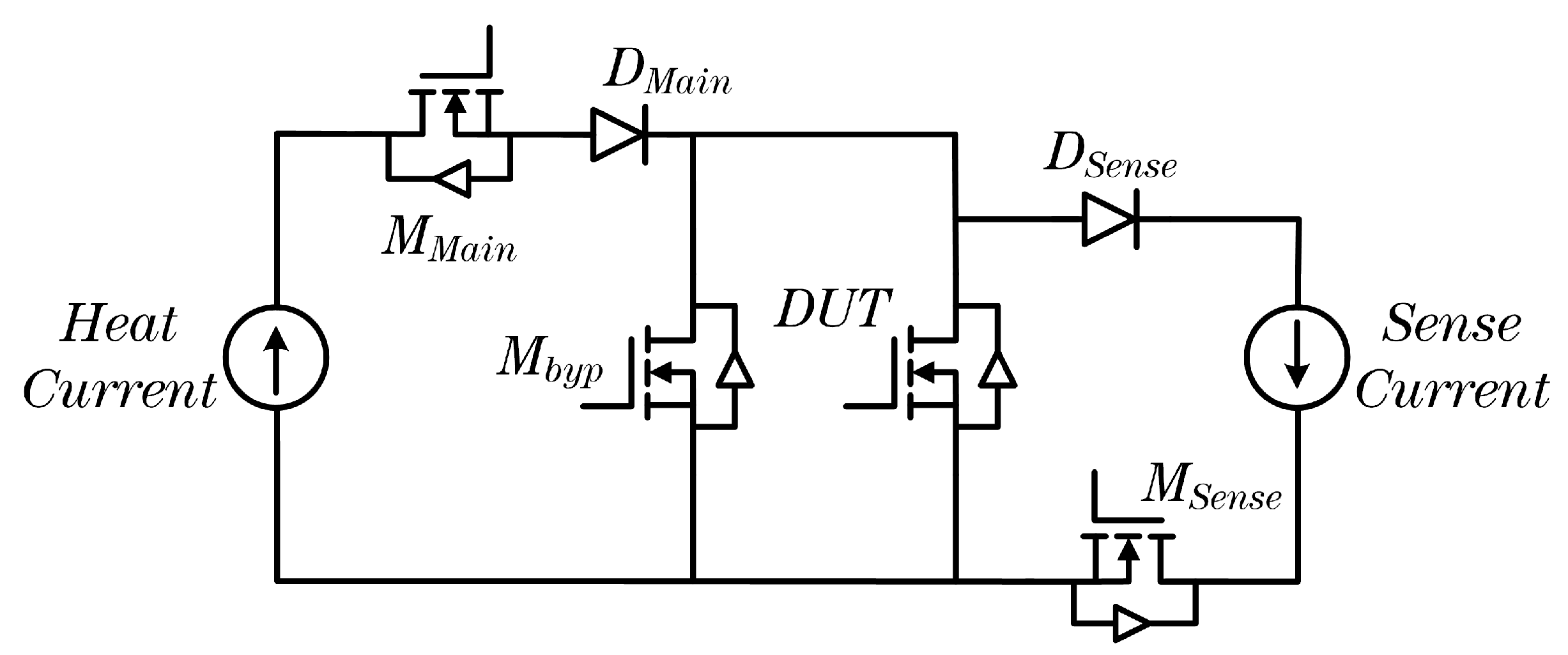

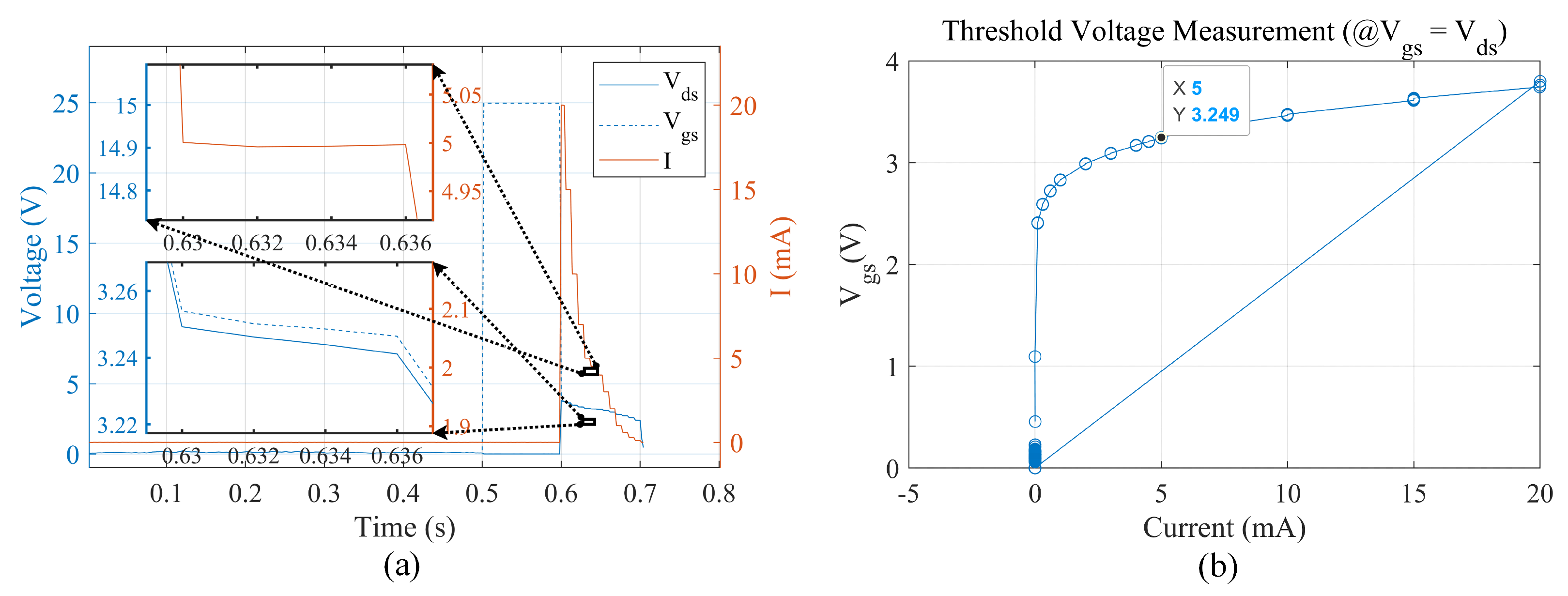

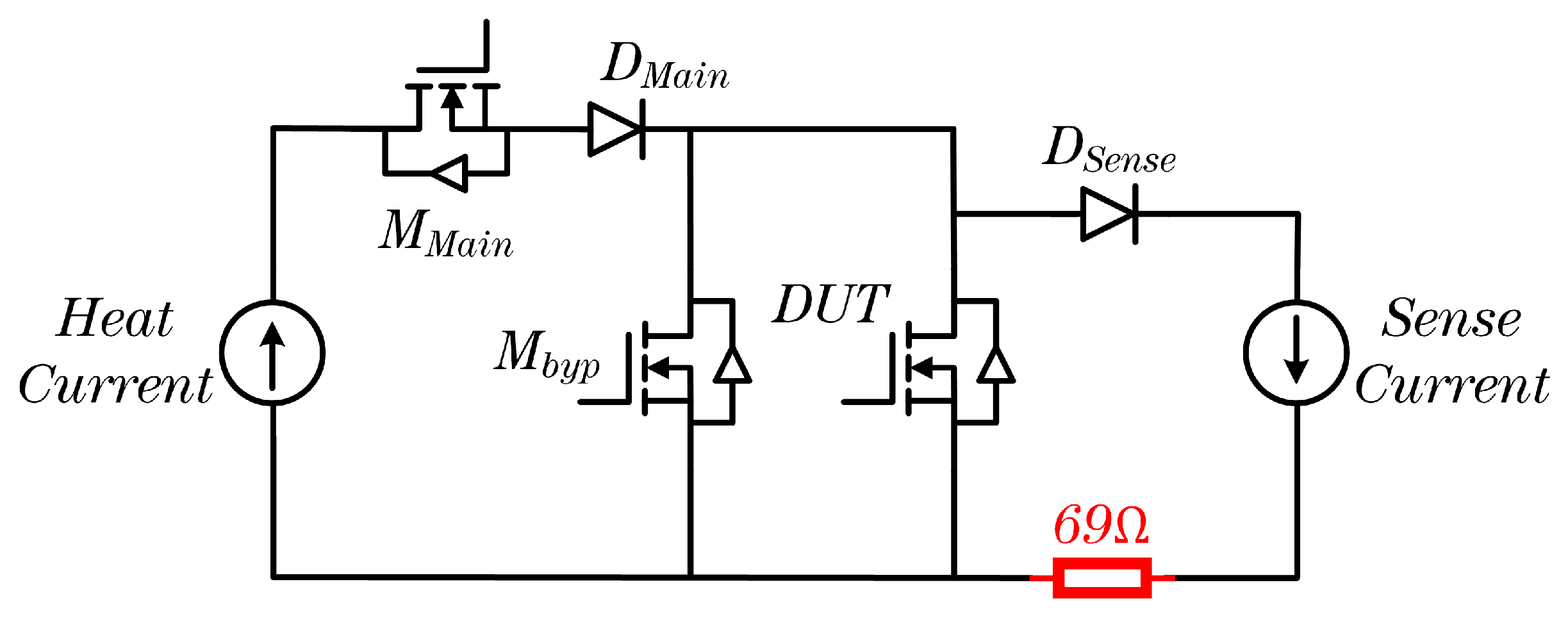

This paper aims to conduct a thorough investigation into the performance evolution of SiC MOSFETs under specific power cycling conditions, analyzing the underlying failure mechanisms through a systematic series of experimental studies. To establish a solid foundation, this paper begins with a concise overview of failure experiments conducted under power cycling conditions. This overview includes elucidating the fundamental failure principles of the device, discussing various experimental methodologies employed in power cycling, describing calibration procedures for temperature-sensitive parameters, and explaining the measurement techniques used to assess thermal impedance. Subsequently, a detailed description of the experimental methodology is presented. To accurately measure the variation in its threshold voltage, an offline threshold voltage measurement circuit is utilized, mitigating the short-term drift value arising from the wide bandgap characteristics of SiC [

19]. Furthermore, to precisely monitor the junction-to-case thermal impedance and identify the aging state of the solder layer, a thermal characterization experiment is conducted based on JESD51-14 [

20]. In the final section, the experimental results are comprehensively analyzed, delving into the exploration of potential failure mechanisms. Additionally, a brief discussion is presented regarding strategic measures to enhance the reliability of SiC MOSFETs.

4. Results and Discussion

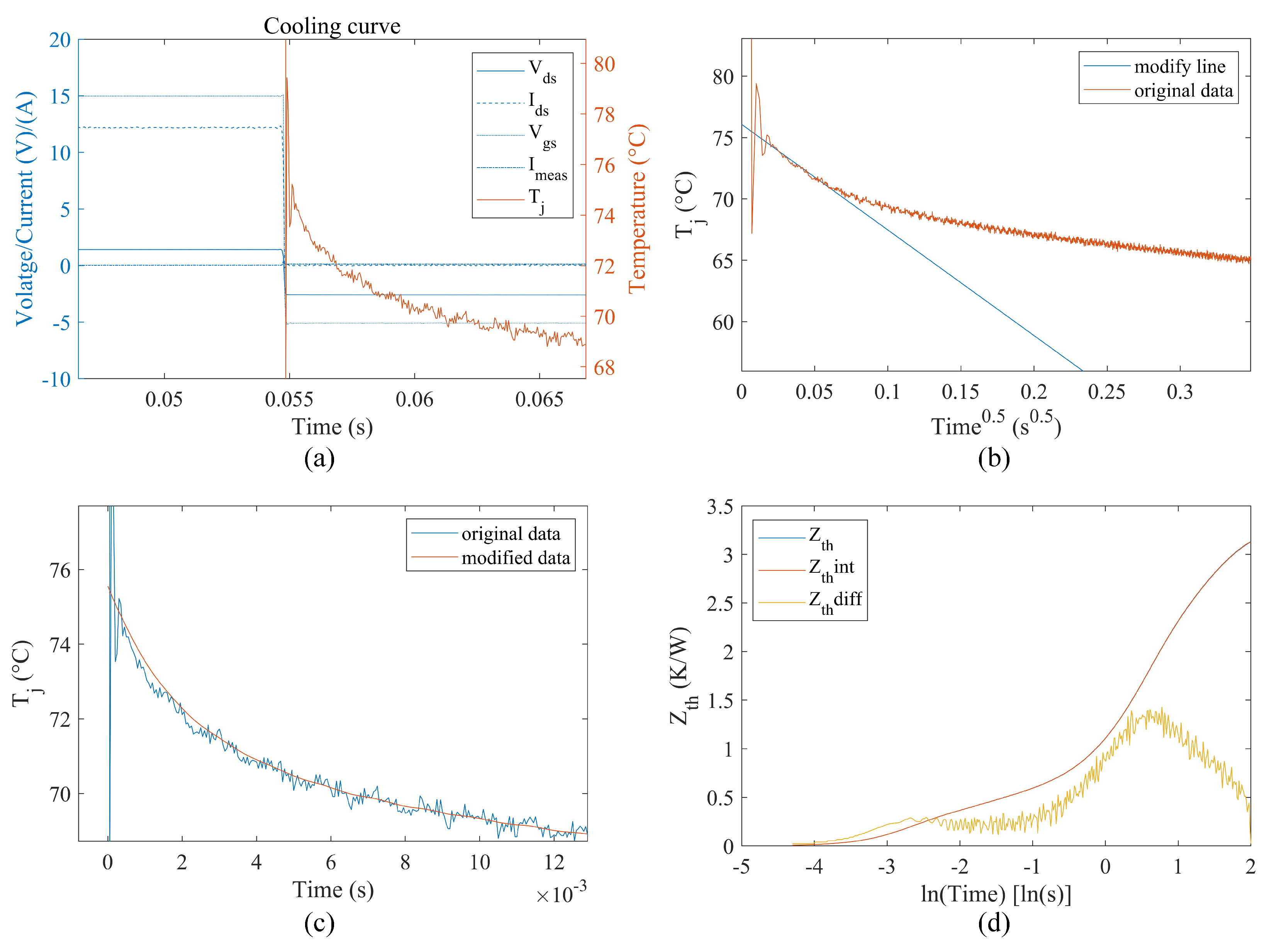

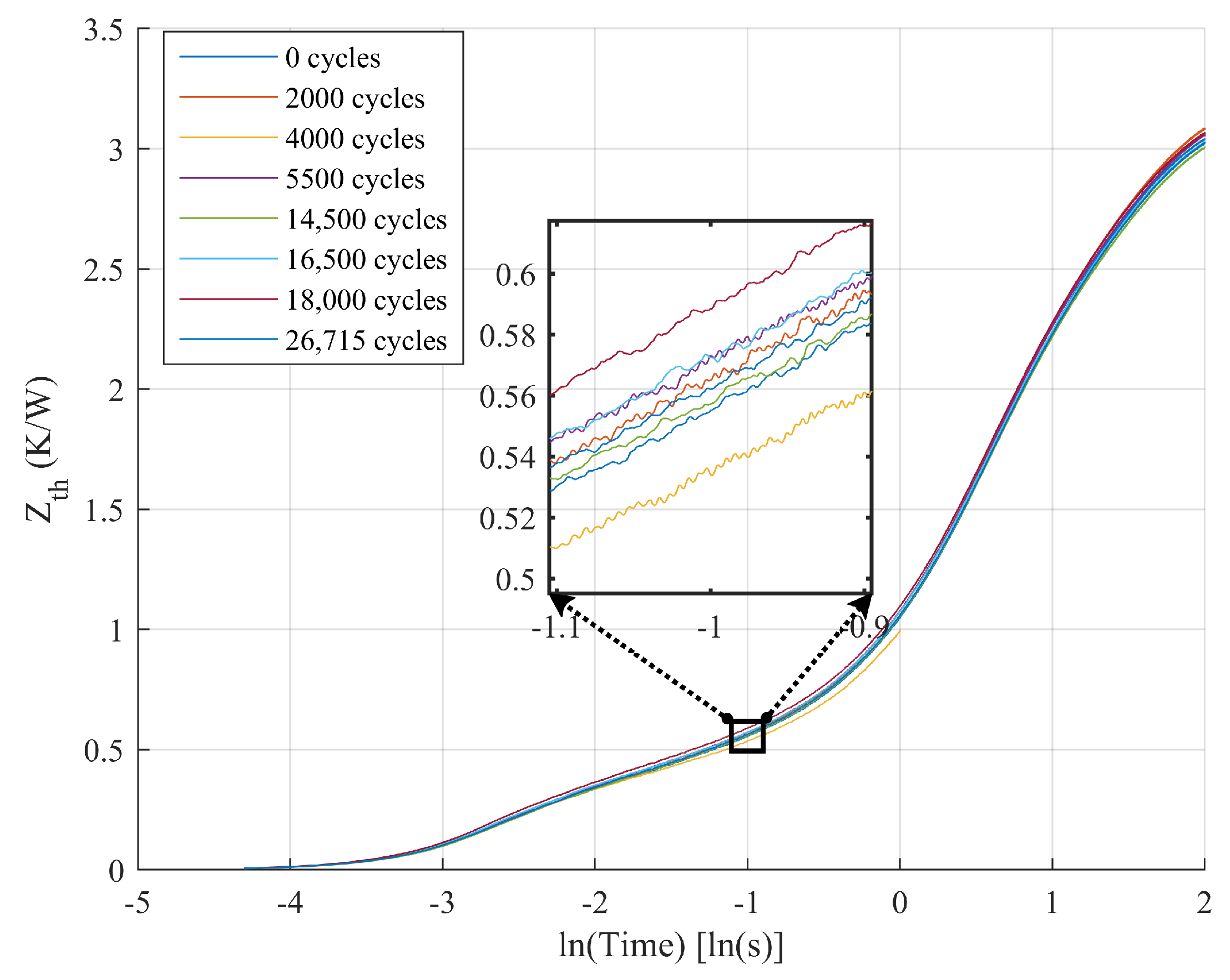

The thermal impedance curve of the device during the PCT is presented in

Figure 17, where the measured data for the initial 0.1 s represent the junction-to-case thermal impedance curve. The experimental results indicate that the thermal impedance did not exhibit a distinct or consistent increasing or decreasing trend, exhibiting fluctuations ranging from +4.7% to −5.6%. These fluctuations in the data can be attributed to inherent measurement errors in the instrumentation and variations in ambient temperature. Consequently, it can be deduced that there was no significant degradation of the solder layer within the device.

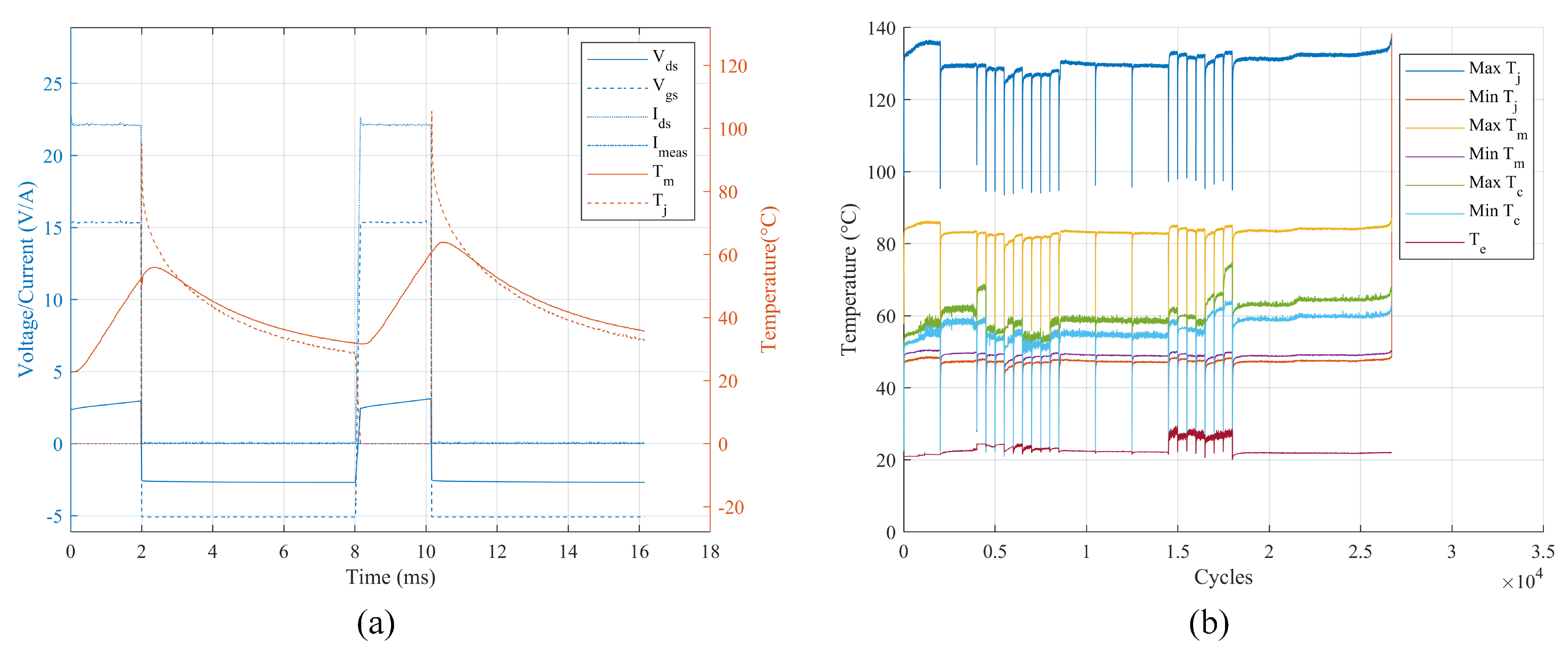

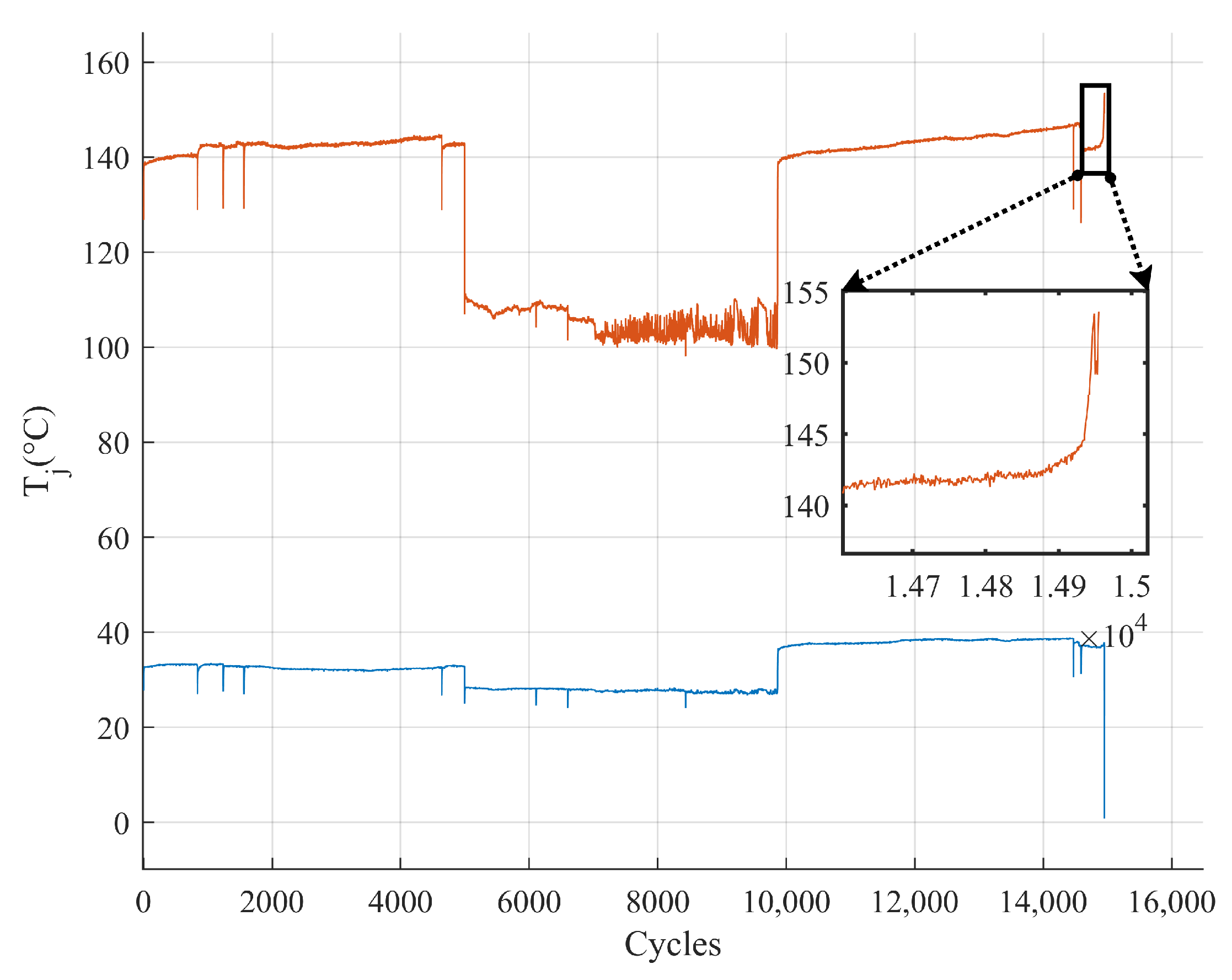

As depicted in

Figure 18, after completing the initial 2000 cycles, the device was removed from the test bench, resulting in a change in the contact resistance between the device and the test bench, thereby causing a variation in the maximum

. Subsequently, the maximum

stayed at around 130 ∘C for the initial 21,000 cycles, exhibiting a slightly increasing trend, as shown in

Table 6.

Figure 18 indicates that the environmental temperature also influenced the maximum

. At around 21,650 cycles, there was a significant rise in the maximum

. A distinct and abrupt increase in the maximum

was observed during power cycling at around 26,500 cycles. Utilizing the maximum temperature of the 3200th cycle as the baseline value, the percentage variation corresponding to the maximum

for different cycles is detailed in

Table 6. The results of

, a parameter characterizing bond-wire failure, are illustrated in

Figure 19, with the associated cycle numbers and percentage increases shown in

Table 6.

demonstrates a high degree of correlation with the trend of maximum

.

To mitigate the influence of current fluctuations, the corresponding

for different cycles was calculated. However, since

exhibited a positive correlation with

, it was necessary to consider the impact of

fluctuations on

. As the TSEP utilized was the body diode voltage drop at small currents, determining

during the high-current heating phase, i.e., the on-state phase of the device, was impractical. However,

could be reliably measured by affixing a thermocouple at the middle pin of the device, and

during the PCT was notably more discernible compared to the case temperature, as depicted in

Figure 18. Hence,

was regarded as representative of

during the heating phase. Given that the thermal impedance of the device remained relatively stable, the relationship between

and

theoretically remained consistent. The correlation between

and

during the cooling process was plotted for varying cycle numbers, and the outcomes are illustrated in

Figure 20.

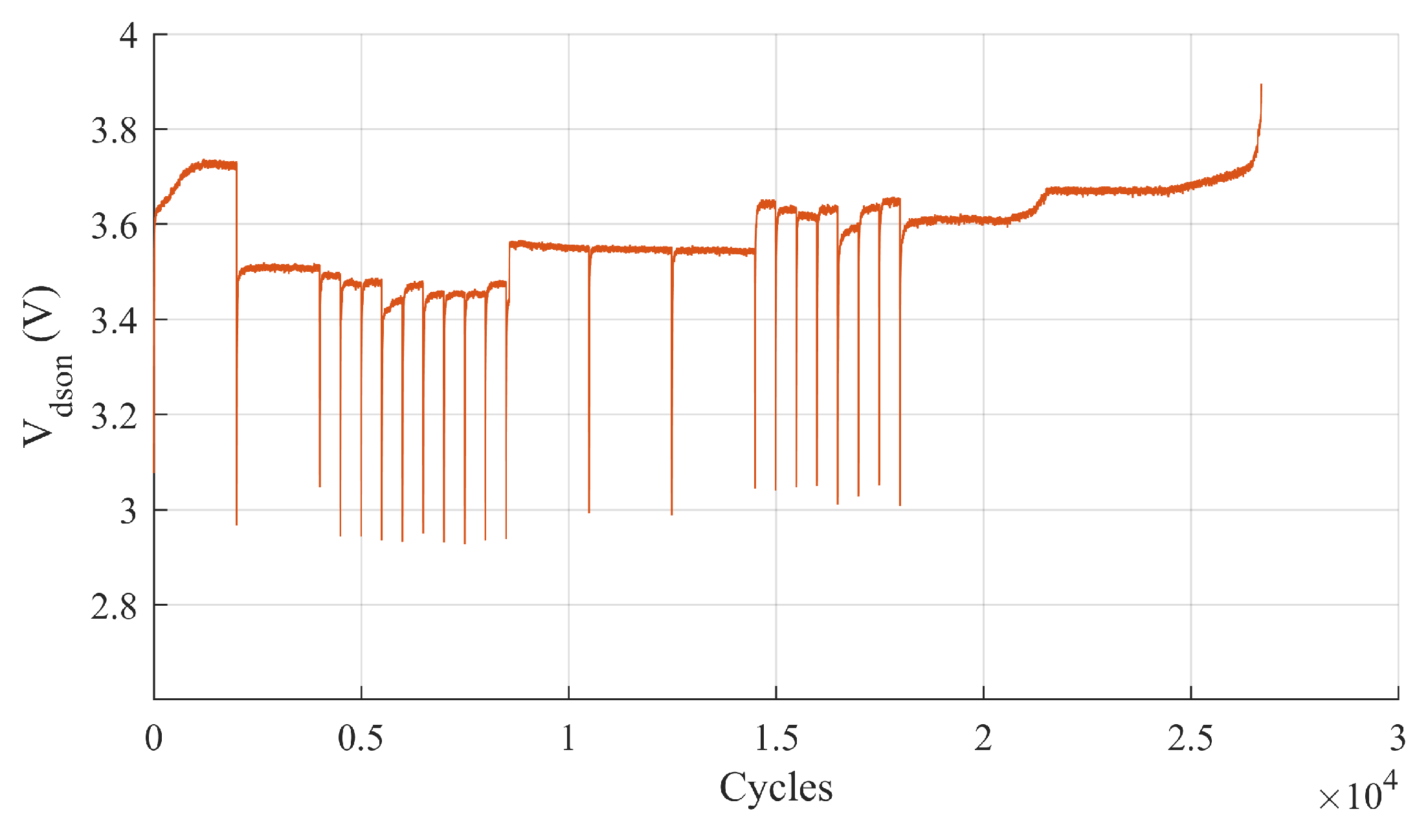

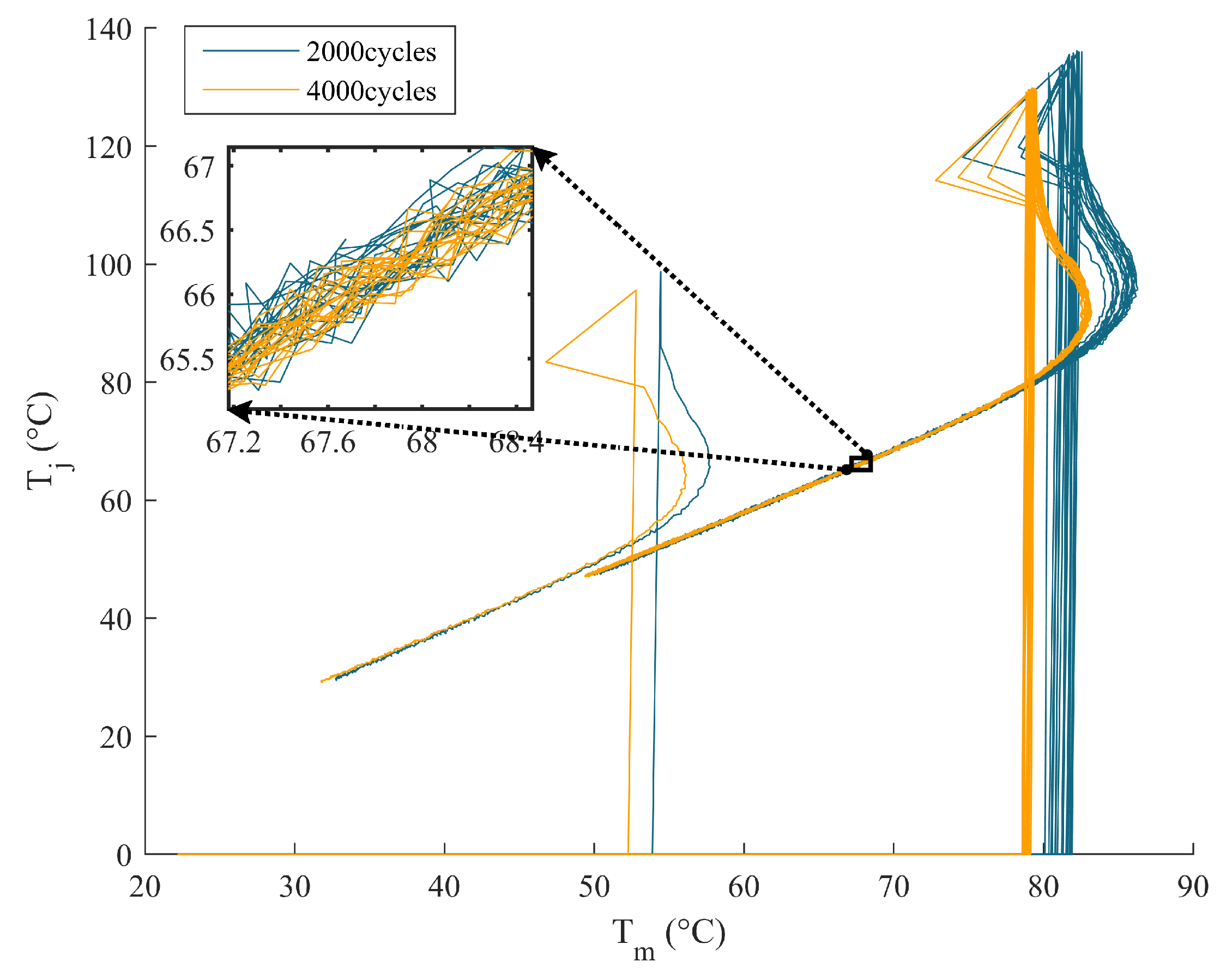

The relationship between

and

exhibits non-linearity as

nears its peak value following cycle stabilization across various cycle counts. Nevertheless, within the temperature range of 50 ∘C to 75 ∘C, a distinct linear correlation is evident, with a maximum error margin of less than 1 ∘C. This correlation is expressed by Equation (

3).

was plotted against

at 70 °C for each cycle, as depicted in

Figure 21. The corresponding

measurements for each cycle, along with their percentage increases, are summarized in

Table 6. A more consistent increasing trend can be observed from the

data. The 5 m

to 6 m

drop in

produced after the 2000 cycle can be attributed to changes in contact resistance within the circuit.

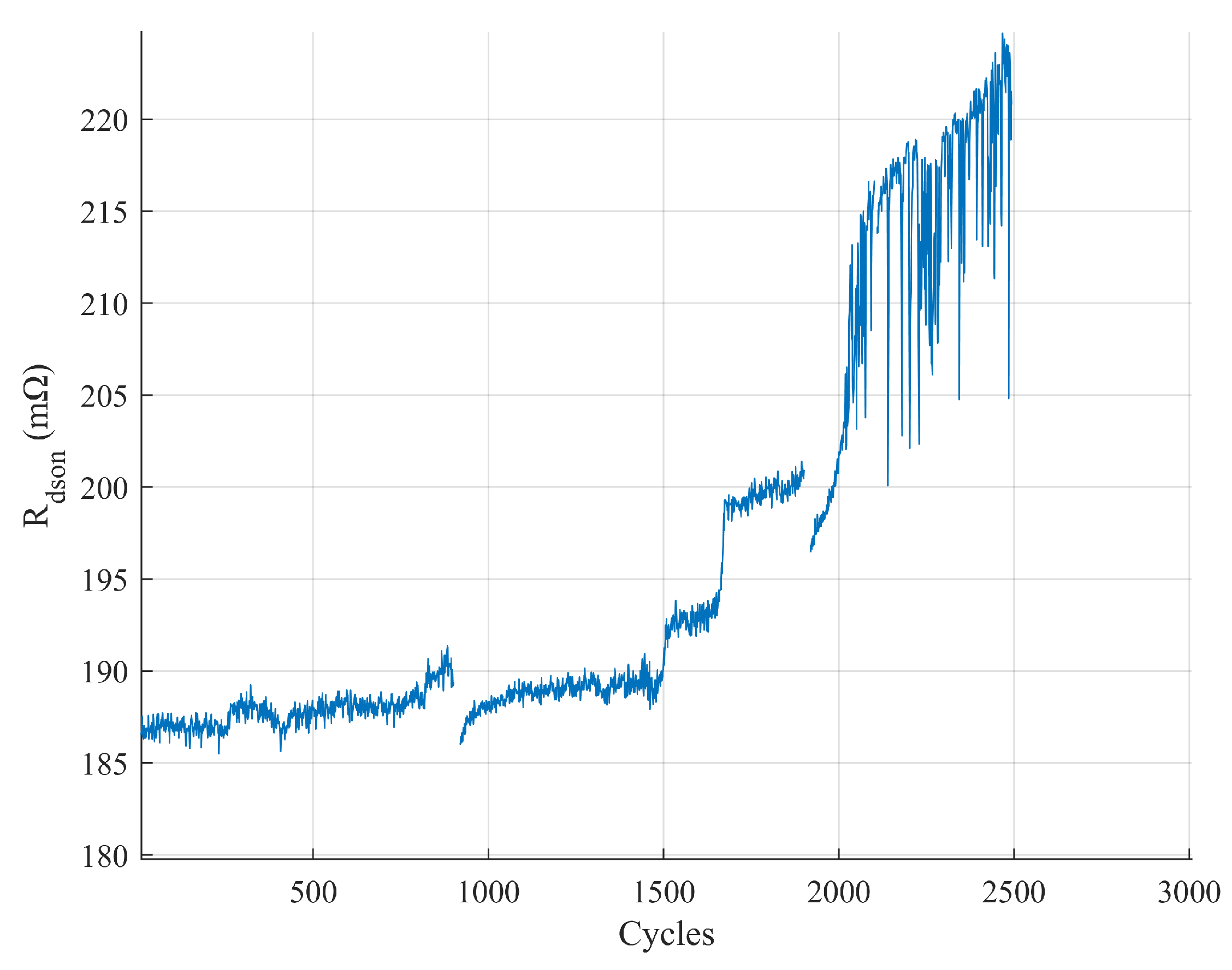

Since there was no significant degradation in the solder layer of the device, the change in

primarily stemmed from the failure of the bond wires. The C2M0080120D device with multiple bond wires shown in

Figure 18b was compared to the SCT30N120 device with a single bond wire, as shown in

Figure 22 (the notch in the PCT from 5000 to 9800 cycles is the maximum

change due to the current reduction caused by the misoperation of the current source). It was observed that the sudden

change phenomenon occurred only once for the device with a single bond wire, and the device could no longer operate for switching after 20 cycles following the sudden change in

. Therefore, it was concluded that one of the bond wires of the C2M0080120D device was lifted at 21,650 cycles, and the other bond wire exhibited visible cracking at 26,500 cycles, during which time the device could continue to operate.

The subsequent operation of another device of the same type after generating a drop of more than 5% in

is illustrated in

Figure 23. Following the lifting of one bond wire, the

of the device increased, resulting in higher power loss at the same current level. This increased power loss led to elevated currents passing through the remaining bond wires, intensifying the thermal stresses on the wires and accelerating the lifting of the other bond wire. The 5% failure criterion typically occurred between the lifting of the first bond wire and the lifting of the other bond wire. Remarkably, the device retained its operational capability during this process. In contrast to a single bond wire, which rapidly lost its functionality, multiple bond wires could still function for a certain period after reaching the failure criterion, thereby potentially enhancing the device’s reliability.

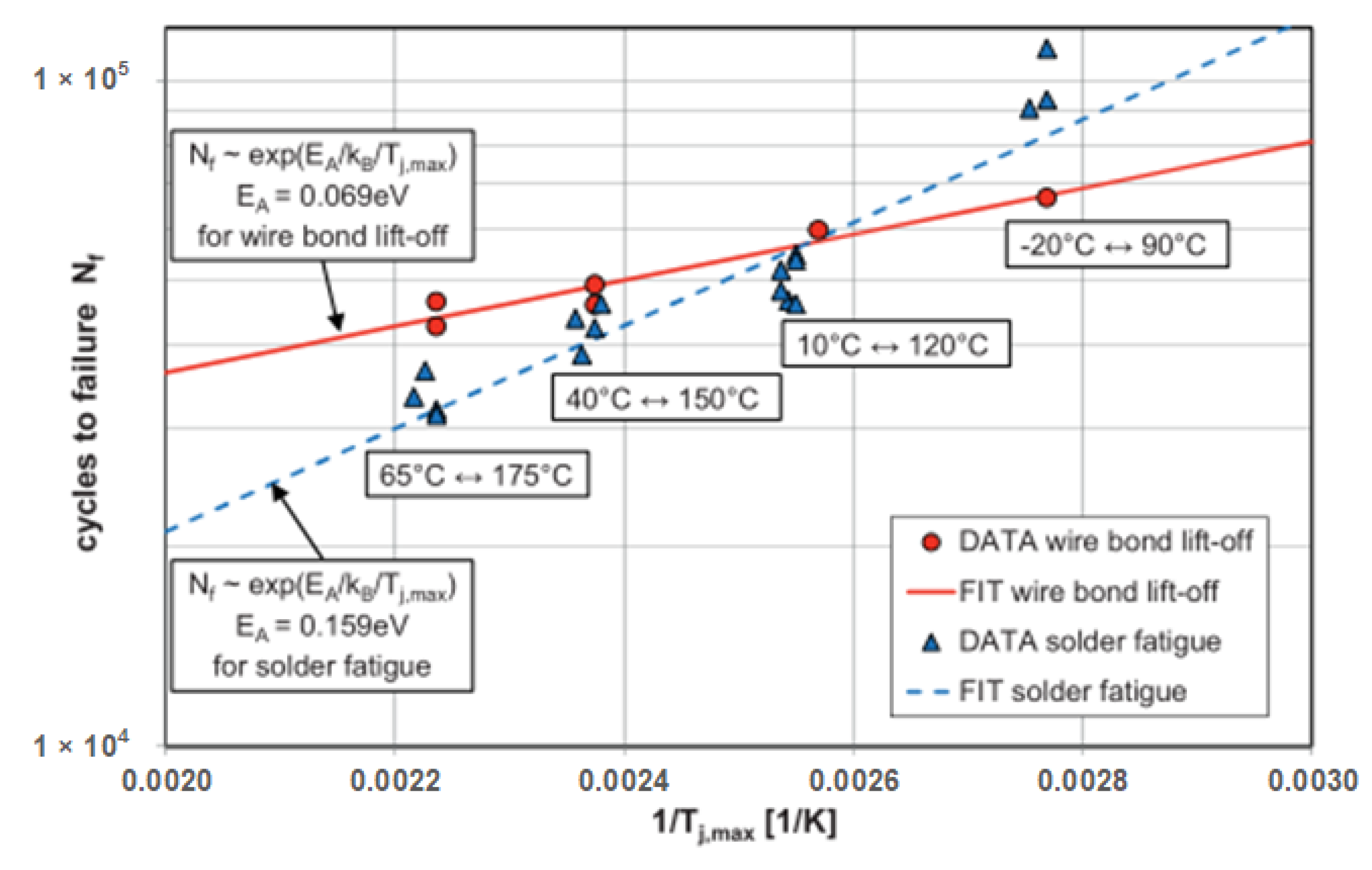

As shown in

Figure 17 and

Figure 21, the experimental results indicate that under second-level power cycling with

fluctuations ranging from approximately 47 ∘C to 130 ∘C, the predominant failures in devices were bond-wire failures, while there was no notable failure observed in the solder layer. The relationship between the number of cycle failures (

) and the maximum

can be expressed as follows:

, where

represents the activation energy and

denotes the Boltzmann constant. Compared to bond wires, solder layer fatigue necessitates higher activation energy, approximately twice the activation energy required for bond wires [

71], as illustrated in

Figure 24. Under the experimental conditions, where the maximum

was slightly lower, the number of cycles needed for solder layer failure exceeded that required for bond wires, thus rendering bond wires more susceptible to failure.

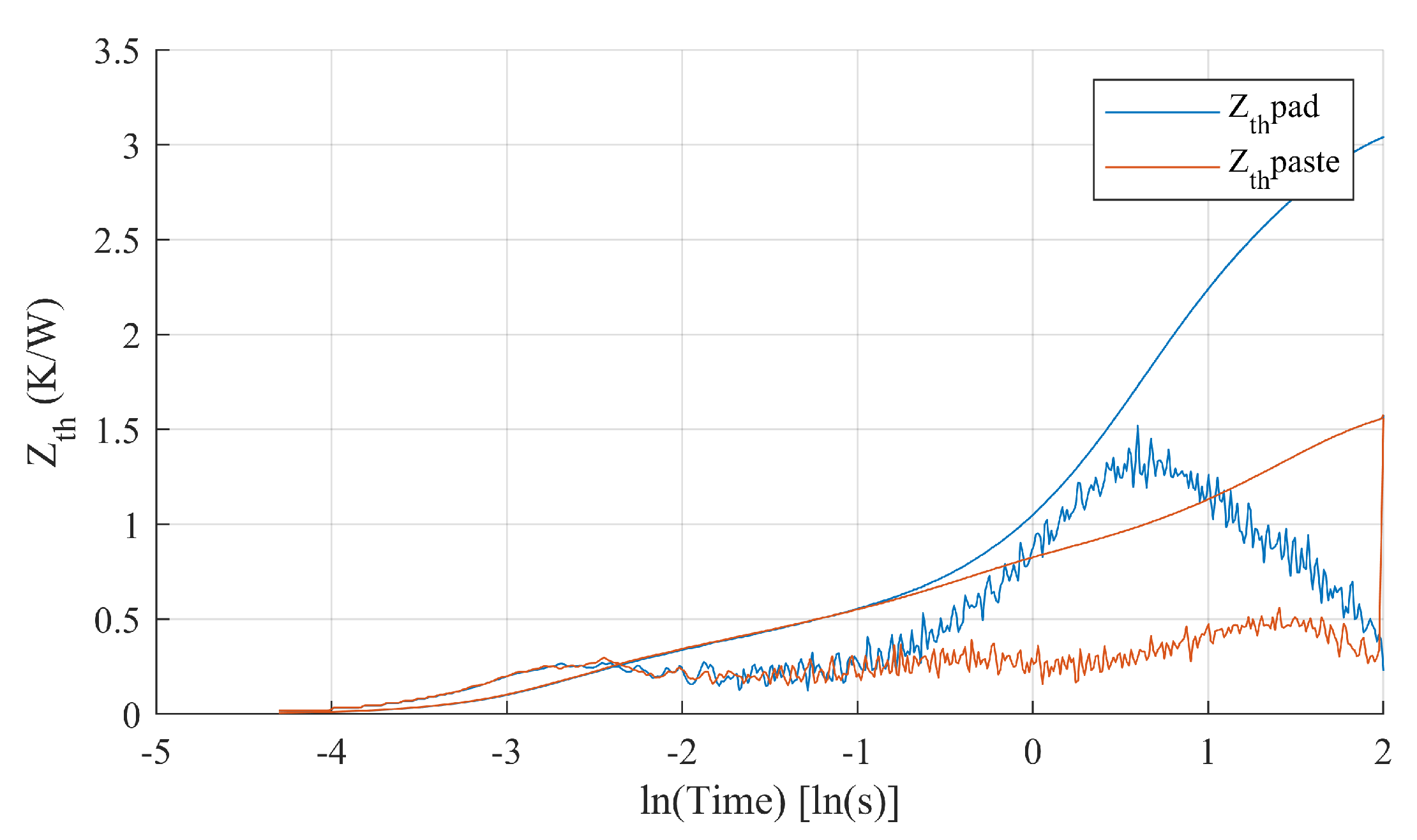

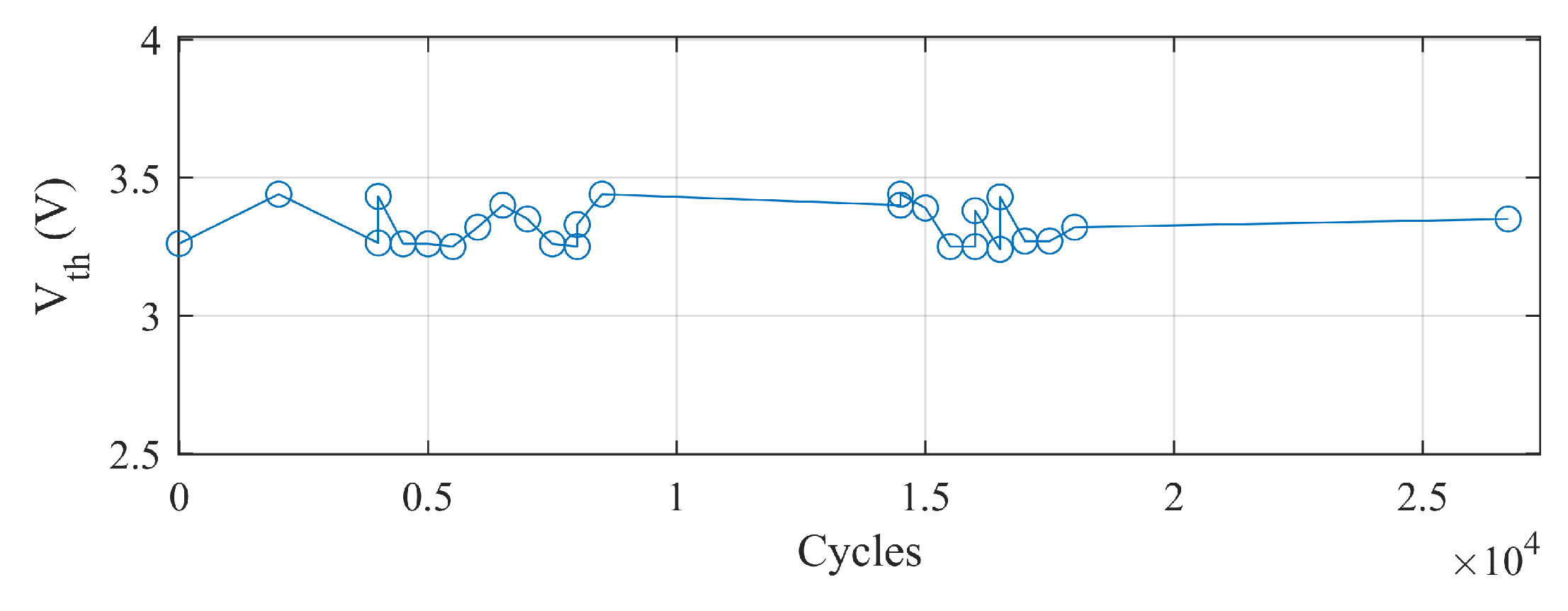

Figure 25 illustrates the fluctuation in the device’s threshold voltage throughout the entire power cycling process. Notably, during the experiment, the threshold voltage exhibited minimal changes, with a fluctuation range of 0.2 V. Given the power cycling test conditions, which involved a positively biased gate voltage of +15 V for 2 s during turn-on and a negatively biased gate voltage of −5 V for 6 s during turn-off, the products of the duration and value for both positively and negatively biased voltages were equivalent. This arrangement mitigates, to some extent, the threshold voltage drift caused by prolonged positive/negative biasing, as reported in [

29]. Furthermore, the existing literature [

72] indicates that the threshold voltage remains relatively stable when the gate voltage alternates between positive and negative values. This could explain the limited degradation observed in the threshold voltage. According to [

19], an increase in the threshold voltage due to drift would typically lead to an increase in channel resistance. However, when comparing the fluctuations in the threshold voltage and resistance, no corresponding decrease in

was observed despite an increase in the threshold voltage. Based on our experimental results, a clear correlation between these two parameters does not seem to exist.